Abstract

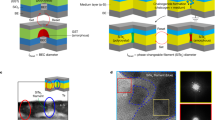

Metal–oxide memristive integrated technologies for analogue neuromorphic computing have undergone notable developments in the past decade, but are still not mature enough for very large-scale integration with complementary metal–oxide–semiconductor (CMOS) processes. Although non-volatile floating-gate synapse transistors are a more advanced technology embedded within CMOS processes, their performance as analogue resistive memories remains limited. Here, we report a low-power, two-terminal floating-gate transistor fabricated using standard single-poly technology in a commercial 180 nm CMOS process. Our device, which is integrated with a readout transistor, can operate in an energy-efficient subthreshold memristive mode. At the same time, it is linearized for small-signal changes with a two-orders-of-magnitude resistance dynamic range. Our device can be precisely tuned using optimized switching voltages and times, and can achieve 65 distinct resistive levels and ten-year analogue data retention. We experimentally demonstrate the feasibility of a selector-free integrated memristive array in basic neuromorphic applications, including spike-time-dependent plasticity, vector-matrix multiplication, associative memory and classification training.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the plots within this paper and other findings of this study are available from the corresponding author upon reasonable request.

Code availability

The computer codes used in this study are available within this paper and its Supplementary Information files.

References

Merolla, P. A. et al. A million spiking-neuron integrated circuit with a scalable communication network and interface. Science 345, 668–673 (2014).

Hasler, J. & Marr, B. Finding a roadmap to achieve large neuromorphic hardware systems. Front. Neurosci. 7, 118 (2013).

Benjamin, B. V. et al. Neurogrid: a mixed-analog-digital multichip system for large-scale neural simulations. Proc. IEEE 102, 699–716 (2014).

Furber, S. B., Galluppi, F., Temple, S. & Plana, S. The SpiNNaker project. Proc. IEEE 102, 652–665 (2014).

Indiveri, G. et al. Neuromorphic silicon neuron circuits. Front. Neurosci. 5, 73 (2011).

Likharev, K. K. CrossNets: neuromorphic hybrid CMOS/nanoelectronic networks. Sci. Adv. Mater. 3, 322–331 (2011).

LeCun, Y., Bengio, Y. & Hinton, G. Deep learning. Nature 521, 436–444 (2015).

Diorio, C., Hasler, P., Minch, A. & Mead, C. Neuromorphic Systems Engineering: Neural Networks in Silicon Ch. 14 (Springer, 1998).

Diorio, C., Hasler, P., Minch, A. & Mead, C. A single-transistor silicon synapse. IEEE Trans. Electron. Dev. 43, 1972–1980 (1996).

Hasler, P., Minch, B. A. & Diorio, C. Adaptive circuits using pFET floating-gate devices. In Proceedings of the 20th Anniversary Conference on Advanced Research in VLSI (ARVLSI) 215–229 (IEEE, 1999).

Hasler, P., Diorio, C., Minch, B. A. & Mead, C. Single transistor learning synapses. In Proceedings of the 7th International Conference on Neural Information Processing Systems (NIPS) 817–824 (ACM, 1994).

Hasler, P., Minch, B. A. & Diorio, C. An autozeroing floating-gate amplifier. IEEE Trans. Circ. Syst. II 48, 74–82 (2001).

Ramakrishnan, S., Hasler, P. & Gordon, C. Floating gate synapses with spike time dependent plasticity. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS) 369–372 (IEEE, 2010).

Wong, H. S. P. & Salahuddin, S. Memory leads the way to better computing. Nat. Nanotechnol. 10, 191–194 (2015).

Waser, R. & Aono, M. Nanoionics-based resistive switching memories. Nat. Mater. 6, 833–840 (2007).

Chua, L. O. Memristor—the missing circuit element. IEEE Trans. Circuit Theory 18, 507–519 (1971).

Chua, L. O. & Kang, S. M. Memristive devices and systems. Proc. IEEE 64, 209–223 (1976).

Strukov, D. B., Snider, G. S., Stewart, D. R. & Williams, R. S. The missing memristor found. Nature 453, 80–83 (2008).

Jo, S. H. et al. Nanoscale memristor device as synapse in neuromorphic systems. Nano Lett. 10, 1297–1301 (2010).

Wang, Z. et al. Fully memristive neural networks for pattern classification with unsupervised learning. Nat. Electron. 1, 137–145 (2018).

Xia, Q. & Yang, J. J. Memristive crossbar arrays for brain-inspired computing. Nat. Mater. 18, 309–323 (2019).

Prezioso, M. et al. Training and operation of an integrated neuromorphic network based on metal–oxide memristors. Nature 521, 61–64 (2015).

Merrikh Bayat, F. et al. Implementation of multilayer perceptron network with highly uniform passive memristive crossbar circuits. Nat. Commun. 9, 2331 (2018).

Adam, G. C., Khiat, A. & Prodromakis, T. Challenges hindering memristive neuromorphic hardware from going mainstream. Nat. Commun. 9, 5267 (2018).

Niu, D., Chen, Y., Xu, C. & Xie, Y. Impact of process variations on emerging memristor. In Proceedings of the 47th Design Automation Conference (DAC) 877–882 (IEEE, 2010).

Waser, R., Dittmann, R., Staikov, G. & Szot, K. Redox-based resistive switching memories—nanoionic mechanisms, prospects and challenges. Adv. Mater. 21, 2632–2663 (2009).

Pouyan, P., Amat, E. & Rubio, A. Reliability challenges in design of memristive memories. In Proceedings of the 5th European Workshop on CMOS Variability (VARI) 1–6 (IEEE, 2014).

Indiveri, G. et al. Integration of nanoscale memristor synapses in neuromorphic computing architectures. Nanotechnology 24, 384010 (2013).

Merrikh Bayat, F. et al. High-performance mixed-signal neurocomputing with nanoscale floating-gate memory cell arrays. IEEE Trans. Neural Netw. Learn. Syst. 29, 4782–4790 (2018).

Merrikh Bayat, F. et al. Redesigning commercial floating-gate memory for analog computing applications. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS) 1921–1924 (IEEE, 2015).

Merrikh Bayat, F. et al. Model-based high-precision tuning of NOR flash memory cells for analog computing applications. In Proceedings of the Device Research Conference (DRC) 1–2 (IEEE, 2016).

Guo, X. et al. Temperature-insensitive analog vector-by-matrix multiplier based on 55 nm NOR flash memory cells. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC) 1–4 (IEEE, 2017).

Guo, X. et al. Fast, energy-efficient, robust, and reproducible mixed-signal neuromorphic classifier based on embedded NOR flash memory technology. In Proceedings of the International Electron Devices Meeting (IEDM) 6.5.1–6.5.4 (IEEE, 2017).

Ziegler, M. et al. Memristive operation mode of floating gate transistors: a two-terminal MemFlash-cell. Appl. Phys. Lett. 101, 263504 (2012).

Ziegler, M. & Kohlstedt, H. Mimic synaptic behavior with a single floating gate transistor: a MemFlash synapse. J. Appl. Phys. 114, 194506 (2013).

Himmel, N. et al. Memristive device based on a depletion-type SONOS field effect transistor. Semicond. Sci. Technol. 32.6, 06LT01 (2017).

Winterfeld, H. et al. Technology and electrical characterization of MemFlash cells for neuromorphic applications. J. Appl. Phys. 51, 324003 (2018).

Roizin, Y. & Pikhay, E. Memristor using parallel asymmetrical transistors having shared floating gate and diode. US patent 9,514,818 (2016).

Sharroush, S. M., Abdalla, Y. S., Dessouki, A. A. & El-Badawy, E. S. A. Subthreshold MOSFET transistor amplifier operation. In Proceedings of the 4th International Design Test Workshop (IDT) 1–6 (IEEE, 2009).

Chang, T., Jo, S. H. & Lu, W. Short-term memory to long-term memory transition in a nanoscale memristor. ACS Nano 5, 7669–7676 (2011).

Caporale, N. & Dan, Y. Spike timing-dependent plasticity: a Hebbian learning rule. Annu. Rev. Neurosci. 31, 25–46 (2008).

Brivio, S. et al. Extended memory lifetime in spiking neural networks employing memristive synapses with nonlinear conductance dynamics. Nanotechnology 30, 015102 (2018).

Hu, S. G. et al. Associative memory realized by a reconfigurable memristive Hopfield neural network. Nat. Commun. 6, 7522 (2015).

Verleysen, M., Sirletti, B., Vandemeulebroecke, A. & Jespers, P. G. A. A high-storage capacity content-addressable memory and its learning algorithm. IEEE Trans. Circ. Syst. 36, 762–766 (1989).

Tank, D. & Hopfield, J. J. Simple ‘neural’ optimization networks: an A/D converter, signal decision circuit and a linear programming circuit. IEEE Trans. Circ. Syst. 33, 533–541 (1986).

Hopfield, J. J Neurons with graded response have collective computational properties like those of two-state neurons. Proc. Natl Acad. Sci. USA 81, 3088–3092 (1984).

Sandrini, J. et al. Effect of metal buffer layer and thermal annealing on HfOx-based ReRAMs. In Proceedings of the IEEE International Conference on the Science of Electrical Engineering (ICSEE) 1–5 (IEEE, 2016).

Ko, P. K., Hu, C. & Tam, S. Lucky-electron model of channel hot-electron injection in MOSFET’s. IEEE Trans. Electron Dev. 31, 1116–1125 (1984).

Chan, T. Y., Chen, J., Ko, P. K. & Hu, C. The impact of gate-induced drain leakage current on MOSFET scaling. In Proceedings of the International Electron Devices Meeting (IEDM) 718–721 (IEEE, 1987).

Zidan, M. A., Fahmy, H. A. H., Hussain, M. M. & Salama, K. N. Memristor-based memory: the sneak paths problem and solutions. Microelectron. J. 44, 176–183 (2013).

Acknowledgements

This research was partially supported by the Israeli Planning and Budgeting Committee Fellowship, by the Israel Ministry of Economics KAMIN project no. 57681, by the Andrew and Erna Finci Viterbi Graduate Fellowship and by the European Research Council under the European Union’s Horizon 2020 Research and Innovation Programme under agreement no. 757259.

Author information

Authors and Affiliations

Contributions

L.D., Y.R., R.D. and S.K. designed the study. L.D., E.H. and E.P. performed experiments and collected data. E.P. and Y.R. invented the Y-flash memristive structure and L.D., R.D. and S.K. invented the subthreshold small-signal memristive operation mode. L.D. developed models and executed simulations. All authors analysed the data, discussed the results and wrote the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Sections 1–6 and Tables 1–10.

Rights and permissions

About this article

Cite this article

Danial, L., Pikhay, E., Herbelin, E. et al. Two-terminal floating-gate transistors with a low-power memristive operation mode for analogue neuromorphic computing. Nat Electron 2, 596–605 (2019). https://doi.org/10.1038/s41928-019-0331-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-019-0331-1

This article is cited by

-

Interface-type tunable oxygen ion dynamics for physical reservoir computing

Nature Communications (2023)

-

Nanograin network memory with reconfigurable percolation paths for synaptic interactions

Light: Science & Applications (2023)

-

Humanlike spontaneous motion coordination of robotic fingers through spatial multi-input spike signal multiplexing

Nature Communications (2023)

-

Multi-neuron connection using multi-terminal floating–gate memristor for unsupervised learning

Nature Communications (2023)

-

Recent progress in three-terminal artificial synapses based on 2D materials: from mechanisms to applications

Microsystems & Nanoengineering (2023)