Abstract

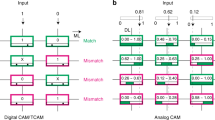

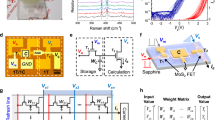

Ternary content-addressable memory (TCAM) is specialized hardware that can perform in-memory search and pattern matching for data-intensive applications. However, achieving TCAMs with high search capacity, good area efficiency and good energy efficiency remains a challenge. Here, we show that two-transistor–two-resistor (2T2R) transition metal dichalcogenide TCAM (TMD-TCAM) cells can be created by integrating single-layer MoS2 transistors with metal-oxide resistive random-access memories (RRAMs). The MoS2 transistors have very low leakage currents and can program the RRAMs with exceptionally robust current control, enabling the parallel search of very large numbers of data bits. These TCAM cells also exhibit remarkably large resistance ratios (R-ratios) of up to 8.5 × 105 between match and mismatch states. This R-ratio is comparable to that of commercial TCAMs using static random-access memories (SRAMs), with the key advantage that our 2T2R TCAMs use far fewer transistors and have zero standby power due to the non-volatility of RRAMs.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the plots within this paper and other findings of this study are available from the corresponding author upon reasonable request.

References

Wong, H.-S. P. & Salahuddin, S. Memory leads the way to better computing. Nat. Nanotechnol. 10, 191–194 (2015).

Theis, T. N. & Wong, H.-S. P. The end of Moore’s law: a new beginning for information technology. Comput. Sci. Eng. 19, 41–50 (2017).

Ventra, M. D. & Pershin, Y. V. The parallel approach. Nat. Phys. 9, 200–202 (2013).

Guo, Q. et al. Resistive ternary content addressable memory systems for data-intensive computing. IEEE Micro 35, 62–71 (2015).

lelmini, D. & Wong, H.-S. P. In-memory computing with resistive switching devices. Nat. Electron. 1, 333–343 (2018).

Chang, M. F. et al. A 3T1R nonvolatile TCAM using MLC ReRAM for frequent-off instant-on filters in IoT and big-data processing. IEEE J. Solid-St. Circ. 52, 1664–1679 (2017).

Pagiamtzis, K. & Sheikholeslami, A. Content-addressable memory (CAM) circuits and architectures: a tutorial and survey. IEEE J. Solid-St. Circ. 41, 712–727 (2006).

Li, J., Montoye, R. K., Ishii, M. & Chang, L. 1 Mb 0.41 μm2 2T-2R cell nonvolatile TCAM with two-bit encoding and clocked self-referenced sensing. IEEE J. Solid-St. Circ. 49, 896–907 (2014).

Matsunaga, S. et al. A 3.14 μm2 4T-2MTJ-cell fully parallel TCAM based on nonvolatile logic-in-memory architecture. 2012 Symp. VLSI Circuits (VLSIC) https://doi.org/10.1109/VLSIC.2012.6243781 (IEEE, 2012).

Imani, M., Rahimi, A. & Rosing, T. S. Resistive configurable associative memory for approximate computing. In 2016 Design, Automation & Test in Europe Conference & Exhibition (DATE) 1327–1332 (IEEE, 2016).

Gurarslan, A. et al. Surface-energy-assisted perfect transfer of centimeter-scale monolayer and few-layer MoS2 films onto arbitrary substrates. ACS Nano 8, 11522–11528 (2014).

Aly, M. M. S. et al. Energy-efficient abundant-data computing: the N3XT 1,000 × . IEEE Computer 48, 24–33 (2015).

Huang, Y. L. et al. Bandgap tunability at single-layer molybdenum disulphide grain boundaries. Nat. Commun. 6, 6298 (2015).

Alam, K. & Lake, R. K. Monolayer MoS2 transistors beyond the technology road map. IEEE Trans. Electron Devices 59, 3250–3254 (2012).

Ryou, J., Kim, Y.-S., Santosh, K. C. & Cho, K. Monolayer MoS2 bandgap modulation by dielectric environments and tunable bandgap transistors. Sci. Rep. 6, 29184 (2016).

Illarionov, Y. Y. et al. Improved hysteresis and reliability of MoS2 transistors with high-quality CVD growth and Al2O3 encapsulation. IEEE Electron Device Lett. 38, 1763–1766 (2017).

Kshirsagar, C. U. et al. Dynamic memory cells using MoS2 field-effect transistors demonstrating femtoampere leakage currents. ACS Nano 10, 8457–8464 (2016).

Wang, H. et al. Large-scale 2D electronics based on single-layer MoS2 grown by chemical vapor deposition. 2012 IEEE Int. Electron Devices Meeting (IEDM) https://doi.org/10.1109/IEDM.2012.6478980 (IEEE, 2012).

Smithe, K. K. H., Suryavanshi, S. V., Rojo, M. M., Tedjarati, A. D. & Pop, E. Low variability in synthetic monolayer MoS2 devices. ACS Nano 11, 8456–8463 (2017).

Wachter, S., Polyushkin, D. K., Bethge, O. & Mueller, T. A microprocessor based on a two-dimensional semiconductor. Nat. Commun. 8, 14948 (2017).

Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors. Nat. Rev. Mat. 1, 16052 (2016).

Yang, R., Wang, Z. & Feng, P. X.-L. Electrical breakdown of multilayer MoS2 field-effect transistors with thickness-dependent mobility. Nanoscale 6, 12383–12390 (2014).

English, C. D., Smithe, K. K. H., Xu, R. L. & Pop, E. Approaching ballistic transport in monolayer MoS2 transistors with self-aligned 10 nm top gates. 2016 IEEE Int. Electron Devices Meeting (IEDM) https://doi.org/10.1109/IEDM.2016.7838355 (IEEE, 2016).

Liu, H., Neal, A. T. & Ye, P. D. Channel length scaling of MoS2 MOSFETs. ACS Nano 6, 8563–8569 (2012).

Frank, D. J., Taur, Y. & Wong, H.-S. P. Generalized scale length for two-dimensional effects in MOSFETs. IEEE Electron Device Lett. 19, 385–387 (1998).

Yu, Z. et al. Towards intrinsic charge transport in monolayer molybdenum disulfide by defect and interface engineering. Nat. Commun. 5, 5290 (2014).

English, C. D., Shine, G., Dorgan, V. E., Saraswat, K. C. & Pop, E. Improved contacts to MoS2 transistors by ultra-high vacuum metal deposition. Nano Lett. 16, 3824–3830 (2016).

Cao, W., Kang, J., Sarkar, D., Liu, W. & Banerjee, K. 2D semiconductor FETs—projections and design for sub-10 nm VLSI. IEEE Trans. Electron Devices 62, 3459–3469 (2015).

Cui, X. et al. Multi-terminal transport measurements of MoS2 using a van der Waals heterostructure device platform. Nat. Nanotechnol. 10, 534–540 (2015).

Wong, H.-S. P. et al. Metal-oxide RRAM. Proc. IEEE 100, 1951–1970 (2012).

Goux, L. et al. On the gradual unipolar and bipolar resistive switching of TiN/HfO2/Pt memory systems. Electrochem. Solid-St. Lett. 13, G54–G56 (2010).

Wu, H. et al. Stable self-compliance resistive switching in AlOδ/Ta2O5−x/TaOy triple layer devices. Nanotechnology 26, 035203 (2015).

Yu, S., Chen, H.-Y., Gao, B., Kang, J. & Wong, H.-S. P. HfOx-based vertical resistive switching random access memory suitable for bit-cost-effective three-dimensional cross-point architecture. ACS Nano 7, 2320–2325 (2013).

Govoreanu, B. et al. 10 × 10 nm2 Hf/HfOx crossbar resistive RAM with excellent performance, reliability and low-energy operation. 2011 IEEE Int. Electron Devices Meeting (IEDM) https://doi.org/10.1109/IEDM.2011.6131652 (IEEE, 2011).

Lee, M.-J. et al. A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta2O5−x/TaO2− x bilayer structures. Nat. Mater. 10, 625–630 (2011).

Dong, W., Liu, D., Xu, S., Chen, B. & Zhao, Y. Demonstrate high ROFF/RON ratio and forming-free RRAM for rFPGA application based on switching layer engineering. 2017 IEEE 12th Int. Conf. on ASIC (ASICON) https://doi.org/10.1109/ASICON.2017.8252610 (IEEE, 2017).

Nail, C. et al. Understanding RRAM endurance, retention and window margin trade-off using experimental results and simulations. 2016 IEEE Int. Electron Devices Meeting (IEDM) https://doi.org/10.1109/IEDM.2016.7838346 (IEEE, 2016).

Yang, R. et al. 2D molybdenum disulfide (MoS2) transistors driving RRAMs with 1T1R configuration. 2017 IEEE Int. Electron Devices Meeting (IEDM) https://doi.org/10.1109/IEDM.2017.8268423 (IEEE, 2017).

Smithe, K. K. H., English, C. D., Suryavanshi, S. V. & Pop, E. Intrinsic electrical transport and performance projections of synthetic monolayer MoS2 devices. 2D Mater. 4, 011009 (2017).

Sung, C., Song, J., Lee, S. & Hwang, H. Improved endurance of RRAM by optimizing reset bias scheme in 1TIR configuration to suppress reset breakdown. 2016 IEEE Silicon Nanoelectronics Workshop (SNW) https://doi.org/10.1109/SNW.2016.7577996 (IEEE, 2016).

Matsunaga, S. et al. Complementary 5T-4MTJ nonvolatile TCAM cell circuit with phase-selective parallel writing scheme. IEICE Electronics Express 11, 20140297 (2014).

Li, H., Wu, T. F., Mitra, S. & Wong, H.-S. P. Resistive RAM-centric computing: design and modeling methodology. CIEEE Trans. Circuits Syst. I: Reg. Papers 64, 2263–2273 (2017).

Li, H. et al. Device and circuit interaction analysis of stochastic behaviors in cross-point RRAM arrays. IEEE Trans. Electron Devices 64, 4928–4936 (2017).

Cao, Y., Sato, T., Orshansky, M., Sylvester, D. & Hu, C. New paradigm of predictive MOSFET and interconnect modeling for early circuit simulation. Proc. IEEE 2000 Custom Integrated Circuits Conf. (CICC) https://doi.org/10.1109/CICC.2000.852648 (IEEE, 2000).

Ge, R. et al. Atomristor: nonvolatile resistance switching in atomic sheets of transition metal dichalcogenides. Nano Lett. 18, 434–441 (2018).

Acknowledgements

We acknowledge the discussions with T. Phan, A. Tang, Y. Nishi, K. Saraswat and Y. Chai. We acknowledge the support from the Air Force Office of Scientific Research (AFOSR) Multidisciplinary University Research Initiative (MURI) under award FA9550-16-1-0031, the National Science Foundation (NSF) EFRI 2-DARE grant 1542883, the AFOSR grant FA9550-14-1-0251, the Initiative for Nanoscale Materials and Processes (INMP), the Stanford Non-volatile Memory Technology Research Initiative (NMTRI), and Stanford SystemX Alliance. This work was supported in part by ASCENT, one of six centres in JUMP, a Semiconductor Research Corporation (SRC) programme sponsored by DARPA. R.Y. thanks University of Michigan–Shanghai Jiao Tong University Joint Institute at Shanghai Jiao Tong University for their financial support. K.K.H.S. acknowledges partial support from the Stanford Graduate Fellowship programme and the NSF Graduate Research Fellowship (no. DGE-114747). We are grateful to Stanford Nanofabrication Facility (SNF) and Stanford Nano Shared Facilities (SNSF) for providing the equipment for device fabrication and measurements.

Author information

Authors and Affiliations

Contributions

R.Y. and H.-S.P.W. conceived the concept and designed the research. R.Y. performed the fabrication and the electrical measurements of the 2T2R structure. H.L. assisted in the electrical measurement and performed the simulation of the TCAM array. K.K.H.S. performed the CVD growth of MoS2. T.R.K. and K.O. took the TEM images. E.P., J.A.F. and H.-S.P.W. provided feedback on the experiments. R.Y. and H.-S.P.W. wrote the manuscript, with input from E.P. and J.A.F. All authors have discussed the results and given approval to the final version of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Figures 1–11, Supplementary Notes 1–10, and Supplementary Tables 1–2.

Rights and permissions

About this article

Cite this article

Yang, R., Li, H., Smithe, K.K.H. et al. Ternary content-addressable memory with MoS2 transistors for massively parallel data search. Nat Electron 2, 108–114 (2019). https://doi.org/10.1038/s41928-019-0220-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-019-0220-7

This article is cited by

-

Giant tunnelling electroresistance in atomic-scale ferroelectric tunnel junctions

Nature Communications (2024)

-

Demonstration of p-type stack-channel ternary logic device using scalable DNTT patterning process

Nano Convergence (2023)

-

Hybrid 2D–CMOS microchips for memristive applications

Nature (2023)

-

Wurtzite and fluorite ferroelectric materials for electronic memory

Nature Nanotechnology (2023)

-

Monolithic 3D integration of 2D transistors and vertical RRAMs in 1T–4R structure for high-density memory

Nature Communications (2023)