Abstract

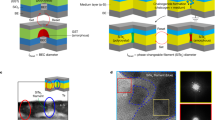

Memristor crossbars offer reconfigurable non-volatile resistance states and could remove the speed and energy efficiency bottleneck in vector-matrix multiplication, a core computing task in signal and image processing. Using such systems to multiply an analogue-voltage-amplitude-vector by an analogue-conductance-matrix at a reasonably large scale has, however, proved challenging due to difficulties in device engineering and array integration. Here we show that reconfigurable memristor crossbars composed of hafnium oxide memristors on top of metal-oxide-semiconductor transistors are capable of analogue vector-matrix multiplication with array sizes of up to 128 × 64 cells. Our output precision (5–8 bits, depending on the array size) is the result of high device yield (99.8%) and the multilevel, stable states of the memristors, while the linear device current–voltage characteristics and low wire resistance between cells leads to high accuracy. With the large memristor crossbars, we demonstrate signal processing, image compression and convolutional filtering, which are expected to be important applications in the development of the Internet of Things (IoT) and edge computing.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

$119.00 per year

only $9.92 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

References

Williams, R. S. What’s next? Comput. Sci. Eng. 19, 7–13 (2017).

Waldrop, M. M. The chips are down for Moore’s law. Nature 530, 144–147 (2016).

Gubbi, J., Buyya, R., Marusic, S. & Palaniswami, M. Internet of Things (IoT): a vision, architectural elements, and future directions. Fut. Gen. Comput. Syst. 29, 1645–1660 (2013).

Yocam, E. W. Evolution on the network edge: intelligent devices. IT Professional 5, 32–36 (2003).

Chua, L. Memristor—the missing circuit element. IEEE Trans. Circuit Theory 18, 507–519 (1971).

Strukov, D. B., Snider, G. S., Stewart, D. R. & Williams, R. S. The missing memristor found. Nature 453, 80–83 (2008).

Yang, J. J., Strukov, D. B. & Stewart, D. R. Memristive devices for computing. Nat. Nanotech. 8, 13–24 (2013).

De Salvo, B. Silicon Non-Volatile Memories: Paths of Innovation (Oxford, Wiley, 2013).

Wong, H.-S. P. et al. Metal–oxide RRAM. Proc. IEEE 100, 1951–1970 (2012).

Ventra, M. D., Pershin, Y. V. & Chua, L. O. Circuit elements with memory: memristors, memcapacitors, and meminductors. Proc. IEEE 97, 1717–1724 (2009).

Truong, S. N. & Min, K.-S. New memristor-based crossbar array architecture with 50% area reduction and 48% power saving for matrix-vector multiplication of analog neuromorphic computing. J. Semicond. Technol. Sci. 14, 356–363 (2014).

Xia, L. et al. Technological exploration of RRAM crossbar array for matrix-vector multiplication. J. Comput. Sci. Technol. 31, 3–19 (2016).

Li, B., Gu, P., Wang, Y. & Yang, H. Exploring the precision limitation for RRAM-based analog approximate computing. IEEE Design Test 33, 51–58 (2016).

Prezioso, M. et al. Training and operation of an integrated neuromorphic network based on metal–oxide memristors. Nature 521, 61–64 (2015).

Yu, S. et al. in Proc. Int. Electron Dev. Meet. 416–419 (San Francisco, IEEE, 2016).

Park, S. et al. Electronic system with memristive synapses for pattern recognition. Sci. Rep. 5, 10123 (2015).

Hu, M. & Strachan, J. P. in Proc. 2016 IEEE Int. Conf. Rebooting Comp. (ICRC) 1–5 (San Diego, IEEE, 2016).

Gao, L., Chen, P.-Y. & Yu, S. Demonstration of convolution kernel operation on resistive cross-point array. IEEE Electron Dev. Lett. 37, 870–873 (2016).

Indiveri, G., Linares-Barranco, B., Legenstein, R., Deligeorgis, G. & Prodromakis, T. Integration of nanoscale memristor synapses in neuromorphic computing architectures. Nanotechnology 24, 384010 (2013).

Park, J. et al. TiOx-based RRAM synapse with 64-levels of conductance and symmetric conductance change by adopting a hybrid pulse scheme for neuromorphic computing. IEEE Electron Dev. Lett. 37, 1559–1562 (2016).

Fumarola, A. et al. in Proc. 2016 IEEE Int. Conf. Rebooting Comp. (ICRC) 1–8 (San Diego, IEEE, 2016).

Ge, N. et al. An efficient analog Hamming distance comparator realized with a unipolar memristor array: a showcase of physical computing. Sci. Rep. 7, 40135 (2017).

Hu, M. et al. in Proc. 53rd Design Automat. Conf. 1–6 (Austin, ACM, 2016).

Gao, L., Alibart, F. & Strukov, D. B. in IEEE/IFIP 20th Int. Conf. VLSI and System-on-Chip, 2012 (VLSI-SoC) 88–93 (Santa Cruz, IEEE, 2012).

Chakrabarti, B. et al. A multiply-add engine with monolithically integrated 3D memristor crossbar/CMOS hybrid circuit. Sci. Rep. 7, 42429 (2017).

Lastras-Montaño, M. A., Chakrabarti, B., Strukov, D. B. & Cheng, K. T. in Design, Automation & Test in Europe Conference & Exhibition (2017) 1257–1260 (Lausanne, IEEE, 2017).

Ma, W. et al. in Proc. Int. Electron Dev. Meet. 436–439 (San Francisco, IEEE, 2016).

Yao, P. et al. Face classification using electronic synapses. Nat. Commun. 8, 15199 (2017).

Sheridan, P. M. et al. Sparse coding with memristor networks. Nat. Nanotech. 12, 784–789 (2017).

Choi, S., Shin, J. H., Lee, J., Sheridan, P. & Lu, W. D. Experimental demonstration of feature extraction and dimensionality reduction using memristor networks. Nano Lett. 17, 3113–3118 (2017).

Jouppi, N. P., Young, C., Patil, N. & Patterson, D. in 44th Int. Symp. Comp. Archit. (ISCA) 1–17 (ACM/IEEE, Toronto, 2017).

LeCun, Y., Bengio, Y. & Hinton, G. Deep learning. Nature 521, 436–444 (2015).

Dally, W. in Neural Information Processing Systems (NIPS2015) Tutorial (NIPS Foundation, Montréal, 2015).

Shafiee, A. et al. in 2016 ACM/IEEE 43rd Int. Symp. Comp. Archit. (ISCA) 14–26 (Seoul, IEEE, 2016).

Hu, M., Li, H., Wu, Q. & Rose, G. S. in 2012 49th ACM/EDAC/IEEE Design Automat. Conf. (DAC) 498–503 (San Francisco, IEEE, 2012).

Jiang, H. et al. Sub-10 nm Ta channel responsible for superior performance of a HfO2 memristor. Sci. Rep. 6, 28525 (2016).

Linn, E., Rosezin, R., Kugeler, C. & Waser, R. Complementary resistive switches for passive nanocrossbar memories. Nat. Mater. 9, 403–406 (2010).

Kim, K. M. et al. Low-power, self-rectifying, and forming-free memristor with an asymmetric programming voltage for a high-density crossbar application. Nano Lett. 16, 6724–6732 (2016).

Li, C. et al. Three-dimensional crossbar arrays of self-rectifying Si/SiO2/Si memristors. Nat. Commun. 8, 15666 (2017).

Midya, R. et al. Anatomy of Ag/Hafnia-based selectors with 1010 nonlinearity. Adv. Mater. 29, 1604457 (2017).

Jo, S. H., Kumar, T., Narayanan, S. & Nazarian, H. Cross-point resistive RAM based on field-assisted superlinear threshold selector. IEEE Trans. Electron Dev. 62, 3477–3481 (2015).

Choi, B. J. et al. Trilayer tunnel selectors for memristor memory cells. Adv. Mater. 28, 356–362 (2016).

Ji, L. et al. Integrated one diode–one resistor architecture in nanopillar SiOx resistive switching memory by nanosphere lithography. Nano Lett. 14, 813–818 (2014).

Van Wees, B. J. et al. Quantized conductance of point contacts in a two-dimensional electron gas. Phys. Rev. Lett. 60, 848–850 (1988).

Yi, W. et al. Quantized conductance coincides with state instability and excess noise in tantalum oxide memristors. Nat. Commun. 7, 11142 (2016).

Rao, K. R. & Yip, P. Discrete Cosine Transform: Algorithms, Advantages, Applications (Cambridge, Academic Press Professional, 1990).

Pennebaker, W. B. & Mitchell, J. L. JPEG: Still Image Data Compression Standard (Berlin, Springer Science & Business Media, 1992).

Malarvizhi, D. & Kuppusamy, D. K. A new entropy encoding algorithm for image compression using DCT. Int. J. Eng. Trends Technol. 3, 327–332 (2012).

Krizhevsky, A., Sutskever, I. & Hinton, G. E. in Advances in Neural Information Processing Systems 25 (NIPS 2012) 1097–1105 (Stateline, NV, NIPS Foundation, 2012).

Lawrence, S., Giles, C. L., Ah Chung, T. & Back, A. D. Face recognition: a convolutional neural-network approach. IEEE Trans. Neural Networks 8, 98–113 (1997).

Hu, M. et al. Memristor-based analog computation and neural network classification with a dot product engine. Adv. Mater. https://doi.org/10.1002/adma.201705914 (in the press).

Acknowledgements

This work was supported in part by the Air Force Research Laboratory (AFRL; grant no. FA8750-15-2-0044), the US Air Force Office for Scientific Research (AFOSR; grant no. FA9550-12-1-0038), the Intelligence Advanced Research Projects Activity (IARPA; contract 2014-14080800008) and the National Science Foundation (NSF; ECCS-1253073). This work was performed in part at the Center for Hierarchical Manufacturing (CHM), an NSF sponsored Nanoscale Science and Engineering Center (NSEC) at University of Massachusetts, Amherst.

Author information

Authors and Affiliations

Contributions

C.L., H.J., N.G., N.D., P.L. and Z.W. built the integrated chips. C.L., M.H., Y.L. and J.P.S. carried out the measurements. E.M., M.H. and J.P.S. built the measurement system. Y.L., M.H. and W.S. performed circuit simulation. J.Z. took the cross-sectional SEM and TEM images. J.P.S., J.J.Y. and Q.X. designed the experiments and supervised the project. Q.X., C.L., J.J.Y. and R.S.W. wrote the manuscript. All authors contributed to analysis of the results and commented on the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Supplementary Information

Supplementary Figures 1–16, Supplementary Table 1, and Supplementary Notes 1–4.

Video

Supplementary Video 1

Programming of the conductance of memristors in a 64 × 64 array to arbitrary values within a pre-defined conductance range.

Supplementary Video 2

Real-time crossbar output with changing input frequencies.

Rights and permissions

About this article

Cite this article

Li, C., Hu, M., Li, Y. et al. Analogue signal and image processing with large memristor crossbars. Nat Electron 1, 52–59 (2018). https://doi.org/10.1038/s41928-017-0002-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-017-0002-z

This article is cited by

-

Photonic neuromorphic architecture for tens-of-task lifelong learning

Light: Science & Applications (2024)

-

Energy efficient photonic memory based on electrically programmable embedded III-V/Si memristors: switches and filters

Communications Engineering (2024)

-

Potential and challenges of computing with molecular materials

Nature Materials (2024)

-

Nanofluidic logic with mechano–ionic memristive switches

Nature Electronics (2024)

-

Memristor-based storage system with convolutional autoencoder-based image compression network

Nature Communications (2024)