Abstract

The continuously intensifying demand for high-performance and miniaturized semiconductor devices has pushed the aggressive downscaling of field-effect transistors (FETs) design. However, the detrimental short-channel effects and the fundamental limit on the sub-threshold swing (SS) in FET have led to a drastic increase in static and dynamic power consumption. The operational limit of nanoscale transistors motivates the exploration of post-CMOS devices like Tunnel FET (TFET), having steeper SS and immunity toward short channel effects. Thus the field of nanoscale 2D-TFET has gained compelling attention in recent times. The nanoscale TFET, with two-dimensional (2D) semiconductor materials, has shown a significant improvement in terms of higher on-state current and lower sub-threshold swing. In this context, the review presented here has comprehensively covered the gradual development and present state-of-arts in the field of nanoscale 2D-TFET design. The relative merits and demerits of each class of 2D materials are identified, which sheds light on the specific design challenges associated with individual 2D materials. Subsequently, the potential device/material co-optimization strategies for the development of efficient TFET designs are highlighted. Next, the experimental development in 2D-TFET design is discussed, and specific synthesis/fabrication challenges for individual material systems are indicated. Finally, an extensive comparative performance study is presented between the simulated as well as experimentally reported potential 2D materials and state-of-the-art bulk material-based TFETs.

Similar content being viewed by others

Introduction

Introduction to TFETs

The ever-increasing demand for miniaturization, operational speed, cost reduction, and diverse functionalities in integrated circuits has been historically sustained through the aggressive downscaling of complementary-metal-oxide-semiconductor (CMOS) field-effect transistors (FET). However, as modern CMOS technology has reached device dimensions well below 100 nm, further downscaling is severely challenged by its high static power dissipation1,2. The higher leakage current and the larger supply voltage in a metal-oxide-semiconductor field-effect transistor (MOSFET) cumulatively contribute to this high power dissipation1. In such nanoscale MOSFETs, the higher leakage current results from compromising the electrostatic integrity of the device, known as short channel effects (SCEs), which can be minimized to some extent through innovative device design3,4. On the other side, the application of a larger supply voltage is necessary to maintain a high drive current and, thereby, a higher speed of operation. In order to scale down the supply voltage of MOSFET without hindering its performance, a fast transition between the off-state and on-state conditions is required, i.e., its sub-threshold swing (SS) should be as small as possible. However, the minimum SS of MOSFET is restricted by its fundamental limit of 60 mV per decade at room temperature, which is sizably larger for practical nanoscale MOSFETs2. These limitations in the existing nanoscale MOSFET devices have motivated the exploration of alternative FET devices that can exhibit extremely small SS. The tunneling field-effect transistor (TFET) has emerged as an alternative to nanoscale MOSFET. In TFET design, it is possible to achieve SS below 60 mV per decade due to their unique carrier injection mechanism, i.e., band-to-band tunneling (BTBT) of electrons2,3,4,5. At the same time, the TFET is effectively immune to device downscaling and can retain a minimal leakage current in the nanoscale device dimensions. However, the BTBT-dominated carrier transport in TFET leads to an on-state current (Ion), usually a few orders of magnitude smaller than the conventional MOSFETs. It should be noted that both SS and Ion of TFET are determined by the probability of BTBT, which is strongly dependent on the device’s electrostatics and semiconductor material properties2. Thus, the device design and materials for TFET are of paramount importance to practically achieve extremely small SS and acceptable Ion. Consequently, over the last decade, ever-increasing research activities have been observed on TFET that paved the path to comprehensive theoretical and design-level understanding. This leads to the development of a variety of performance-boosting strategies for TFETs, and the choice of semiconductor material has always remained one of the key concerns for such approaches.

Introduction to 2D Materials

After the successful synthesis of Graphene in 2004, remarkable progress in research in the area of thin two-dimensional (2D) semiconducting materials with one or few atomic layer thicknesses has been observed. This leads to the ever-expanding family of 2D materials and hitherto undiscovered physical phenomena attributed to prominent quantum mechanical effects, reduced screening, and increased correlations in such materials. Specifically, the 2D materials exhibit remarkable electronic, optical, and magnetic properties distinctly different from their three-dimensional (3D) bulk counterparts6,7. At the same time, the rapidly maturing synthesis techniques allow the uniform and controlled deposition of high-quality atomically thin layers of 2D materials on different substrates7. Equally, substantial progress has been observed in the relevant theoretical works based on the computational material science approach, leading to a profound understanding of the essential physics of such 2D materials. In this line, the ab initio or first principle calculations based on density functional theory (DFT) are emerged to be a crucial technique in exploring and analyzing the properties of 2D materials and their correlation with different external influences, which satisfactorily complementing the current experimental observations8,9,10. All these factors contributed to the successful demonstrations of 2D materials-based electronic, optoelectronic, and spintronic devices that often exhibit notable performance improvements over the bulk materials6,7.

Introduction to 2D TFETs

The 2D crystalline semiconductors are being actively studied as a channel material for the Field Effect Transistors (FETs). The typical advantages of such 2D-transistors include excellent electrostatic control of the gate terminal due to the significantly larger surface-to-volume ratio, higher electrical conductivity due to ballistic/ quasi-ballistic transport, and pristine surfaces that ensure superior interface quality with the insulators. It also provides the layer and stacking-dependent tunable electronic properties that offer additional flexibility for the transistor design1,11. These unique attributes present an opportunity to introduce 2D materials for TFET design that can simultaneously incorporate the advantages of superior electrostatic integrity and tunneling barrier engineering. Hence, the field of 2D materials-based TFET design has substantially grown in the recent past. Specifically, the 2D-TFETs are being considered the promising candidate for the nanoscale device dimensions where the channel lengths are typically ≤40 nm, leading to ballistic/quasi-ballistic carrier transport in the channel. This results in significantly different device physics and demanded unique design considerations for such nanoscale 2D-TFETs.

Motivations of the review

Due to the diversities in the electronic properties of various 2D semiconductors, significant development has been observed toward device/material co-optimization involving different innovative device design strategies and material engineering techniques for nanoscale 2D-TFETs. It is worth mentioning that theoretical/simulation-based investigations remain the driving factor for such development. However, only a limited number of literature has addressed the development of nanoscale 2D TFETs1,2,5,12,13,14. No exclusive reviews are available on this topic to the best of the author’s knowledge.

Therefore, the current review presents a comprehensive account of the development of 2D materials-based nanoscale TFETs. All of the discussions are based on n-channel operational modes of the TFETs. However, the theoretical concepts and design strategies discussed are generic and can also be applicable to p-channel operational modes of the devices.

Organization of the review

The present review is organized as follows:

In section Tunnel FET–A General Overview, a general understanding of TFETs is developed, emphasizing the underlying physics and working principle of the device. Subsequently, the relevant design parameters of TFET are identified and correlated with 2D material systems. Section 2D Materials for Tunnel Fet Design discusses the material properties of the individual 2D semiconductor material and their Van der Waals (vdW) heterostructure, followed by the systematic exploration of different nanoscale TFET design strategies for particular 2D materials. The recent progress in material/device co-design techniques for different 2D semiconductors is highlighted in this context. Section Experimental Realization of 2D-TFET–Challenges and Opportunity presents a comprehensive account of experimental developments in 2D-TFET design, emphasizing the specific fabrication/synthesis challenges associated with individual material systems. Section Comparative Performance Analysis provides a detailed comparative performance analysis of the different 2D semiconductors-based nanoscale TFETs. The performances of potential nanoscale 2D TFETs are benchmarked with their 3D counterparts. Furthermore, the numerical device simulation-based performance of nanoscale 2D TFETs is analyzed in the context of experimentally reported performance for diffusive transport-dominated 2D-TFETs. Finally, the present status and future scope of this domain are indicated.

Tunnel FET- a general overview

Sub-threshold physics of FET devices

The steepness of transition from off-state to on-state in any field effect transistor device can be assessed using the sub-threshold swing (SS) i.e. the minimum applied gate bias required to increase the sub-threshold current by one order of magnitude, which is defined as2:

Where VGS is applied gate bias, ψS is surface potential, ID is drain current. In the RHS of Eq.1, the first term (\(d\left[ {V_{GS}} \right]/d\left[ {\psi _S} \right]\)) is determined by the device electrostatics, whereas the second term (\(d[\psi _S]/d[Log(I_D)]\)) is governed by the sub-threshold carrier transport mechanism of the device2.

The carrier injection mechanism in MOSFET is dominated by thermionic emission. The electrons at the source region having higher energy than the gate-controlled electrostatic potential barrier can be injected into the channel and reach the drain region under the influence of an applied electric field (Fig. 1a)11. However, in the sub-threshold regime, the number of available electrons in the source is restricted by the high energy tail of Fermi-Dirac distribution in the conduction band, which ultimately limits the SS value of the device.

Consequently, for an ideal conventional MOSFET design, the minimum SS that can be achieved is 60 mV per decade (thermal limit) at room temperature. As in this case, the RHS in Eq. 1 becomes:

Where K is the Boltzmann constant, T is the temperature (in Kelvin), and q is the charge of an electron.

In the nanoscale device dimension of MOSFETs, the capacitive coupling of drain terminal over source/channel potential barrier considerably degrades the channel electrostatics, where Eq. 2a evaluates a value significantly larger than one. Subsequently, a typical SS value of around 100 mV per decade is usually observed in well-design nanoscale MOSFETs1. This suggests that for achieving a sub-thermal SS, the conventional MOSFET may be replaced by a new FET device, where subthreshold conduction is governed by a different carrier transport mechanism rather than the thermionic injection potentially bringing down the value of Eq. 2b below 60 mV per decade at T = 300 K.

In this context, TFET is considered a potential alternative to the MOSFET, where the electrons are injected from the valance band of the source to the conduction band of the channel by quantum mechanical tunneling (Fig. 1b)1,2. The BTBT mechanism in TFET leads to distinctly different current-voltage (I–V) characteristics compared to its conventional MOSFET counterpart (Fig. 1c). Typically, a well-designed TFET can demonstrate a significantly larger on-state/off-state current ratio and SS bellow-60 mV per decade at room temperature (Fig. 1c)2. For an efficient design of TFET, the tunneling barrier should be carefully engineered to simultaneously ensure a strong BTBT and superior gate control over BTBT in the tunneling junction.

It is worth mentioning that for direct BTBT, i.e., when the VBM of the source lies at the same crystal momentum as the CBM of the channel, the tunneling probability is higher than that of indirect BTBT. For indirect BTBT, the difference in crystal momentum of the electrons between valance band maxima and conduction band minima is mitigated through the emission or absorption of photons, i.e., quanta of lattice vibrations, limiting the overall tunneling probability. Hence, direct bandgap semiconductors with suitable bandgaps are preferred over indirect bandgap semiconductors for the design of TFETs. Also, unless the channel length is comparable with λ, the tunneling probability is marginally influenced by drain bias2. As a result, unlike conventional MOSFETs, TFETs exhibit higher immunity toward scaling-induced performance degradation. This establishes TFETs as a highly promising alternative to conventional MOSFETs in nanoscale device dimensions.

BTBT in TFETs

In TFET, the potential barrier in the tunneling junction can be approximated as a triangular potential barrier. The wave-like nature of electrons allows evanescent states to have lower energy than the potential barrier, which can quantum mechanically tunnel through the barrier (Fig. 2). Several theoretical frameworks have been developed to estimate the tunneling probability through such triangular barriers, which are extensively reviewed elsewhere14. The Wentzel–Kramer–Brillouin (WKB) approach has been widely considered the most appropriate for calculating BTBT in TFET15. The original work of WKB and its detailed theoretical development are available in standard textbooks and research articles16,17,18. In TFET, the tunneling probability (TWKB), i.e., the likelihood of an electron to transmit by tunneling from the source to the channel, can be calculated using the WKB approximation as follows2:

Where \(m_t^ \ast\) is tunneling mass, Eg is energy bandgap, \(\hbar\) is reduced plank constant, q is the electronic charge, ΔΦ is the energy difference between the source valance band maxima (VBM) and channel conduction band minima (CBM), i.e. energy window of tunneling, and λ is the effective screening length that represents the spatial extent of the energy band bending at the tunneling junction (Fig. 2)2. It should be noted that the minimum tunneling distance WTun for electrons tunneling from source to channel is smaller than λ, and at the same time, strongly depends on the λ. The gate control over the tunneling probability (TWKB) can be appreciated from the fact that the increasing gate bias reduces λ and simultaneously increases ΔΦ.

Sub-threshold physics of TFETs

The tunneling probability demonstrates a super-exponential dependence on gate bias, as indicated by Eq. 3. At the same time, due to the presence of an energy band gap above the VBM, the available electrons at the valance band of the source are not limited by the tail of Fermi-Dirac distribution. Thus, both factors can lead to a SS value smaller than 60 mV per decade in TFET.

However, a detailed analysis of SS is required to identify the design criteria of TFETs with sub-thermal (<60 mV per decade) SS. In this context, in the sub-threshold regime of operation, the following approximations can be invoked for nanoscale TFET19:

-

1.

Double gated n-channel TFET structure with an intrinsic channel, which is usually considered for nanoscale TFET design.

-

2.

Landauer’s formalism for current conduction under ballistic/ quasi-ballistic transport regime, which is a valid consideration for nanoscale TFET.

-

3.

Constant Tunneling probability (TWKB) within tunneling energy window (Δφ), which is valid for BTBT over a range of small Δφ (in the order of a few KT) and essentially correspond to the sub-threshold regime of operation in TFETs.

-

4.

The contributions from the drain-terminal Fermi-Dirac distribution function are negligible compared to the source-terminal Fermi-Dirac distribution function within the tunneling energy window (Δφ), as the drain to source potential difference of nanoscale TFET is usually sufficiently large (>0.1 V) to maintain this condition.

-

5.

The minimum tunneling length is defined from the electrostatic potential profile around the tunnel junction following One-dimensional Poisson’s equations under Yan’s parabolic approximation19 and Kane’s two-band model19, which is a well-established modeling approach for TFET.

A detailed description of the abovementioned approximation can be found in19. Furthermore, these approximations lead to a simplified representation of the SS of the nanoscale TFET, which can be defined as19:

Where, [SS]T and [SS]FD are defined as follows19:

Where EVS is the valance band maxima at the source region, EFS is the Fermi-level (electrochemical potential) of the source region, WTun is the minimum tunneling length, and the term α is defined as:

Where the relative separation between the EVS and EFS is determined by the source doping concentrationNA, i.e. (EVS−EFS) increases with NA.

Equations 4–7 offers a reliable description of SS of TFET at subthreshold biasing conditions for both nanoscale bulk material and 2D material-based TFETs19.

Careful observation reveals that at the onset of tunneling (ΔΦ ~ 0), the SS is determined by [SS]FD, which tends to attend a near-zero value. However, the current at the onset of tunneling is usually dominated by non-BTBT current components, including reverse saturation currents and trap-assisted tunneling (TAT) current. Therefore, the overall subthreshold characteristics of the TFET are usually determined by the SS value for a finite tunneling window (ΔΦ ~ few KT), where [SS]T effectively determines the minimum SS19.

Since the inception of TFET, the exploration of efficient device design strategies based on the device electrostatics and carrier transport mechanism remain at the forefront of TFET research. Typically, any efficient TFET design must simultaneously increase Ion and reduce SS over a few orders of magnitude range of sub-threshold currents.

For a high Ion, the tunneling probability should be as close to unity as possible for a small applied gate bias. Hence, Eq. 3 implies that such requirement can be addressed through minimization of \(m_t^ \ast\), Eg and λ. A smaller effective screening length (λ) represents superior gate control over tunneling junction electrostatics. Typically, λ can be reduced by reducing gate insulator and channel thicknesses and incorporating high-k gate insulators19. At the same time, increasing NA leads to a steeper band bending and subsequently reduce λ. The tunneling mass (\(m_t^ \ast\)) depends on the effective masses in the valance band (\(m_v^ \ast\)) and conduction band (\(m_c^ \ast\)) of the source and channel materials, respectively. In contrast, the energy bandgap (Eg) depends upon the choice of the source material.

However, a careful analysis of Eqs. 3–5 reveals that achieving a smaller SS often contradicts the requirements for a larger Ion. Typically, the reduction in Eg and \(m_t^ \ast\) leads to improvement in TWKB and thereby Ion, whereas the same tends to degrade the SS (through [SS]T). On the other hand, both increasing NA and reducing λ, eventually reduces WTun and increase TWKB. However, the reduced WTun implies a larger band bending at the channel, which induces strong electrostatic screening effects and ultimately limits the rate of change in WTun with ΔΦ and thereby degrades the SS (through [SS]T) of the TFET. In essence, the completing influences of electrostatic and material parameters on Ion and SS suggest the requirements of the careful tradeoff between Ion and SS for TFET through suitable device/material co-design strategies. Therefore, the TFET designs generally focus on the tunneling junction doping profiles, gate-stacking specifications, and the choice of semiconductors with desirable effective masses and energy bandgap at the different regions of the device.

In this context, it is worth mentioning that apart from SS degradation, any arbitrarily small effective masses and energy bandgap are even further counterproductive for TFET design. The smaller effective masses lead to a smaller density of states (DOS) in conduction and valance bands. Subsequently, for significantly smaller effective masses, the lack of available electronic states for tunneling may degrade the Ion/Ioff ratio of TFET. On the other hand, an extremely small energy bandgap at the source leads to a sizeable reverse saturation current, which degrades the off-state current (Ioff) and thereby the entire subthreshold characteristics of the TFET

Performance optimization of TFETs

The performance optimization strategies for TFET can be broadly categorized into two approaches: material engineering and device design strategies. The material engineering strategies attempt to tune the tunneling barrier height (as well as width) and tunneling masses by carefully choosing the materials in the source and channel regions. In this line, both homogeneous and heterogeneous tunneling junctions are proposed for TFET design. Among homogenous TFETs, the lower indirect bandgap semiconductors like- Ge20, SixGe1-x21,22, Strained-Ge23,24, as well as lower direct bandgap semiconductors like- InAs25, InxGa1-xAs26, GexSn1-x27 exhibited notable improvements over the conventional Si TFET. Whereas a wide variety of semiconductor hetero-junctions are adopted for TFET design that usually incorporates heterostructure with both type-2 and type-3 band offset at the tunneling junctions. The type-2 heterostructure exploits the tunneling-junction band alignments to achieve a lower on-set of BTBT. The promising type-2 heterostructure for TFET design include SiGe/Si28, Ge/Si23, GeSn/ Ge28,29, GeSn/SiGeSn30, InGaAs/Ge31, InAs/Si32, and InAs/InGaAs33. The type-3 heterostructure incorporates a broken bandgap in the tunneling junction to achieve a minimal tunneling barrier width. Such heterostructure include InGaAs/GaAsSb34, InAs/GaSb35, InAs/GaAsSb/GaSb36, InGaAs/InP37 AlGaSb/InAs38, InGaN/InN39. For both type-2 and type-3 heterostructure, the lower bandgap material is considered for the source region, leading to smaller tunneling barrier height (width) and thereby higher BTBT. Also, a relatively larger bandgap of the channel material limits the ambipolar BTBT component from channel to drain region and keeps the off-state current as low as possible.

The device design strategies are focused on enhancing gate control over tunneling junction electrostatics. Significant performance improvements in TFET have been achieved by tuning the tunneling barrier width with the introduction of dual gate-metal40,41, dual gate-insulator42,43, channel pocket engineering44,45, charge-plasma-based electrical doping46,47 nanotube architecture48 and nanowire architecture49,50. One of the most notable design strategies for TFET involves aligning the tunneling direction parallel to the applied gate electric field and realizing a significant enhancement in gate control over BTBT. This strategy usually involves either gate overlapping source structure with vertical source pocket engineering51,52,53 or forming the electron-hole bilayer in the channel through asymmetric gate engineering54,55. However, a detailed account of the different device design and material engineering strategies for the conventional three-dimensional (3D) material-based TFETs is out of this review’s scope, and these aspects are already comprehensively reviewed elsewhere2. Apart from these innovative structural/material design strategies, the electrostatic integrity of the TFET is highly influenced by its general device specification, i.e., source doping, the abruptness of source/channel junction, channel thickness, and effective oxide thickness of gate insulator. Specifically, an ultra-thin body device leads to superior gate control over BTBT, thereby larger Ion and smaller SS in TFETs. However, the reduction of thickness in conventional three-dimensional (3D) materials leads to the increasing energy bandgap (tunneling barrier height) due to size quantization. Consequently, the mobile charge centroid shifts from the surface, weakening the gate capacitive coupling. This may ultimately limit the device performance of ultra-thin body TFET architectures. In this context, the one or few atomic layer thick 2D semiconductors offer a unique solution for efficient TFET design, which preserves the superior electrostatic integrity and, at the same time, does not suffer from the drawbacks mentioned above for 3D materials in ultra-thin body device architectures.

2D materials for tunnel fet design

Generic properties of 2D materials

The layered materials exhibit crystalline planner structures. In such materials, the atoms are held together by a strong covalent bond in the in-plane direction. In contrast, the atoms experience weak Van der Waals attraction force in the out-of-plane directions. This allows the separation of a single or few atomic layers from their respective bulk configuration without significantly affecting the in-plane structure. These isolated atomic layers have no periodicity in out-of-plane direction and are commonly referred to as 2D materials6,10,56. The energy and crystal wave vector (E-k) dispersion relation of the layered materials distinctly differs in their monolayer, few layers, and bulk configuration forms.

Consequently, the 2D materials exhibit distinguishable and layer-dependent electronic properties that can be further tuned by applying an electric field, magnetic field, and strain. However, the electronic properties and their response to external influences significantly vary from one 2D material to another. Therefore, the suitability of a specific 2D material differs from one technological application to another.

The crystalline 2D semiconductors have specific energy bandgaps with few atomic layer thicknesses. The charge carriers are naturally confined within an ultra-thin body, allowing the applied gate bias to influence their electrostatic conditions uniformly57. The absence of chemical bonding between the layers of 2D semiconductors offers pristine interfaces that do not suffer from channel mobility degradation due to dangling bonds and interface states11. Furthermore, using 2D semiconductors with desirable material properties (bandgap, effective mass), it is possible to design high-performance TFETs with large Ion and extremely small SS. Moreover, atomically thin 2D semiconductors do not suffer from thickness fluctuation and subsequent band edges smearing effect, facilitating a sharper on-set of BTBT57.

The solid solubility limit limits the substitutional doping in 3D semiconductors, which restricts the maximum internal electric field in the device. Whereas doping in 2D semiconductors is achieved by either charge transfer or electrostatic induction. Subsequently, a larger mobile charge density and thereby a larger internal electric field can be achieved in 2D semiconductors1,58. It should be further noted that most of the structural optimization strategies for 3D-TFETs are equally applicable for 2D-TFETs. Due to this design compatibility, a wide variety of 2D semiconductors found their applications in TFET design over the years. To date, few of these 2D materials-based TFETs have been fabricated, usually having channel lengths of a few hundred nanometers to a few micrometers and, therefore, cannot be considered nanoscale TFET design. In contrast, the sustained development in multiscale simulations allows reliable predictions of electrical characteristics of nanoscale TFET devices operating in ballistic or quasi-ballistic transport regimes19,59,60.

Nanoscale 2D TFETs design

Developing a detailed understanding of the potential of any 2D material for nanoscale TFET design requires an extensive assessment of its properties at different length scales. In this context, the multiscale simulation is evolving as an indispensable strategy for the analysis, design, and performance estimation of 2D material-based nanoscale TFETs. The multiscale simulation strategy bridges through different length scales because it is not necessary to treat individual interaction in an atomistic length scale, as certain microscopic parameters are averaged out and can be represented by macroscopic properties in nanoscale TFETs. The most fundamental description of any material system can be sought from the first principle or ab-initio calculations based on density functional theory (DFT). The DFT simulation provides a reliable description of the energy dispersion (E-k) relations of a 2D material or its structurally/chemically modified variants. This is followed by the extraction of relevant electronic properties, including energy band-gap, effective mass, work-function, electron affinity, and scattering rates which can be utilized to describe the 2D material in a multiscale simulation framework61.

However, for DFT simulation, the computational cost (time and resource) rapidly increases with the number of atoms in the material system. Consequently, it becomes impractical to approach 2D material systems larger than a few hundred atoms using the DFT framework. This limitation is addressed by describing the 2D material system in terms of the material Hamiltonian using a tight-binding approximation that takes into account interactions between neighboring atoms in the lattice and is defined in the atomic orbital basis set60. A set of fitting parameters are defined for the tight-binding Hamiltonian, and the atomic basis set is carefully chosen to ensure that the DFT simulated E-k dispersion relationship of the 2D material can be accurately reproduced near the band edges. This allows efficient computation of the electronic and transport properties like the local density of states and transmission spectrum of a larger 2D material system without inviting the complexity associated with its complete atomistic description61.

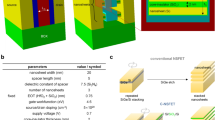

After constructing the material Hamiltonian, the numerical device simulations for nanoscale 2D-TFETs involve the complete quantum mechanical treatment of electronic transport (Fig. 3). This is usually accomplished by using the framework of non-equilibrium Green’s function (NEGF) formalism19. Together with the material Hamiltonian definition and subsequent calibration with DFT simulated energy band structure, the NEGF transport formalism offers a reliable multiscale simulation framework for designing and modeling nanoscale TFETs operating in ballistic/quasi-ballistic regime of operation. It is worth mentioning that apart from MATLAB-based in-house simulators developed by different research groups, the Nano TCAD ViDES62 and OMEN63 are the most commonly available numerical device simulation packages that implement NEGF transport formalism. Furthermore, these packages offer the flexibility of incorporating the user-defined material Hamiltonians, as well as compatibility with different first principle calculation packages, including Quantum Espresso64, Quantum ATK65, VASP66, SIESTA67, and AB-INIT68.

The 2D semiconductors are classified into different families based on the structural similarities between the members of individual families, and the gradual developments in TFET design for each of these families are also comprehensively reviewed in this article. However, the review only considered the TFET structures operating on the principle of BTBT. Subsequently, some 2D material heterostructure used for designing a so-called tunneling transistor that does not operate on the principle of BTBT and is thereby fundamentally limited in achieving SS below 60 mV/decade has not been considered in this review. Finally, the review presented in this article is comprehensively focused on the simulation-based works, which almost entirely contributed the existing literature on 2D material-based nanoscale TFET design.

TFETs based on graphene family

The single layer of Graphite or Graphene is often termed the original 2D material, which is also the first 2D material to be realized. In Graphene, the carbon atoms are arranged in a hexagonal honeycomb structure with a thickness of precisely one atomic layer (Fig. 4). Each carbon atom forms three sp2 bonds with its nearest neighbors, whereas the out-of-plane pz orbitals overlap and form π-bonds. Correspondingly, the delocalized electrons in π-bands and π*-bands determine the electronic properties of the valance band and conduction band of Graphene, respectively. Furthermore, the sp2 hybridization and subsequent π-bonds formation offer a high degree of in-plane stability and perfectly flat layers of atoms for Graphene.

The Graphene exhibits a semi-metallic nature as the conduction band minima (CBM), and valance band maxima (VBM) touch each other at the Dirac point of the Brillouin zone (Fig. 4). The linear dispersion relation near the Dirac point indicates that the electrons behave like mass-less quasi-relativistic particles traveling with a velocity close to the speed of light. This leads to Graphene’s extremely high charge carrier mobility56,69. However, the absence of an energy bandgap in Graphene restricts its application for TFET design, as the large difference between the off-state and on-state current necessary for switching application cannot be achieved in Graphene (Gr) TFETs70,71. Consequently, different material engineering strategies have been proposed to open small energy bandgaps in Graphene by breaking the symmetries of the honeycomb lattice structure.

Similar to monolayer Gr, the 2L-Gr exhibits a zero bandgap, i.e., the CBM and VBM touch each other at the Dirac point. However, the lattice symmetry of 2L-Gr breaks under the applied transverse (vertical) electric field, and the dispersion relation gets modified such that a finite bandgap is observed (Fig. 5a).

This fact is exploited in designing double-gated 2L-Gr TFETs with two independent gate terminals that partially overlap with source and drain regions. In this structure, the difference between applied biases in the separate gates leads to the bandgap opening in the channel as well as gate-overlapped source and drain regions (Fig. 5b). Accordingly, the entire gated structure acts as TFET. The difference in applied biases in independent gates determines the electric field in the vertical direction and the magnitude of the bandgap opening. This offers additional flexibility for tuning the electrical characteristics of 2L-Gr-TFET (Fig. 5c)72.

The bandgap opening in 2L-Gr-TFET can be further facilitated through selective doping by charge transfer from physisorbed tetrafluorotetracyano-quinodimethane (F4TCNQ) on the top layer of 2L-Gr. The subsequent charge asymmetry between the two layers enhances the bandgap opening under the applied transverse electric field. In such structures, the source and drain doping can be realized by work-function engineering of metal electrodes of these regions, which suitably shifts the position of the Fermi level with respect to CBM and VBM (Fig. 6a). Subsequently, a large on-state/off-state current ratio can be achieved at a relatively smaller difference between the applied gate biases (Fig. 6b)73.

The 2L-Gr demonstrates a unique feature in its density of states (DOS) near CBM and VBM, referred to as the van Hove singularities. The dispersion relation of 2L-Gr under applied transverse electric field assumes a “Mexican hat” feature (Fig. 7a), and the electrons and holes are located in a ring in crystal-momentum space near the band edges, unlike the point in such space for parabolic dispersion relations (Fig. 7b). Such feature can be effectively utilized in favor of BTBT considering the fact that after alignment of CBM of the channel with VBM of source, a large overlap in DOS can be observed. However, such characteristics usually get smeared by the band-tailing effect in the presence of dopants and charged impurities. Subsequently, 2L-Gr TFET with unaffected van Hove singularities can be realized by using pristine 2L-Gr with electrostatic doping. The introduction of top gates over the source and drain regions with suitably applied biases induce large hole and electron densities, respectively (Fig. 7c). Correspondingly, such 2L-Gr TFET exhibits an abrupt increase in electronic states for tunneling, leading to an ultra-low SS (Fig. 7d)74.

a Plots of “Mexican hat” feature in E-p dispersion relation and subsequent density of states profiles near CBM and VBM of 2L-Gr, b electronic states distribution (highlighted in red) under CBM and VBM overlap during BTBT in Gr-Bl, and parabolic band semiconductors c schematics and d transfer characteristics of electrostatically doped 2l-Gr TFET, adapted with permission from74. Copyright (2016) Nature.

The crystal symmetry of Graphene can be broken by introducing substrate-induced potential that leads to a finite bandgap opening. This fact is exploited in favor of TFET design by depositing the Graphene on either the Silicon-terminated face of Silicon Carbide (SiC) substrates75 or 2D hexagonal Boron Nitride (hBN) substrates76. Typically, the close structural compatibility of hBN with Graphene leads to high carrier mobility with suitable bandgap opening for TFET design. Furthermore, the BTBT component of Graphene on hBN (Gr-hBN) TFET is considerably influenced by the relative stacking orientation and interlayer spacing between the Graphene and hBN76.

An alternative approach for bandgap engineering in Graphene involves quantum confinement of charge carrier across the width of Graphene that results in a quasi-one-dimensional strip-like structure known as Graphene nanoribbon (GrNR). The Graphene-like monolayer honeycomb structures of Silicon and Germanium are known as Silicene and Germanene, respectively, which also exhibit semi-metallic natures (Fig. 8). However, the relatively larger ionic radius in Silicene and Germanene are favorable to sp3 hybridization, and subsequently, a mixed in-plane sp2-sp3 bonding is observed in these cases. This leads to the low-buckled structure where sub-lattices are slightly shifted vertically with respect to each other (Fig. 8)56.

Similar to GrNR, the Silicene nanoribbon (SiNR) and Germanene nanoribbon (GeNR) have also drawn considerable interest for their structurally tunable electronic properties. However, the electronic properties of such nanoribbons (NRs) strongly depend upon their edge configuration and edge chemistry, i.e. specific atom/group used to saturate uncompensated bonds of edge atoms. These NR exhibits semiconducting properties in their armchair edge configuration. Furthermore, based on the number of atoms across the width direction, this armchair NRs can be characterized into three families having distinct electronic properties, namely 3 m, (3 m + 1), and (3 m + 2), where m is an integer. However, in each of these families, the bandgap of armchair NR inversely varies with its width77. In general, the performance of these NR-TFETs is found to be strongly dependent on NR width. A suitable bandgap for NR must be considered to achieve larger on-state BTBT at the Source/Channel junction while keeping the off-state ambipolar BTBT component at the Channel/Drain junction as low as possible.

The ambipolar BTBT-dependent leakage current is found to pose a considerable challenge to reliable operations of GrNR-TFET78. The ambipolar component can be partially mitigated by introducing a lightly-doped drain region in GrNR-TFET79. However, this problem can be more effectively addressed through a hetero-junction GrNR-TFET design that incorporates a relatively wider GrNR width in the tunneling junction (Fig. 9a). The subsequent smaller bandgap at this region has significantly improved the on-state BTBT in the Source/Channel junction, whereas the larger bandgap for the rest of the channel restricts the ambipolar BTBT in Channel/Drain junction (Fig. 9b). Consequently, in hetero-junction GrNR-TFET, a significantly larger Ion can be achieved without affecting the on-state/off-state current ratio compared to uniform width GrNR-TFET structure (Fig. 9c). However, the full potential of such hetero-junctions engineering is usually hindered by the presence of a large conduction band offset in the tunneling junction. This leads to the quantum well formation and quantization of conduction band energy states in the tunneling region of the channel (Fig. 9d). The discrete energy states pin the electrostatics potential in the tunneling junction, degrading the gate control over the BTBT component80.

Schematics of a uniform and b hetero-structure GrNR-TFET and subsequent c lateral band-profiles at on-state, d drive current as a function of on-state/off-state current ratio, adapted with permission from80. Copyright (2010) IEEE.

The relative band alignment and the conduction band offset at the tunneling junction depends on the gate electrode work function. Therefore, the height of the quantum well can be reduced by introducing a dual metal gate architecture with a higher work-function metal gate over the tunneling junction. This diminishes the energy quantization in the tunneling region and subsequently improves the gate control over the BTBT component of the hetero-junction GrNR-TFET81. An alternative strategy for inducing low bandgap in tunneling junction involves selective edge saturation of GrNR. The saturation of Carbon atoms at the edge of GrNR using a Hydrogen (H) atom and a hydroxyl (OH) group leads to an increase and reduction in energy bandgap, respectively. Thus, a relatively smaller bandgap can be achieved by saturating the source and neighboring channel with the OH group at the source/channel junction. At the same time, a larger bandgap at the channel/drain region can be achieved by saturating the drain and neighboring channel with the H atom (Fig. 10a, b). Thus, both Ion and Ion/Ioff can be improved in such selective edge saturated GrNR-TFET (Fig. 10c), and the overall performance can be further optimized by carefully tuning the length of the OH-saturated (tunneling) region of the channel (Fig. 10d)82. However, simple design strategies like asymmetrically doped source/drain structures83 and pocket doped channel regions84 are also reasonably effective in suppressing the ambipolar BTBT and improving the overall performance of GrNR-TFET.

a Schematic of selective edge saturated gate hetero-structure GrNR-TFET and subsequent b lateral band-profiles at on-state and off-state, c transfer characteristics d performance optimization with tunneling region length, adapted with permission from82. Copyright (2017) IEEE.

Few reports attempted to assimilate the advantages of GrNR with other bandgap engineering strategies of Graphene for TFET design. Consequently, the 2L-GrNR-TFET allows the tuning of bandgap based on the width of 2L-GrNR and the application of asymmetric gate bias85,86. A similar dual bandgap tuning approach has also been adopted in GrNR-on-hBN TFET design87.

At this point, it should be noted that the design strategies discussed for GrNR are generic and can be adopted for SiNR and GeNR as well. However, the relatively larger bond lengths of SiNR/GeNR lead to smaller bandgaps compared to that of GrNR for the same NR widths77. Correspondingly, a relatively smaller bandgap sensitivity can be observed on the widths of SiNR and GeNR. At the same time, for similar bandgaps, the GrNR exhibits smaller effective masses compared to that of SiNR and GeNR77. All of these factors need to be carefully considered for the design and performance optimization of SiNR- and GeNR- TFETs. In this line, different groups have reported TFETs based on SiNR88 and GeNR89. However, compared to GrNR, the SiNR and GeNR are yet to be sufficiently explored for TFET design.

In this context, it should be noted that very narrow and uniform widths are usually required in these NRs to achieve an energy bandgap suitable for TFET operation. At the same time, the bandgaps remain highly sensitive to edge configuration and edge chemistry of NRs. These impose a significant challenge in the lithography and patterning requirements for realizing uniformly thin NR geometry without the deleterious edge effects.

TFETs based on transition metal di-chalcogenides

The transition metal di-chalcogenide (TMD) are represented as MX2, where one transition metal atom, M (Mo, W, Zr, Hf) is covalently sandwiched between two chalcogen atoms, X (S, Se, Te), and is arranged in the hexagonal honeycomb structure within a single atomic layer (Fig. 11a, b). The electronic properties of TMDs are highly sensitive to their phase. Subsequently, the VIB MX2 (M = Mo, W and X = S, Se, Te) exhibits natural bandgaps in 2H-phase, whereas IVB- MX2 (M = Zr, Hf and X = S, Se) shows natural bandgaps in 1T-phase6,10. In general, the energy bandgaps of TMDs gradually increase with reducing layer numbers due to the increasing quantum confinement of charged carriers10. The VIB MX2 shows an indirect to direct bandgap transition in their monolayer configurations (Fig. 11a). However, the IVB MX2 remains an indirect bandgap semiconductor at all layer thicknesses (Fig. 11b)56.

The TFETs designs using homogenous monolayers of different VIB MX2 have been studied, and it has been observed that the direct BTBT in these homogenous monolayers can be exploited to achieve small SS with an acceptable Ion90. However, the choice of a specific VIB MX2 monolayer is very important for the design of such nanoscale TFETs (Fig. 12a). Typically, the smaller energy bandgap and effective masses of WTe2 are found to be most suitable for TFET design91,92,93. However, the lack of stability of WTe2 in its 2H phase is a major concern for the physical realization of WTe2-TFET94. In this context, the TFET using WSe2 outperforms the other monolayer VIB MX2-based TFETs except for WTe2 (Fig. 12b). It has been observed that WSe2 possesses a moderate direct bandgap, smaller effective masses, and a smaller dielectric constant95. Such dielectric constant leads to a smaller effective screening length and thereby superior gate control over the tunneling junction electrostatics compared to the other VIB MX2 for any given device specifications94. In this context, it has been found that the TFETs based on IVB MX2, such as HfSe2, usually exhibit a notably inferior performance compared to WSe292.

a Schematics of monolayer-TMD based TFETs, and b Plots of Transfer characteristics of monolayer 2H- VIB TMDs adapted with permission from91. Copyright (2015) IEEE.

Furthermore, the strain can be utilized to effectively tune the electronic properties of monolayer TMDs10,90. The direct bandgap and effective masses of WSe2 can significantly be reduced by incorporating suitable bi-axial tensile strain (Fig. 13a). This eventually leads to a large improvement in the SS and Ion of WSe2-TFETs (Fig. 13b, c)95. A similar biaxial strain engineering strategy has been explored for monolayer PtSe2, a group-X TMD, demonstrating a simultaneous Ion improvement and SS reduction by exploiting the strain-induced reduction in the direct bandgap and effective masses of PtSe296.

a Plots of E-k dispersion relation of monolayer WSe2 with and without applied biaxial tensile strain, adapted with permission from90. Copyright (2013) IEEE, b transfer characteristics and c SS-Ion plot of monolayer WSe2–TFET with and without applied biaxial tensile strain, adapted with permission from97. Copyright (2016) IEEE.

TFETs based on phosphorene

The monolayer of Black Phosphorus is known as Phosphorene, which is the most stable known allotropes of phosphorus. In Phosphorene, each phosphorous atom is bound to three adjacent atoms through sp3 hybridization, leaving a lone pair of electrons in the p orbital. This gives rise to Phosphorene’s highly buckled structure, where each layer of the honeycomb structure contains two atomic layers (Fig. 14). In contrast to Graphene, Phosphorene exhibits a non-zero direct bandgap at all layer thicknesses (Fig. 14), which is highly tunable depending on the number of layers and incorporated strain. At the same time, the high anisotropy in Phosphorene allows small effective masses in the transport direction without compromising the overall density of states (DOS)6,97. These properties make Phosphorene an extremely potential choice for TFET design (Fig. 15a).

a Schematics of Phosphorene-based TFETs, Layer dependent b band-gap, c armchair direction effective masses, and d comparative transfer characteristics of Ph- and TMD- TFETs, adapted with permission from102. Copyright (2016) Nature.

It has been observed that the BTBT in a few-layer (ML) Phosphorene (Ph) TFET is highly influenced by the number of layers and the transport direction. Specifically, the BTBT is significantly higher in the armchair direction than in the zigzag direction, owing to the small effective masses in this direction. The increasing layer thickness further reduces the effective masses and energy bandgaps of Phosphorene (Fig. 15b, c)98. The number of layers must be carefully chosen to simultaneously optimize the tunneling junction shape and channel electrostatics of such Ph-TFET99,100. Thus, significantly superior performance can be achieved in a few-layer Ph-TFETs compared to its monolayer/few-layer TMD counterparts (Fig. 15d)101.

The performance of Ph-TFET can be significantly improved by applying suitable uniaxial strain. It has been observed that the applied compressive strain has substantially enhanced the BTBT component in the armchair direction due to the relevant bandgap reduction. However, for a large compressive as well as tensile strain, the bandgap switches from direct to indirect (Fig. 16a). Interestingly, under the applied tensile strain, the CBM shifted to the second conduction sub-band, where a much lower electron effective mass can be observed along the zigzag direction, and the opposite trend can be observed across the armchair direction (Fig. 16b, c).

Plots of a E-k dispersion relation and b Energy band-gap and c effective mass of Phosphorene under applied uniaxial strain, adapted with permission from103. Copyright (2017) IEEE.

At the same time, the direct bandgap at these second sub-band positions becomes very close to the indirect bandgap, and the direct BTBT dominates the transport. Therefore, the differences in the BTBT component in the armchair and zigzag direction can be made negligible through appropriate strain engineering, and the overall Ion can be significantly improved in Ph-TFET (Fig. 17)102. However, due to the reducing bandgaps and effective masses, the ambipolar BTBT component also increases, which degrades the SS of the Ph-TFET98. Thus, to effectively suppress the ambipolar BTBT component, a heterostructure design strategy can be adopted for Ph-TFET. Such design incorporates a few-layer Phosphorene in the Source/Channel junction and a monolayer Phosphorene in the Channel/Drain region (Fig. 18a). The smaller effective mass and bandgap of tri-layer Phosphorene enhance the on-state BTBT. In contrast, the ambipolar BTBT remains significantly smaller owing to the higher bandgap of monolayer Phosphorene (Fig. 18b, c)103. This substantially improves the Ion without compromising the Ioff component of Ph-TFET (Fig. 18b, c).

Transfer characteristics of Ph-TFET for a p-type and b n-type operational mode in armchair direction, c p-type and d n-type operational mode in the zigzag direction, under applied uniaxial strain, adapted with permission from103. Copyright (2017) IEEE.

a Schematics, energy band diagrams in a off-state and c on-state, and d I–V characteristics of hetero-structure Ph-TFET, adapted with permission from100. Copyright (2016) IEEE.

Another promising alternative Ph-TFET design strategy involves the vertical BTBT, where the applied electric field is parallel to the tunneling direction. However, for such TFETs, careful device design considerations are necessary to restrict the lateral BTBT component to achieve steeper SS104. Similar vertical BTBT-based Ph-TFET has also been realized in reconfigurable architecture using an additional tunneling gate terminal that controls the vertical BTBT component105.

Despite its promising material properties, Phosphorene demonstrates a strong affinity toward ambient water molecules. Typically, the long-term exposure results in layer-by-layer peeling, volume inflation, and unintentional doping in a few layers of Phosphorene. This ambient instability is expected to influence the electronic properties of Phosphorene significantly and poses a significant challenge in developing Ph-TFET. This encouraged the researcher to explore other stable 2D materials having electronic properties similar to Phosphorene for nanoscale TFET design.

TFETs based on metal mono-chalcogenides

The Group-IV mono-chalcogenides, which are often represented as IV MX (M = Ge, Sn; X = S, Se, Te) are the emerging 2D semiconductors that exist in different crystalline structures and exhibit a highly buckled honeycomb structure similar to Phosphorene in their orthorhombic crystal structure (Fig. 19).

Such MX also exhibits relatively smaller effective masses and moderate to small semiconducting bandgaps where the direct bandgaps are comparable to the indirect bandgaps (Fig. 19). Furthermore, the anisotropic nature of MX leads to smaller effective masses in their zigzag transport direction compared to that of armchair direction. Due to this, the MX has drawn considerable research interest for TFET design.

In the MX family, the GeSe and SnTe exhibit direct bandgaps. It has been observed that the direct BTBT component and smaller effective masses in the transport direction of monolayer GeSe-TFET lead to a large Ion while maintaining a sub-60 mV/decade SS106. The monolayer GeSe and SnSe-based TFETs have demonstrated Ion comparable to the monolayer Ph-TFET in their ballistic transport limit107. On the other hand, owing to their smallest direct bandgap and effective masses among different MX, the monolayer SnTe-TFET has been found to surpass the performance of few-layer Ph-TFETs as well as the monolayer WTe2-TFET (Fig. 20a, b)92. The MX materials are also found to be effective for hetero-tunneling junction design by varying layer thickness at different regions of nanoscale TFET. In this line, using a bilayer SnS in source/drain regions with monolayer SnS in the channel region, a SS below 50 mV/dec over four orders of current has been demonstrated108.

Comparative a material properties and drive currents and b transfer characteristics of mono chalcogenides and other 2D materials, adapted with permission from92. Copyright (2018) IEEE.

In essence, these results exhibited the potential of suitable IV MX for the design of nanoscale TFET. However, adequate research on both the material and device optimizations is further required to understand the design of MX-TFETs fully.

On the other hand, Group-III mono-chalcogenides, i.e., III MX (M = In, Ga; X = S, Se, Te) family of 2D materials exhibits hexagonal crystal structure and are rapidly drawing attention owing to their distinct electronic properties, including high carrier mobility and effective mass anisotropy109,110. Nevertheless, to the best of the author’s knowledge, no exclusive III MX-based nanoscale TFET design has been reported to date. Such absence of III MX nanoscale-TFET in literature may be attributed to their relatively higher energy bandgap (2–3 eV), which can potentially diminish the BTBT probability. However, there are reports on III MX and other 2D material-based heterostructure TFETs, which are discussed in the context of van der Waals (vdW) TFET design.

TFETs based on other 2D materials

To date, most of the reports on 2D semiconductor-based TFET design can be found in the categories mentioned in the previous sections. However, apart from such well-explored 2D semiconductors, several works using other 2D materials for TFET design have also been reported.

The post-transition metal tri-chalcogenides such as Bi2Se3 have been adopted for TFET design. The Bi2Se3 has a rhombohedral crystal structure with a small direct energy bandgap and electron’s effective masses in its few-layer configurations. Subsequently, under a small supply voltage, the Bi2Se3-TFET demonstrated below 60 mV per decade SS with a good Ion/Ioff ratio111. In this line, similar to Phosphorene, the other Group-V materials with highly buckled honeycomb structures, including Arsenene, Antimonene, and Bismuthene, have recently received attention for their ambient stability and small effective masses. Bismuthene appears to be most promising for TFET design due to its lowest and direct energy bandgap and small effective masses. Subsequently, the few-layer Bi-TFET exhibits a large Ion which is comparable to that of Ph-TFET. It should be noted that even if the Ion of As-TFET and At- TFET are nearly an order of magnitude smaller than Bi-TFET, a significantly superior SS and on-state/off-state current ratio can be observed in TFETs based on these materials112.

There are a number of 2D materials that are yet to be synthesized. However, the theoretical prediction of electronic properties suggests their suitability for TFET applications. In this line, the small direct energy bandgap and low effective masses in layered metal nitride halides such as TiNBr and TiNCl are also highly promising for TFET applications (Fig. 20a). The TFETs based on these materials exhibit significantly larger Ion than TMD and Phosphorene counterparts (Fig. 20b)92.

In this context, MXenes, a recently introduced member of 2D materials family, is rapidly increasing its footprints for different electronic applications113,114. The MXenes are 2D transition metal carbides, nitrides, and carbonitrides, which are often represented as Mn+1Xn (M = Sc, Ti, V, Cr, Zr, Nb, Mo, Hf, Ta; X = C, N; n = 1–3), and are structurally analogous to Graphene and demonstrates zero bandgaps at Dirac point. However, some of these MXenes (for example- Sc2CF2, Ti2CO2, Zr2CO2, and Hf2CO2) exhibit suitable semiconducting energy bandgap with low effective masses after surface functionalization113. Although the properties of semiconducting MXenes suggest their suitability for nanoscale TFET design, to the best of the authors’ knowledge, no reports are available on this line.

In spite of the apparent potential for TFET applications, the successful adoption of different ‘novel’ and emerging 2D semiconductors is still limited due to their lack of adequate theoretical understanding, reliable synthesis techniques, and stability issues.

TFETs based on van der Waals heterostructure

The weak Van der Waals interaction between individual layers of 2D materials enables the realization of designer heterostructures by vertically stacking one or few layers of two dissimilar 2D materials. These structures are usually referred to as the Van der Waals (vdW) heterostructure with atomically sharp interfaces with novel electronic and optical properties6. From the perspective of TFET design, the vdW heterostructure offers an exciting opportunity to realize suitable band-alignments at atomistically sharp interfaces that can be exploited as tunneling junctions with tunable tunneling barrier shapes.

In this context, the band alignments of different potential 2D materials for TFET design are compared (Fig. 21), demonstrating the possibility of realizing many vdW heterostructures with desirable type-II or type-III band alignments on the tunneling junction. Typically, retaining a relatively larger bandgap material at the source region for subduing the off-state leakage current and SS degradation, and at the same time, realizing a small BTBT barrier height with suitable bandgap overlapping at the tunneling junction for boosting up the Ion is highly desirable for TFET design. Consequently, the relative band alignment suggests some of the vdW heterostructure systems, including VI-B-MX2/ VI-B-MX2, VI-B-MX2/ IV-B-MX2, VI-B-MX2/SnX2, Ph/ VI-B-MX2, Ph/ III-MX, Ph/ IV-MX, MXenes/ VI-B-MX2, etc. can potentially offer the advantages of higher Ion without degrading the subthreshold characteristics (SS and Ioff) in TFET. Some of these vdW heterostructures based on high-performance nanoscale vdW-TFETs are discussed in this section.

The vdW-TFETs usually incorporate the hetero-junction between two different 2D materials in the channel region of double-gated TFETs (Fig. 22a). The vdW heterostructures are inherently advantageous for TFET design since it enables the formation of suitable hetero tunneling junction with reduced tunneling barrier height, atomically thin barrier width in the order of the inter-layer vdW gap, and the strong asymmetric gate-bias controlled vertical tunneling in the parallel direction of the applied gate electric field (Fig. 22b). Here the lateral/diagonal tunneling paths are naturally eliminated. In this line, Gong et al. have observed that the distinctive difference in energy bandgaps and work functions of the VIB MX2 and IVB MX2 monolayers can be effectively exploited to realize suitable type-2 and type-3 band-alignments in the vdW heterostructure for TFET design115.

The vdW heterostructure between monolayers of two dissimilar VIB-TMDs offers the advantages of direct BTBT between the VBM and CBM, where the effective tunneling barrier height, i.e., bandgap, can be tuned by carefully choosing the constituent materials. In this class of materials, the MoS2/WTe2 has drawn considerable interest, where the difference of in-plane lattice constants introduces a compressive and tensile strain in WTe2 and MoS2, respectively. The subsequent type-2 hetero-junction demonstrated an ultra-small effective direct bandgap of 0.135 eV with moderate electron and hole’s effective masses which are contributed by CBM of MoS2 and VBM of WTe2, respectively (Fig. 23a, b).

a Device schematics, b on-state/off-state band alignments in MoS2/WTe2 vdW hetero-junction, transfer characteristics for different c MoS2/WTe2 vdW hetero-junction lengths, adapted with permission from116. Copyright (2016) IEEE.

Such nearly broken bandgap alignment with moderate effective masses was highly beneficial for a sharp rise in tunneling component after the on-set of BTBT, leading to a sub-thermal SS. The Ion and SS of such vdW-TFET can be further optimized by carefully tuning the ratio of overall channel length to vdW hetero-junction length at the channel (Fig. 23c)116. On the other hand, the vdW heterostructure between IVB- and VIB- TMDs have also been studied for TFET applications. The MoS2/ZrS2 heterostructure exhibited an indirect bandgap of 0.26 eV, where ZrS2 and MoS2 contribute to the CBM and VBM, respectively. Interestingly, in this heterostructure, a second CBM has been observed practically at the same energy as the first CBM, demonstrating a significantly smaller transport direction effective mass than the first CBM. Furthermore, it has been observed that the CB effective mass and thereby tunneling probability can be significantly reduced by tuning the relative orientation and position between ZrS2 and MoS2 layers. This offers additional freedom for performance optimization through material engineering of such vdW-TFET117.

The vdW heterostructure-based vertical TFETs have also been demonstrated by combining TMD and non-TMD materials. In this context, the semiconducting Tin Di-Chalcogenides (SnX2; X = S, Se) have shown considerable structural similarity with TMDs and an indirect bandgap semiconductor in their monolayer and multilayer configurations compared to that of the TMDs. The SnX2/TMD-based vdW heterostructure has shown promise for the design of TFETs, where the SnX2 and TMD, respectively, contribute to the CBM and VBM. Typically, the monolayer SnS2/MoTe2 forms a type-2 hetero-junction with effective indirect bandgaps of 0.19 eV leading to a larger on-state BTBT (Fig. 24a, b)118.

On the other hand, the type-2 band alignment has also been observed in the vdW hetero-junction of monolayer WSe2/SnSe2 with an effective bandgap of 0.20 eV and a relatively smaller CBM/VBM effective masses than that of SnS2/MoTe2 (Fig. 24c). Thus, such vdW-TFETs demonstrate a high Ion of ~500 µA/µm with sub-20 mV per decade SS (Fig. 24d)118.

Among non-TMD/non-TMD vdW heterostructure, the vdW heterostructure of group-III and -IV MX materials with other suitable 2D materials showed considerable promise for TFET design. Typically, the Ph/InSe material system exhibits type-2 low band-gap band alignment, which offers a significantly higher on-state current for the vdW-TFETs119,120. Apart from suitable type-2 band alignments, the broken bandgap or type-3 band alignments are also highly suitable for TFET design. In this effect, the vdW-TFETs using GaTe/SnSe2, GeSe/SnS2, GeSe/SnSe2, and GeS/SnS2 have shown considerable potential owing to their suitable broken-gap band alignment and lower effective masses121,122. Furthermore, type-1 band alignment with a lower bandgap has also been explored for vdW-TFET design. In this line, a GeSe/GeTe vdW-TFET is reported with sub-thermal SS and a significantly larger Ion123.

It should be noted that there are potential vdW heterostructures that are yet to be explored, which may significantly broaden the landscape of nanoscale vdW-TFET design in the future.

In essence, the vdW heterostructures appeared particularly suitable for realizing different custom-built hetero-interfaces with desired band alignments in the tunneling junction. Consequently, by combining appropriate 2D materials in vdW heterostructure, a lower tunneling barrier height with suitable effective masses at the band edges can be accomplished at the tunneling junction. The constituent 2D materials are separated by the vdW gap at the hetero-junction, leading to atomistic thin tunneling barrier width. Furthermore, the large vertical overlap between the constituent 2D materials at the vdW interfaces results in a significantly larger tunneling area, where the electrostatics can be directly addressed by the out-of-plane gate electric field acting parallel to the tunneling path at the hetero-interface. The factors mentioned above can significantly boost the tunneling probability in vdW heterostructure-based TFET compared to their lateral junction-based counterparts.

Consequently, several recent theoretical and experimental works have been proposed on vdW-TFETs, and the numerical simulations clearly depict superior tunneling probability at the carefully designed vdW heterojunctions. In this context, to date, the majority of the experimentally reported 2D TFETs with sub-thermal (<60 mV per decade at room temperature) SS are realized using vdW heterostructures between two different 2D materials124,125,126,127,128, which indicates the potential of vdW heterostructure for nanoscale TFET design over their lateral-junction-based 2D material counterparts.

However, it is worth mentioning that inherent factors associated with vdW heterostructures can bottleneck the expected performance improvement in nanoscale vdW-TFETs. During fabrication, the different aspects, including substrate roughness, rippling in 2D materials, and interlayer misalignments, can modulate and even induce a spatial non-uniformity in the vdW gap at the heterojunction. In this context, it has been observed that the tunneling probability at the vdW heterojunction is extremely sensitive to the magnitude of the vdW gap between two dissimilar 2D materials. Specifically, the on-state current of TFET gradually reduces with the increasing vdW gap129. At the same time, the non-uniformity in the vdW gap-thickness can significantly degrade the sub-threshold characteristics and, thereby, the average SS129. Since the fabrication process strongly influences the vdW gap and its uniformity, dedicated process optimization approaches are required to realize the precise control of the vdW gap for high-performance vdW-TFET design.

On the other hand, the in-plane and outer-of-plane anisotropy in 2D materials usually result in heavier effective masses in the out-of-plane direction13,130,131. This can reduce the overall tunneling probability in the out-of-plane direction in vdW heterostructure and subsequently impose an inherent limitation on the performance of vdW-TFETs. Consequently, based on the choice of constituting 2D materials, irrespective of its inherent advantages, the Ion and overall Ion/Ioff ratio may be considerably degraded in the vdW-TFET. This suggests the need for careful choice of 2D materials and exploration of appropriate material engineering strategies for further tuning the effective masses of vdW heterostructure while retaining their inherent advantages for nanoscale TFET design.

Experimental realization of 2d-TFET - challenges and opportunity

This section comprehensively reviews the experimental realization of TFETs based on different 2D materials, and state-of-the-art fabricated 2D-TFET designs are highlighted. In this context, it should be noted that the fabricated 2D-TFETs usually have channel lengths in the order of a few hundred nanometers to a few micrometres and, therefore, cannot be considered a nanoscale TFET design. On the other hand, the experimental 2D-TFETs with longer channel lengths are often failed to demonstrate the desirable sub-thermal SS78,132,133. Consequently, the fabricated 2D TFETs with reported sub-thermal SS are emphasized in this review.

TFETs based on graphene nanoribbon

Despite the potential of GrNR for 2D-TFET design, as suggested in numerical simulation-based investigations, no experimental reports have demonstrated sub-thermal SS for GrNR-TFETs. Arguably, the best SS achieved is around 47 mV per decade at the temperature range of 5 to 40 K. However, the exponential increase in SS with temperature leads to severe degradation in subthreshold characteristics at room temperature134. Another approach demonstrated the room-temperature operation of GrNR-TFET by patterning GrNR with a sub-10 nm width and subsequent realization of a sharper tunneling junction using electrostatic doping from two adjacent Graphene side gates embedded in solid polymer electrolyte78. However, apart from an unacceptably large SS, the room temperature performance of these reported GrNR-TFETs is further compromised by their exceedingly small on-state/off-sate current ratio78,134.

This temperature-dependent performance degradation in GrNR-TFET can be primarily attributed to the non-uniform and low band-gap of synthesized GrNR, which leads to a significantly larger leakage current at room temperature. Therefore, the synthesis of Graphene and similar nanoribbon structures impose a highly challenging requirement for the lithography and patterning process for realizing uniform and extremely thin NR geometry with appropriate edge pacifications, which are presently bottlenecking the overall performance and subsequent development of GrNR-TFETs.

TFETs based on transition metal di-chalcogenides

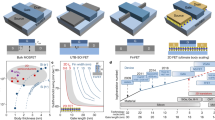

The numerical device simulations indicate that the relatively larger values of the bandgap (1–2 eV) in monolayer/few-layer VI-B TMDs can limit the BTBT component for 2D-TFET design. One of the significant breakthroughs in 2D-TFET design mitigated this shortcoming by incorporating a low band-gap 3D material as the source region to boost BTBT, while a suitable TMD is considered as the channel region to retain the superior electrostatic integrity of 2D-TFET. In this line, for the first time, a sub-thermal SS in 2D-TFET has been demonstrated using a bilayer (2 L) MoS2 channel on Germanium (Ge) source (Fig. 25a). The MoS2 was synthesized using conventional CVD technique and then transferred using PMMA-assisted technique to p-type doped Ge substrate. The device is patterned using standard photolithography and E-beam lithography technique and utilizes polymer electrolyte gating with polyethylene oxide (PEO) as a gate-insulator. A partial 2L-MoS2-channel overlap with Ge-source is introduced to ensure vertical BTBT-dominated transport while eliminating possible lateral tunneling paths in the device (Fig. 25b). This design offers multiple advantages to boost the BTBT component, including staggered hetero-junction formation between Ge and MoS2 with ultra-sharp source/channel doping profiles, reduced tunneling barrier height in low band-gap Ge source, atomically thin barrier width in the order of vdW gap between MoS2 and Ge, and strong gate-controlled vertical tunneling in the direction parallel to applied gate electric field through a significantly larger tunneling area in the Ge/2L-MoS2 overlapped region. The band alignments between Ge and two monolayers of MoS2 separated by the vdW gap restricts the available electronic states for tunneling in the absence of applied gate bias, whereas a sharp rise in entirely vertical tunneling-dominated charge transport is observed under applied gate bias (Fig. 25b). Subsequently, the Ge/2L-MoS2-TFET demonstrated an extremely low minimum SS of 3.9 mV per decade with an average SS of 31.1 mV per decade (over four orders of magnitude currents) current at room temperature, with a large Ion of 10 µA per µm (Fig. 25c, d)135.

a Device schematics, b on-state/off-state band alignments at the tunneling junction c transfer characteristics of Ge-source/2L-MoS2-channel, adapted with permission from135. Copyright (2015) Nature.

A similar 3D/2D vertical TFET structure has been reported based on the tri-layer (3 L) MoS2 channel and Silicon (Si) source. The Si/3L-MoS2-TFET demonstrated a minimum SS of 15 mV per decade at room temperature while maintaining an on-state current above 1 µA/µm136.

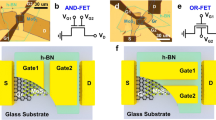

Therefore, it can be surmised that incorporating a low bandgap and a highly doped 3D materials-based source with suitable TMD channel materials presents a promising approach for high-performance 2D-TFET design. However, the formation of an interfacial oxidation layer in the 3D materials (Si or Ge) can potentially limit the overall tunneling probability in the 3D/2D tunneling junction for such a design. A different design approach for TMD-TFET has been recently reported. The device is realized using a hetero-structure of Gr, hexagonal boron nitride (h-BN), and few-layer (FL) MoTe2. In this design, the relatively lower bandgap FL-MoTe2 serves as a channel region, h-BN as a thin 2D gate insulator, and Gr as a gate contact. The inherent compatibility of Gr and h-BN systems ensure a better metal/insulator interface. The entire structure is realized on a defect-free poly-methyl methacrylate (PMMA) substrate, and the source/drain metallic electrodes are embedded in the PMMA layer. In contrast, the Gr top gate is encapsulated by polycarbonate (PC). The FL-MoTe2-TFET demonstrates a minimum SS of 36.4 mV per decade and an average SS of 44 mV per decade (over four orders of magnitude current) at room temperature. Nevertheless, the device suffers from a relatively inferior Ion (~0.1 µA per µm)137.

On the other hand, like any other 2D material, the TMD-based 2D-TFET design has to address its own set of fabrication challenges. In this context, it should be noted that the only way to ensure repeatability and controlled growth of monolayer to few-layer crystals of TMDs is by chemical vapour deposition (CVD). The growth process of TMDs via CVD is still in its research stage, and large area, uniform, and controlled growth remain challenging. Furthermore, the growth process is not deterministic, where the crystal growth varies in different regions of the substrate. Hence, the post-processing for the metal contacts has to be performed by electron beam lithography, which is not suitable for bulk production owing to its low throughput138,139,140,141,142,143,144,145,146,147. Thus the CVD process needs to be carefully optimized for the controlled and specific growth of monolayer TMDs while ensuring its compatibility with the photolithography process.

TFETs based on phosphorene

The attractive material properties of Ph (BP), and the subsequent high performance of Ph-TFETs as predicted in device simulation, motivated experimental exploration in this line. The experimental reports on a few-layer Ph-TFET exploited the electrostatic doping technique by introducing additional gates in the source/drain region. Consequently, the polarity and concentration of charge carriers in the source/drain region are controlled by suitable bias in the electrostatic gates. Such electrostatic doping often fails to achieve sufficiently sharper band bending in the tunneling junction, which might result in the observed large SS at room temperature and relatively smaller Ion (<1 µA per µm) in these Ph-TFETs133,148. In an attempt to optimize the performance, a homogenous vertical TFET design is proposed, where two independent bottom gates are introduced beneath bulk oxides, with sufficient lateral overlaps with the top gate. In this Ph -TFET, the BTBT in the vertical direction is tuned by applying suitable potentials in top and bottom gates, which leads to a notably larger Ion (>10 µA per µm). However, the sub-threshold characteristics of the device are still limited by an unacceptably large minimum SS (>180 mV per decade)105.