Abstract

Two-dimensional (2D) materials have been extensively adopted in various device architectures for advanced applications owing to their structural diversity, high functionality, and ease of integration. Among the various architectures, split-gate field-effect transistors (SG-FETs) have been widely studied based on their sequentially located SG electrode along the source/drain electrodes. In this paper, we propose two different homogeneous molybdenum disulfide (MoS2)-based SG-FET structures, namely AND-FET and OR-FET, whose gap directions are perpendicular to each other. It can exhibit AND or OR switching characteristics if it has a longitudinal or latitudinal gapped SG structure, respectively. Moreover, the AND-FET and OR-FET are regarded as folded structures of series and parallel connections of two n-type transistors. By using these switching devices, we successfully demonstrate NAND and NOR logic gates through a single active channel. These approaches are expected to pave the way for the realization of multi-functionality and high integration of 2D material-based future electronic devices.

Similar content being viewed by others

Introduction

Two-dimensional van der Waals (2D vdW) materials, consisting of atomically thin bodies and dangling-bond-free surfaces, have attracted significant research interest for the development of future electronics and their applications. For example, transition metal dichalcogenide (TMDC) semiconductors have emerged as active channel materials owing to their outstanding electrical properties. The use of monolayer molybdenum disulfide (MoS2), which is the most representative n-type TMDC semiconductor, has been reported for field-effect transistor (FET) applications with high electron mobility of ~167 cm2 V−1 s−1 and a high ON/OFF drain current (ID) ratio of ~108 1,2. Furthermore, the tunable bandgap of MoS2 has been investigated from 1.3 (bulk) to 1.9 eV (monolayer)3, and the presence of bandgap has raised overcoming the limitation of bandgap-less graphene property4,5.

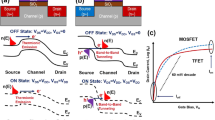

In addition, heterostructure devices, which are constructed by stacking different 2D vdW materials as Lego-like building blocks, have been explored6,7,8. These assembled 2D vdW materials can be used to create diverse device architectures for advanced electronic applications and have been demonstrated to be dual-gate FETs9,10, tunnel FETs (TFETs)11,12, heterojunction devices13,14, and split-gate FETs (SG-FETs)15,16,17. Among these, the dual-gate FET has top- and bottom-gate electrodes; therefore, its active channel experiences the gate field effect in two directions. In contrast, the SG-FET has two sequentially located SG electrodes along the source/drain (S/D) electrodes, which can locally control the carrier concentration in active channel materials. These charming device structural features have great strengths in device integration and implementation of new functional logic devices for 2D material-based future electronics.

Logic circuit application is one of the most representative methods to demonstrate advanced electronic performances. To construct logic gates such as AND, OR, NAND, and NOR, at least two transistors should be typically used18,19,20,21,22,23. For example, in the pull-down network (PDN) of inverter circuit applications, the series connection of two n-type transistors works as a NAND logic gate; conversely, the parallel connection of two n-type transistors works as a NOR logic gate. In previous studies, dual-gate FETs and SG-FETs were reported to demonstrate these conventional logic gates by using a single active channel9,15,24,25,26. These application methods could prove that 2D vdW materials have high functionality and exhibit ease of integration in advanced electronic devices.

In this study, we demonstrated single MoS2-based NAND or NOR logic gates, which were realized as different SG-FET structures. Based on the structural engineering of the SG-FET, the gap direction of the SG electrodes was defined for the longitudinal or latitudinal direction to the channel length direction. In other words, as their gap directions were perpendicular to each other, different switching characteristics, i.e., “AND” (AND-FET) or “OR” (OR-FET), were realized. We believe that this simple innovation will open further opportunities for the high-end application of 2D electronics.

Results and discussion

Longitudinal and latitudinal split-gate models

Figure 1a shows the optical microscopy (OM) image of the AND-FET, which has a generally established SG-FET structure with sequentially located SG electrodes along the S/D electrodes15,16,17,27,28. Our AND-FET consisted of a graphene S/D, MoS2 active channel, and h-BN top-gate insulator on a glass substrate. To construct the SG electrodes of the AND-FETs, the nanogap patterning technique was used to define the nanoscale gap. The detailed device fabrication method is presented in the Methods section and Supplementary Fig. 1. Figure 1b, c show the circuit symbol and 3D schematic top view of the AND-FET.

Figure 1d shows the OM image of the OR-FET, which has an SG gap direction that is perpendicular to that of the AND-FET. Our OR-FET also consisted of a graphene S/D, MoS2 active channel, and h-BN gate insulator, and the SG electrodes were fabricated by the nanogap patterning technique used to fabricate those of the AND-FET device (see Supplementary Fig. 2 for further details on the device fabrication process). However, the gap direction of the OR-FET was latitudinal to the channel length direction. Figure 1e, f, which respectively show the circuit symbol and the 3D schematic top view of the OR-FET, allow for an intuitive comparison of the gap directions of the AND-FET and OR-FET. These two different MoS2-based SG-FET structures are expected to have different switching characteristics owing to their structural differences.

Electrical characteristics and operating schematics of AND-FET

Figure 2a, b, respectively, show the 3D color surface and contour color map of drain current (ID) in the AND-FET at each first gate voltage (VG1) and second gate voltage (VG2) ranging from –7 to 7 V. Four distinct transition modes of the AND-FET were observed at high and/or low VG1 and VG2 values: AA (VG1 = VG2 = 7 V), DD (–VG1 = –VG2 = 7 V), DA (–VG1 = VG2 = 7 V), and AD (VG1 = –VG2 = 7 V) transition modes, where A and D are accumulation and depletion states of the active channel, respectively. The high ID only occurred in the AA mode, while the low ID occurred in the DD, DA, and AD modes. The black dashed line of Fig. 2b indicates the threshold voltage (Vth) of the AND-FET. When a common gate voltage is simultaneously applied to both SG electrodes, the AND-FET will be operated as a quasi-single gate MoS2 FET as shown to be a diagonal yellow dashed line in Fig. 2b (see Supplementary Fig. 3 with further details of the common gate operation). The high ON/OFF ratio in the common gate operation are clearly shown due to the gate-induced Fermi level modulation of graphene S/D electrodes contacted with MoS2 channel9,29. From the Fermi level modulation of graphene, the higher ON current and even the lower OFF current were observed in comparison with a metal S/D electrode which has a similar work function to the Dirac point of graphene30.

a, b 3D color surface (a) and contour color map (b) of ID in the AND-FET at each VG1 and VG2 value in the range from –7 to 7 V with VD of 1 V. c ID–VD output characteristics of the four distinct transition modes of the AND-FET. d The operating schematics for the four distinct transition modes (AA, DD, DA, and AD modes). e Circuit diagrams showing how the same switching function can be achieved with a single transistor (horizontally folded structure).

Figure 2c shows the output characteristics obtained in the four distinct transition modes of the AND-FET. The AND-FET has AND switching characteristic and exhibits a high ID at high VG1 and VG2 values (AA mode).

Figure 2d shows the operating schematics of the four distinct transition modes. The AND-FET has sequentially located SG electrodes along the S/D electrodes; therefore, the SG electrodes can independently modulate carrier concentration in the MoS2 active channel near the S electrode region (below the G1 electrode) and the D electrode region (below the G2 electrode)31,32. Accordingly, two working cases can be achieved with the AND-FET structure: (1) in the AA mode, the electron channels in both regions are formed below the G1 and G2 electrodes (channel on); (2) in the DD, DA, and AD modes, even one depletion region occurs an interrupted electron path (channel off). Therefore, ID can flow from the D electrode to the S electrode in case 1, while at least one depletion region (case 2) cannot permit the flow of ID. These two working cases cause the AND switching characteristics of the AND-FET owing to its SG electrodes being sequentially located along the S/D electrodes (see Supplementary Fig. 4 for further details on the band diagram of the AND-FET operation). Furthermore, as these switching characteristics generally occur in a series connection of two n-type transistors, we can consider the AND-FET a horizontally folded structure with a series connection of two n-type transistors, as shown in Fig. 2e.

Electrical characteristics and operating schematics of OR-FET

Figure 3a, b, respectively, show the 3D color surface and contour color map of ID in the OR-FET with respect to each VG1 and VG2 in the range from –3 to 3 V. Four distinct transition modes of the OR-FET are also observed, as in the case of the AND-FET, according to the high and/or low VG1 and VG2 values: AA (VG1 = VG2 = 3 V), DD (–VG1 = –VG2 = 3 V), DA (–VG1 = VG2 = 3 V), and AD (VG1 = –VG2 = 3 V) transition modes. Unlike the AND-FET, the OR-FET has a high ID in the AA, DA, and AD modes. A low ID only occurred in the DD mode. The diagonal yellow dashed line of Fig. 3b indicates the common gate operation of the OR-FET (see Supplementary Fig. 5 for further details on the common gate operation). Figure 3c shows the output characteristics obtained from the four distinct transition modes of the OR-FET. The OR-FET, which only has a low ID at low VG1 and VG2 (DD mode), shows an OR switching characteristic.

a, b 3D color surface (a) and contour color map (b) of ID in OR-FET at each VG1 and VG2 value in the range from –3 to 3 V with VD of 3 V. c ID–VD output characteristics of the four distinct transition modes of the OR-FET. d The operating schematics for the four distinct transition modes (AA, DD, DA, and AD modes). e Circuit diagrams showing how the same switching function can be realized with a single transistor (vertically folded structure).

Figure 3d shows the operating schematic from the four distinct transition modes of the OR-FET. The OR-FET has side-by-side located SG electrodes to channel length direction; therefore, the SG electrodes can independently modulate carrier concentration in the MoS2 active channel like two active channel devices. In other words, when one region of the MoS2 active channels is modulated by an electron channel (AA, DA, and AD modes), ID can flow along the S/D electrodes. For these reasons, the mapped ID of the OR-FET is different from that of the AND-FET: the AA, DA, and AD modes exhibit high ID (channel on), while the DD mode has a low ID (channel off) (see Supplementary Fig. 6 for further details on the band diagram of the OR-FET operation). Meanwhile, according to Fig. 3c, a higher ID is observed in the DA mode than in the AD mode. This phenomenon is due to the larger MoS2 active channel width under the G2 electrode as shown in Fig. 1d. In addition, the ID in the AA mode is the summation of the ID in the AD and DA modes. These results are clear evidence that our OR-FET is independently operated and has two current paths. These phenomena are distinguished from the AND-FET, and it can be considered a vertically folded structure with a parallel connection of two n-type transistors, as shown in Fig. 3e.

Demonstration of NAND and NOR logic gates

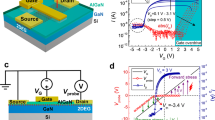

The AND-FET and OR-FET are two-input systems that can lead to different mapped ID results; therefore, their logic inverter circuit applications can be expected to produce different logic operations33. Furthermore, according to Supplementary Fig. 7, the two-input of AND-FET and OR-FET would be isolated correctly by using our proposed nanogap patterning technique. Figure 4a, d show the AND- and OR-FET-based inverter circuit diagrams, respectively. In these applications, the VG1 and VG2 of the AND-FET or OR-FET are used for the first input voltage (Vin1) and second input voltage (Vin2), respectively. Figure 4b shows the voltage transfer characteristics (VTC) curves of our AND-FET-based inverter circuit. Vin2 was swept from –7 to 7 V with a fixed Vin1 of 7 V (black line) and –7 V (red line) at a supply voltage (VDD) of 1 V. As a result, the low output voltage (Vout) only occurs in the AA mode, whereas the DD, DN, and AD modes show a high Vout. The inset table shows the truth table of the proposed AND-FET-based inverter circuit application. Figure 4c shows the Vout responses of our AND-FET-based inverter circuit application depending on the time domain for all the truth table cases, where we defined the relatively high and low voltage levels as a logic state “1” and “0,” respectively. This logic operation is known as NAND logic, and it has only an output state of 0 at the input state (1, 1).

a, d Inverter circuit diagram consisting of the external resistor with the AND-FET (a) and the OR-FET (d). b, e The VTC curves are shown as a function of Vin2 with the fixed Vin1 in the AND-FET (b) and the OR-FET (e). The inset tables show the truth tables of the NAND and NOR logic gates. c, f The time-domain operation of our NAND (c) and NOR (f) logic gates.

Figure 4e shows the VTC curves of our OR-FET-based inverter circuit. In this case, Vin2 was swept from –3 to 3 V with a fixed Vin1 of 3 V (black line) and –3 V (red line) at a VDD of 3 V. The OR-FET-based inverter circuit application only shows the output state 1 at the input state (0, 0) and an output state 0 at the input states (0, 1), (1, 0), and (1, 1). This logic operation is known as the NOR logic gate, and Fig. 4f shows the truth table of this logic operation depending on the time domain. Our NAND and NOR logic gates consist of a single MoS2 active channel, which can be organized by half the number of transistors. These approaches are simply motivated by the structural difference of SG-FETs and realize the multi-functionality and high integration of 2D vdW materials. To the best of our knowledge, this is the first demonstration of a different logic operation from the gap direction of a single MoS2-based SG-FET.

Beyond the small-footprint logic gate applications, the simple innovation of structural engineering in split-gate structure provides the demonstration of advanced logic applications such as multi-value logic and reconfigurable devices. For example, the multi-value logic could be demonstrated by the asymmetric schematic of the OR-FET, and both the top and bottom split-gates structure could make reconfigurable characteristics for the neuromorphic applications.

In summary, we demonstrated two different n-type MoS2-based SG-FET structures exhibiting AND or OR switching characteristics (AND-FET or OR-FET) depending on the values of VG1 and VG2. These switching characteristics were determined based on the gap direction between the SG electrodes. The nano-gapped gate electrodes of the AND-FET were longitudinal to the channel direction, while those of the OR-FET were latitudinal to the channel direction. We demonstrated AND-FET- and OR-FET-based inverter circuit applications for NAND and NOR logic gates, respectively, which were achieved by using a single MoS2 active channel. The SG-FETs in this study were structurally engineered to obtain these results, which indicate that 2D vdW materials with high integration and functionality can be realized for advanced electronic applications.

Methods

Device fabrication

The glass substrate was ultrasonically cleaned in acetone, methyl alcohol, and isopropyl alcohol (IPA) for 15 min. For the first step of device fabrication, the components comprising 2D nanosheet materials, such as the graphene S/D, MoS2 active channel, and h-BN top-gate insulator, were exfoliated and transferred onto the substrate using polydimethylsiloxane (PDMS) stamps. Then, the grown zinc-oxide (ZnO) NWs were dispersed on the PDMS using the drop-and-dry method with the IPA solvent and transferred onto the target site on the h-BN/MoS2 platform. After the 2D and 1D materials were transferred, Pt/Ti/Pt (20/10/20 nm) tri-layered electrodes were deposited on the patterned area by a DC sputtering system, and this area was defined by photolithography and lift-off processes. Finally, when the attached ZnO NWs under the monolithic gate electrodes were removed by the mechanical method, we successfully realized the top-gate staggered MoS2 SG-FET structures.

Device electrical characterization

All the static electrical measurements of our devices, such as ID–VG transfer, ID–VD output, mapped ID plots, and VTCs, were obtained using an Agilent 4156 B semiconductor parameter analyzer and a Tektronix AFG 1062 function generator in a dark box at room temperature.

Data availability

The authors confirm that the data supporting the findings of this study are available within the paper and its supplementary information files.

References

Radisavljevic, B. et al. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Wang, Yan et al. Van der Waals contacts between three-dimensional metals and two-dimensional semiconductors. Nature 568, 70–74 (2019).

Mak, K. F. Atomically thin MoS2: a new direct-gap semiconductor. Phys. Rev. Lett. 105, 136805 (2010).

Schwierz, F. Graphene transistors. Nat. Nanotechnol. 5, 487–496 (2010).

Das, A. Monitoring dopants by Raman scattering in an electrochemically top-gated graphene transistor. Nat. Nanotechnol. 3, 210 (2008).

Geim, A. K. & Grigorieva, I. V. Van der Waals heterostructures. Nature 499, 419–425 (2013).

Yao, J. D. & Yang, G. W. All-2D architectures toward advanced electronic and optoelectronic devices. Nano Today 36, 101026 (2021).

Tang, J. et al. Vertical integration of 2D building blocks for all-2D electronics. Adv. Electron. Mater. 6, 2000550 (2020).

Choi, K. et al. Non-lithographic fabrication of all-2D α-MoTe2 dual gate transistors. Adv. Funct. Mater. 26, 3146–3153 (2016).

Lee, G.-H. et al. Highly stable, dual-gated MoS2 transistors encapsulated by hexagonal boron nitride with gate-controllable contact, resistance, and threshold voltage. ACS Nano 9, 7019–7026 (2015).

Georgiou, T. et al. Vertical field-effect transistor based on graphene–WS2 heterostructures for flexible and transparent electronics. Nat. Nanotechnol. 8, 100–103 (2012).

Kim, S. et al. Thickness-controlled black phosphorus tunnel field-effect transistor for low-power switches. Nat. Nanotechnol. 15, 203–206 (2020).

Lim, J. Y. et al. Van der Waals junction field effect transistors with both n- and p-channel transition metal dichalcogenides. npj 2D Mater. Appl. 2, 37 (2018).

Jeon, P. J. et al. Enhanced device performances of WSe2–MoS2 van der Waals junction p–n diode by fluoropolymer encapsulation. J. Mater. Chem. C. 3, 2751 (2015).

Kwon, J. et al. All-2D ReS2 transistors with split gates for logic circuitry. Sci. Rep. 9, 10354 (2019).

Buscema, M. et al. Photovoltaic effect in few-layer black phosphorus PN junctions defined by local electrostatic gating. Nat. Commun. 5, 4651 (2014).

Bie, Y.-Q. et al. A MoTe2-based light-emitting diode and photodetector for silicon photonic integrated circuits. Nat. Nanotechnol. 12, 1124–1129 (2017).

Wang, H. et al. Integrated circuits based on bilayer MoS2 transistors. Nano Lett. 12, 4674–4680 (2012).

Radisavljevic, B., Whitwick, M. B. & Kis, A. Integrated circuits and logic operations based on single-layer MoS2. ACS Nano 5, 9934 (2010).

Kong, L. et al. Doping-free complementary WSe2 circuit via van der Waals metal integration. Nat. Commun. 11, 1866 (2020).

Resta, G. V. et al. Doping-free complementary logic gates enabled by two-dimensional polarity-controllable transistors. ACS Nano 12, 7039–7047 (2018).

Wu, P., Reis, D., Hu, X. S. & Appenzeller, J. Two-dimensional transistors with reconfigurable polarities for secure circuits. Nat. Electron. 4, 45–53 (2021).

Lin, Z. et al. Solution-processable 2D semiconductors for high-performance large-area electronics. Nature 562, 254–258 (2018).

Kim, J. S. et al. Dual gate black phosphorus field effect transistors on glass for NOR logic and organic light emitting diode switching. Nano Lett. 15, 5778–5783 (2015).

Liu, C. et al. Small footprint transistor architecture for photoswitching logic and in situ memory. Nat. Nanotechnol. 14, 662–667 (2019).

Chung, Y.-Y. et al. Switchable NAND and NOR logic computing in single triple-gate monolayer MoS2 n-FET. In IEEE International Electron Devices Meeting 897–900 (IEEE, 2020).

Pan, C. et al. Reconfigurable logic and neuromorphic circuits based on electrically tunable two-dimensional homojunctions. Nat. Electron. 3, 383–390 (2020).

Wu, G. et al. MoTe2 p–n homojunctions defined by ferroelectric polarization. Adv. Mater. 32, 1907937 (2020).

Lee, Y. T. et al. Graphene versus ohmic metal as source-drain electrode for MoS2 nanosheet transistor channel. Small 10, 2356–2361 (2014).

Choi, M. et al. Direct comparison of ohmic contact properties between graphene and metal source/drain electrodes. J. Korean Phys. Soc. 80, 986–990 (2022).

Hu, W. et al. Ambipolar 2D semiconductors and emerging device applications. Small Methods 5, 2000837 (2021).

Luo, P. et al. Doping engineering and functionalization of two-dimensional metal chalcogenides. Nanoscale Horiz. 4, 26–51 (2019).

Yi, J. et al. Double-gate MoS2 field-effect transistors with full-range tunable threshold voltage for multifunctional logic circuits. Adv. Mater. 33, 2101036 (2021).

Acknowledgements

Y.T.L. acknowledges the financial support from the National Research Foundation of Korea (NRF) (No. NRF-2021R1C1C1005235). D.K.H. acknowledges the financial support from the Korea Institute of Science and Technology (KIST) Institution Program (Grant No. 2E31532).

Author information

Authors and Affiliations

Contributions

All authors conceived the idea and designed the experiments. D.K.H., M.K., and Y.T.L. supervised the whole project. M.L. performed device fabrication and electrical measurements and C.Y.P. assisted in the verification of the operation of each device under Y.T.L.’s supervision. All authors analyzed the experimental data and co-wrote the manuscript with the discussion on it.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Lee, M., Park, C.Y., Hwang, D.K. et al. Longitudinal and latitudinal split-gate field-effect transistors for NAND and NOR logic circuit applications. npj 2D Mater Appl 6, 45 (2022). https://doi.org/10.1038/s41699-022-00320-w

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41699-022-00320-w

This article is cited by

-

Graphene Bridge Heterostructure Devices for Negative Differential Transconductance Circuit Applications

Nano-Micro Letters (2023)