Abstract

Two-dimensional van der Waals materials offer unique advantages for the development of band-to-band tunneling devices given their lack of dangling bonds, atomically flat thickness and steep band edges. Here, we present the experimental demonstration of an electric double layer (EDL) Esaki junction in synthetic WSe2 thin films. A Si-compatible process is developed for the fabrication of nanoscale FETs utilizing molecular beam epitaxy of WSe2 performed directly on top of a high-κ dielectric at back-end-of-line-friendly temperatures (<550 °C). Degenerate and abrupt doping profiles are obtained by modulating the electron/cation and hole/anion EDLs formed at the interface between a tens-of-nanometer long WSe2 channel and a solid polymer electrolyte, polyethylene oxide:cesium perchlorate (PEO:CsClO4). Numerical simulations are used to determine the bias dependence of the equilibrium ion and carrier density profiles. The EDL-doped tunnel diode exhibits repeatable, gate-tunable band-to-band tunneling with negative differential resistance in the forward bias regime at temperatures up to 140 K, and strong conduction in reverse bias. A maximum peak-to-valley current ratio of 3.5 is measured at 110 K.

Similar content being viewed by others

Introduction

Quantum mechanical band-to-band tunneling (BTBT) is remarkably displayed in the negative differential resistance (NDR) region of the current–voltage (I–V) characteristic of a forward-biased Esaki diode.1 Esaki junctions lie at the heart of the tunnel field-effect transistor (TFET), a viable candidate for low-voltage electronics.2,3 The subthreshold swing (SS) of the metal-oxide–semiconductor field-effect transistor (MOSFET) is limited by the Maxwellian tails of the source Fermi distribution to 60 mV/decade at room temperature, thus hampering supply voltage scaling in today’s transistors. On the other hand, BTBT across the source/channel energy barrier of a TFET does not suffer the same constraints and can provide steep current switching, thus beating the 60 mV/decade wall.4,5,6,7,8,9 However, thickness inhomogeneities and dangling bonds acting as trap sites at the tunneling junction in thinned bulk semiconductors, in conjunction with doping-induced band-edge smearing, present obstacles to the realization of steep-slope devices.10,11

Owing to their intrinsic atomic flatness and lack of dangling bonds, 2D layered semiconductors, such as transition metal dichalcogenides (TMDs), provide a new testbed for steep transistors.12 In 2D tunnel junctions, NDR has been observed in several vertical Esaki heterojunctions including staggered, viz. MoS2/WSe2,13,14,15 SnSe2/WSe2,16 or broken-gap, viz. black phosphorous (BP)/SnSe217 and BP/ReS2,18 with all of these band alignments created by stacking of exfoliated 2D flakes. NDR in a lateral homojunction requires degenerate and abrupt doping profiles to enable BTBT, and due to difficulties in 2D doping, only two prior reports have been published. Pang19 utilized a substochiometric SiNX and a top-gated MOS structure to dope a WSe2 flake n-type and p-type, respectively. NDR with a peak-to-valley current ratio (PVCR) of ~2 at room temperature was reported and a peak current (IP) of 9 pA. In the study by Liu,20 an Al2O3-masked benzyl viologen and gold chloride enabled degenerate n-type and p-type doping, respectively, in an MoS2 flake. Liu reported PVCR < 2, and IP ~ 50 nA/µm. The measured peak voltage (VP) by Pang19 was ~1.5 V, and Liu20 reported 0.8 V, which is well above what is expected in an Esaki tunnel junction, VP ≈ (Φn + Φp)/2 (with Φn and Φp being the electron and hole degeneracies, respectively). The difference between the expected VP and its measured value suggests an additional voltage drop in the current path of these devices to account for the high VP. Herein, we observe BTBT with peak voltage below 0.5 V, in accord with expectations for Esaki tunneling.

In this study, which refines and extends the analysis of our prior work,21 a TMD-on-insulator approach is used to fabricate nanoscale FETs, in which synthetic, few-layer WSe2 films are grown by molecular beam epitaxy (MBE) directly on top of an amorphous high-κ dielectric deposited by atomic layer deposition (ALD) on Si. Degenerate n-type and p-type doping are achieved by stabilizing the electron/cation and hole/anion electric double layers (EDLs) formed at the interface between the 2D channel and a solid polymer electrolyte, polyethylene oxide:cesium perchlorate (PEO:CsClO4). The EDLs are stabilized by cooling the device while gating, and this “frozen junction” technique22 is illustrated in Fig. 1a–c. CsClO4 dissociates into Cs+ and ClO4− in the solid polymer, and with no bias applied, the ions are homogeneously distributed within the polymer matrix (Fig. 1a). Upon the application of a channel source/drain (S/D) bias, anions (cations) drift towards the positively (negatively) biased electrode until steady-state conditions are reached (Fig. 1b). The movement of the ions relies on the polymer chains being mobile as well. Therefore, when the temperature exceeds the glass transition temperature of the polymer electrolyte (Tg ~ 240 K for PEO:CsClO4), the ions are free to move. However, by setting the location of the ions with the S/D bias, and then lowering the temperature of the system to T < Tg, the segmental mobility of the polymer chains is arrested, and the ions are locked into place. Even when the programming bias is removed (Fig. 1c), the ions remain immobilized, and therefore the established ion distribution is mirrored by free carriers in the underlying 2D channel, setting the doping profile. TMD23,24 and graphene25 frozen p–i–n junctions have been demonstrated with sheet charge densities even exceeding ~1013 cm−2, however, the S/D spacing must be reduced to the tens-of-nanometer scales for tunneling to be observed—an assertion that is demonstrated in this paper. Further, we show that the junction electric field can be further increased by utilizing a back gate (BG) to shape the spatial arrangement of the charged layers and enable BTBT.

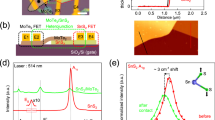

Schematic explanation of the frozen junction method. When no external bias is applied, a ions are randomly distributed and free to move within the polymer matrix at temperatures above the glass transition temperature Tg. b In response to an electric field, anions drift towards the positively biased electrode, while cations drift towards the negatively biased electrode. After the steady-state ion profile is configured, the cooling-while-biasing step is used where the device is quenched below Tg of the solid polymer. c Below Tg ions are immobile, hence the programming bias can be released and the doping profile in the 2D channel is a mirror function of the overlying ion distribution. d Schematic cross section of the fabricated EDL WSe2 FET. e False-colored SEM top view of a 40 nm-long WSe2 FET prior to PEO:CsClO4 coating. Scale bar is 500 nm. f TEM cross section showing a 6–7 layer WSe2 thin film sandwiched in between the Al2O3 BG oxide and Ti/Pd metal stack. Scale bar is 5 nm

Results and discussion

Figure 1d shows a schematic cross section of the fabricated WSe2 EDL FETs. Van der Waals epitaxy of WSe2 was carried out onto a 30 nm-thick Al2O3 high-κ dielectric deposited by ALD on top of an n-type Si substrate thermally oxidized with 10 nm of SiO2. The MBE growth lasted 7 h at a temperature of 550 °C yielding a WSe2 thin film consisting of 6–7 layers as measured by transmission electron microscopy (TEM) (Fig. 1f). The top-view scanning electron micrograph (SEM) of Fig. 1e elucidates the device layout; a patterned 300 nm-wide stripe of WSe2 is highlighted in orange, the exposed Al2O3 surface after mesa etch is in blue, and closely spaced Ti (1 nm)/Pd (20 nm)/Au (30 nm) S/D electrodes are in green. The channel length is measured to be ~40 nm. Two side-gate (SG) electrodes are also visible and used for EDL gating measurements. Inside an Ar-filled glovebox, the WSe2 FETs are finally coated with the solid polymer electrolyte, PEO:CsClO4, to complete the device fabrication.

Quantifying the strength and spatial extent of the EDLs formed at the solid polymer/semiconductor interfaces requires a simulation approach capable of capturing both carrier and ion dynamics. Figure 2a shows the structure simulated using COMSOL Multiphysics.26 Ion transport within the polymer domain is here described via a modified Poisson–Nernst–Planck model (MPNP)27 to account for the finite size and close-range correlations of the ions. The Stern layer28 is accounted for by the insertion of a 0.3 nm charge-free vacuum layer. According to the model, the modified Nernst–Planck equation reads:

where cA (cC) is the anion (cation) concentration, D the diffusion coefficient, z the ion valence, e the elementary charge, ψ the electrostatic potential, and a is a phenomenological parameter which determines a maximum ionic concentration when the ions are packed at the EDL cMAX = 1/(NAa3), where NA is the Avogadro’s constant. Since the Bjerrum length in PEO can be as large as ~8 nm and the ionic radius is at the Angstrom scale, there is uncertainty on the selection of a. In the simulations, a = 0.75 nm for both ion species (cMAX ≈ 3.94 mol/l ≈ 2.37 × 1021 cm−3), resulting in a sheet charge density of ~1.3 × 1014 cm−2, which is consistent with measurements on 2D materials.29 Neglecting mass transfer across the Stern layer and electrochemical reactions at the polymer boundaries, the polymer and semiconductor domains are only coupled through Poisson’s equation. Since we are interested in the steady-state ion profile, the diffusion coefficient D = kBTµ/e (assumed equal for both cations and anions) does not impact the results of the computation.

Numerical modeling of EDL Esaki junctions. a Simulation domain. CCsClO4 = 1 mol/l, EG = 1.1 eV, χ = 4.1 eV, ΦM = 4.7 eV, ΦBG = 4.3 eV, εPEO = 7, εWSe2⊥(∥) = 5 (8). The anion and cation mobilities, µCs = µClO4 = 10–7 cm2/V s, are chosen to speed up convergence; the values do not affect the steady-state geometry of the EDL. b Anion, cation, and net ion profile at the bottom surface of the PEO:CsClO4 domain, i.e. 0.3 nm above the top of the semiconductor surface. Inset: net ion concentration as vs. position in the proximity of the source metal electrode. Modulation of the net ion concentration profile by applying a c positive or d negative BG voltage during the “junction set” step. The computed ion distributions are subsequently employed as fixed charge inputs for Poisson’s equation of the “frozen junction” state, for T = 220 K and VD = VS = VBG = 0 V. The corresponding equilibrium band diagrams are shown in e and f, respectively. e inset: junction electric field enhancement for the different ion doping profiles examined

Figure 2b shows the steady-state anion, cation, and net ion distribution profiles versus position at the bottom of the PEO:CsClO4 domain, i.e. along the A–A’ line cut in Fig. 2a, obtained for a programming bias of VD = −VS = 1.5 V, and VBG = 0 V. In response to a lateral electric field, an anion (cation) EDL is formed in a narrow region near the drain (source) electrode. The inset of Fig. 2b shows that the net ion concentration saturates at cMAX in the proximity of the source contact. The ion concentrations then decay to their bulk, charge-neutral values near the center of the channel. The net ion distribution profile results in degenerately n-type and p-type doping at the two ends of the channel, in turn connected through a graded profile reaching peak electric fields of 0.45 MV/cm. The lateral potential profile of the ion-induced p–n junction can be modulated as a function of VSG and VDS in the ambipolar regime of an EDL FET.30,31 Here we employ the BG to directly access the ion population above the WSe2 channel. As can be seen in Fig. 2c, increasing VBG from 0 to 5 V results in a strong accumulation of anions, and the strengthening of the same EDL as VBG is made more positive, while the cation EDL maintains its position near the source. Moreover, the transition region between the two EDLs becomes narrower and sharper, as inferred by the net ion concentration 5 nm past the junction point increasing from 1.1 × 1020 to 3.7 × 1020 cm−3 for VBG = 1 V and VBG = 5 V, respectively. Similar considerations apply for the negative VBG case as shown in Fig. 2d. The ion profile of Fig. 2c, d are then used as fixed charge inputs for the calculation of the equilibrium band diagrams of Fig. 2e, f at T = 220 K, respectively, along the B–B′ line cut in Fig. 2a. At VBG = 0 V, a p–i–n diode is obtained with degenerate doping at the S/D electrodes. On the other hand, the channel central region becomes p+ as the BG voltage increases, with an abrupt transition to n+ near the source end, resulting in a tunneling distance Λ ~ 11 nm for VBG = 5 V. In addition, the junction peak electric field increases from 0.45 to 1.12 MV/cm, for VBG equal to 0 and 5 V, respectively, as shown in the inset of Fig. 2e. Conversely, using the ion distribution for negative BG voltage, the n+ region extends past the middle of the channel, with a sharp change to p+ near the drain. A slightly larger Λ with respect to the previous condition is predicted which is due to the negative flat-band voltage, VFB = −0.4 V, resulting from the work function difference between the S/D and BG metal contacts.

Prior to establishing the junction doping profile, SG transfer curves are recorded to confirm the ambipolar characteristics of the ion-gated WSe2 FET.23 The room temperature SG voltage (VSG) sweeps reported in Fig. 3a (sweep rate (SR) of 5 mV/s ensures measurement repeatability) indicate strong ambipolar conduction with electron and hole ON currents reaching ~25 and 15 µA/µm, respectively, VDS = −0.25 V, and ON/OFF ratios exceeding 104. The presence of both an electron and hole branch indicate that with the appropriate VSG polarity, Cs+ and ClO4− can unipolarly accumulate on top of the WSe2 channel. Moreover, the device behaves as a Schottky barrier (SB) FET with the Fermi level at the WSe2/Pd interface pinned towards the valence band edge of the semiconductor.32 The hole subthreshold current is substantially independent of VDS, which is reasonable for a p-type SB FET because the drain bias has little impact on the height or shape of the SB at the source side. The subthreshold swing in the hole branch is ~230 mV/dec over three decades of ID, suggesting an immobile charge density of ~8 × 1012 cm−2. Meanwhile the subthreshold swing degrades strongly for the electron branch, with significant higher drain-induce barrier lowering related to the exponential dependence of the tunneling probability through the drain SB as a function of VDS.

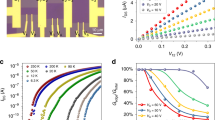

SG transfer characteristics. a Room temperature EDL gating of a 40 nm-long WSe2 FET. The open circles, open diamonds, and crosses represent ID, IBG, and ISG, respectively. b SG sweeps for VBG = 10 V (open triangle) and VBG = −10 V (open circles). c 2D colormap of ID versus VSG and VBG (VDS = −0.05 V). d Iso-ID data points in the VSG–VBG space for the electron (triangles) and hole (squares) branches. Lines represent a linear fit

As predicted in the modeling section and observed experimentally, the BG modulates the ion population on top of the TMD channel which can be seen in the shift of the electron and hole threshold voltages with VBG (Fig. 3b). This is due to the capacitive coupling between the BG and the channel surface potential mediated through the EDL formed at the WSe2 top surface. The influence of the latter can be estimated by means of repeated DC transfer curves. Figure 3c shows a contour plot of ID in logarithmic scale as a function of both VSG and VBG, at fixed VDS = −0.05 V (each ID scan is obtained by sweeping VSG while keeping VBG constant). The dark blue portion of the plot indicates the OFF state of the device, while the hole (electron) branch rises to the left (right) with respect to the minimum conduction point. Figure 3d highlights two constant-drain current values at 5 and 50 nA/µm from Fig. 3c, in which the triangles (squares) indicate the electron (hole) branch. Following double gate (DG) MOSFET theory, the threshold VTH as a function of VBG can be written as33

where VTH0 is a constant, CBG, CD, and CSG are the BG, semiconductor depletion, and SG capacitances, respectively, and VFB,BG is the BG flat band voltage. Assuming CD ≫ CBG, the slope of the linear fit of Fig. 3d reads ΔVBG/ΔVSG = −CSG/CBG, hence the SG capacitance is estimated CSG = 0.43 (0.56) µF/cm2 for the hole (electron) branch. For comparisons Xu24 extracted a value of ~3.8 µF/cm2 using a similar method. The relatively small values of the extracted CSG in this scaled transistor geometry suggested that the EDL capacitance is not the dominant part of CSG but is embedded in a network which includes two EDL capacitances, at the WSe2/PEO and PEO/SG, plus pad, interface trap, and/or quantum capacitances that reduce the SG efficiency.34,35,36

At room temperature, the EDL Esaki junction is formed by applying VD = −VS = 1.5 V and VBG = 5 V for 1 h, and subsequently lowering the temperature of the system below Tg, while continuously biasing the device. The I–V characteristics of the frozen junction at T = 80 K are shown in Fig. 4a. The EDL-doped diode is more conductive in the reverse direction, and in the forward bias it exhibits the characteristic NDR at low VDS, before the turn on of the diode thermionic current, both indications of BTBT. The upward and downward sweeps (SR = 125 mV/s) in the forward bias regime in linear scale are reported in Fig. 4b, c, respectively, and clearly show that NDR is present independent of sweep direction.

Evidence of Esaki tunneling at T = 80 K. a Tunnel diode I–V characteristics in logarithmic scale. The characteristic N-shaped NDR region is observed in forward bias (inset), together with a strong conduction in the reversed bias. NDR is tuned by the BG bias. Linear scale I–V in forward bias for the b upward and c downward sweep direction. d PVCR, peak (solid triangles), and valley (open circles) e currents and f voltages versus VBG. Double-sweep I–V traces were obtained by steeping the drain voltage from −0.75 to 0.75 V at a SR = 0.125 V/s, with a hold time of 10 s between measurements

The variations in PVCR, peak and valley currents and voltages as a function of BG voltages are quantified in Fig. 4d–f. The PVCR is ~1.3, (Fig. 4d), and IP ~ 1.3 nA/µm (Fig. 4e), for VBG = −10 V. A modulation of the NDR region is observed as a function of the BG bias in the range from −10 to 5 V; no NDR is observed for VBG > 5 V. The measured PVCR, peak and valley currents are remarkably consistent as a function of VBG and sweep direction. The recorded backward sweep of the first closed-loop scan for VBG = −10 V indicates a shift for both the peak and valley voltages (Fig. 4f), which is a signature of trapping during the forward sweep. The superlinear turn on of the tunneling current for VDS < 0.25 suggests that the SBs in series with the tunneling junction are limiting the transport for small applied bias. In fact, the results of the transport measurements can be thought of as the series combination of two reverse-biased tunneling contacts in series with the Esaki diode. The impact of the former is more pronounced for small VDS, where a slow turn-on of tunneling current is observed. Even so, VP remains below 0.5 V for all the BG biases and for both sweep polarities.

Figure 5a shows our measured Esaki characteristics and a labeled cartoon of the representative characteristics illustrating our understanding of the transport. For larger VDS, BTBT current becomes the limiting factor in the transport, therefore we can observe the NDR region between VP and VV in the forward bias. The valley current is set by the increasing Itherm component due to excess and thermionic currents. In the reverse bias, Zener tunneling conduction is observed without current saturation, as a function of VBG, as desired for a TFET. This is a consequence of the geometry of the junction since the BG is not aligned to the tunneling junction. The I–V characteristics of two additional frozen junctions, namely devices D2 and D3, at T = 80 K are provided in Fig. 5b, c. Comparison plots are provided in (Fig. 5d) of the measured peak and valley voltages and (Fig. 5e) of the peak and valley currents. As previously noted, the Esaki peak voltages are typical for Esaki tunneling.

Esaki junction transport explained and additional device results. a Qualitative explanation of the measured I–V characteristics of the EDL Esaki junction. b Semi-log plot of the tunnel diode I–V characteristics at T = 80 K for the device D2. c Same characterization for the device D3. d Comparison of the measured VP and VV for the three different devices exhibiting NDR (D1 is the device under study in Fig. 4). Lighter (darker) color tone indicate the valley (peak) voltages. Different colors indicate different VBG as indicated in the legend. e Comparison of the measured IP and IV for the same devices

In Fig. 6a the same characterization is reported for T = 110 K for the device D1 (the inset shows the I–V at T = 140 K and VBG = −10 V), and the absolute conductance ID/VDS is plotted in Fig. 6b. No NDR is observed for T > 140 K, because the excess current resulting from defects exceeds the valley current. The conductance slope extracted from the NDR region of the I–V characteristics represents a key figure of merit of the rate of change of the joint valence/conduction band density of states11, and its steepness is related to the minimum SS achievable in a TFET when density-of-state switching is limiting the current modulation. Because electrostatic, and not substitutional doping is used in this report, the extracted conductance slope is an indication of the intrinsic band-edge steepness of the MBE-grown WSe2 films. The dashed-dotted lines represent a linear fit of the semi-log plot, and the numbers next to the lines indicate the average conductance slope, whose minimum value reads 125 mV/decade. The reason for the BG-dependence on the extracted conductance slope can be qualitatively explained with the help of the band diagrams of Fig. 6f: the BG modulates the position of the tunneling junction along the channel and due to spatial inhomogeneities, such as thickness fluctuations also noticeable in Fig. 1f, this will cause a smearing of the band-edge. A maximum PVCR of 3.5 is measured for VBG = −5 V, which exhibits a nonmonotonic dependence on VBG (Fig. 6c). Since the BG is a global terminal for our EDL Esaki diode, a more positive (negative) VBG will tend to accumulate (deplete) electrons on the n-side of the junction while at the same time depleting (accumulating) holes on the p-side, as it is qualitatively explained with the plot of the electron and hole degeneracies versus VBG of Fig. 6g. Hence, the BG modulation should show an optimum for the tunneling window and distance (Fig. 6h), causing the PVCR nonmonotonic trend.

Esaki tunneling and conductance slope. a Semi-log plot of the tunnel diode I–V characteristics at T = 110 K. Inset: same characterization at T = 140 K. b Absolute conductance ID/VDS versus VDS for different VBG biases. Dashed-dotted lines indicate the linear fit of the conductance slope (number next to lines) in the NDR region. c PVCR, peak (solid triangles), and valley (open circles), d currents, and e voltages versus VBG. The maximum PVCR reads 3.5 for T = 110 K and VBG = −5 V. f Modulation of the equilibrium conduction and valence band profiles as a function of VBG. g Electron and hole degeneracies, and h tunnel distance vs. VBG

In Fig. 6d, a 10x modulation of IP (solid triangles) and IV (open circles) is reported as a function of VBG, with tunneling current values reaching ~nA/µm levels. As shown in Fig. 6e, the peak voltages are now shifted in the 0.2–0.3 V range, with significantly lower voltages in comparison to the reports of Pang19 and Liu.20 Doping levels of ~2.8 × 1013 cm−2 are inferred assuming that the measured minimum VP corresponds to the junction degeneracy, consistent with previous reports of PEO:CsClO4-doped WSe2 channels.37 As already mentioned, the Schottky contact at the WSe2/metal interface (especially for electrons) is limiting the device performance, hence a combined high/low metal work function contact scheme would be desirable to further increase IP and reduce VP. From 110 to 140 K, IP and IV evidence a positive temperature coefficient ascribable to trap/phonon-assisted tunneling processes preventing the observation of NDR at higher temperatures.

In conclusion, Esaki tunnel junctions are demonstrated in WSe2 FET with 40 nm channel length. EDLs form with opposite sign at opposite contact edges of the channel to induce a p–n junction. Numerical simulations of the coupled systems show that degenerate and abrupt doping profiles are achievable. A BG is employed which makes the NDR gate-tunable at temperatures up to 140 K, and maximum PVCR of 3.5 at T = 110 K. When compared to previous reports for WSe2,15 the fabricated Esaki junctions provide increased PVCRs, from ~2 to 3.5, 100× higher IP, from ~pA/µm to ~nA/µm levels, and a significant reduction in VP, from 1.5 to 0.2 V, as should be expected for tunnel diodes.

Methods

On top of an n-type Si substrate (ρ ~ 3–14 Ω cm) thermally oxidized with 10 nm of SiO2, a 30 nm Al2O3 dielectric is deposited by ALD using trimethylaluminum/water precursors at 200 °C. WSe2 (pulse time and purge time were 15 ms and 8 s, respectively, for both precursors). MBE growth was performed in a VG Semicon V80H system, at a temperature of 550 °C with elemental Se and W supplied at pressures of 1 × 10−4 and 2 × 10−7 Pa, respectively. In order to promote 2D growth, high chalcogen/transition metal flux ratios are required,38,39 the latter additionally boosted by periodically closing and opening the W shutter for 20 s, which conjointly increases the time for the Se to react with the W adatoms.40 Prior to the WSe2 growth, the substrate was annealed at 550 °C for 1 h, and the Se and W sources outgassed for 2 h to guarantee high purity. The duration of the MBE growth was 7 h resulting in a WSe2 film composed of 6–7 layers. After precleaning by hot acetone and isopropyl alcohol (IPA), the sample was backed at 150 °C for 2 min to dehydrate the surface. Electron beam lithography (EBL) and a XeF2 vapor phase etching were employed to pattern the WSe2 film. A 120 nm-thick poly(methyl methacrylate)-950-C2 (PMMA-950-C2, MicroChem) layer was spin-coated at 4000 rpm for 45 s, followed by a soft bake at 180 °C for 1 min. After exposure, the wafer was developed in methyl ethyl ketone/methyl isobutyl ketone/IPA (MEK:MIBK:IPA) solution (volume ratios of 3:50:150) at room temperature for 45 s, spin-dried at 5000 rpm for 30 s, followed by a post-development bake at 105 °C for 5 min. The XeF2 etch was conducted using a Memstar BT001 system at a pressure of 3 Torr for 50 s. Photoresist stripping was performed by dipping the sample in hot acetone for 20 min, followed by a 5-min IPA rinse. Subsequent EBL, metal deposition and lift-off steps defined Ti (1 nm)/Pd (20 nm)/Au (30 nm) S/D electrodes, and Ti (20 nm)/Au (120 nm) probing pads. A dual layer resist stack was employed consisting of a 300 nm undercut layer of methyl methacrylate-8.5-EL9 (MMA-8.5-EL9, MicroChem) spin coated at 4000 rpm for 45 s and soft baked at 150 °C for 1 min, topped with PMMA-950-C2. The development and lift-off recipe followed the procedure already described for single layer PMMA. Inside an Ar-filled glovebox, the WSe2 FETs were coated with a solution containing 1 wt% PEO:CsClO4 (PEO ether oxygen to Cs+ molar ratio of 76:1, corresponding to an ion concentration of ~2.2 × 1020 cm−3) in anhydrous acetonitrile, and annealed at 90 °C for 2 h to complete the device fabrication. Electrical characterization was carried out inside a Cascade Microtech PLC50 cryogenic vacuum probe station at a base pressure < 10−5 Torr using an Agilent B1500A semiconductor parameter analyzer.

Data availability

The data used in this study are available upon reasonable request from the corresponding author P.P. (ppaletti@nd.edu)

References

Esaki, L. New phenomenon in narrow Germanium p–n junctions. Phys. Rev. 109, 603 (1958).

Seabaugh, A. C. & Zhang, Q. Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 98, 2095–2110 (2010).

Ionescu, A. M. & Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479, 329–337 (2011).

Lu, H. & Seabaugh, A. Tunnel field-effect transistors: state-of-the-art. IEEE J. Electron Devices Soc. 2, 44–49 (2014).

Ahn, D. H., Ji, S. M., Takenaka, M. & Takagi, S. Performance improvement of InxGa1−x As tunnel FETs with quantum well and EOT scaling. In Proc. Symposium on VLSI Technology, 224–225. https://doi.org/10.1109/VLSIT.2016.7573443 (IEEE, 2016).

Memisevic, E., Svensson, J., Hellenbrand, M., Lind, E. & Wernersson, L. E. Vertical InAs/GaAsSb/GaSb tunneling field-effect transistor on Si with S = 48 mV/decade and I on = 10 µA/µm for I off = 1 nA/µm at V ds = 0.3 V. In Proc. IEEE International Devices Meeting (IEDM), 19.1.1–19.1.4. https://doi.org/10.1109/IEDM.2016.7838450 (IEEE, 2016).

Alian, A. et al. InGaAs tunnel FET with sub-nanometer EOT and sub-60 mV/dec sub-threshold swing at room temperature. Appl. Phys. Lett. 109, 243502 (2016).

Takagi, S. et al. III-V and Ge/strained SOI tunneling FET technologies for low power LSIs. In Proc. Symposium on VLSI Technology, T22–T23. https://doi.org/10.1109/VLSIT.2015.7223687 (IEEE, 2015).

Zhao, X., Vardi, A. & del Alamo, J. A. Sub-thermal subthreshold characteristics in top-down InGaAs/InAs heterojunction vertical nanowire tunnel FETs. IEEE Electron Device Lett. 38, 855–858 (2017).

Pala, M. G. & Esseni, D. Interface traps in InAs nanowire tunnel-FETs and MOSFETs−Part I: Model description and single trap analysis in tunnel-FETs. IEEE Trans. Electron Devices 60, 2795–2801 (2013).

Agarwal, S. & Yablonovitch, E. Band-edge steepness obtained from Esaki/backward diode current-voltage characteristics. IEEE Trans. Electron Devices 61, 1488–1493 (2014).

Fiori, G. et al. Electronics based on two-dimensional materials. Nat. Nanotechnol. 9, 768–779 (2014).

Roy, T. et al. Dual-gated MoS2/WSe2 van der Waals tunnel diodes and transistors. ACS Nano 9, 2071–2079 (2015).

Nourbakhsh, A., Zubair, A., Dresselhaus, M. S. & Palacios, T. Transport properties of a MoS2/WSe2 heterojunction transistor and its potential for application. Nano Lett. 16, 1359–1366 (2016).

Movva, H. C. P. et al. Room temperature gate-tunable negative differential resistance in MoS2/hBN/WSe2 heterostructures. In Proc. 2016 74th Annual Device Research Conference (DRC), 1–2. https://doi.org/10.1109/DRC.2016.7548486 (IEEE, 2016).

Roy, T. 2D-2D tunneling field-effect transistors using WSe2/SnSe2 heterostructures. Appl. Phys. Lett. 108, 08311 (2016).

Yan, R. et al. Esaki diodes in van der Waals heterojunctions with broken-gap energy band alignment. Nano Lett. 15, 5791–5798 (2015).

Shim, J. et al. Phosphorene/rhenium disulfide heterojunction-based negative differential resistance device for multi-valued logic. Nat. Commun. 7, 13413 (2016).

Pang, C.-S., Ilatikhameneh, H. & Chen Z. Gate tunable 2D WSe2 Esaki diode by SiNx doping. In Proc. 2017 75th Annual Device Research Conference (DRC), 1–2. https://doi.org/10.1109/DRC.2017.7999450 (IEEE, 2017).

Liu, X. et al. Homogenous molybdenum disulfide tunnel diode formed via chemical doping. Appl. Phys. Lett. 112, 183103 (2018).

Paletti, P., Seabaugh, A., Yue, R., & Hinkle, C. Electric double layer Esaki tunnel junction in a 40-nm-length, WSe2 channel grown by molecular beam epitaxy on Al2O3. In Proc. 2018 48th European Solid-State Device Research Conference (ESSDERC), 110–113. https://doi.org/10.1109/ESSDERC.2018.8486874 (IEEE, 2018).

Gao, J., Yu, G. & Heeger, A. J. Polymer light-emitting electrochemical cells with frozen p-i-n junction. Appl. Phys. Lett. 71, 1293–1295 (1997).

Fathipour, S., Paletti, P., Fullerton-Shirey, S. & Seabaugh, A. Demonstration of electric double layer pin junction. In Proc. 2016 74th Annual Device Research Conference (DRC), 1–2. https://doi.org/10.1109/DRC.2016.7548485 (IEEE, 2016).

Xu, H., Fathipour, S., Kinder, E. W., Seabaugh, A. C. & Fullerton-Shirey, S. K. Reconfigurable ion gating of 2H-MoTe2 field-effect transistors using poly (ethylene oxide)-CsClO4 solid polymer electrolyte. ACS Nano 9, 4900–4910 (2015).

Xu, K. et al. Reconfigurable pn junction formation and bandgap opening in bilayer graphene using polyethylene oxide and CsClO4 solid polymer electrolyte. In Proc. 2015 73rd Annual Device Research Conference (DRC) 173–174. https://doi.org/10.1109/DRC.2015.7175612 (IEEE, 2015).

COMSOL Multiphysics® v. 5.3: Semiconductor module, General form PDE, https://www.comsol.com.

Kilic, M. S., Bazant, M. Z. & Ajdari, A. Steric effects in the dynamics of electrolytes at large applied voltages. II. Modified Poisson–Nernst–Planck equations. Phys. Rev. E 75, 021503 (2007).

Wang, H. & Pilon, L. Accurate simulations of electric double layer capacitance of ultramicroelectrodes. J. Phys. Chem. C 115, 16711–16719 (2011).

Ueno, K. et al. Field-induced superconductivity in electric double layer transistors. J. Phys. Soc. Jpn. 83, 032001 (2014).

Zhang, Y., Suzuki, R. & Iwasa, Y. Potential profile of stabilized field-induced lateral p–n junction in transition-metal-dichalcogenides. ACS Nano 11, 12583–12590 (2017).

Zhang, Y. J., Ye, J. T., Yomogida, Y., Takenobu, T. & Iwasa, Y. Formation of a stable p–n junction in a liquid-gated MoS2 ambipolar transistor. Nano Lett. 13, 3023–3028 (2013).

Das, S. & Appenzeller, J. WSe2 field effect transistors with enhanced ambipolar characteristics. Appl. Phys. Lett. 103, 103501 (2013).

Balestra, F., Benachir, M., Brini, J. & Ghibaudo, G. Analytical models of subthreshold swing and threshold voltage for thin- and ultra-thin-film SOI MOSFETs. IEEE Trans. Electron Devices 37, 2303–2311 (1990).

Ciarrocchi, A., Avsar, A., Ovchinnikov, D. & Kis, A. Thickness-modulated metal-to-semiconductor transformation in a transition metal dichalcogenide. Nat. Commun. 9, 919 (2018).

Gutiérrez-Lezama, I., Reddy, B. A., Ubrig, N. & Morpurgo, A. F. Electroluminescence from indirect band gap semiconductor ReS2. 2D Mater. 3, 045016 (2016).

Melzer, K. et al. Characterization and simulation of electrolyte-gated organic field-effect transistors. Faraday Discuss. 174, 399 (2014).

Fathipour, S., Pandey, P., Fullerton-Shirey, S. & Seabaugh, A. Electric-double layer doping of WSe2 field-effect transistors using polyethylene-oxide cesium perchlorate. J. Appl. Phys. 120, 234902 (2016).

Walsh, L. A. & Hinkle, C. L. van der Waals epitaxy: 2D materials and topological insulators. Appl. Mater. Today 9, 504–515 (2017).

Yue, R. et al. Nucleation and growth of WSe2: enabling large grain transition metal dichalcogenides. 2D Mater. 4, 045019 (2017).

Walsh, L. A. et al. WTe2 thin films grown by beam-interrupted molecular beam epitaxy. 2D Mater. 4, 025044 (2017).

Acknowledgements

This work was supported, in part, by the Center of Low Energy Systems Technology (LEAST), a STARnet Semiconductor Research Corporation program sponsored by MARCO and DARPA. The authors would like to thank Tatyana Orlova and Sergei Rouvimov at the Notre Dame Integrated Imaging Facility for TEM specimen preparation and imaging.

Author information

Authors and Affiliations

Contributions

P.P and A.S. conceived the experiments. R.Y. performed the BG oxide deposition and MBE growth under the supervision of C.H. P.P. designed and fabricated the devices, performed the COMSOL simulations, and carried out the transport measurements. S.K.F.-S. and A.S. provided guidance for the model development. P.P and A.S analyzed the data and wrote the manuscript with inputs from all the authors.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Paletti, P., Yue, R., Hinkle, C. et al. Two-dimensional electric-double-layer Esaki diode. npj 2D Mater Appl 3, 19 (2019). https://doi.org/10.1038/s41699-019-0101-y

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41699-019-0101-y

This article is cited by

-

Creation of unexplored tunnel junction by heterogeneous integration of InGaAs nanowires on germanium

Scientific Reports (2022)

-

Computational study of transition metal dichalcogenide cold source MOSFETs with sub-60 mV per decade and negative differential resistance effect

npj 2D Materials and Applications (2022)

-

Intelligent control of nanoparticle synthesis on microfluidic chips with machine learning

NPG Asia Materials (2022)

-

Electrical Properties of 6 nm to 19 nm Thick Polyethylene Oxide Capacitors for Ion/Electron Functional Devices

Journal of Electronic Materials (2021)

-

Electric-double-layer p–i–n junctions in WSe2

Scientific Reports (2020)