Abstract

Nanoscience offers a unique opportunity to design modern materials from the bottom up via low-cost, solution processed assembly of nanoscale building blocks. These systems promise electronic band structure engineering using not only the nanoscale structural modulation, but also the mesoscale spatial patterning, although experimental realization of the latter has been challenging. Here, we design and fabricate a new type of artificial solid by stacking graphene on a self-assembled, nearly periodic array of nanospheres, and experimentally observe superlattice miniband effects. We find conductance dips at commensurate fillings of charge carriers per superlattice unit cell, which are key features of minibands that are induced by the quasi-periodic deformation of the graphene lattice. These dips become stronger when the lattice strain is larger. Using a tight-binding model, we simulate the effect of lattice deformation as a parameter affecting the inter-atomic hopping integral, and confirm the superlattice transport behavior. This 2D material-nanoparticle heterostructure enables facile band structure engineering via self-assembly, promising for large-area electronics and optoelectronics applications.

Similar content being viewed by others

Introduction

Band structure engineering is key to realizing next-generation electronic and optoelectronic devices. One promising approach toward this goal is superlattice modulation, i.e., engineering long-range periodic patterns to artificially tailor the electronic band structure. This artificial lattice can have a periodicity in the range of 1–50 nm, which is shorter than the electron mean free path and longer than the angstrom-level atomic bond length, inducing the formation of minibands. To date mainly two types of electronic superlattices have been demonstrated: (1) vertically stacked layers with alternating composition, widely used for quantum cascade lasers and infrared photodetectors1,2; (2) lateral two-dimensional (2D) Moiré superlattices composed of lattice-aligned graphene/hexagonal boron nitride (hBN) heterostructures,3,4,5,6 which are promising for plasmonic modulations and light-harvesting applications.7,8 However, both systems require lattice-matching conditions, which pose constraints on the choice of materials composition and the extent of device applications.

Self-assembly of solution processed nanoparticles is a low-cost method for nanostructure engineering, which can produce large-area close-packed superlattices having overall polycrystalline order and local crystalline domains.9,10,11 Despite the high structural quality, superlattice miniband effects have not been experimentally observed in these systems, largely due to the presence of defects on the (semiconducting) nanoparticle surfaces and the weak inter-particle electronic coupling.12,13,14 Here we demonstrate a new way to design a 2D superlattice device by integrating solution processed dielectric nanoparticles with 2D materials to form a heterostructure (Fig. 1a), which takes advantage of both the structural versatility of the nanoparticle assemblies and the high mobility of the 2D materials. We observe superlattice miniband conduction in a polycrystalline system where graphene (Gr) is quasi-periodically deformed on top of SiO2 nanospheres (NSs). We find that the size dispersion and imperfect ordering of the NSs induces broadening in the miniband density of states. While this effect is not ideal for applications where sharp states are needed (e.g., lasers and single-color LEDs), it can be beneficial for optoelectronic systems that require broadband modulation of the optical spectrum, such as optical modulators,15 photo-thermal conversion,16,17 infrared sensors,18 and optical communication.19 While currently we are using CVD grown graphene, this superlattice fabrication method is compatible with solution processed 2D materials.20 Fully solution processed superlattices can enable low-cost large-area applications.

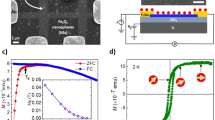

Device schematics and images. a Schematic of the strain superlattice device structure. SiO2 nanospheres (NSs) with 20 nm diameter are assembled on 300 nm SiO2/n++ Si substrate. Graphene is stacked on top of the NSs and contacted by 1 nm Cr/110 nm Au. Channel length and width are between 0.6–2.4 μm in all the fabricated devices. b Scanning electron microscopy (SEM) image of one Gr–NS superlattice device, showing the Au contacts, SiO2 nanospheres, and graphene on nanospheres. c High-resolution SEM images of a monolayer NS assembly, where each region enclosed by red dashed lines is a single-crystalline domain

Results and discussion

Device fabrication and electronic transport

We use SiO2 NSs for heterostructure fabrication because of their insulating nature, clean surface chemistry (terminated with hydroxyl groups and without organic capping molecules), and the ease of comparison with flat SiO2 substrates (same surface chemistry with hydroxyl group termination). The NSs are packed in a polycrystalline structure where each single-crystalline domain consists of tens to hundreds of NSs; within each domain the NSs are hexagonal close packed (Fig. 1b, c). Our previous study shows that, after stacking graphene on top of these spheres, Gr bends and stretches around the apex of the NSs, giving rise to a quasi-periodically varying strain pattern.21 Within the experimentally accessible NS diameter range of 20–200 nm (spheres will have irregular shape and large size dispersity if diameter is less than 20 nm), we found that the overall strain in graphene is largest for the smallest sphere diameter.21 Therefore, here we choose the NSs with 20 nm diameter to induce a strain superlattice in Gr and study the electronic transport. This Gr–NS system shows periodic strain variations in graphene with a peak-to-peak magnitude in the scale of ~2%.21

We fabricated back-gated 2-terminal devices with Au contacts (Fig. 1a, b), and measured the electronic transport behavior of the Gr–NS systems; we also studied control samples consisting of graphene on flat SiO2/Si substrate (see Methods for details). All the transport results shown here were obtained at 2 Kelvin. Figure 2a shows the conductance (G) as a function of gate voltage (VG) for two control devices (Gr on flat SiO2 substrate, labeled Gr1 and Gr2), which exhibit increasing conductance with gradually decreasing slope at both sides of the Dirac points (DPs). These are characteristic features of graphene-on-SiO2 devices due to the coexistence of long and short-range scatterers.22,23,24 Gr on NS devices (labeled Gr-NS1, 2, 3), in contrast, show emergent conductance dip/kink features in the G vs. VG curves (Fig. 2b). Remarkably, although the kink features occur at different gate voltages for separate devices, all of them are ~15 V away from their DPs. This same separation for different Gr–NS devices indicates that the conductance dips have the same origin. To remove the effect of the (doping induced) DP offsets and the device geometry on the transport characteristics, we plot the conductivity (σ) as a function of gate-tuned carrier density (n) for the same devices in Fig. 2c. Note that conductivity is defined as \(\sigma = G\frac{L}{W}\), where G is the conductance, L is the channel length, and W is the channel width (Supplementary Section 1.1 shows the values of L and W and the method to convert gate voltage to n). Now it is evident that all three Gr–NS devices show dip features near n = ±1 × 1012 cm−2 (corresponding to a VG position of ~15 V away from the DP), while the amplitude of the dips varies among different devices and between the electron and hole sides. Note that all the Gr–NS devices show nearly the same minimum conductivity at DPs (\(\sigma \cong 2\frac{{e^2}}{h}\)), indicating that all the devices have negligible amounts of random vacancy defects and cracks.

Experimental superlattice transport. a Conductance (G) vs. gate voltage (VG) curves for two control devices (Gr on flat SiO2) Gr1 and Gr2. b G vs. VG curves for three batches of Gr on 20 nm NS devices as labeled. c Conductivity (σ) vs. carrier density (n) for a control device (Gr1) and three Gr–NS superlattice devices. The conductivity of Gr1 is multiplied by a factor of 1/2 in order to fit to the same scale as other devices. d Normalized conductivity for the same devices shown in c (detailed normalization procedures discussed in Supplementary Section 1.2). Vertical dashed lines mark the positions of superlattice Dirac points (SDPs) in all the figures, corresponding to a carrier density of four electrons/holes per supercell. All the transport results shown here were obtained at T = 2 K

To further quantitatively compare the magnitude of the conductance kinks among different devices, we follow a well-developed protocol to normalize the conductance curves,22 which involves subtracting a series resistance (originating from contact resistance and short-range scatterers) from each curve to restore the linear background, and multiplying the curves by constant factors to normalize them to the same scale (Supplementary Section 1.2). As shown in Fig. 2d, after this normalization procedure, the control sample shows linear conductivity at both sides of the DP. The curves for all the Gr–NS devices perfectly overlap with that of the control sample at |n| > 1 × 1012 cm−2, and show clear slope-changing features at the characteristic carrier density of about ±1 × 1012 cm−2. The magnitude of the divergence from that of the control device is a measure of the amplitude of the conductance dips of the Gr–NS systems. Note that the electron and hole sides are processed separately for each curve, with different normalization factors, and therefore they do not necessarily align at the DP.

The position of the conductance dips matches with the commensurate filling of four electrons per superlattice unit cell (this number originates from the 4-fold spin and valley degeneracies in graphene). This can be seen by taking the lattice constant of the superlattice to be λ ~21 nm (~20 nm NS diameter and ~1 nm gap between adjacent NSs), and using the supercell area \(A = \sqrt 3 \lambda ^2{\mathrm{/}}2 \approx 4 \times 10^{ - 12}{\kern 1pt} {\mathrm{cm}}^2\). Then, one electron per supercell corresponds to a carrier density of n0 = 1/A = 2.5 × 1011 cm−2, and the dips occur at n = ±4n0 = ±1 ×1012 cm−2. The excellent match of the filling number with the theoretically expected value is strong evidence that the dip features are a consequence of superlattice effects, corresponding to superlattice Dirac points (SDPs). These SDPs occur at the mini-Brillouin-zone boundaries due to the superlattice modulation, where the small density of states leads to dips in conductance.4,5,6,25

From the perspective of materials design, the widely studied graphene/hBN system allows a maximum superlattice period of ~14 nm, limited by lattice mismatch conditions of the constituent layers.4,5,6 As a result, the SDP position of Gr/hBN systems is at least ~2.4 ×1012 cm−2. Our Gr–NS system offers a route to tune SDP positions in a larger range, including small carrier densities (<2 × 1012 cm−2) that are easily accessible via gate tuning. To further demonstrate this capability, we fabricated and measured a Gr–NS device where the NSs have a diameter of ~50 nm. Transport results reveal an intriguing conductance oscillation with a periodicity of ~4.5 × 1010 cm−2, corresponding to one electron per supercell (Supplementary Fig. S2c, d), where the supercell now corresponds to the 50 nm NSs. Note that the same 1 e−/supercell oscillation feature (~2.5 × 1011 cm−2 periodicity) is also present in the 20 nm system Gr–NS1, in addition to the SDPs at 4 e−/supercell (~1 × 1012 cm−2) (Supplementary Fig. S2a, b). Overall, the 4 e−/supercell feature occurs in all of the measured devices with 20 nm spheres, while the 1 e−/supercell feature only occurs in some of the devices. Similar transport behavior has recently been observed in bilayer graphene and trilayer graphene–hBN superlattices, and explained as electron correlation effects.26,27 While the exact mechanism behind these transport features is still under study and is beyond the scope of this paper, the dip/oscillation features at commensurate filling for Gr–NS systems having two different NS sizes are strong evidence of superlattice effects.

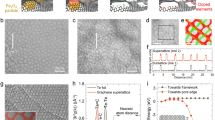

To examine the effect of strain on the superlattice transport properties, it is desirable to deliberately modify the strain of a device while leaving other parameters unaltered, and observe the change in transport features. Previous work shows that temperature cycling can lead to compressive strain in an initially strain-free flake of Bi2Se3 contacted by electrodes.28 Here we use the same approach to alter the strain properties of our system. After cooling down from 300 K to 2 K, and then warming up to 300 K again, we find that, via Raman spectroscopy, the doping remains nearly the same while the spatially averaged tensile strain decreases by ~20% (Fig. 3a, Supplementary Section 1.5). The actual change of the nanoscale strain variation amplitude, or the RMS (root mean square) strain, can be much larger than the shift of average strain (Supplementary Section 1.5, Tables S2 and S3). Meanwhile, transport measurements of a Gr–NS device (Gr–NS2) reveal that the superlattice dip feature becomes much weaker after temperature cycling, compared to the same device before the thermal process (Fig. 3b, c). From the transport results, we also extract the mobility values (proportional to the slope of the curves for n < −1 × 1012 cm−2) and find it to have only a minor change (~6% decrease) after temperature cycling, revealing that the modifications of structural defects are small. Therefore, we conclude that strain modulation is likely the major factor contributing to superlattice transport features in the Gr–NS devices.

Experimental strain manipulation and the effect on superlattice transport. a Correlation analysis of the measured Raman G and 2D peak positions, revealing a decrease of spatially averaged strain by 20% ± 4.9% after temperature cycling. In contrast, the average doping value shows negligible change (an increase of 2.3% ± 8.8%). Each point represents a spectrum obtained at an optical pixel with a size of ~0.5 × 0.5 μm2 (details in Supplementary Section 1.5). b Conductivity vs carrier density for Gr–NS2, after the first cool down to 2 K (purple curve), and after warming up to 300 K then cooling down to 2 K again (dark blue curve). c Normalized conductivity for the same devices shown in b, and the control device Gr1 (black curve, same as that in the left panel of Fig. 2d). The curves are expanded to a carrier density range close to the SDP, and the kink angles of the Gr–NS2 device before and after temperature cycling are labeled as θ1 and θ2, respectively

In Fig. 3c, we show how the amplitude of the conductance kinks at SDPs can be quantified by the slope changing angle in the normalized conductivity curves (θ1 and θ2 for Gr–NS2 before and after temperature cycling, respectively). We observe that θ1 > θ2, which quantitatively confirm the weakening of superlattice modulations. This conductance normalization and “kink angle” method can be generally used to quantify the amplitude of broad conductance dip features in polycrystalline or polydisperse superlattice systems.

In addition to the temperature cycling studies, to decisively prove the strain effect on superlattice transport, we prepared an extra control sample where 20 nm SiO2 NSs are assembled on top of graphene on a flat SiO2 substrate. Compared to the graphene-on-NS samples, this control sample is expected to have similar amounts of impurity, doping, and scattering at the graphene–NS interface, but strain will be absent since graphene lies on the flat substrate. Electronic transport results, shown in Supplementary Fig. S3, reveals that a NS-on-graphene device exhibit no conductance dip feature. This result further proves that: (1) the conductance dip features of the Gr–NS devices are due to superlattice effects, instead of random scattering induced by the NSs; (2) strain modulation is the key factor contributing to the superlattice effects in the Gr–NS systems.

Quantum transport simulations

While our previous work has revealed periodic strain variations in the Gr–NS systems,21 and now we have experimentally observed the effect of strain on electronic transport in the superlattice (Fig. 3), it is still worth to theoretically examine all the possible factors that can contribute to superlattice transport. One possibility is doping modulation. It is known that random charged impurities are present on the SiO2 surface, which induce p-type doping and charge fluctuations (or charge puddles) in the graphene layer on top.23,24,29,30,31,32 In our Gr–NS samples, the random charged impurities (with a concentration ni) on the NS surfaces, together with the spatial variation of Gr to NS distance, determine the potential distribution of the graphene. From our experimental transport results, we estimate that ni ~7 × 1011 cm−2 (Supplementary Section 1.6), which agrees with previous reports.23,24,29,30,31 This corresponds to ~3 charged impurities per supercell on average, given that the NS diameter is only 20 nm. Considering the random, discrete, and sparse distribution of these impurities, we expect the induced potential modulation in graphene to be mostly random and produce no superlattice effects. This is confirmed by our Coulomb potential and quantum transport simulations (Supplementary Section 2.5).

Another possible superlattice modulation factor is the gate-induced electrostatic potential variation in graphene resulting from its inhomogeneous dielectric environment. However, due to the small height variations of graphene (~2 nm, determined from atomic force microscopy) and the small size of spheres (20 nm) compared to the thickness of the flat SiO2 dielectric layer (300 nm), we expect the gate-tuned carrier density in graphene to be nearly homogeneous. Our electrostatic simulation confirms that, within the experimental range of gate voltage, the gate-induced variation in electrostatic potential is smaller than the random potential fluctuations in Gr caused by the charged impurities on the SiO2 surface (Supplementary Section 1.7). As a result, the electrostatic contribution to superlattice transport should be negligible. This is in agreement with our experimental result shown in Fig. 2b, where we find a strong SDP feature for Gr–NS2 on the hole side occurring near zero VG, revealing that superlattice transport can occur without any electrostatic modulation.

To further quantify the effect of strain variations on carrier transport, we perform tight-binding transport simulations incorporating the experimentally relevant NS size and distribution and Gr strain variation parameters (details in Supplementary Sections 2.1 and 2.2). We use the following formula to relate the bond length to the hopping parameter (t) in the tight binding Hamiltonian:

where a and l are the bond length of the unstrained and strained graphene, respectively, and β = 3.37 is a constant parameter.33 We chose a range of strain magnitude, and simulate the conductance of the Gr–NS system with both single-crystalline and polycrystalline packing structures (Fig. 4a, b). Note that we directly imported the experimentally imaged NS packing profile for simulation of the polycrystalline system, shown in the inset of Fig. 4b (see also Supplementary Fig. S11). The unstrained graphene (Gr on flat SiO2 substrate) system shows the standard transport features of graphene with no superlattice conductance dips. When strain is added, SDPs appear at the expected energy levels, and become more evident as strain is increased, for both the single-crystalline and polycrystalline systems. The main difference between these two systems is that the polycrystalline devices exhibit broader conductance dips due to the structural disorder. The simulation results on the polycrystalline system are in good agreement with the experimental data in Fig. 2b–d, and imply that the variations in the magnitude of the dip features in different experimental Gr–NS devices can be attributed to differences in strain amplitudes. For example, comparing Fig. 2c, d with Fig. 4b, we can roughly estimate that the RMS strain values of Gr–NS2 and Gr–NS3 are ~2% and ~1% (by comparing the kink angles), respectively. Other factors, such as fluctuations in charge doping, mobility, and NS ordering are either negligible or do not correlate with the change of dip features (Supplementary Section 1.8). The strain variation among different samples is likely due to the device fabrication and cooling down processes.

Quantum transport simulations. a Simulated conductance (G) vs. energy (E) curves for graphene on single crystalline NSs (packing structure shown in the inset), with different RMS strain values of 0, 0.28%, 1.11%, 2.02%, 2.94% from top to bottom (black to red) (details shown in Supplementary Section 2.3). b Simulated G vs. E curves for graphene on polycrystalline NSs. The simulated NS packing structure, as shown in the inset, is adopted from our experimental image. From top to bottom (black to red), the curves correspond to RMS strain values of 0, 0.99%, 1.42%, 1.86%, 2.75%, 3.64% (details shown in Supplementary Section 2.4). Vertical dashed lines mark the expected SDP position at \(E_{{\mathrm{SDP}}} = \pm \frac{{h\nu _F}}{{\sqrt 3 \lambda }} = \pm 0.11{\kern 1pt} {\mathrm{eV}}\), where h is the Planck constant and νF = 1 × 106 m/s is the Fermi velocity of graphene3

In summary, we have created a large-area applicable superlattice device by stacking graphene on solution processed assemblies of SiO2 NSs. Electronic transport measurements reveal strain-tunable conductance dips due to superlattice miniband effects. Key evidences for superlattice transport in the Gr–NS devices are: (1) conductance dips occur at 4e− per supercell for all the Gr–NS devices, which diminish when strain is reduced; (2) control devices of flat Gr and NS-on-flat Gr do not show conductance dips; (3) transport simulations of Gr–NS systems incorporating the actual polycrystalline NS packing structure reveal strain-dependent conductance dips, similar to the experimental results.

We expect that our hybrid heterostructure, combining solution-processed, self-assembled nanoparticle superlattices, and atomically thin 2D materials (with superior flexibility compared to bulk34,35,36,37), will be a powerful framework to design a variety of “artificial solids” that enable band structure engineering via real space patterning. These superlattice devices are cost-effective to manufacture, and are promising for large-area, broadband optoelectronic applications such as optical modulators, infrared sensors, and photothermal converters.15,16,17,18,19

Materials and methods

Sample preparation

SiO2 NSs with 20 nm diameter were purchased from nanoComposix, product number SISN20-10M. The surfaces of these NSs are clean with only hydroxyl groups covering them (no organic capping ligands). The NSs were dispersed in water with a concentration of 5 mg/mL. 300 nm SiO2/n++ Si substrates were cleaned by acetone, IPA, and O2 plasma, followed by spin-coating of the NSs. The sample was then baked on hotplate at 170 °C for 20 min to remove the residual water. The NSs were attached to the SiO2/Si surface with sub-monolayer coverage on the whole substrate, and closely packed monolayer domains in the scale of microns to tens of microns were observed. CVD graphene (purchased from ACS Material) was transferred to the NS substrate using the standard wet-transfer techniques,38 followed by critical point drying to avoid ripping of graphene. We observed both regions of graphene on top of the NS monolayers and regions of Gr on the flat SiO2 substrate on each sample.

Device fabrication and measurements

Confocal Raman spectroscopy was performed to identify defect-free areas of graphene for device fabrication. E-beam lithography was performed to define 2-terminal electrodes for both the Gr–NS regions and the flat Gr regions, followed by thermal evaporation of 1 nm Cr/110 nm Au. The gap between each pair of leads is between 0.6–2.4 μm, and these leads provide structural support for the graphene in the channel region during the following fabrication steps. This is important for the Gr–NS systems where free-standing regions of graphene (between the neighboring NSs) are fragile. For the same reasons, previous high-quality transport measurements of free-standing graphene were performed on 2-terminal devices instead of multi-terminal Hall bar devices.39 Subsequently, another e-beam lithography step was performed to define etch patterns, and O2 plasma was used to etch graphene into rectangular areas between the 2-terminal leads. After each lithography and lift-off step, the samples were dried in a critical point dryer to avoid structural degradation. The completed devices were wire-bonded and measured in a physical property measurement system under vacuum conditions. An AC current source (10 nA, 17 Hz) was applied to the Au source/drain leads to measure the resistance using a lock-in amplifier, while gate voltage was applied to the Si substrate to tune the carrier density.

Raman spectroscopy

Confocal Raman spectroscopy was performed using a Nanophoton Raman 11 system at room temperature, with an excitation wavelength of 532 nm. 100× objective was used and the laser power was between 0.5–1 mW. All the measured spectra were calibrated using the emission lines of a neon lamp.

Transport simulations

A tight-binding model was used to construct the model Hamiltonian for graphene and observables were computed using non-equilibrium Green’s function formalism. The form of the Hamiltonian and simulation details are available in Supplementary Section 2.

Data availability

The data used in this study are available upon reasonable request from the corresponding author Y.Z. (yjz@illinois.edu).

References

Faist, J. et al. Quantum cascade laser. Science 264, 553–556 (1994).

Tsu, R. Superlattice to Nanoelectronics. (Elsevier, Oxford, 2005).

Yankowitz, M. et al. Emergence of superlattice Dirac points in graphene on hexagonal boron nitride. Nat. Phys. 8, 382–386 (2012).

Ponomarenko, L. A. et al. Cloning of Dirac fermions in graphene superlattices. Nature 497, 594–597 (2013).

Dean, C. R. et al. Hofstadter’s butterfly and the fractal quantum Hall effect in moiré superlattices. Nature 497, 598–602 (2013).

Hunt, B. et al. Massive Dirac fermions and Hofstadter butterfly in a van der Waals heterostructure. Science 340, 1427–1430 (2013).

Ni, G. X. et al. Plasmons in graphene moiré superlattices. Nat. Mater. 14, 1217–1222 (2015).

Wu, S. et al. Multiple hot-carrier collection in photo-excited graphene Moiré superlattices. Sci. Adv. 2, e1600002 (2016).

Dong, A. G., Chen, J., Vora, P. M., Kikkawa, J. M. & Murray, C. B. Binary nanocrystal superlattice membranes self-assembled at the liquid–air interface. Nature 466, 474–477 (2010).

Boneschanscher, M. P. et al. Long-range orientation and atomic attachment of nanocrystals in 2D honeycomb superlattices. Science 344, 1377–1380 (2014).

Cargnello, M. et al. Substitutional doping in nanocrystal superlattices. Nature 524, 450–453 (2015).

Kagan, C. R. & Murray, C. B. Charge transport in strongly coupled quantum dot solids. Nat. Nanotech. 10, 1013–1026 (2015).

Alimoradi Jazi, M. et al. Transport properties of a two-dimensional PbSe square superstructure in an electrolyte-gated transistor. Nano Lett. 17, 5238–5243 (2017).

Zhang, Y. et al. Molecular oxygen induced in-gap states in PbS quantum dots. ACS Nano 9, 10445–10452 (2015).

Liu, M. et al. A graphene-based broadband optical modulator. Nature 474, 64–67 (2011).

Rinnerbauer, V. et al. Superlattice photonic crystal as broadband solar absorber for high temperature operation. Opt. Express 22, A1895–A1906 (2014).

Zhou, L. et al. Self-assembly of highly efficient, broadband plasmonic absorbers for solar steam generation. Sci. Adv. 2, e1501227 (2016).

Deng, B. et al. Coupling-enhanced broadband mid-infrared light absorption in graphene plasmonic nanostructures. ACS Nano 10, 11172–11178 (2016).

Bao, Q. & Loh, K. P. Graphene photonics, plasmonics, and broadband optoelectronic devices. ACS Nano 6, 3677–3694 (2012).

Wang, S. et al. High mobility, printable, and solution-processed graphene electronics. Nano Lett. 10, 92–98 (2010).

Zhang, Y. et al. Strain modulation of graphene by nanoscale substrate curvatures: a molecular view. Nano Lett. 18, 2098–2104 (2018).

Morozov, S. V. et al. Giant intrinsic carrier mobilities in graphene and its bilayer. Phys. Rev. Lett. 100, 016602 (2008).

Hwang, E. H., Adam, S. & Das Sarma, S. Carrier transport in two-dimensional graphene layers. Phys. Rev. Lett. 98, 186806 (2007).

Samaddar, S., Yudhistira, I., Adam, S., Courtois, H. & Winkelmann, C. B. Charge puddles in graphene near the Dirac point. Phys. Rev. Lett. 116, 126804 (2016).

Park, C. H., Yang, L., Son, Y. W., Cohen, M. L. & Louie, S. G. New generation of massless Dirac fermions in graphene under external periodic potentials. Phys. Rev. Lett. 101, 126804 (2008).

Cao, Y. et al. Correlated insulator behaviour at half-filling in magic-angle graphene superlattices. Nature 556, 80–84 (2018).

Chen, G. et al. Gate-tunable Mott insulator in trilayer graphene-boron nitride moiré superlattice. Preprint at https://arxiv.org/abs/1803.01985 (2018).

Charpentier, S. et al. Induced unconventional superconductivity on the surface states of Bi2Te3 topological insulator. Nat. Commun. 8, 2019 (2017).

Adam, S., Hwang, E. H., Galitski, V. M. & Das Sarma, S. A self-consistent theory for graphene transport. Proc. Natl Acad. Sci. USA 104, 18392–18397 (2007).

Rossi, E. & Das Sarma, S. Ground state of graphene in the presence of random charged impurities. Phys. Rev. Lett. 101, 166803 (2008).

Zhang, Y., Brar, V. W., Girit, C., Zettl, A. & Crommie, M. F. Origin of spatial charge inhomogeneity in graphene. Nat. Phys. 5, 722–726 (2009).

Chen, J.-H., Jang, C., Xiao, S., Ishigami, M. & Fuhrer, M. S. Intrinsic and extrinsic performance limits of graphene devices on SiO2. Nat. Nanotech. 3, 206–209 (2008).

Pereira, V. M., Castro Neto, A. H. & Peres, N. M. R. Tight-binding approach to uniaxial strain in graphene. Phys. Rev. B 80, 045401 (2009).

Lee, C. et al. Frictional characteristics of atomically thin sheets. Science 328, 76–80 (2010).

Lee, C., Wei, X., Kysar, J. W. & Hone, J. Measurement of the elastic properties and intrinsic atrength of monolayer graphene. Science 321, 385–388 (2008).

Yamamoto, M. et al. “The princess and the pea” at the nanoscale: wrinkling and delamination of graphene on nanoparticles. Phys. Rev. X 2, 041018 (2012).

Wei, Q. & Peng, X. Superior mechanical flexibility of phosphorene and few-layer black phosphorus. Appl. Phys. Lett. 104, 251915 (2014).

Suk, J. W. et al. Transfer of CVD-grown monolayer graphene onto arbitrary substrates. ACS Nano 5, 6916–6924 (2011).

Bolotin, K. I., Ghahari, F., Shulman, M. D., Stormer, H. L. & Kim, P. Observation of the fractional quantum Hall effect in graphene. Nature 462, 196–199 (2009).

Acknowledgements

We thank J.W. Lyding for valuable discussions. Y.Z. was supported by a Beckman Institute Postdoctoral Fellowship at the University of Illinois at Urbana-Champaign, with funding provided by the Arnold and Mabel Beckman Foundation. N.M. acknowledge support from the NSF-MRSEC under Award Number DMR-1720633. Y.Z. acknowledge research support from the National Science Foundation under Grant No. ENG-1434147. M.J.G. acknowledge support from the National Science Foundation under Grant No. ECCS-1351871. This work was carried out in part in the Frederick Seitz Materials Research Laboratory Central Facilities and in the Beckman Institute at the University of Illinois.

Author information

Authors and Affiliations

Contributions

Y.Z. conceived the experiment. Y.Z. designed and fabricated devices, and carried out transport measurements. Y.K. and M.J.G. performed the transport simulations. Y.Z., Y.K., M.J.G., and N.M. analyzed the data and wrote the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Zhang, Y., Kim, Y., Gilbert, M.J. et al. Electronic transport in a two-dimensional superlattice engineered via self-assembled nanostructures. npj 2D Mater Appl 2, 31 (2018). https://doi.org/10.1038/s41699-018-0076-0

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41699-018-0076-0

This article is cited by

-

Tunable magnetic confinement effect in a magnetic superlattice of graphene

npj 2D Materials and Applications (2024)

-

A prospective future towards bio/medical technology and bioelectronics based on 2D vdWs heterostructures

Nano Research (2020)