# **scientific** reports

# **OPEN** Three-dimensional vertical structural electrochemical random access memory for high-density integrated synapse device

Hyejin Kim¹, Jongseon Seo¹, Seojin Cho¹, Seonuk Jeon², Jiyong Woo² & Daeseok Lee¹⊠

Three-terminal (3T) structured electrochemical random access memory (ECRAM) has been proposed as a synaptic device based on improved synaptic characteristics. However, the proposed 3T ECRAM has a larger area requirement than 2T synaptic devices; thereby limiting integration density. To overcome this limitation, this study presents the development of a high-density vertical structure for the 3T ECRAM. In addition, complementary metal-oxide semiconductor (CMOS)-compatible materials and 8-inch wafer-based CMOS fabrication processes were utilized to verify the feasibility of mass production. The achievements of this work demonstrate the potential for high-density integration and mass production of 3T ECRAM devices.

Recently, unstructured data such as videos, images, sounds, and portable document format files have been growing at an exponential rate, leading to a significant increase in the amount of data that needs to be processed. The efficient processing of such vast amounts of data requires faster data processing with low-power consumption. However, the conventional Von-Neumann architecture, which processes data via a series of operations between the central processing unit and memory unit, has a bottleneck effect that causes slow data processing<sup>2–5</sup>. To overcome this, researchers have explored neuromorphic computing systems utilizing parallel data processing, which enables faster and more energy-efficient processing of humungous amounts of data<sup>6.7</sup>. To implement such neuromorphic computing systems in hardware, each synaptic device in the array must satisfy several requirements, such as linear and symmetric conductance modulation under identical pulse bias, wide on/off conductance ratio, data retention, and endurance. Based on these requirements, precise and energy-efficient computing processes (involving training and inference) can be achieved. Previous studies have extensively investigated various simple and high-density two-terminal (2T) memory devices, such as resistive random access memory, phase-change memory<sup>10</sup>, and ferroelectric random access memory<sup>11</sup>. However, the previously proposed 2T synaptic devices exhibit non-ideal synaptic characteristics that degrade system accuracy, including abrupt conductance changes, small on/off ratio, sneak current issues in arrays, and reliability issues (data retention, and endurance)<sup>12-15</sup>.

To address these limitations, three terminals (3T) structured synaptic devices have been proposed, particularly the ion-based electrochemical random access memory (ECRAM), which operates via ionic electrochemical reactions. Compared to 2T synaptic devices, 3T ECRAMs exhibit significantly improved synaptic characteristics, such as low-power operation, larger on/off ratio, linear conductance modulation, more reliable retention, and excellent endurance 16,17. Among the ECRAMs with various ions, oxygen ion based ECRAMs (OxECRAMs) have the added advantage of using CMOS fabrication processes<sup>18,19</sup>. Despite the improved synaptic characteristics exhibited by OxECRAM, there is still an obstacle in terms of the integration density. Compared to 2T synaptic devices, the 3T OxECRAM requires a larger area owing to its 3T structure. Therefore, in this research, we propose a vertical structure for the 3T OxECRAM (V-ECRAM), which can overcome the limitation in integration density. We utilized 8-inch wafer-based CMOS fabrication processes through a semiconductor fab to verify the feasibility of mass production.

<sup>1</sup>Department of Electronic Materials Engineering, Kwangwoon University, Seoul 01897, Republic of Korea. <sup>2</sup>School of Electronic and Electrical Engineering, Kyungpook National University, Daegu 41566, South Korea. <sup>™</sup>email: leeds@kw.ac.kr

### Methods

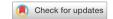

The V-ECRAM was fabricated using an 8-inch wafer-based CMOS fabrication process. Ti/TiN/Ti/SiO $_2$ /Ti/TiN /SiO $_2$  stacks were formed on a 1,000 nm thick thermally grown SiO $_2$ . Both Ti and TiN layers were deposited using a sputtering system while the SiO $_2$  layer was formed via plasma-enhanced chemical vapor deposition. The two TiN layers play the role of the source and drain electrodes, respectively. The Ti layers were deposited to serve as an adhesion layer for the TiN and SiO $_2$  layers. Subsequently, it was etched in the shape of a via-hole with 1.5  $\mu$ m diameter. Finally, the channel/electrolyte/oxygen reservoir/gate electrode were deposited on the side wall of the via-hole.

For all cases, a WO $_3$  (60 nm) channel was deposited via reactive sputtering using a WO $_3$  target in Ar and O $_2$  mixed ambient gas. Thereafter, an approximately 3 nm Yttria-stabilized zirconia (YSZ) electrolyte and approximately 230 nm of Ta $_2$ O $_5$  oxygen reservoir were deposited in Ar ambient gas. Lastly, W layer (50 nm) was deposited as the gate electrode in an Ar ambient gas. The WO $_3$  and YSZ were deposited at working pressures of 5 mTorr and 40 mTorr, respectively. Moreover, Ta $_2$ O $_5$  and W were deposited at 10 mTorr. The fabrication schematic and flow diagram are depicted in Fig. 1a,b.

Electrical analyses were conducted using a semiconductor parameter analyzer (HP 4156A) and pulse generator (Agilent 81110A). A series of positive and negative identical pulses were applied to the gate electrode and read operation was conducted on the source-drain electrode by applying read bias. During the writing process, all electrical measurements were performed with a common ground for both the source and drain, while applying gate bias. During the reading process, only the source was grounded, a read bias ( $V_{SD} = 0.5 \text{ V}$ ) was applied to the drain. For each sample, all the conditions during fabrication and electrical analyses were optimized to achieve the best synaptic characteristics.

### **Results and Discussion**

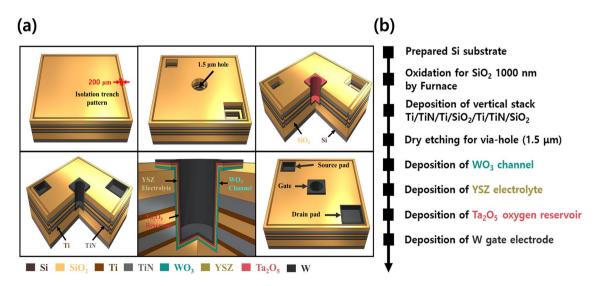

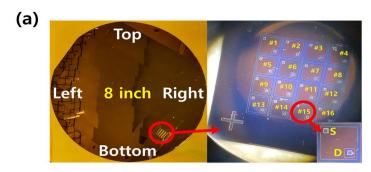

In this study, we propose a 3D vertical structure to overcome the limitations in integration density of 3T OxE-CRAM. Compared to the existing 3T-based ECRAMs, which occupy more than  $10F^2$  of a single cell<sup>20,21</sup>, the proposed V-ECRAM has the advantage of being reduced to  $4F^2$  because the source and drain are vertically stacked. To realize this, the 3D vertical structure was fabricated using an 8-inch fabrication process (Fig. 2a). Figure 2b shows the transmission electron microscope (TEM) image and energy dispersive x-ray spectrometer (EDS) mapping of the fabricated 3D vertical structure. These results confirm that  $_{22}$  Ti/TiN/Ti/SiO $_2$ /Ti/TiN/SiO $_2$  stacks were properly deposited on the thermally grown SiO $_2$  substrate with a thickness of 1,000 nm. The WO $_3$ , YSZ, Ta $_2$ O $_5$ , and W of CMOS compatible materials were sequentially deposited as channel, electrolyte, oxygen reservoir, and gate electrode on the side wall of via-hole with 1.5  $\mu$ m diameter formed via typical dry etching. The device manufacturing process is described in detail in Fig. 1 and the "Methods" Section. The possibility of high-density integration and mass production of the synapse device was confirmed by successfully fabricating a 3T (gate, source, and drain)-based V-ECRAM.

The operation mechanism of V-ECRAM is the same as that of the oxygen based ECRAM reported so far<sup>22,23</sup>. When positive bias is applied to the gate electrode, oxygen ions de-doped from the channel layer migrated the oxygen reservoir through the electrolyte layer, increasing the conductance of the channel layer (potentiation process). On the contrary, when negative bias is applied, oxygen ions are doped from the oxygen reservoir to the channel layer, resulting in a depression process in which the conductance of the channel layer is reduced. Based on this operation mechanism, the electrolyte should act as an ionic path between the channel and the oxygen reservoir layer to facilitate the movement of oxygen ions<sup>20,24</sup>. Therefore, we used YSZ with excellent ionic conductivity as the electrolyte<sup>19</sup>, and the YSZ layer was controlled to optimize device performance.

**Figure 1.** (a) Fabrication schematic image and (b) flow diagram of V-ECRAM manufactured using a three-dimensional vertical structure wafer.

**Figure 2.** (a) 8-inch wafer with 3D vertical structure for high-density and mass production. There are  $4 \times 4$  cells (total 16 cells) in one die. (b) EDS mapping and cross-sectional TEM image of 3D vertical structure. The results show that Ti/TiN/Ti/SiO $_2$ /Ti/TiN/SiO $_2$  stacks were properly deposited on the thermally grown SiO $_2$  substrate.

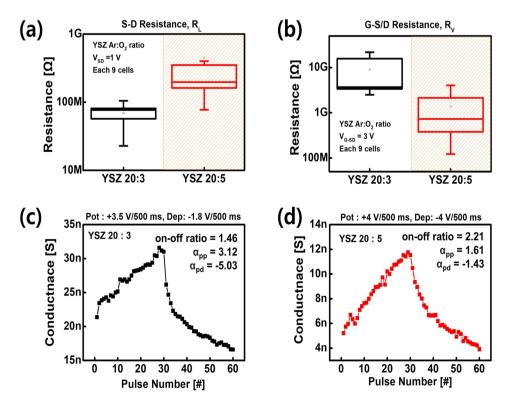

The ratio of Ar and  $O_2$  mixed ambient gas was controlled to optimize the YSZ electrolyte layer. Figure 3 presents a comparison of the characteristics of Ar:  $O_2 = 20$  sccm: 3 sccm and 20 sccm: 5 sccm, which were named YSZ 20:3 and YSZ 20:5, respectively. The source-drain (lateral resistance,  $R_L$ ) and gate-source/drain resistance (vertical resistance,  $R_V$ ) in the initial state, which varies with the  $O_2$  ratio, are shown in Fig. 3a,b. Thus, as the  $O_2$  ratio of YSZ increases,  $R_L$  increases and  $R_V$  decreases. For  $R_L$ , it can be explained that oxygen ions move

**Figure 3.** Nine cells distribution of (a) lateral (source-drain) and (b) vertical (gate-source/drain) resistance. The potentiation-depression of (c) YSZ 20:3 and (d) YSZ 20:5 for synaptic characteristic.

to a more stable material owing to the difference in Gibbs free energy between the WO<sub>3</sub> channel and the YSZ electrolyte during the deposition of YSZ layer. The Gibbs free energy for oxide formation of each material is as follows: YSZ (-1755.26 kJ/mol) < WO<sub>3</sub> (-756.7 kJ/mol)<sup>25,26</sup>. Consequently, oxygen ions de-doped from the channel layer during YSZ electrolyte deposition are absorbed into the YSZ electrolyte layer with a more stable state. When the O<sub>2</sub> ratio increases from YSZ 20:3 to 20:5, the oxygen vacancies in the YSZ layer decrease during the deposition of the YSZ layer, resulting in a relative decrease in the amount of oxygen ions absorbed from the WO<sub>3</sub> channel layer to the YSZ electrolyte layer. Accordingly, in the case of YSZ 20:5, the oxygen ions in the WO<sub>3</sub> channel layer are larger than those of YSZ 20:3, which increases R<sub>L</sub>, which is the resistance between the source and drain (Fig. 3a).

In contrast,  $R_V$  decrease as the  $O_2$  ratio increases, primarily because YSZ has the characteristics of a p-type semiconductor<sup>27</sup>. Therefore, as the  $O_2$  ratio increases from YSZ 20:3 to 20:5, the resistance of the YSZ layer decreases, reducing the overall  $R_V$  (Fig. 3b). Both YSZ 20:3 and 20:5 have significantly higher  $R_V$  than  $R_L$ . In other words, the channel conductance can be evaluated without the effect of gate leakage when reading the channel conductance.

The potentiation and depression were measured to evaluate the synaptic characteristics of the optimized device. Once a pulse was applied to the gate electrode, a read voltage ( $V_{SD} = 0.5 \text{ V}$ ) was applied to the source and drain to read the conductance of the channel. The gate pulse amplitude and width of each device are +3.5 V/-1.8 V, 500 ms for YSZ 20:3 and +4 V/-4 V, 500 ms for YSZ 20:5, which is optimized for each device. Furthermore, the linearity parameter ( $\alpha$ ) was setted to evaluate the linearity of the weight-update curve, as follows.

$$G = \begin{cases} ((G_{\text{MAX}}^{\alpha} - G_{\text{MIN}}^{\alpha}) \times \omega + G_{\text{MIN}}^{\alpha})^{\frac{1}{\alpha}}) & \text{if } \alpha \neq 0, \\ G_{\text{MIN}} \times (G_{\text{MAX}}/G_{\text{MIN}})^{\omega} & \text{if } \alpha = 0. \end{cases}$$

(1)

$$G_{MAX}/G_{MIN}$$

(2)

Where,  $G_{MAX}$  and  $G_{MIN}$  are maximum conductance state and minimum conductance state, respectively, and  $\omega$  is an internal variable which ranges from 0 to 1. The ideal case is when  $\alpha=1$ . Based on Equation (1), the linearity of potentiation ( $\alpha_{pp}$ ) and depression ( $\alpha_{pd}$ ) was calculated. As a result of evaluating the linearity parameter according to the Ar:O<sub>2</sub> ratio, the  $\alpha_{pp}$  and  $\alpha_{pd}$  of the YSZ 20:5 is 1.61, -1.43, respectively. In addition, the on/off ratio was obtained based on Equation (2). The on/off ratio of the YSZ 20:5 is 2.21, which exhibits a more improved synaptic characteristics than YSZ 20:3 (Fig. 3c,d).

The relatively lower vertical resistance of the YSZ 20:5 is the reason for the better performance compared to the YSZ 20:3. The voltage drop across the YSZ layer is relatively small in YSZ 20:5. Therefore, the electric field applied to the channel is larger. Consequently, the migration of doped and de-doped oxygen ions in the channel becomes more active and exhibits stable characteristics. Furthermore, the porosity of the YSZ layer increases when the Ar:O<sub>2</sub> ratio increases in the process of deposition of the YSZ layer. Therefore, in YSZ 20:5, the migration path of the oxygen ions is formed to facilitate the ion movement, and this leads to increase the ion mobility. As a result, YSZ 20:5 has a more linear and symmetrical conductance change in the channel layer and a larger on/off ratio, so that improved synaptic characteristics can be achieved. However, the on/off ratio is still one of the important synaptic characteristics to be improved. To overcome this limitation, there is a method of reducing the thickness of the gate and channel layer. By reducing the thickness between the gate and channel layer, a stronger electric field will be applied to the channel when the gate bias is applied. This leads to increase the ion movement, thereby increasing the on/off ratio.

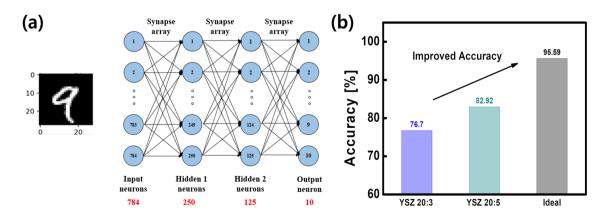

A pattern recognition simulation comprising four-layers was performed to verify the system-level performance of the V-ECRAM. The neural network was constructed with an input layer (784 neuron nodes), hidden layer 1 (250 neuron nodes), hidden layer 2 (125 neuron nodes), and output layer (10 neuron nodes) (Fig. 4a). The neuron node of each layer was connected to the next neuron node via a synapse device. We used the Modified

**Figure 4.** MNIST pattern recognition accuracy of the YSZ 20:3 and YSZ 20:5. (a) Schematic of four-layer neural network. MNIST dataset pattern recognition accuracy was evaluated by 784 inputs  $\times$  250 first hidden  $\times$  125 second hidden  $\times$  10 output neurons. (b) Pattern recognition accuracy for YSZ 20:3, YSZ 20:5, and ideal case.

|                       | Reference <sup>31</sup> | Reference <sup>32</sup> | This work       |

|-----------------------|-------------------------|-------------------------|-----------------|

| Type                  | Two-terminal            | Two-terminal            | Three-terminal  |

| Structure             | Planar                  | Planar                  | Vertical        |

| Dimension             | 4F <sup>2</sup>         | 10 <sup>2</sup>         | 4F <sup>2</sup> |

| Channel length        | 1 μm                    | 100 μm                  | 0.1 μm          |

| Linearity (pot./dep.) | -                       | 0.69/0.42               | 1.61/-1.43      |

| On/off ratio          | 2.25                    | 2.17                    | 2.21            |

**Table 1.** Comparison of the 2T, planar 3T, and vertical 3T (this work) synaptic device. The V-ECRAM demonstrated the feasibility of high-density integration and mass production.

National Institute of Standards and Technology (MNIST) dataset  $(28 \times 28)$  as an input image. To compare the accuracy, potentiation/depression linearity, on/off ratio, and number of multilevel of V-ECRAM were considered in the simulation.

The results confirm that the vertical 3T synapse device fabricated using 8-inch wafer-based CMOS fabrication demonstrates the feasibility of high-density integration and mass production. We improved the synaptic characteristics, such as linearity of the potentiation/depression and on/off ratio by optimizing the YSZ electrolyte layer, which plays a crucial role in the ECRAM device. Accordingly, in Fig. 4b, we confirmed that the pattern recognition accuracy at the system-level was improved from 76.70% to 82.92%. Although the synaptic characteristics of synaptic devices have been secured, they still need to be improved compared to ideal synaptic characteristics<sup>30</sup>. In addition, research on reliability characteristics such as retention and endurance are also essential to continuously operate the device.

# Conclusion

The V-ECRAM was successfully developed using an 8-inch wafer-based CMOS fabrication process. Therefore, the area occupied by single cell was reduced from  $10F^2$  to  $4F^2$ , demonstrating the feasibility of high-density integration and mass production. From the optimization of electrolyte layer, in Table 1, improved synaptic characteristics such as linearity of the potentiation/depression (1.61/–1.43) and on/off ratio (2.21) were achieved, which resulted in improved recognition accuracy from 76.70% to 82.92%. These results obviously demonstrate the feasibility of mass production and high integration density of the 3T OxECRAM device.

Received: 10 June 2023; Accepted: 23 August 2023

Published online: 31 August 2023

#### References

- 1. Dhanda, N. Big data storage and analysis. Advances in Data Science and Analytics: Concepts and Paradigms 293-312 (2023).

- 2. Xu, X. et al. Scaling for edge inference of deep neural networks. Nat. Electron. 1, 216-222 (2018).

- 3. Cai, F. et al. A fully integrated reprogrammable memristor-CMOS system for efficient multiply-accumulate operations. Nat. Electron. 2, 290–299 (2019).

- 4. Tang, J. et al. Bridging biological and artificial neural networks with emerging neuromorphic devices: Fundamentals, progress, and challenges. Adv. Mater. 31, 1902761 (2019).

- 5. Mead, C. Neuromorphic electronic systems. Proc. IEEE 78, 1629-1636 (1990).

- 6. Indiveri, G. & Liu, S.-C. Memory and information processing in neuromorphic systems. Proc. IEEE 103, 1379-1397 (2015).

- 7. Jeong, D. S., Kim, I., Ziegler, M. & Kohlstedt, H. Towards artificial neurons and synapses: A materials point of view. RSC Adv. 3, 3169–3183 (2013).

- 8. Byun, K. et al. Recent advances in synaptic nonvolatile memory devices and compensating architectural and algorithmic methods toward fully integrated neuromorphic chips. Advanced Materials Technologies 2200884 (2022).

- 9. Moon, K. et al. Analog synapse device with 5-b MLC and improved data retention for neuromorphic system. *IEEE Electron Device Lett.* 37, 1067–1070 (2016).

- 10. Kim, S. et al. Nvm neuromorphic core with 64k-cell (256-by-256) phase change memory synaptic array with on-chip neuron circuits for continuous in-situ learning. In 2015 IEEE international electron devices meeting (IEDM), 17–1 (IEEE, 2015).

- 11. Oh, S. et al. HfZrOx-based ferroelectric synapse device with 32 levels of conductance states for neuromorphic applications. IEEE Electron Device Lett. 38, 732–735 (2017).

- 12. Lee, D., Moon, K., Park, J., Park, S. & Hwang, H. Trade-off between number of conductance states and variability of conductance change in Pr0. 7Ca0. 3MnO3-based synapse device. *Appl. Phys. Lett.* **106**, 113701 (2015).

- 13. Choi, Y. et al. Structural engineering of li-based electronic synapse for high reliability. IEEE Electron Device Lett. 40, 1992–1995 (2019).

- 14. Kim, S. et al. Experimental demonstration of a second-order memristor and its ability to biorealistically implement synaptic plasticity. *Nano Lett.* **15**, 2203–2211 (2015).

- 15. Gao, B., Wu, H., Kang, J., Yu, H. & Qian, H. Oxide-based analog synapse: Physical modeling, experimental characterization, and optimization. In 2016 IEEE International Electron Devices Meeting (IEDM), 7–3 (IEEE, 2016).

- 16. Tang, J. et al. Ecram as scalable synaptic cell for high-speed, low-power neuromorphic computing. In 2018 IEEE International Electron Devices Meeting (IEDM), 13–1 (IEEE, 2018).

- 17. Lee, C., Choi, W., Kwak, M., Kim, S. & Hwang, H. Excellent synapse characteristics of 50 nm vertical transistor with wo x channel for high density neuromorphic system. In 2021 Symposium on VLSI Technology, 1–2 (IEEE, 2021).

- Go, J. et al. W/wo3-x based three-terminal synapse device with linear conductance change and high on/off ratio for neuromorphic application. Appl. Phys. Express 12, 026503 (2019).

- 19. Nikam, R. D., Kwak, M. & Hwang, H. All-solid-state oxygen ion electrochemical random-access memory for neuromorphic computing. *Adv. Electron. Mater.* 7, 2100142 (2021).

- 20. Lee, J. et al. Improvement of synaptic properties in oxygen-based synaptic transistors due to the accelerated ion migration in substoichiometric channels. Adv. Electron. Mater. 7, 2100219 (2021).

- 21. Huang, H.-Y. et al. Electrolyte-gated synaptic transistor with oxygen ions. Adv. Func. Mater. 29, 1902702 (2019).

- 22. Jeong, Y. et al. Elucidating ionic programming dynamics of metal-oxide electrochemical memory for neuromorphic computing. Adv. Electron. Mater. 7, 2100185 (2021).

- 23. Han, G., Seo, J., Kim, H. & Lee, D. Role of the electrolyte layer in CMOS-compatible and oxide-based vertical three-terminal ECRAM. *J. Mater. Chem. C* 11, 5167–5173 (2023).

- 24. Li, Y. et al. Electrolyte-gated transistors with good retention for neuromorphic computing. Appl. Phys. Lett. 120, 021901 (2022).

- 25. Kostov, A. & Friedrich, B. Selection of crucible oxides in molten titanium and titanium aluminum alloys by thermo-chemistry calculations. *J. Min. Metall. B: Metall.* 41, 113–125 (2005).

- 26. Boatemaa, L., Kwakernaak, C., Van Der Zwaag, S. & Sloof, W. G. Selection of healing agents for autonomous healing of alumina at high temperatures. *J. Eur. Ceram. Soc.* **36**, 4141–4145 (2016).

- 27. Casselton, R. & Scott, J. Conduction mechanism in yttria stabilized zirconia. Phys. Lett. A 25, 264-265 (1967).

- 28. Choi, S. et al. Effect of oxygen content on current stress-induced instability in bottom-gate amorphous ingazno thin-film transistors. Materials 12: 3149 (2019).

- 29. Lee, C., Choi, W., Kwak, M., Kim, S. & Hwang, H. Impact of electrolyte density on synaptic characteristics of oxygen-based ionic synaptic transistor. *Appl. Phys. Lett.* **119** (2021).

- 30. Moon, K. et al. Rram-based synapse devices for neuromorphic systems. Faraday Discuss. 213, 421-451 (2019).

- 31. Song, W. et al. Analog switching characteristics in tiw/al2o3/ta2o5/ta rram devices. Appl. Phys. Lett. 115 (2019).

- 32. Lee, K. et al. Improved synaptic functionalities of li-based nano-ionic synaptic transistor with ultralow conductance enabled by al2o3 barrier layer. Nanotechnology 32, 275201 (2021).

# Acknowledgements

This research was supported by the MSIT (Ministry of Science and ICT), Korea, under the ITRC (Information Technology Research Center) support program (IITP-2023-RS-2022-00156225) supervised by the IITP (Institute for Information & Communications Technology Planning & Evaluation) and partially supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MIST) (2009-0082580).

### **Author contributions**

D.L. conceived and the directed the research. H.K. and J.S. conducted the experiment. H.K., J.S., S.C., and S.J. analysed the results. H.K. wrote the manuscript. J.W. revised the manuscript. All authors reviewed the manuscript.

# Competing interests

The authors declare no competing interests.

### Additional information

Correspondence and requests for materials should be addressed to D.L.

Reprints and permissions information is available at www.nature.com/reprints.

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

© The Author(s) 2023