# scientific reports

## **OPEN** Enhancing on/off ratio of a dielectric-loaded plasmonic logic gate with an amplitude modulator

Kai-Hao Chang<sup>1,2</sup>, Zhan-Hong Lin<sup>2</sup>, Po-Tsung Lee<sup>1</sup> & Jer-Shing Huang<sup>2,3,4,5</sup>

Plasmonic waveguides allow focusing, guiding, and manipulating light at the nanoscale and promise the miniaturization of functional optical nanocircuits. Dielectric-loaded plasmonic (DLP) wavequides and logic gates have drawn attention because of their relatively low loss, easy fabrication, and good compatibility with gain and active tunable materials. However, the rather low on/off ratio of DLP logic gates remains the main challenge. Here, we introduce an amplitude modulator and theoretically demonstrate an enhanced on/off ratio of a DLP logic gate for XNOR operation. Multimode interference (MMI) in DLP waveguide is precisely calculated for the design of the logic gate. Multiplexing and power splitting at arbitrary multimode numbers have been theoretically analyzed with respect to the size of the amplitude modulator. An enhanced on/off ratio of 11.26 dB has been achieved. The proposed amplitude modulator can also be used to optimize the performance of other logic gates or MMI-based plasmonic functional devices.

Using photons for communication and circuit operation features lower loss, higher frequency, large bandwidth, and thus faster speed compared to conventional electronics. Modern photonic technology has been advanced to overcome the limitations of conventional electronics, such as interconnect delays and increased power dissipation in electronic transistors<sup>1,2</sup>. However, the footprint of photonic circuits using dielectric waveguides is rather large due to the cutoff of photonic modes. Moreover, the performance in term of the on/off ratio is relatively low compared to electronic circuits. These drawbacks limit the miniaturization and applications of photonic devices. Merging electrons and photons, surface plasmon polaritons (SPPs) offer unique opportunities for next-generation optical nanocircuits and communication<sup>3-5</sup>. The advantages of using SPPs as information carriers lie in the ultra-high operating frequency in the optical range and cutoff-free field confinement down to the nanoscale<sup>6-9</sup>. Based on these characteristics, plasmonic nanocircuits and waveguides are considered as potential substitutes for dielectric photonic devices, in particular for matching nanoscale electronic devices for optoelectronic modulation<sup>10</sup>. Related plasmonic optoelectronic components, such as modulators<sup>11-14</sup>, filters<sup>15-17</sup>, switches<sup>18-21</sup>, circuits<sup>8,22-25</sup>, sensors<sup>26</sup>, have been demonstrated and reported.

One of the main drawbacks of plasmonic waveguides compared to photonic waveguides is the rather challenging fabrication, high losses, and limited propagation length. To address these issues, well-designed dielectric materials have been used in combination with plasmonic substrates<sup>27</sup>. These DLP devices offer the possibility to prolong the propagation length to millimeter range<sup>28-31</sup> and allow easy design and fabrication of subwavelength optical devices<sup>32-34</sup>. In addition, combining dielectric materials with plasmonic substrate also allows the introduction of gain materials for loss compensation or even laser<sup>35-37</sup>, as well as phase-changing materials for active control<sup>38-42</sup>. For subwavelength waveguide and circuit operation in the optical regime, DLP waveguides are promising for their relatively easy fabrication, low loss, and potential of interconnection with silicon photonic circuits<sup>43</sup>. Low-loss power splitters and spatial light modulators based on DLP devices have been demonstrated at telecommunication frequencies<sup>44</sup>. Broadband operation with high transmittance has been demonstrated with a footprint as small as several hundreds of nanometers<sup>45,46</sup>. In addition, DLP waveguides also provide a convenient

<sup>1</sup>Department of Photonics, College of Electrical and Computer Engineering, National Yang Min Chiao Tung University, Hsinchu 300, Taiwan. <sup>2</sup>Leibniz Institute of Photonic Technology, Albert-Einstein Straße 9, 07745 Jena, Germany. <sup>3</sup>Institute of Physical Chemistry and Abbe Center of Photonics, Friedrich-Schiller-Universität Jena, Helmholtzweg 4, 07743 Jena, Germany. <sup>4</sup>Research Center for Applied Sciences, Academia Sinica, Taipei 11529, Taiwan. <sup>5</sup>Department of Electrophysics, National Yang Ming Chiao Tung University, Hsinchu 30010, Taiwan. <sup>⊠</sup>email: potsung@mail.nctu.edu.tw; jer-shing.huang@leibniz-ipht.de

platform for light coupling to optical fibers and other silicon-on-insulator devices fabricated by complementary metal-oxide semiconductor-compatible processes<sup>47</sup>.

To perform logic operation and other essential functions of a microprocessor on DLP logic gates, the most widely used approach is to introduce a well-designed patch of DLP waveguide that properly accommodates MMI<sup>48</sup>, which generates predictable and fruitful spatial distribution of power flux due to the constructive and destructive interference between fundamental and high-order plasmonic modes. This approach avoids the use of Mach-Zehnder-based architecture and thus reduces the loss<sup>49,50</sup>. Based on the MMI scheme, Fukuda et al. have purposed the DLP devices for half and full adder operation, based on a  $1 \times 1$  MMI phase modulators and a  $2 \times 2$  MMI intensity modulators<sup>51,52</sup>. The contrast ratios of the AND and XOR operations of their adders reach 5.82 and 17.16 dB, respectively, as measured by scanning near-field optical microscopy. The measured near-field interference patterns require careful analysis because of the inevitable contribution of photonic modes in the thick dielectric layer. The main challenge is the loss due to the complex connections between logic gates and the relatively poor logical performance, i.e., low on/off ratio, compared to typical metal-oxide-semiconductor fieldeffect transistors. Although many functions have been proposed and demonstrated, weak logic performance due to low on/off ratio remains the main challenge for plasmonic logic gates to enter the realm of practical applications. For the same reason, developing and fabricating useful logic conjunctions, which are critical for AND and XNOR logic operations, remains extremely difficult. Only a few previous related works have been reported but the corresponding on/off ratios are rather low<sup>53-55</sup>.

To improve the on/off ratio of DLP waveguide-based logic gates, we introduce an amplitude modulator for the first time in this work. MMI scheme is employed to design the compact DLP waveguide-based XNOR logic gate. We theoretically demonstrate that the amplitude modulator helps achieve complete constructive and destructive interference. We demonstrate a high contrast ratio of XNOR logic operation by using a specific arrangement of amplitude and phase modulators. The proposed amplitude modulator is not limited to the XNOR gate shown in this work but also applies to all MMI-based DLP functional devices, which requires high on/off ratio.

#### Results

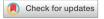

The schematic diagram of the plasmonic XNOR gate used in this work is shown in Fig. 1a. It comprises two input waveguides (input A and input B) and one reference waveguide (Ref). Each of the two inputs is equipped with a phase modulator and the reference waveguide has an amplitude modulator. Three waveguides inject SPPs modes into a common plate for MMI. The designed logic operation for off and on states is illustrated in Fig. 1b–d. The "off" state occurs when either input A or input B interferes with the mode from the reference to produce destructive interference at the output channel (Fig. 1b,c). As for the "on" state, it occurs when both input A and input B inject the modes to interfere with the mode from the Ref channel. This leads to a significantly large power transmission through the output channel (Fig. 1d).

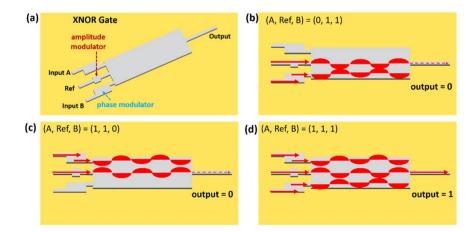

The in-plane and cross-sectional dimensions of the designed XNOR gate used in the simulation are shown in Fig. 2a. We have chosen  $SiO_2$  as the dielectric material because it is compatible with modern CMOS fabrication process. We note that DLP waveguides with a sufficiently large cross section of the dielectric channel can support both the plasmonic and the photonic modes. The cross section of our dielectric input channels is as large as  $500 \times 500$  nm<sup>2</sup>. Therefore, it also supports both the plasmonic and the photonic modes. Nevertheless, the plasmonic mode can be readily distinguished from the photonic mode by examining the mode profile. The plasmonic mode features a spatial distribution that exponentially decays from the metal/dielectric interface, whereas the photonic mode exhibits a mode distribution with maximum intensity around the center and decays toward the boundary of the dielectric channel. Figure 2b shows the simulated mode profiles of the fundamental plasmonic (top panel) and photonic mode (bottom panel) of our DLP waveguide. The effective index and mode order of the guided plasmonic mode vary as a function of the waveguide width. As shown in Fig. 2c, fundamental

**Figure 1.** (a) The schematic diagram of plasmonic XNOR gate. Input A and input B contain a phase modulator. The Ref channel has an amplitude modulator. (**b**,**c**) The cases of zero output when (A, Ref, B) = (0, 1, 1) and (1, 1, 0). (**d**) The case of unitary output when (A, Ref, B) = (1, 1, 1).

Figure 2. (a) Dimension of the plasmonic XNOR gate in the x-y (top panel) and y-z plane (bottom panel). Gold and  $SiO_2$  are chosen as the material for the substrate and the dielectric waveguide, respectively. (b) Simulated cross-sectional electric field mode profile of the fundamental plasmonic (top panel) and photonic (bottom panel) guided mode in a  $500 \times 500$  nm<sup>2</sup> SiO<sub>2</sub> dielectric channel on a gold substrate. White solid lines mark the boundaries of the dielectric waveguide and the surface of the gold substrate. (c) Simulated effective indices of the fundamental plasmonic (navy blue squares) and photonic mode (dark green dots) as functions of the width of the SiO<sub>2</sub> dielectric waveguide between 200 and 600 nm. (d) Same plot as (c) with only the indices of fundamental and high-order plasmonic guided modes with respect to the waveguide width over the extended range of 1000-5000 nm. Apart from the fundamental plasmonic mode (navy blue squares), the firstorder (orange dots), second-order (blue triangles), and third-order (green inverted triangles) plasmonic modes can also exist in the DLP waveguide. (e) The optimal distance for n-branched power splitting plotted versus the number of branches, n. Dots are data points obtained from COMSOL simulation and the dashed curve is obtained from fitting the simulated data with Eq. (1). (f) Simulated spatial distribution of optical power flow for the cases of two- (top panel) and three-branched power splitting (bottom panel) cases. The input on the left side of the image is a single SiO<sub>2</sub> channel (cross-section:  $500 \times 500$  nm<sup>2</sup>) on a gold substrate and the following MMI section has the same height but a much larger width of 5000 nm with lengths optimized for two- and threebranched splitting.

plasmonic mode (the 0th order at a vacuum wavelength of 785 nm) emerges at the waveguide width of 200 nm, which is much smaller than the case of fundamental photonic mode. The effective index of the plasmonic guided mode increases with increasing the waveguide width and saturates at around 1.40. With relatively small cross section, the guided fundamental plasmonic mode features high mode index and absence of cutoff.

Further increasing the width of the dielectric channel to more than 1000 nm allows guiding the high-order transverse plasmonic modes (Fig. 2d). The effective index of all modes eventually converges to around 1.40, which is determined by the index of the dielectric material and the index of the metal substrate. Based on the results of mode analyses, we have chosen 500 nm as the width of the input and Ref ports because this width supports a sufficiently high effective index of the fundamental plasmonic mode without the introduction of high-order plasmonic modes. As for the section for MMI, we have chosen a width of 5000 nm for two reasons. First, this width is sufficient to accommodate all the input and output channels. Secondly, DLP waveguide of this width

also supports high orders of plasmonic modes. This is critical for the MMI as will be discussed later. The length of the MMI section is calculated to be  $15 \,\mu m$  according to the following formula<sup>56,57</sup>,

$$L = \frac{P}{N}(L_{\pi}),\tag{1}$$

where *P* denotes the period along the propagating direction and  $L_{\pi}$  denotes the beating length of the two lowestorder modes, which can be expressed as

$$L_{\pi} \approx \frac{\pi}{\beta_0 - \beta_\nu} = \frac{4n_{eff} W^2}{3\lambda_0}.$$

(2)

$\beta_{o}$  and  $\beta_{v}$  are propagation the constants in air (n = 1) and in the DLP waveguide, respectively. The latter depends on the modal profile and is indicated by the mode number v. For v = 1,  $\beta_v$  matches the fundamental transverse standing wave condition. W and n<sub>eff</sub> are the width of DLP waveguide and the effective refractive index of the guided mode, respectively.  $\lambda_o = 785$  nm is the operating wavelength in air. Along the propagating direction, mode beating results in evolving transverse field profile, which can be described by the mode transition number n. Equations (1) and (2) can be used to analytically calculate the optimal distance required for the transverse mode profile to transform into a specific n-fold intensity distribution. This calculation is important for the design of DLP logic gates because the calculated optimal distance determines the optimal length of the MMI section for targeted n-branched power splitting. In principle, these formulas allow us to determine the length of the MMI waveguide section in order to split the power into any number of branches. We verify Eq. (1) with electromagnetic simulations using COMSOL. Figure 2e plots the optimal distances for the corresponding branch number n obtained from COMSOL simulation, which can be well fitted with Eq. (1). The simulated spatial distributions of the guided power in MMI sections designed for two- and three-branched power splitting are given as examples in Fig. 2f. With the input of a fundamental plasmonic mode from a single dielectric channel (cross-section:  $500 \times 500$  nm<sup>2</sup>) on a gold substrate, the DLP waveguide sections of lengths 22 and 15  $\mu$ m serve as interfering plates for MMI, leading to optimized one-to-two and one-to-three power splitting, respectively.

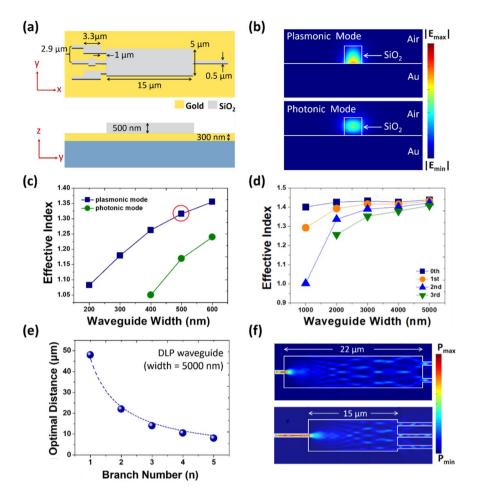

Having analyzed the important parameters for designing DLP logic gates, we further demonstrate that the logic operation of the XNOR logic gate shown in Fig. 2a can be enhanced by introducing well-designed phase and amplitude modulators. We first demonstrate an XNOR logic gate with only a phase modulator but without any amplitude modulator at A and B input ports. The simulated  $E_z$ -field distribution in Fig. 3a shows the logic performance of the XNOR gate. Various input conditions of the XNOR logic operation lead to the "on" and "off" states, showing distinctively different  $E_z$ -field intensity at the output port on the right side. The Ref port plays an important role in the logic operation of an XNOR gate. Destructive interference for the "off" state comes from the superimposition of the input signals. Since the dimensions of the DLP waveguide section for MMI are fixed, it is important to optimize the phase difference between the input modes for perfect destructive interference.

**Figure 3.** (a) Simulated electric field  $(E_z)$  of the XNOR gate with phase modulators in the waveguides of input A and input B. Boolean operations of "off" (top and middle panels) and "on" states (bottom panel) at different input conditions. "Off" and "on" states correspond to very low and high power transmission through the output port on the right. (b) Simulated electric field  $(E_z)$  distributions revealing the phase modulation at different widths of the phase tuning plate. (c) The transmittance and contrast ratio of the XNOR gate as a function of the width of the phase modulator. The contrast ratio is defined as the power of the "on" state over that of the "off" state.

For this, the modulation of the input phase has been achieved by controlling the width of the phase modulators, which are the wider plates in input A and input B. To optimize the logic operation, we have scanned the width of the phase modulator at a fixed length for both input ports. Figure 3b shows the simulated real electric field in the DLP logic gate. The phase of the guided mode shifts as a function of the width of the phase plate. Increasing the width allows adjusting the phase of the electric field up to  $\pi$ , seen as the color change from blue to red in the area indicated by black dash lines. The phase variation induced by the modulator can be analytically described as<sup>51,56</sup>

$$\Delta \varphi_a = (\beta_s - \beta_a) L_a \approx \left( \frac{1}{W_{se}^2} - \frac{1}{W_{ae}^2} \right) \frac{\pi \lambda_0}{4n_{eff}} L_a, \tag{3}$$

where  $\beta_s$  and  $\beta_a$  are the propagation coefficients of the fundamental mode in the single waveguide and the phase modulator, respectively.  $W_{se}$  and  $W_{ae}$  are the effective waveguide widths for the fundamental mode in the singlemode waveguide and phase adjuster, respectively.  $L_a$  is the length of the phase modulator. We adapt this design of phase plate to the XNOR gate.

Figure 3c shows the transmittance and contrast ratio of the XNOR gate by with respect to the width of the phase plate. Here, the contrast ratio is defined as the output power of the "on" state over that of the "off" state. The transmittance is obtained by dividing the output power by the sum of the power of all inputs. For our XNOR gate at "off" state, the minimum transmittance and maximum contrast ratio are obtained at 1100 nm. Low transmittance with enhanced contrast ratio is the optimization target for the phase modulator in an XNOR gate at "off" state.

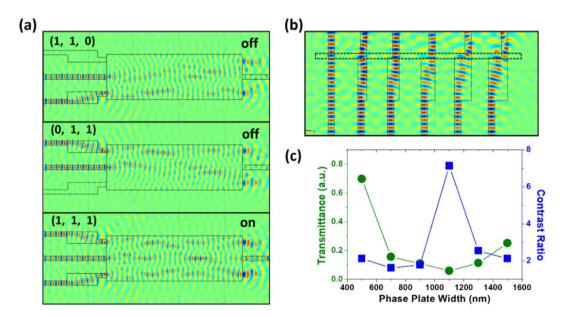

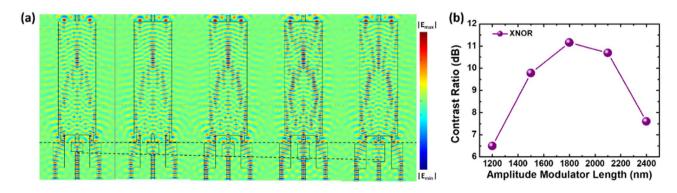

To further improve the performance of the logic gate, the amplitude should also be optimized. For this purpose, we introduce an amplitude modulator to the Ref input port with the best optimized phase modulators on input A and input B. Figure 4a shows the  $E_z$ -field distribution of the XNOR gate obtained with an amplitude modulator at different lengths installed on the Ref port. By optimizing the length of the amplitude modulator on the Ref port, the on/off ratio of the logic performance can be enhanced up to 11.26 dB at the length of 1800 nm. This is higher than the 8.57 dB (ratio = 7.2) of the original design. As shown in Fig. 4b, by modulating the optical loss in the amplitude modulator, near-perfect destructive interference in the "off" state can be achieved within a limited range of modulator length (approximately 1500–2300 nm), resulting in an improved contrast ratio.

In this work, we focus on the theoretical demonstration of the amplitude modulator. Here, we briefly discuss the fabrication possibilities and errors. In the simulations, the thickness of the dielectric layer has been set to a constant value. In real applications, the designed structures can be realized by modern nanofabrication technologies, such as electron-beam lithography, focused ion beam milling, nanoimprint, or nanoprinting methods. The imperfection of the nanofabrication may, however, lead to a discrepancy between the theoretical prediction and the performance of a real structure. We briefly discuss the possible fabrication errors and their impacts. Since the designed structures do not contain sub-50 nm features, such as nanogaps, the above-mentioned modern nanofabrication technologies should be sufficient in terms of spatial resolution. However, keeping a constant thickness of the dielectric layer might be challenging. Uncertainty in the thickness of the dielectric layer may lead to a deviation of the mode index from the theoretically predicted value. The corrugation of the surface of the dielectric layer can also lead to scattering of the guided mode. Both errors can change the interference pattern of the modes in the MMI section and thereby change the results. For dielectric-loaded plasmonic nanocircuits with a rather thick dielectric layer (>500 nm), photonic modes are coexisting and the mode index can be significantly affected by the thickness uncertainty. For nanocircuits with a very thin dielectric layer (<100 nm), the near field of the surface plasmons extends out of the dielectric layer. In this case, the thickness variation can lead to the variation of the "effective surrounding index", resulting in the index change of the plasmonic modes<sup>32,33</sup>. Therefore, the thickness of the dielectric layer should be carefully controlled.

In conclusion, we have theoretically studied the guided modes in dielectric-loaded plasmonic waveguides. Using the DLP waveguide, we have designed an XNOR logic gate based on MMI and demonstrated that introducing an amplitude modulator at the input port can significantly enhance the on/off ratio of the XNOR logic operation. Together with optimized phase modulators, we have achieved an on/off ratio up to 11.26 dB. Introducing an amplitude modulator to the Ref input port is an effective way to optimize the on/off ratio of plasmonic logic gates

**Figure 4.** (a)  $E_z$ -field distribution of the XNOR gate in the "on" state. The length of the amplitude modulator on the Ref port is varied as indicated by the black dashed lines. (b) Relation of contrast ratio as the function of amplitude modulator length.

<sup>5</sup>

based on MMI. This approach is not limited to the demonstrated XNOR gate but generally applicable to various logical gates based on MMI for other logic operations. The unique design flexibility of the amplitude modulator allows for a wide range of applications in optimizing logic operations for nano optics and photonic circuits. The dielectric-loaded nature of the proposed plasmonic nanocircuit also facilitates the fabrication because the structures are realizable for nanoimprint and or nanoprinting methods, which are capable of printing dielectric structures with sub-micrometer features on metallic substrates.

#### Methods

**Numerical method.** Simulations were performed using commercial software (COMSOL) based on finite element method to obtain the power flow distribution of plasmonic logic gates. The effective indices of the guided modes were obtained by solving eigenvalue problems in the RF module. The dielectric function of Au was taken from previously published data<sup>58</sup>. Transverse magnetic incident waves were used for the excitation of the input ports.

#### Discussion

The discussion must not contain subheadings.

#### Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

Received: 3 November 2022; Accepted: 2 March 2023 Published online: 28 March 2023

#### References

- Dionne, J. A., Sweatlock, L. A., Sheldon, M. T., Alivisatos, A. P. & Atwater, H. A. Silicon-based plasmonics for on-chip photonics. IEEE J. Sel. Top. Quantum Electron. 16(1), 295–306 (2010).

- 2. Brongersma, M. L. & Shalaev, V. M. The case for plasmonics. Science 328(5977), 440-441 (2010).

- 3. Ozbay, E. Plasmonics: Merging photonics and electronics at nanoscale dimensions. *Science* **311**, 189–193 (2006).

- 4. Schuller, J. A. et al. Plasmonics for extreme light concentration and manipulation. Nat. Mater. 9(3), 193-204 (2010).

- 5. Gramotnev, D. K. & Bozhevolnyi, S. I. Plasmonics beyond the diffraction limit. Nat. Photon. 4(2), 83-91 (2010).

- Hung, Y.-T., Huang, C.-B. & Huang, J.-S. Plasmonic mode converter for controlling optical impedance and nanoscale light-matter interaction. Opt. Express 20(18), 20342–20355 (2012).

- 7. Cohen, M., Zalevsky, Z. & Shavit, R. Towards integrated nanoplasmonic logic circuitry. Nanoscale 5(12), 5442-5449 (2013).

- Dai, W. H., Lin, F. C., Huang, C. B. & Huang, J. S. Mode conversion in high-definition plasmonic optical nanocircuits. Nano Lett. 14(7), 3881–3886 (2014).

- Schorner, C., Adhikari, S. & Lippitz, M. A single-crystalline silver plasmonic circuit for visible quantum emitters. Nano Lett. 19(5), 3238–3243 (2019).

- Heni, W. *et al.* Plasmonic IQ modulators with attojoule per bit electrical energy consumption. *Nat. Commun.* 10(1), 1694 (2019).

Cai, W., White, J. S. & Brongersma, M. L. Compact, high-speed and power-efficient electrooptic plasmonic modulators. *Nano Lett.* 9(12), 4403–4411 (2009).

- 12. Haffner, C. et al. Low-loss plasmon-assisted electro-optic modulator. Nature 556(7702), 483-486 (2018).

- 13. Chauhan, D., Sbeah, Z., Dwivedi, R. P., Nunzi, J.-M. & Thakur, M. S. An investigation and analysis of plasmonic modulators: A review. J. Opt. Commun. 20, 22 (2022).

- 14. Chauhan, D., Mola, G. T. & Dwivedi, R. P. An ultra-compact plasmonic modulator/switch using VO2 and elasto-optic effect. *Optik* 20, 201 (2020).

- Volkov, V. S., Bozhevolnyi, S. I., Devaux, E., Laluet, J.-Y. & Ebbesen, T. W. Wavelength selective nanophotonic components utilizing channel plasmon polaritons. *Nano Lett.* 7(4), 880–884 (2007).

- 16. Bozhevolnyi, S. I., Volkov, V. S., Devaux, E., Laluet, J. Y. & Ebbesen, T. W. Channelling surface plasmons. Appl. Phys. A 89(2), 225-231 (2007).

- 17. Chauhan, D. *et al.* Theoretical analysis of VO2 filled double rectangular cavity-based coupled resonators for plasmonic active switch/modulator and band pass filter applications. *Opt. Materi.* **20**, 125 (2022).

- Pala, R. A., Shimizu, K. T., Melosh, N. A. & Brongersma, M. L. A nonvolatile plasmonic switch employing photochromic molecules. Nano Lett. 8(5), 1506–1510 (2008).

- 19. Emboras, A. et al. Atomic scale plasmonic switch. Nano Lett. 16(1), 709-714 (2016).

- 20. Xiang, D., Wu, J. & Gordon, R. Coulomb blockade plasmonic switch. Nano Lett. 17(4), 2584–2588 (2017).

- 21. Chauhan, D. et al. High performance vanadium dioxide based active nano plasmonic filter and switch. Optik 2, 25 (2021).

- Davis, T. J., Gómez, D. É. & Roberts, A. Plasmonic circuits for manipulating optical information. Nanophotonics 6(3), 543-559 (2017).

- Chen, T. Y. et al. Modal symmetry controlled second-harmonic generation by propagating plasmons. Nano Lett. 19(9), 6424–6428 (2019).

- Chen, T. Y., Tyagi, D., Chang, Y. C. & Huang, C. B. A polarization-actuated plasmonic circulator. Nano Lett. 20(10), 7543–7549 (2020).

- Wu, P.-Y., Chang, Y.-C. & Huang, C.-B. Broadband plasmonic half-subtractor and digital demultiplexer in pure parallel connections. *Nanophotonics* 11(16), 3623–3629 (2022).

- 26. Sbeah, Z. A. et al. GST-based plasmonic biosensor for hemoglobin and urine detection. Plasmonics 17(6), 2391-2404 (2022).

- 27. Meng, Y. et al. Optical meta-waveguides for integrated photonics and beyond. Light Sci. Appl. 10(1), 235 (2021).

- Oulton, R. F., Sorger, V. J., Genov, D. A., Pile, D. F. P. & Zhang, X. A hybrid plasmonic waveguide for subwavelength confinement and long-range propagation. *Nat. Photon.* 2(8), 496–500 (2008).

- Holmgaard, T., Gosciniak, J. & Bozhevolnyi, S. I. Long-range dielectric-loaded surface plasmon-polariton waveguides. *Opt. Express* 18(22), 23009–23015 (2010).

- Volkov, V. S. et al. Long-range dielectric-loaded surface plasmon polariton waveguides operating at telecommunication wavelengths. Opt. Lett. 36(21), 4278–4280 (2011).

- Zenin, V. A. et al. Directional coupling in long-range dielectric-loaded plasmonic waveguides. Opt. Express 21(7), 8799–8807 (2013).

- 32. Liu, Y., Zentgraf, T., Bartal, G. & Zhang, X. Transformational plasmon optics. Nano Lett. 10(6), 1991–1997 (2010).

- Zentgraf, T., Liu, Y., Mikkelsen, M. H., Valentine, J. & Zhang, X. Plasmonic Luneburg and Eaton lenses. Nat. Nanotechnol. 6(3), 151–155 (2011).

- Chen, C. et al. Waveguide-Integrated Compact Plasmonic Resonators for On-Chip Mid-Infrared Laser Spectroscopy. Nano Lett 18(12), 7601–7608 (2018).

- 35. Oulton, R. F. et al. Plasmon lasers at deep subwavelength scale. Nature 461(7264), 629-632 (2009).

- Ma, R. M., Oulton, R. F., Sorger, V. J., Bartal, G. & Zhang, X. Room-temperature sub-diffraction-limited plasmon laser by total internal reflection. *Nat. Mater.* 10(2), 110–113 (2011).

- 37. Sorger, V. J. & Zhang, X. Spotlight on plasmon lasers. Science 333(6043), 709-710 (2011).

- Abdollahramezani, S. et al. Tunable nanophotonics enabled by chalcogenide phase-change materials. Nanophotonics 9(5), 1189– 1241 (2020).

- 39. Qin, S. *et al.* Near-infrared thermally modulated varifocal metalens based on the phase change material Sb2S3. *Opt. Express* **29**(5), 7925–7934 (2021).

- 40. Wang, Y. et al. Electrical tuning of phase-change antennas and metasurfaces. Nat. Nanotechnol. 16(6), 667-672 (2021).

- Zhang, Y. et al. Electrically reconfigurable non-volatile metasurface using low-loss optical phase-change material. Nat. Nanotechnol. 16(6), 661–666 (2021).

- 42. Shalaginov, M. Y. *et al.* Reconfigurable all-dielectric metalens with diffraction-limited performance. *Nat. Commun.* **12**(1), 1225 (2021).

- 43. Pleros, N., et al. Tb/s switching fabrics for optical interconnects using heterointegration of plasmonics and silicon photonics: The FP7 PLATON approach, 2010 23rd Annual Meeting of the IEEE Photonics Society, 7–11 Nov. 2010; 2010; pp 165–166.

- 44. Bruck, R. et al. All-optical spatial light modulator for reconfigurable silicon photonic circuits. Optica 3, 4 (2016).

- Wang, J. et al. Sub-µm2 power splitters by using silicon hybrid plasmonic waveguides. Opt. Express 19(2), 838–847 (2011).

Lu, C., Hu, X., Yang, H. & Gong, Q. Chip-integrated ultrawide-band all-optical logic comparator in plasmonic circuits. Sci. Rep.

- 4, 3869 (2014).

47. Jimenez Gordillo, O. A. *et al.* Plug-and-play fiber to waveguide connector. *Opt. Express* 27(15), 20305–20310 (2019).

- 48. Wei, H. et al. Quantum dot-based local field imaging reveals plasmon-based interferometric logic in silver nanowire networks. Nano Lett. **11**(2), 471–475 (2011).

- Dikken, D. J., Spasenović, M., Verhagen, E., van Oosten, D. & Kuipers, L. Characterization of bending losses for curved plasmonic nanowire waveguides. Opt. Express 18(15), 16112–16119 (2010).

- 50. Fu, Y. et al. All-optical logic gates based on nanoscale plasmonic slot waveguides. Nano Lett. 12(11), 5784-5790 (2012).

- Ota, M., Sumimura, A., Fukuhara, M., Ishii, Y. & Fukuda, M. Plasmonic-multimode-interference-based logic circuit with simple phase adjustment. Sci. Rep. 6, 24546 (2016).

- Fukuda, M., Watanabe, R., Tonooka, Y. & Ota, M. Feasibility of cascadable plasmonic full adder. *IEEE Photon. J.* 11(4), 1–12 (2019).

Pan, D., Wei, H. & Xu, H. Optical interferometric logic gates based on metal slot waveguide network realizing whole fundamental

- logic operations. *Opt. Express* **21**(8), 9556–9562 (2013). 54. Birr, T., Zywietz, U., Chhantyal, P., Chichkov, B. N. & Reinhardt, C. Ultrafast surface plasmon-polariton logic gates and half-adder.

- *Opt. Express* 23(25), 31755–31765 (2015).

55. Gao, L., Chen, L., Wei, H. & Xu, H. Correction: Lithographically fabricated gold nanowire waveguides for plasmonic routers and logic gates. *Nanoscale* 10(30), 14771 (2018).

- Soldano, L. B. & Pennings, E. C. M. Optical multi-mode interference devices based on self-imaging: Principles and applications. *J. Lightw. Technol.* 13(4), 615–627 (1995).

- 57. Song, Y., Wang, J., Yan, M. & Qiu, M. Efficient coupling between dielectric and hybrid plasmonic waveguides by multimode interference power splitter. J. Opt. 13, 7 (2011).

- 58. Olmon, R. L. et al. Optical dielectric function of gold. Phys. Rev. B 86, 23 (2012).

#### Acknowledgements

The financial support from the MOST-BMBF project-related-mobility program under contract numbers 107-2911-I-009-518 (MOST, Taiwan) and 01DO18018 (BMBF, Germany) and from the DFG in Germany (CRC 1375 NOA and HU2626/3-1) is gratefully acknowledged.

#### Author contributions

K.-H.C., P.-T.L. and J.-S.H. conceive the research idea. K.-H.C. performed the COMSOL simulations. K.-H.C. and Z.-H.L. performed the data analysis. P.-T.L. and J.-S.H. supervised the research. All authors contributed to the interpretation of the results and the preparation of the manuscript.

#### Funding

Open Access funding enabled and organized by Projekt DEAL.

### **Competing interests**

The authors declare no competing interests.

#### Additional information

Correspondence and requests for materials should be addressed to P.-T.L. or J.-S.H.

#### Reprints and permissions information is available at www.nature.com/reprints.

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

© The Author(s) 2023