# scientific reports

Check for updates

## **OPEN** Effect of high-pressure D<sub>2</sub> and H<sub>2</sub> annealing on LFN properties in FD-SOI pTFET

Hyun-Jin Shin<sup>1</sup>, Sunil Babu Eadi<sup>1</sup>, Yeong-Jin An<sup>1</sup>, Tae-Gyu Ryu<sup>1</sup>, Do-woo Kim<sup>2</sup>, Hi-Deok Lee<sup>1⊠</sup> & Hyuk-Min Kwon<sup>3⊠</sup>

Tunneling field-effect transistors (TFETs) are a promising candidate for the next generation of low-power devices, but their performance is very sensitive to traps near the tunneling junction. This study investigated the effects of high-pressure deuterium  $(D_2)$  annealing and hydrogen  $(H_2)$ annealing on the electrical performance and low-frequency noise (LFN) of a fully depleted siliconon-insulator p-type TFET. Without high-pressure annealing, the typical noise power spectral density exhibited two Lorentzian spectra that were affected by fast and slow trap sites. With high-pressure annealing, the interface trap density related to fast trap sites was reduced. The passivation of traps near the tunneling junction indicates that high-pressure H<sub>2</sub> and D<sub>2</sub> annealing improves the electrical performance and LFN properties, and it may become a significant and necessary step for realizing integrated TFET technology in the future.

Tunneling field-effect transistors (TFETs) have attracted significant attention as the next generation of low-power devices because they can realize a very low off-current and subthreshold swing (SS) of less than 60 mV dec<sup>-11-3</sup>. Because a very low SS is difficult to achieve in practice without the use of a special substrate or structure<sup>1-3</sup>, TFET operation is extremely sensitive to the materials used, geometry, and traps near the source/channel (tunneling) junction. Many studies have been conducted to improve the electrical efficiency of TFETs by modifying the device structure, introducing new substrate materials, or improving fabrication technology<sup>1-3</sup>. However, other important factors such as the 1/f noise and random telegraph signal noise (RTN) have received less attention despite being a significant limiting factor in analog and digital circuits. The effects of trap sites within the gate oxide and the current induced via fluctuation have emerged as critical concerns as devices continue to be scaled down<sup>4,5</sup>. The gate and potential barrier between the channel and source control the band-to-band tunneling mechanism in TFETs while drift-diffusion is used in conventional metal-oxide-semiconductor field-effect transistors (MOS-FETs). The low-frequency noise (LFN) properties of TFETs and MOSFETs are generally dominated by the gate dielectric. For TFETs, the trapping and de-trapping characteristics of trap sites away from the tunnel junction may have a weak effect on the drain current  $(I_{DS})$  fluctuation. A few active traps around the tunnel junction of a TFET can influence the junction electric field and result in current fluctuations. Since the tunneling junction in TFET has a significant impact on electrical performance, the major LNF mechanism in nTFETs has been explained by carrier number fluctuations<sup>6</sup>. However, as the LNF properties in pTFETs have been still unclear, studies of the improvement on the LFN properties are still merit.

RTN also causes TFETs to have a high amplitude and significant device-to-device variability. Recently, deuterium (D<sub>2</sub>) and hydrogen (H<sub>2</sub>) annealing has been used to improve the reliability and LFN properties of silicon devices, including nanowire FETs<sup>7,8</sup>. Several studies have reported that high-pressure annealing improves the electrical performance with the benefit of a short annealing time because of the high concentration of  $D_2$  or  $H_2$ gas within a particular space<sup>9,10</sup>. The binding energy of the Si-D bond is known to have a higher kinetic isotope effect than that of the Si-H bond. In other words, the Si-D bond provides an energy-relaxation pathway that makes it more difficult to detach<sup>11</sup>. However, studies on p-type TFETs (pTFETs) have been limited compared with those on general n-type TFETs (nTFETs). Moreover, the effects of high-pressure H<sub>2</sub> and D<sub>2</sub> annealing on the LFN and RTN characteristics of pTFETs have not been reported.

<sup>1</sup>Department of Electronics Engineering, Chungnam National University, 99, Daehak-ro, Yuseong-gu, Daejeon, Republic of Korea. <sup>2</sup>Department of Semiconductor Design, Semiconductor Convergence Campus of Korea Polytechnic College, 41-12, Songwon-Gil, Kongdo-Eup, Anseong, Kyunggi-Do, Republic of Korea. <sup>3</sup>Department of Semiconductor Processing Equipment, Semiconductor Convergence Campus of Korea Polytechnic College, 41-12, Songwon-Gil, Kongdo-Eup, Anseong, Kyunggi-Do, Republic of Korea. Memail: hdlee@cnu.ac.kr; hmkwon@ kopo.ac.kr

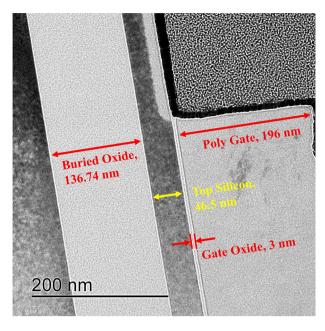

Figure 1. TEM image of the cross-section of an FD-SOI TFET.

In this study, we investigated the effects of high-pressure  $D_2$  and  $H_2$  annealing on the LFN properties of a fully depleted silicon-on-insulator (FD-SOI) pTFET. Multilevel RTN due to one fast trap site and one slow trap site was observed in the case without high-pressure annealing. High-pressure deuterium annealing (HPDA) had a curing effect on both fast and slow trap sites for a wide range of gate oxide depths. The interface trap density related to the fast trap sites was extracted by using the charge pumping method. Furthermore, we extracted the slow trap sites induced by fluctuation in the pTFET operation region. Our findings indicate that high-pressure annealing may be a significant and essential step toward improving the electrical performance and LFN properties of pTFETs.

#### Methods

TFETs were fabricated by using the FD-SOI technology. The top silicon layer was 46.5 nm thick with a doping concentration of about  $10^{16}$  cm<sup>-3</sup>. The gate oxide layer was 3 nm thick and consisted of SiO<sub>2</sub>. n + poly-silicon (Si) was grown by low-pressure chemical vapor deposition. After the poly-Si gate electrode was patterned, arsenic implantation was applied from the source, and the drain was doped with BF<sub>2</sub> implantation. The doping concentration was about  $3 \times 10^{20}$  cm<sup>-3</sup> for both the source and drain. The pTFET had a width of 50 µm and length of 0.25 µm. A Cs-corrected scanning transmission electron microscopy image of the FD-SOI pTFET is shown in Fig. 1. After metal patterning, rapid thermal annealing for activation was performed for 10 s at 950 °C. To improve the LFN characteristics, post-metal annealing was performed for 30 min at 400 °C and 10 atm using D<sub>2</sub> gas (6% D<sub>2</sub> and 94% N<sub>2</sub>) or H<sub>2</sub> gas (6% H<sub>2</sub> and 94% N<sub>2</sub>).

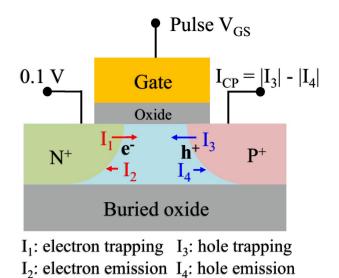

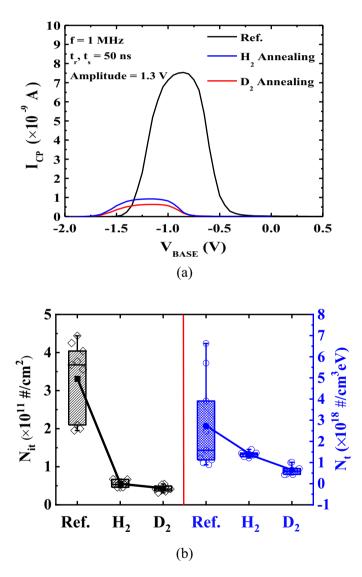

An Agilent 4156C semiconductor parameter analyzer was used to evaluate the electrical characteristics. A noise measurement system was used to characterize the LFN<sup>12</sup>. To separate the variability of the drain current, the typical noise power spectral density (PSD) was averaged 15 times. The normalized drain current noise  $(S_{ID}/I_{DS}^2)$ was measured at  $|V_{DS}| = 0.3$  V, and  $V_{GS}$  was a constant at  $|I_{DS}| = 1 \mu A$ . The RTN was measured for up to 2 s at the observed time domain and voltage at a specific frequency under the same conditions. The RTN was not averaged because it occurs during the short capture and emission events induced by a channel carrier. The charge pumping method for no-body contact was previously studied for a floating-body device<sup>4,13</sup> and the three-dimensional interface of a fin structure<sup>14</sup>. Despite the no-body contact, the charge pumping method for TFETs is similar to the conventional charge pumping method for CMOSFETs. A charge pumping current could be measured in the p<sup>+</sup> region similar to the body contact when a pulse was applied to the TFET gate, as shown in Fig. 2. A potential of 100 mV was applied to the n<sup>+</sup> region, which was sufficient to eliminate the geometric component<sup>15</sup>. The interface trap density  $(N_{it})$  was extracted by using a fixed-amplitude charge pumping measurement method. A 1-MHz square waveform was applied to the gate terminator by an 81104A pulse generator (Agilent), and the charge pumping current was simultaneously measured by using the Agilent 4156C semiconductor parameter analyzer. The periodic trapezoidal pulses had a rising/falling time of 50 ns, amplitude of 1.3 V, base level of -1.8 V, and duty cycle of 50%.

#### **Results and discussion**

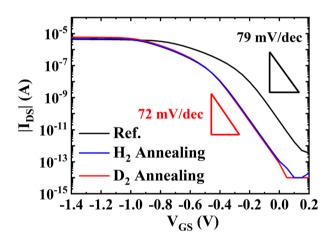

Figure 3 compares the electrical performances of the FD-SOI pTFET without annealing (black), with high-pressure hydrogen annealing (HPHA, blue), and with HPDA (red). The SS of the pTFET was 79 mV dec<sup>-1</sup> without annealing and 72 mV dec<sup>-1</sup> with HPDA. The on-current also increased by ~ 33% from 4.44  $\mu$ A without annealing to 5.92  $\mu$ A with HPDA, and Vtcc at 1 nA shifted by – 200 mV. This demonstrates that HPDA resulted in effective passivation.

**Figure 2.** Schematic of the charge pumping method with the FD-SOI pTFET. When a pulse is applied to the pTFET gate, the charge pumping current is measured in the  $p^+$  region with the body contact. The reverse voltage at the  $n^+$  region is set to 100 mV, which is sufficient to eliminate the geometric component.

**Figure 3.** Subthreshold swing and electrical performance of the FD-SOI pTFET: without annealing (black), with HPHA (blue), and with HPDA (red).

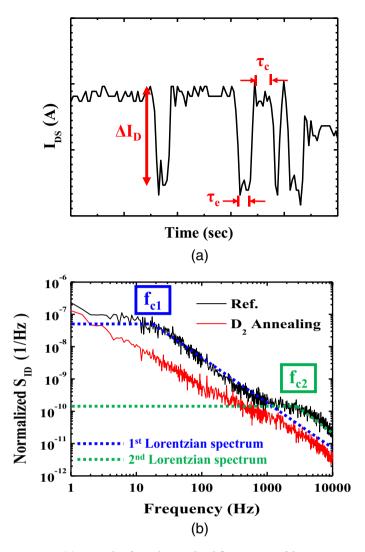

For a single trap, RTN was observed at two discrete levels in the time domain, as shown in Fig. 4a. RTN exhibited a high or low state in the time domain denoted by  $\tau_c$  and  $\tau_e$ , respectively. If the dominant trap sites within a gate oxide have different levels, the current can fluctuate between two or more states, similar to an RTN waveform, because of random trapping and/or de-trapping of carriers within trap centers. The noise PSD of the current fluctuation can be calculated from the time domain data as follows<sup>16</sup>:

$$\frac{S_{ID}}{I_D^2} = \left(\frac{4\tau_r^2}{\tau_t}\right) \left(\frac{\Delta I_D}{I_D}\right)^2 \left[\frac{1}{1 + (2\pi f \tau_r)^2}\right] \tag{1}$$

$$f_c = \frac{1}{2\pi} \left( \frac{1}{\tau_c} + \frac{1}{\tau_e} \right) \tag{2}$$

where  $\tau_c$  is the capture-time constant (i.e., time until an electron is captured within a trap site) and  $\tau_e$  is the emission time constant (i.e., time until the electron is emitted from the trap site). These can be used to obtain  $\tau_r = \tau_c \tau_e/(\tau_c + \tau_e)$  and  $\tau_t = \tau_c + \tau_e$ , *f* is the frequency,  $f_c$  is the plateau region or corner frequency of the Lorentzian spectrum where the noise level is independent of frequency, and  $\Delta I_{DS}$  is the amplitude of the current induced by fluctuation. As shown in Fig. 4b, the PSD for RTN at two discrete levels has Lorentzian spectra with a corner frequency (blue or green dash lines). A longer  $\tau_c$  is required as the trap moves further away from the channel, and  $f_c$

**Figure 4.** (a) Example of two discrete level fluctuations of drain current in the time domain induced by a single trap site. (b) Typical noise power spectral densities of the FD-SOI pTFET without annealing (black) and with HPDA (red). Two  $f_c$  without annealing can be observed with the superposition of different Lorentzian spectra, and the PSD is steeper with the HPDA than without the HPDA.

corresponds to the location information of trap sites by (2)<sup>16</sup>. Interestingly, several  $f_c$  can be observed with the superposition of different Lorentzian spectra when multilevel RTN is induced from a number of trap sites. As shown in Fig. 4b, the PSD without high-pressure annealing (black) had two Lorentzian spectra. The first spectrum was caused by a slow trap site near 20 Hz ( $f_{Cl}$ , blue), and the second was caused by a fast trap site near 3000 Hz ( $f_{C2}$ , green). This means that the two trap sites were at different depths within the gate oxide near the source/channel junction. In contrast, Fig. 4b shows that the PSD with HPDA (red) exhibited only a flicker noise characteristic because the dominant trap sites within the gate oxide were passivated, which resulted in a uniform spatial distribution of the gate oxide traps.

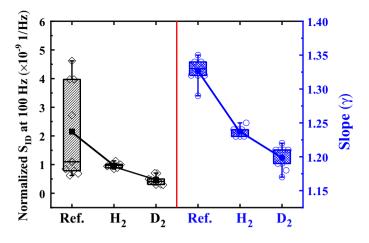

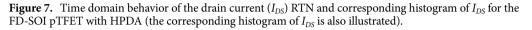

Figure 5 shows that the normalized  $S_{ID}/I_{DS}^2$  at 100 Hz was  $2.15 \times 10^{-9}$  Hz<sup>-1</sup> without annealing,  $9.53 \times 10^{-10}$  Hz<sup>-1</sup> with HPHA, and  $4.49 \times 10^{-10}$  Hz<sup>-1</sup> with HPDA. Thus, HPDA reduced the normalized  $S_{ID}/I_{DS}^2$  by ~ 79% compared to without annealing. The frequency exponent ( $\gamma$ ) also decreased with high-pressure annealing, which means that the trap sites within the gate oxide were nearly uniformly distributed in terms of energy and depth<sup>17</sup>.  $\gamma$  was 1.327 without annealing, 1.237 with HPHA, and 1.199 with HPDA. These  $\gamma$  values are in the same range as those obtained for silicon-based devices such as MOSFETs<sup>17</sup>.

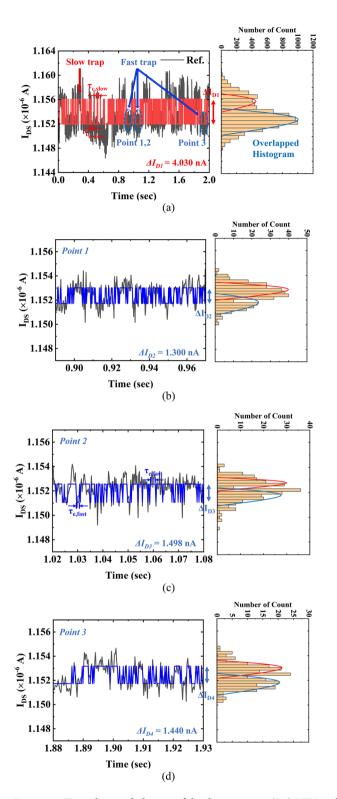

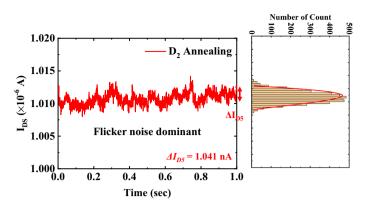

Figures 6 and 7 show the measured time domain drain current ( $I_{DS}$ )-RTN and the corresponding histograms for the FD-SOI pTFET without and with HPDA. The randomly observed  $I_{DS}$ -RTN was statistically analyzed to extract its distribution from the histogram<sup>18,19</sup>. The IDS-RTN measured for the pTFETs without and with HPDA was obtained by decoupling individual current levels using the change point detection method. Figure 6a shows the multilevel RTN due to one fast trap site and one slow trap site, along with an enlarged view of the fast trap site. The multilevel RTN indicated the non-uniformity of the traps. The multilevel RTN can also be identified in the enlarged views of the fast trap site, as shown in Fig. 6b–d. In general, bulk traps (i.e., slow traps) that are

**Figure 5.** Normalized drain current noise  $(S_{ID}/I_{DS}^2)$  and frequency exponent ( $\gamma$ ) as a function of the annealing conditions.

relatively deep require a long period for  $\tau_c$  and  $\tau_e$ , whereas shallow interface traps (i.e., fast traps) require a short  $\tau_c$  and  $\tau_e$ . The trap depth is connected to the RTN amplitude ( $\Delta I_D/I_D$ ), and a larger RTN amplitude indicates a further distance from the existing trap in the gate oxide.

The variations in the drain current induced by slow and fast trap sites were  $\Delta I_{DI} = 4.030$  nA,  $\Delta I_{D2} = 1.300$  nA,  $\Delta I_{D3} = 1.498$  nA, and  $\Delta I_{D4} = 1.440$  nA. Figure 7 shows that the flicker noise was dominant after HPDA, which means that the typical characteristic of the RTN was no longer observed. This is consistent with the PSD with HPDA, as shown in Fig. 7. The amplitude was  $\Delta I_{D5} = 1.041$  nA after HPDA, which shows that the  $I_{DS}$  amplitude was reduced compared with the case without annealing. This indicates that HPDA had a curing effect on both fast and slow trap sites for a wide range of gate oxide depths.

To verify the interface trap density related to the fast trap sites,  $N_{it}$  was extracted by using the charge pumping method for no-body contact<sup>13</sup>.  $N_{it}$  can be calculated from  $I_{CP}$  in Fig. 8a as follows<sup>13</sup>:

$$N_{it} = \frac{I_{cp,max}}{Aqf_p} \tag{3}$$

where  $I_{CP}$  is the charge pumping current, A is the gate area, q is the unit charge, and  $f_p$  is the pulse frequency. Figure 8b shows that the  $N_{it}$  values were  $3.307 \times 10^{11}$  cm<sup>-2</sup> without annealing,  $5.559 \times 10^{10}$  cm<sup>-2</sup> with HPHA, and  $4.286 \times 10^{10}$  cm<sup>-2</sup> with HPDA. This means that  $N_{it}$  related to the fast trap sites was reduced because of passivation by HPDA and HPHA. The slow trap sites were attributed to the capture and emission of channel carriers by the trap sites in the gate oxide, which caused a large RTN amplitude as mentioned previously. The trap sites near the tunneling junction contributed to the LFN. Thus, pTFET design must consider the influence of the tunneling junction characteristics as well as channel transportation, and its impact on device design and circuit performance may need to be quantified. The small-signal model proposed by Wan et al.<sup>20</sup> was used to calculate the total PSD of the pTFET, in which a tunneling diode and MOSFET are connected in series. The accuracy of the LFN model for the FD-SOI TFET was verified by Yaron and Frohman-Bentchkowsky<sup>21</sup>, and it can be calculated as follows:

$$\frac{S_{ID}}{I_D^2} = \left(\frac{1}{1+\kappa}\right)^2 \left\{ \left(\frac{\beta\kappa^2}{A}\right) \left(\frac{1}{N} + \alpha\mu\right)^2 \frac{1}{f} + \left(\frac{4\tau_r^2}{\tau_t}\right) \left(\frac{\Delta I_D}{I_D}\right)^2 \left[\frac{1}{1+(2\pi f\tau_r)^2}\right] \right\}$$

(4)

$$=kT\lambda N_t$$

(5)

where  $\kappa = R_c/R_t$ ,  $R_t$  is the tunneling junction resistor,  $R_c$  is the channel resistor, and the pre-factor  $[1/(1 + \kappa)] (4\tau_r^2/\tau_t) = 5 \times 10^{-5} \text{ Hz}^{-1}$  and pre-factor  $[\kappa/(1 + \kappa)]^2(\beta/A)[1/N + \alpha\mu]^2 = 9 \times 10^{-9}$  are assumed constant<sup>21</sup>.  $\beta$  is proportional to the trap density but is independent of  $|V_{GS}|$ ; N is the carrier density in the channel and is assumed to be  $10^{12} \text{ cm}^{-2}$  for a p-poly-SiO<sup>2</sup> system<sup>22-24</sup>.  $\alpha$  is the scattering coefficient, and it was reported to be  $10^5 \text{ Vs C}^{-1}$  for holes<sup>25</sup>.  $\mu$  is the carrier defective mobility<sup>22</sup>, and it was assumed to be 300 cm<sup>2</sup> Vs<sup>-1</sup>. However, it is so small that it does not affect the final value in the calculation with (4). In other words,  $N_t$  can be obtained from (5), where k is the Boltzmann constant, T is the temperature, and  $\lambda$  is the tunneling attenuation length ( $\approx 0.1 \text{ nm in SiO}_2$ )<sup>26</sup>.

β

As shown in Fig. 8b,  $N_t$  from (5) was  $2.72 \times 10^{18} \text{ eV}^{-1} \text{ cm}^{-3}$  without annealing,  $1.35 \times 10^{18} \text{ eV}^{-1} \text{ cm}^{-3}$  with HPHA, and  $6.55 \times 10^{17} \text{ eV}^{-1} \text{ cm}^{-3}$  with HPDA. This means that  $N_t$  related to the slow trap sites was reduced because of passivation by HPDA and HPHA. Therefore, the results show that HPHA and HPDA are potentially significant and essential for future integrated TFET technology because they reduce typical noise characteristics such as the RTN and LFN as well as the thermal budget.

**Figure 6.** Time domain behavior of the drain current  $(I_{DS})$  RTN and corresponding histogram of  $I_{DS}$  for the FD-SOI pTFET without HPDA (the corresponding histogram of  $I_{DS}$  is also illustrated). (a) Multilevel RTN is induced by a slow trap site and fast trap site. (b) Point 1: Enlarged view of the fast trap site from 0.89 to 0.97 s. (c) Point 2: Enlarged view of the fast trap site from 1.02 to 1.08 s. (d) Point 3: Enlarged view of the fast trap site from 1.88 to 1.93 s.

**Figure 8.** (a) Charge pumping current as a function of the gate pulse base voltage without and with HPHA and HPDA. The relation between the interface trap density and fast trap sites was verified by using the charge pumping method in pTFET. (b) Comparison of the interface trap density ( $N_{it}$ ) extracted by the charge pumping method and trap density extracted by the unified model as a function of the annealing conditions.  $N_{it}$  and  $N_t$  are related to the fast and slow trap sites, respectively, and indicate passivation via HPDA and HPHA.

#### Conclusion

This study evaluated the effects of HPDA and HPHA on the LFN properties of an FD-SOI pTFET. HPDA was found to improve the electrical performance and LFN properties. The PSD without high-pressure annealing had two Lorentzian spectra while the PSD with HPDA had a steeper slope. The multilevel RTN without high-pressure annealing was caused by one fast trap site and one slow trap site. The Nit related to the fast trap sites and Nt related to the slow trap sites were reduced by passivation via HPDA and HPHA. These results indicate that HPHA and HPDA are potentially significant and essential for future integrated TFET technology.

#### Data availability

The datasets generated during and/or analyzed during the current study are available from the corresponding author after reasonable request.

Received: 2 March 2022; Accepted: 17 October 2022 Published online: 02 November 2022

#### References

- Choi, W. Y., Park, B.-G., Lee, J. D. & Liu, T.-J.K. Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. *IEEE Electron Dev. Lett.* 28, 743–745. https://doi.org/10.1109/LED.2007.901273 (2007).

- Tomioka, K. & Fukui, T. Tunneling field-effect transistor using. Appl. Phys. Lett. 98, 083114. https://doi.org/10.1063/1.3558729 (2011).

- Vanlalawpuia, K. & Bhowmick, B. Investigation of Ge-source vertical TFET with delta-doped layer. *IEEE Trans. Electron Dev.* 66, 4439–4445. https://doi.org/10.1109/TED.2019.2933313 (2019).

- Shin, H.-J. et al. Correlation between low-frequency noise and interface traps of fully-depleted silicon-on-insulator tunneling FETs induced by hot carrier stress. Jpn. J. Appl. Phys. https://doi.org/10.35848/1347-4065/abb8f0 (2020).

- Wan, J., Royer, C. L., Zaslavsky, A. & Cristoloveanu, S. Low-frequency noise behavior of tunneling field effect transistors. *Appl. Phys. Lett.* 97, 243503–243501. https://doi.org/10.1063/1.3526722 (2010).

- Shin, H.-J. et al. A study on dominant mechanism and analytical model of low-frequency noise in FD-SOI pTFET. IEEE J. Electron Dev. Soc. 10, 679–686. https://doi.org/10.1109/JEDS.2022.3199763 (2022).

- Onishi, K. et al. Improvement of surface carrier mobility of HfO/Sub 2/ MOSFETs by high-temperature forming gas annealing. IEEE Trans. Electron Dev. 50, 384–390. https://doi.org/10.1109/TED.2002.807447 (2003).

- Yang, G. et al. Reduction of random telegraph noise by high-pressure deuterium annealing for p-type omega-gate nanowire FET. Nanotechnology 31, 415201. https://doi.org/10.1088/1361-6528/ab9e90,Pubmed:32559755 (2020).

- Song, H.-D. et al. Experimental optimization of post metal annealing on fully depleted-silicon on insulator tunneling field effect transistor. Jpn. J. Appl. Phys. 59, 1193–1196. https://doi.org/10.35848/1347-4065/ab8e1c (2020).

- 10. Park, H. *et al.* Effect of high pressure deuterium annealing on electrical and reliability characteristics of MOSFETs with high-k gate dielectric. In *IEEE Int. Reliab. Phys. Symp. Proc.*. 43rd Annual (2005).

- Lee, J. et al. Application of high pressure deuterium annealing for improving the hot carrier reliability of CMOS transistors. IEEE Electron Dev. Lett. 21, 221–223. https://doi.org/10.1109/55.841302 (2000).

- Kwon, H.-M. et al. Characterization of random telegraph signal noise of high-performance p-MOSFETs with a high-k dielectric/ metal gate. IEEE Electron Dev. Lett. 32, 686–688 (2011).

- Groeseneken, G., Maes, H. E., Beltran, N. & De Keersmaecker, R. F. D. A reliable approach to charge-pumping measurements in MOS transistors. *IEEE Trans. Electron Dev.* 31, 42–53. https://doi.org/10.1109/T-ED.1984.21472 (1984).

- Ouisse, T. et al. Adaptation of the charge pumping technique to gated p-i-n diodes fabricated on silicon on insulator. IEEE Trans. Electron Devices 38, 1432–1444. https://doi.org/10.1109/16.81636 (1991).

- Dou, C. et al. Characterization of interface state density of three-dimensional Si nanostructure by charge pumping measurement. Microelectron. Rel. 54, 725–729 (2014).

- 16. Haartman, M. & Ostling, M. Low-Frequency Noise in Advanced Mos Devices 92 (Springer Science+Business Media, 2007).

- Francis, S. A., Dasgupta, A. & Fleetwood, D. M. Effects of total dose irradiation on the gate-voltage dependence of the 1/f noise nMOS and pMOS transistors. *IEEE Trans. Electron Dev.* 57, 503–510. https://doi.org/10.1109/TED.2009.2036297 (2010).

- Roux-dit-Buisson, O., Ghibaudo, G. & Brini, J. Model for drain current RTS amplitude in small-are MOS transistors. Solid State Electron. 35, 1273–1276. https://doi.org/10.1016/0038-1101(92)90161-5 (1992).

- 19. Tega, N. *et al.* Anomalously large threshold voltage fluctuation by complex random telegraph signal in floating gate flash memory. In *Int. Electron. Devices Meeting* (2006).

- Wan, J., Le-Royer, C. L., Zaslavsky, A. & Cristoloveanu, S. A tunneling field effect transistor model combining interband tunneling with channel transport. J. Appl. Phys. 110, 104503. https://doi.org/10.1063/1.3658871 (2011).

- Bu, S. T., Huang, D. M., Jiao, G. F., Yu, H. Y. & Li, M.-F. Low frequency noise in tunneling field effect transistors. *Solid State Electron*. 137, 95–101. https://doi.org/10.1016/j.sse.2017.08.008 (2017).

- Yaron, G. & Frohman-Bentchkowsky, D. Capacitance voltage characterization of poly Si-SiO2-Si Structures. Solid State Electron. 23, 433–439. https://doi.org/10.1016/0038-1101(80)90078-7 (1980).

- 23. Choi, S. *et al.* Interface analysis of ultrathin SiO2 layers between c-Si substrates and phosphorus-doped poly-Si by theoretical surface potential analysis using the injection-dependent lifetime. *Prog. Photovolt. Res. Appl.* **29**, 32–46 (2020).

- 24. Devireddy, S. P. et al. İmproved low frequency noise characteristics of sub-micron MOSFETs with TaSiN/TiN gate on ALD HfO2 dielectric. *Microelectron. Rel.* 47, 12281232 (2007).

- Bennamane, K. *et al.* Mobility couping effects due to remote coulomb scattering in thin-film FD-SOI CMOS devices. *Electron.* Lett. 49, 490–492. https://doi.org/10.1049/el.2012.4150 (2013).

- 26. Grasser, T. Noise in Nanoscale Semiconductor Devices 36 (Springer, 2022).

#### Acknowledgements

This research work was supported by the Ministry of Trade, Industry, and Energy (MOTIE) (Grant No. 10067808) and the Korea Semiconductor Research Consortium (KSRC) support program for the development of future semiconductor devices. This research was supported by National R&D Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science and ICT (2022M3I8A1078437). This work was also supported by the National Research Foundation of Korea (NRF) funded by the National Research Foundation of Korea (NRF) funded by the Korean Government (MSIT) (Grant No. NRF-2019S1A5C2A03081332 and Grant NRF-2022R1F1A1008954).

### Author contributions

H.-J.S. conducted most of the experiments and wrote the manuscript, including preparing the figures, electrical characterization, and low-frequency noise properties. H.-J.S., S.B.E., Y.-J.A., T.-G.R., and D.-W.K. prepared the original draft of the manuscript. H.-D.L. and H.-M.K. initiated the work, provided the main idea, supervised the entire process, and reviewed the manuscript. H.-D.L. supported the funding acquisition. All authors analyzed and discussed the results. All authors have read and agreed to the published version of the manuscript.

#### **Competing interests**

The authors declare no competing interests.

#### Additional information

Correspondence and requests for materials should be addressed to H.-D.L. or H.-M.K.

Reprints and permissions information is available at www.nature.com/reprints.

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

© The Author(s) 2022