Abstract

Light initiated multi-gate semiconductor switch (LIMS) is a kind of power electronic device which has many differences from traditional thyristor triggered by electric pulse. LIMS is triggered by laser, the turn-on time is smaller, and the anti-electromagnetic interferences is strong. The opening mode of LIMS is obviously different to traditional thyristor. After the laser into the gate area, a large number of electrons and holes will appear in P-base region, holes gather in the area of P-base in PN junction J2, and electrons gather in N-drift region around the PN junction J2. PN junction J2 will open first, then PN junction J3 opens. The delay time of the NPN and PNP thyristors is close to zero when the laser pulse is narrow and the peak power is high, so the turn-on velocity is fast. To optimize the characteristics of the LIMS at high temperatures, we propose a new structure of the LIMS with the optimization of the n+ layer, circular light gate, and the new-style edge termination. The diameter of the LIMS is 23 mm. The experiment results show that the leakage current of the proposed LIMS has been decreased from more than 1 mA to 500 μA at 125 °C, the output current of the LIMS is 10.2 kA with a voltage of 4 kV at 85 °C, and the output current of the LIMS is 12.1 kA with a voltage of 4 kV at − 55 °C. Additionally, di/dt is larger than 30 kA/μs.

Similar content being viewed by others

Introduction

As the most powerful semiconductor switches, electrically-triggered and light-triggered thyristors are the devices of choice for ultra-high voltage power applications, such as high voltage direct current (HVDC) transmission or pulsed power application1,2,3,4,5. Compared with the electrically-triggered thyristor, the light-triggered thyristor has more advantages in simplifying the driver circuit and improving electromagnetic compatibility6. However, in the ultra-high pulsed power system, such as for railgun applications, the turn-on time is short and the di/dt of the thyristor is high, resulting in traditional electrically-triggered and light-triggered thyristors being unable to fulfill the above requirement. Accordingly, the light initiated multi-gate semiconductor switch (LIMS) has been proposed. LIMS is a kind of power electronic device that possesses many differences from the traditional thyristors triggered by electrical or light pulses. The LIMS is triggered by lasers, and the turn-on velocity is fast, where the di/dt is higher than 60 kA/μs.

However, the structure of the LIMS is similar to the thyristor, which contains four layers of different doping, forming an N-P-N and a P-N-P bipolar transistor. Under high operating temperatures, the leakage current of the LIMS will increase amplified by the transistor gains, leading to the parasitic turn-on of the thyristor. This will degrade the functioning of the application in some cases, such as for military, utility, and aerospace applications6,7.

The study shows that the thyristor leakage current at high temperatures can also come from surface currents at the chip terminal8. Then, adequate edge termination and passivation techniques are necessary to minimize the leakage current, representing a significant part of the total leakage current in the LIMS.

In this paper, a new structure of the LIMS with the optimization of the n+ layer, circular gate, and the new-style edge termination has been proposed, with the diameter of the LIMS being 23 mm. The leakage current of the proposed LIMS is about 500 μA at 125 °C, and the output current of the LIMS is 10.2 kA with a voltage of 4 kV at 85 °C.

Principle of LIMS

Figure 1a is the structure of the traditional Si LIMS chip. The LIMS is almost identical to the structure of thyristor, except for the gate area, to excite more carriers by photons. However, the opening mode of the LIMS is obviously different from the traditional electrically triggered thyristor. After the laser is pointed into the light-triggered area, many electrons and holes will appear in the P-base region, holes gather around P-base in the PN junction J2, and electrons gather in the N-drift region around the PN junction J2. When the laser pulse is narrow and the peak power is high, the NPN thyristor will open before the PNP thyristor, but the delay time of the NPN and PNP thyristors is minimal. When the laser energy in unit time (laser energy and pulse width) is suitable, the PNP thyristor and NPN thyristor will open at one time. Therefore, the turn-on velocity of the LIMS is fast.

Characteristics of LIMS at high temperatures

The current I of the LIMS can be expressed by the following equation9

Here, Io is the light-triggered current, and tnpn and tpnp are the transportation times of the carriers at the p-base and n-drift area, respectively.

where Wp and Wn are the thicknesses of p-base and n-drift, respectively; Wdn is the thickness of the depletion layer; and Dn and Dp are the diffusion coefficients of the electron and hole, respectively.

The di/dt of the LIMS can be expressed by the following equation9:

The di/dt is related to the light-triggered current, the thickness of p-base, n-drift, and the depletion layer.

The key leakage current of the LIMS can be expressed by the following equation10:

Here, Lp is the diffusion length of the hole, ND is the dopant concentration of the n-drift, ni is the intrinsic carrier concentration, and τ is the carrier lifetime. It can be seen that, from Eqs. (3) and (4), the leakage current and di/dt will be affected by Wdn and Dp. Lp, ND, and τ will affect the leakage current, and Dp, Lp, ND, and τ are all related to the temperature T. Therefore, the leakage current and di/dt at high temperature should be considered comprehensively while setting parameters of the LIMS chip.

Based on the above theory, the leakage current and turn-on velocity (di/dt) are related to the thickness of the depletion layer, a new structure of the LIMS with the optimization of the n+ layer, and circular gate, so the new-style edge termination has been proposed11. To decrease the leakage current at high temperatures, the n− (i) layer has been inserted between the p-base and n-drift, and the passivation layer (SiO2) has been added at the beveled termination, which will decrease the surface state density.

To increase the turn-on velocity (di/dt), a multi-light triggered electrode structure of cathode for LIMS has been proposed, as shown in Figs. 1b and 2. The study shows that the distance l (Fig. 1b) of the n+ layer extends from the cathode electrode edge to the light triggered area, affecting the current’s peak value when the di/dt is high. Accordingly, the optimization of the n+ layer is important to the characteristics of the LIMS.

Simulation

The LIMS was modeled with Sentaurus. In the simulation, the structure, as is shown in Fig. 1b, was modeled in 2D dimensions. For the optimizational LIMS, the thickness and dopant concentration of the n+ layer are 10 μm and 1 × 1020 cm−3, respectively. The thickness and dopant concentration of the p-base layer are 35 μm and 2 × 1017 cm−3, respectively. The thickness and dopant concentration of the n− layer are 100 μm and 4 × 1012 cm−3, while those for the n-drift layer are 800 μm and 1.2 × 1013 cm−3, respectively. Furthermore, the thickness and dopant concentration of the p+ layer are 15 μm and 6 × 1017 cm−3, respectively. The distance l (Fig. 1b) of the n+ layer extending from the cathode electrode edge to the light triggered area is about 30 μm. Also, the passivation layer (SiO2) has been added at the beveled termination.

Additionally, the anode current was simulated by solving model equations in cylindrical coordinates. The optical window and cathode electrode are shown in Fig. 2. The monochromatic optical source was set to be uniformly irradiated to the optical windows.

Figure 3 presents the simulation results. The simulation results in Fig. 3 show that the leakage current of the LIMS with the optimization of the n+ layer, circular gate, and the new-style edge termination is 480 μA with a dc voltage of 5 kV and a temperature of 125 °C (the leakage current of the traditional thyristor in Fig. 1a is larger than 1 mA, as shown in Fig. 3).

Experiment and results

The Si LIMS used in this paper was in a n+pn−np+ structure, with the schematic representation shown in Fig. 1b. The thickness and dopant concentration of the n+ layer, p-base layer, n− layer, n-drift layer, p+ layer for the LIMS are the same as the description in the section "Simulation". The distance l of the n+ layer extending from the cathode electrode edge to the light triggered area is about 30 μm. Figure 4 presents the picture of the prepared Si LIMS, with the diameter of the LIMS chip being 23 mm.

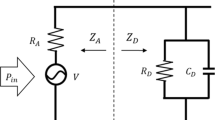

Figure 5 is the schematic circuit diagram for evaluating the switching characteristics of the LIMS. In the figure, C represents the storage capacitor (1 μF), Rcharge is the charging resistor (1 kΩ), Rc is the load resistor, and Lc is the stray inductance. Herein, Rc corresponds to the resistance of LIMS and Load. Lc is the parasitic inductance, which originates from the layout wiring of the LIMS and other devices. A 980 nm LD (with the laser energy of 120 μJ and pulse width of 200 ns) was used as a light source to trigger the Si LIMS. The output current measurements through the LIMS were performed using a Rogowski coil whose sensitivity and response time were 0.1 V/A and 2.2 ns, respectively. The input voltage measurement was measured with the Tektronix P6015A High Voltage Probe.

As shown in Fig. 5, capacitor C charges while the LIMS is maintained in the off-state and discharges through an RLC circuit when the LIMS is triggered.

At a high temperature (125 °C), the leakage current of the prepared LIMS has been measured and is about 500 μA with a dc voltage of 5 kV (the leakage current of the traditional thyristor is larger than 1 mA). If the leakage current of the LIMS is high, part of the current for the capacitor charging is deviated by the LIMS and flows through the RLC circuit, resulting in a longer time required for charging the capacitor.

Then, the turn-on characteristic of the LIMS is measured. Figure 6a presents the discharging waveforms of the LIMS with a voltage of 4 kV at room temperature. It shows that, from Fig. 6a, the peak value of the output current is about 10.4 kA and di/dt is 35 kA/μs.

Figure 6b displays the discharging waveforms of the LIMS with a voltage of 4 kV at 125 °C (here, the capacitor C in Fig. 5 is 0.1 μF). In Fig. 6b, the peak value of the output current is about 2 kA and di/dt is 12 kA/μs. Figure 6c shows the discharging waveforms of the LIMS with a voltage of 4 kV at 85 °C. In Fig. 6c, the peak value of output current is about 10.2 kA and di/dt is about 30 kA/μs.

The characteristics of the LIMS at the low temperature of − 55 °C has also been measured. The discharging waveforms are shown in Fig. 6d. The peak value of the output current is about 12.1 kA and di/dt is about 43 kA/μs.

The conclusion can be made that the prepared LIMS can work steadily at high temperatures, the leakage current is about 500 μA at 125 °C, and the output current can achieve 10.2 kA at 85 °C (di/dt is larger than 30 kA/μs).

Conclusion

To optimize characteristics of the LIMS at high temperatures, we propose a new structure of LIMS with the optimization of the n+ layer, circular light gate, and the new-style edge termination, with the diameter of the LIMS being 23 mm. The experimental results show that the leakage current of the proposed LIMS has been decreased from more than 1 mA to 500 μA at 125 °C, the output current of the LIMS is 10.2 kA with a voltage of 4 kV at 85 °C, and the output current of the LIMS is 12.1 kA with a voltage of 4 kV at − 55 °C. Furthermore, di/dt is larger than 30 kA/μs. The LIMS has broad application potential in the fields of HVDC transmission or pulsed power.

Data availability

The data that comprise Fig. 6 are available from the corresponding author upon reasonable request.

References

Toulon, G., Bourennane, A. & Isoird, K. Analysis and optimization of a thyristor structure using backside schottky contacts suited for the high temperature. IEEE Trans. Electron Devices 60(11), 3814–3820 (2013).

Vobecky, J. et al. Silicon thyristors for ultrahigh power (GW) applications. IEEE Trans. Electron Dev. 64(3), 760–768 (2017).

Lips, H. P. Technology trends for HVDC thyristor valves. in Proc. Int. Conf. Power Syst. Technol., pp. 451–455 (1998).

Wang, X. et al. Demonstration of 4H-SiC thyristor triggered by 100-mW/cm2 UV light. IEEE Electron Device Lett. 41(6), 824–827 (2020).

Spahn, E., Buderer, G., Wey, J., Wegner, V. & Jamet, F. The use of thyristors as main switches in EML applications. IEEE Trans. Magn. 29(1), 1060–1065 (1993).

Nakagawa, T., Satoh, K., Yamamoto, M., Hirasawa, K., & Ohta, K. 8 kV/3.6 kA light triggered thyristor. in Proc. 7th ISPSD, 175–180 (1995).

Kokosa, R. A. & Tuft, B. R. A high-voltage, high-temperature reverse conducting thyristor. IEEE Trans. Electron Devices 17(9), 667–672 (1970).

Obreja, V. V. N., Codreanu, C., Podaru, C., Nuttall, K. I., & Buiu, O. The operation temperature of silicon power thyristors and the blocking leakage current. IEEE Power Electronics Specialists Conf., 2990–2993 (2004).

Baliga, B. J. Fundamentals of Power Semiconductor Devices 663–686 (Springer Science+ Business Media, 2008).

Vitezlav, B., John, G. & Duncan, A. G. Power semiconductor devices theory and applications 192–195 (Chemical Industry press, 2005).

Obreja, V. V. N., & Nuttall, K. I. On the high temperature operation of high voltage power devices. ESSDERC 1–4 (2002).

Acknowledgements

This work was Supported by the National Natural Science Foundation of China (Grant No. 61504127 and 51807185).

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Luan, C., Liu, H., Fu, J. et al. Study of a Si-based light initiated multi-gate semiconductor switch for high temperatures. Sci Rep 12, 15508 (2022). https://doi.org/10.1038/s41598-022-19767-4

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-022-19767-4

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.