Abstract

The interplay between ferromagnetism and topological properties of electronic band structures leads to a precise quantization of Hall resistance without any external magnetic field. This so-called quantum anomalous Hall effect (QAHE) is born out of topological correlations, and is oblivious of low-sample quality. It was envisioned to lead towards dissipation-less and topologically protected electronics. However, no clear framework of how to design such an electronic device out of it exists. Here we construct an ultra-low power, non-volatile, cryogenic memory architecture leveraging the QAHE phenomenon. Our design promises orders of magnitude lower cell area compared with the state-of-the-art cryogenic memory technologies. We harness the fundamentally quantized Hall resistance levels in moiré graphene heterostructures to store non-volatile binary bits (1, 0). We perform the memory write operation through controlled hysteretic switching between the quantized Hall states, using nano-ampere level currents with opposite polarities. The non-destructive read operation is performed by sensing the polarity of the transverse Hall voltage using a separate pair of terminals. We custom design the memory architecture with a novel sensing mechanism to avoid accidental data corruption, ensure highest memory density and minimize array leakage power. Our design provides a pathway towards realizing topologically protected memory devices.

Similar content being viewed by others

Introduction

Electronic bands of non-trivial topology give rise to quantum phenomena at macroscopic scale. Under a strong magnetic field, two-dimensional electron systems exhibit such a quantum state- the quantum Hall effect, i.e. the quantization of Hall resistance1. Back in 1988, Haldane2 predicted that a quantum Hall state can arise even in the absence of an external magnetic field. This new state became known as the quantum anomalous Hall effect (QAHE). However, it took more than two decades for the first experimental realization of QAHE, when it was demonstrated in a magnetic topological insulator [Cr-doped Bi(Sb)2Te3]3,4,5,6,7,8,9,10. The experimental fingerprint of QAHE is straightforward: The Hall resistance is quantized to h/ve2 (where \(\nu ,\) the so-called Chern number, is an integer that depends on the topological properties of the band structure) at zero magnetic field. Such simple and universal values stem from the current being carried by lossless edge channels which require neither high electron mobility11,12 nor external magnetic fields. Moreover, on a given edge, the current flows only in one direction. Thanks to such transport properties which are also immune to sample complexities11,12, QAHE can potentially be useful in spin-filtering11, resistance metrology13 and topological quantum computing14. However, how we can materialize these prospects and come up with a QAHE-based electronic device have remained elusive so far.

Here we bridge the gap between the QAHE physics and device architecture to build the framework of a scalable non-volatile memory. We utilize the quantization of Hall resistance in QAHE to design a memory cell and then construct a 3D cross-point memory array capable of efficient read and write operations.

Design of a QAHE based memory

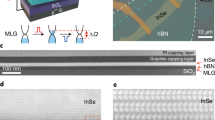

To design our memory cell, we use the intrinsic QAHE reported in a twisted bilayer graphene (tBLG) on hexagonal boron nitride (hBN) moiré heterostructure, where the quantization of Hall resistance persists at temperatures as high as 6 K1. This is significantly higher compared to the magnetic topological materials, such as transition metal doped (Bi, Sb)2Te3 thin films15,16,17,18 and MnBi2Te419.With the ongoing thrust in material discoveries, room-temperature applications may become feasible. Very recent works on QAHE in TbMn6Sn6, MnBi2Te4 offer such prospects20,21,22.

We start by delineating the dynamics of a QAH insulator and how it can be used as a non-volatile memory cell. Figure 1a illustrates the schematic of a QAH insulator with electric contacts to apply bias current and to measure both longitudinal and transverse (Hall) voltages. The QAH states occur when an applied gate voltage tunes the bulk carrier density to close to zero. Then, the Hall resistance shows a hysteretic switching with the change of magnetic field. Also, magnetic domains of the ferromagnetic materials (for example, tBLG) strongly interact with the applied electrical current, which provides the electrical control over the polarization of the magnetic domains23. It has also been shown1 that the switching of Hall resistance driven by DC bias current is similar to that driven by magnetic field. We leverage this tunability in our design. Broadly, our design can be implemented with any material platform harboring an electrically tunable QAHE. Note that the exact reason behind the electrical switching of QAHE in tBLG awaits a comprehensive understanding. Orientation of the graphene layers as well as the interaction between the electrical current and ferromagnetic domains in tBLG may play a role22. It is also worthwhile to add that electrically tunable QAHE is not unique in tBLG; tri-layer graphene (twisted monolayer-bilayer graphene) also shows similar tunability24,25.

Schematic representation of quantum anomalous Hall effect. (a) Schematic of our device, where the red circles represent the electron and the red arrows show the spin of the electrons. A gate voltage can be applied at the back of the substrate to control the electronic density. Vxx and Vxy are the longitudinal and transverse (Hall) voltages, respectively, developed in response to the bias current, IBias. (b) Illustration of the Hall resistance Rxy versus the bias current, IBias at zero external magnetic field. IC− and IC+ are two critical values of IBias which determine the hysteretic switching of Rxy between − h/e2 and h/e2.

Figure 1b shows a schematic of the hysteretic switching of Hall resistance Rxy (= Vxy/IBias) with the bias current at absolutely zero external magnetic field. Here, we mark two critical values of bias current, IC- and IC+, which denote the values of bias current required for the switching of Hall resistance between ± h/e2.

Figure 2 captures the highlight of our idea to leverage the quantized Hall resistance of a QAH insulator as a non-volatile memory cell along with the write and read operations. We define the quantized Hall resistances, − h/e2 and + h/e2, as logic ‘0’ and logic ‘1’ respectively. Based on this definition, IBias can be divided into three regions (Fig. 2a)—(i) IBias ≤ IC-: write ‘0’ region, (ii) IBias ≥ IC+: write ‘1’ region, and (iii) IC- < IBias < IC+: read region. Figure 2b shows the bias current dependence of the Hall voltage, Vxy (= IBias × Rxy). Importantly, as seen in Fig. 2b, write operations of both logic ‘0’ and ‘1’ entail positive Vxy because IBias and Rxy are either both positive (when writing logic ‘1’; Fig. 2c), or both negative (when writing logic ‘0’; Fig. 2d). In sharp contrast, read operations of logic ‘0’ and ‘1’ manifest opposite sign of Vxy. For example, if we use a positive bias current (0 < IBias < IC+), logic ‘1’ and logic ‘0’ correspond to positive and negative Vxy, respectively. The clear difference in the sign of the Hall voltage for logic ‘0’ and ‘1’ makes the sensing of the memory states simple and straightforward. Figure 2g summarizes the key idea of a non-volatile memory utilizing the quantization of the Hall resistance in a QAH insulator, listing IBias for write and read operations, as well as the state of the Hall resistance and Hall voltage for the two memory states.

Illustration of the quantum anomalous Hall effect based memory operation. (a) Rxy vs. IBias at zero external magnetic field. Hall resistance values of − h/e2 and + h/e2 are defined as logic ‘0’ and logic ‘1’ respectively. Three regions: (i) IBias ≤ IC-, (ii) IBias ≥ IC+, and (iii) IC− < IBias < IC+ are marked as write ‘0’, write ‘1’ and read region, respectively. We use this division to choose the required IBias for different memory operations. (b) Hall voltage, Vxy plotted as a function of IBias. (c), (d), (e), & (f) The procedures of write ‘0’, write ‘1’, read ‘0’, and read ‘1’ operations, respectively, along with the state of electron spins (red arrows). (g) Summary of the key idea for the QAHE based memory. The table enlists the required ranges of IBias corresponding to all memory operations, along with the corresponding Hall resistance and Hall voltage levels.

Operation of a QAHE based memory

It is worthwhile to analyze the operation of the proposed QAHE based non-volatile memory in a 3D cross-point memory array. Figure 3a schematically shows our memory element: a tBLG moiré heterostructure where tBLG (with interlayer twisted angle of 1.1\(^\circ\)) is encapsulated between flakes of hBN14. We have developed a Verilog A based phenomenological model for the QAHE in tBLG moiré heterostructure to use in our analysis of the heterostructure as a memory cell. The model can also be calibrated for other QAH insulators using the values of bias currents (IC- and IC+) and the Chern number (\(\nu\)). A behavioral representation of our model is shown in Fig. 3b. Figure 3c shows Rxy as a function of IBias at zero external magnetic field and at T = 4 K which is obtained from the model shown in Fig. 3b. As seen from Fig. 3c, we can deduce the values of IC- and IC+ for the tBLG heterostructure (approximately − 4 nA and 100 pA, respectively) which are crucial for the memory operation. In our phenomenological model, we also account for the temperature dependence of Hall resistance using the following Eq. 1:

where R1 is a fitting constant, \(\Delta\) (= 26 ± 4 K) is the energy required to create and separate an excitation of particle-antiparticle of the QAH state and T is the temperature. Figure 3d, which shows the temperature dependence of the Hall resistance obtained from our model, agrees reasonably with the measured values reported in Ref.1.

Design of the 3D cross-point memory array structure using a tBLG moiré heterostructure as a memory element and mixed-ionic-electronic-conduction based access device as selector. (a) Schematic of a tBLG moiré heterostructure where tBLG is encapsulated between flakes of hBN and a flake of few-layer graphite is used as gate. (b) Behavioral representation of our phenomenological model of the observed QAHE in the tBLG moiré heterostructure. (c) Rxy data, plotted as a function of IBias at T = 4 K and B = 0 T, exhibit current driven hysteretic switching. (d) Temperature dependence of Rxy with an experimental matching. (e) I–V characteristics obtained from a look-up table (LUT) based model of the mixed-ionic-electronic-conduction (MIEC) based selector device. (f) Illustration of the overall memory array structure, custom-designed for the QAHE based memory devices.

Design of a cross-point array

To evaluate the practicality of a memory device, it is crucial to consider an array level scenario. The unique properties of our QAHE based memory device necessitate a custom designed memory array. To ensure the highest storage density, we adopt the cross-point memory architecture26 with slight modification in the inter-cell connection pattern. A major component of the cross-point array is a two-terminal selector device27 that allows access to a specific cell for read/write operation and suppresses current flow through the other cells. The selector devices are connected in series with the memory elements in every cell. A multitude of selector devices exist28,29,30,31,32,33 with diverse selectivity (ON/OFF ratio) and switching thresholds. For our QAHE based memory, the Cu-containing mixed-ionic-electronic-conduction (MIEC) material will be a perfect selector, due to its high selectivity (~ 106), and ultra-low leakage (< 10 pA)34,35,36. We have developed a look-up-table based phenomenological model (in Verilog-A) for this selector and calibrated the model (Fig. 3e) with the measured current–voltage (I–V) characteristics reported in Refs.34,35,36.

Figure 3f shows the schematic view of our proposed array architecture. Every memory cell (QAHE device + selector) is sandwiched between orthogonally running metal lines, namely word line (WL) and bit line (BL). The WLs and the BLs are shared along the rows and columns of the array, respectively. The difference between the DC voltages applied on the WL and BL of a particular a memory cell essentially dictates the effective voltage across the cell (VCell). Note, the substrate terminal of every cell is biased with a constant voltage to maintain an appropriate electron density [not illustrated in the figures for simplicity]. Conveniently, we need only one control input, VCell, to read from or write into the QAHE devices. We utilize three different levels of VCell (with appropriate polarity) to write logic ‘1/0’ and to read the stored data.

Our architecture entails accessing one cell per row at a time. The Hall-voltage terminals of the neighboring cells in the same row are electrically connected in series with each other (Fig. 3f). Importantly, the resultant voltage across the end terminals of the series connected cells in a row (\({V}_{hr}\)) bears the signature of the stored data in the accessed memory cell, along with some residual contributions from the other cells in the same row. For example, consider that every row holds n cells, and the kth cell of the ith row is being accessed. The resultant terminal voltage for this row can be expressed as:

here \({V}_{loss}\) denotes the average loss component per contact, indicating the inherent non-ideality. The specialized biasing scheme of the memory array (discussed later) ensures that the losses and residual components are negligible (quantified in the Sect. 3 of the Supplementary Materials) compared with the Hall voltage of the accessed cell. As a result, the polarity of Vhr is dictated by the Rxy of the accessed cell. For the tBLG moiré heterostructure based QAHE device, we need to amplify the Vhr from a few tens of microvolts to tens of millivolts using cryogenic amplifiers. A suitable candidate for such an amplifier can be one of the cryogenic low-noise amplifiers reported in Refs.37,38,39. After the amplification, the millivolt level Hall voltage is used to determine the memory state of the accessed cell. Recall, during read operation, logic ‘0’ and ‘1’ memory states correspond to opposite polarity of Hall voltage (Fig. 2b). Therefore, we feed the amplified Vhr to a cryogenic voltage comparator40 to sense the memory state of the accessed cell.

Read/write operations

In Fig. 4, we present the simulated memory operations (read/write) in our proposed QAHE based cross-point array. Figure 4a illustrates four types of memory cells in a block of cross-point array. We utilize a standard biasing scheme for cross-pint arrays, commonly known as the V/2 biasing33. Different levels of access voltage (VACC) are applied to read from or write into a specific cell. The row (column) that holds the accessed cell is called the half-accessed row (column), because the inactive cells in this row (column) receive half of the access voltage (VACC/2). All the other unaccessed cells ideally have zero voltage across them. Without any loss of generality, we assume M11 (Fig. 3f) to be the accessed cell and examine its read/write dynamics. Figure 4b shows the cell current levels through the accessed, half-accessed, and unaccessed cells during 1→0 memory write operation. Only the accessed cell exhibits a transition (+ h/e2 → − h/e2) in the Hall resistance (Rxy) (Fig. 4c), indicating a successful write operation in the accessed cell without disturbing the other cells. Figure 4d,e show similar time dynamics for the 0→1 write operation. Note, the cell current level for the 0→1 operation is of the opposite polarity compared to the 1→0 operation (Fig. 4d). The repeated write operations (0→0 and 1→1) have also been tested and are presented in supplementary Fig. S2.

Compilation of the simulation results for the memory array. (a) Arrangement and types of memory cells in a conventional cross-point memory array under the V/2 biasing scheme. Write ‘0’ operation: (b) Cell Bias currents (IBias) through different memory cells generated by applying appropriate VACC (c) The time dynamics of the Hall resistance (Rxy) illustrating state transition only in the accessed cell. Write ‘1’ operation: (d) IBias with different magnitude and opposite polarity (compared with the write ‘0’ case) flowing through different memory cells (e) Corresponding transition in Rxy. Read operation: (f) The IBias is of the same polarity as the write ‘o’ operation, but has ~ 3X lower magnitude. The peripheral circuits (amplifier and comparator) are enabled only during this period. The comparator output is always initialized at zero volage. (g) If the memory cell holds binary ‘0’, the Hall voltage (Vxy) exhibits a positive polarity during the read operation. Rxy remains unchanged throughout the process. (h) The amplified Vxy is fed into a comparator which produces a digital output. While reading ‘0’, the comparator output remains unchanged at its initial value (0 V). (i) Read ‘1’ operation produces the opposite polarity in Vxy, and Rxy remains unchanged. (j) The amplified Vxy triggers a 0→VDD transition in the comparator output, which remains stable throughout the read operation.

Next, we examine the read dynamics (Fig. 4f–j) of the proposed memory cell. The current flow direction for the read operation is the same as the 1→0 write operation (Fig. 4f). However, the magnitude of the read current is about one-third of the critical current of transition (IC-), which alleviates the possibility of accidental 1→0 data flip. In addition, the chosen polarity of the read current nullifies the possibility of accidental 0→1 transition. The read current through the QAHE device generates a Hall voltage (Vxy), whose polarity is dictated by the previously set Hall resistance ((+ h/e2 or − h/e2). In our design, positive/negative polarity of Vxy corresponds to logic 0/1, respectively (Fig. 4g,i). It is worth noting, the read operation utilizes different pair of terminals than the write operation, allowing independent optimization of read/write peripheral circuits. Furthermore, the amplifier-comparator pairs are enabled only during the read operation to minimize peripheral power demand. The comparator in our design also provides digital outputs corresponding to the stored data in the accessed cell (Fig. 4h,j). Note, the resistance of the MIEC exponential selector drastically increases for lower voltage range (< 0.35 V), as shown in supplementary Fig. S5. The array biasing scheme is designed to enforce high resistance mode of the selector in every memory cell but the accessed cell. This design technique ensures that the half-accessed and unaccessed cells encounter orders of magnitude less current compared with the accessed cell. The MIEC selector takes an overwhelming share of any voltage applied across the cell, averting the chances of a breakdown in the QAHE device. The bias currents that flow through the cells during different memory operations are shown in Fig. 4k which clearly demonstrate that the memory states of the half-accessed and unaccessed cells will not be disturbed during write or read operation in the accessed cell. Thus, our architecture lays out a device-to-array design pathway for the QAHE based unique memory devices.

Outlook and discussion

Our cryogenic memory framework is transferable to the material structures that exhibit current-controlled switching of QAH states (e.g., tri-layer graphene24,25). Some of these material structures will necessitate an initialization step to first create a magnetic moment in the system. The additional analog components required for this purpose will be parts of the array peripherals. The underlying transition mechanisms of the QAHE devices may determine their endurance and reliable life span.

We close by discussing the broad impact of our work. This manuscript makes the first mark to construct a working electronic device using topological properties of materials. Here we leverage QAHE, that does not require an external magnetic field, and design an elegant memory device that can be built with topological quantum materials. The proposed non-volatile memory architecture is a strong candidate for the cryogenic memory system, thanks to its ultra-low temperature compatibility. Note, the cryogenic memory block is a crucial component of quantum computing systems based on superconducting qubits41. Our proposed QAHE-based memory device offers a significant reduction in the cell area and 1000 times reduction in the cell read/write power compared with the state-of-the-art cryogenic memory devices42,43,44,45,46,47,48,49 (see supplementary Table S1 for detailed comparison). Our proposed memory device is a potential game-changer for scalable quantum computing systems41 and space cryogenics50.

Data availability

The data that support the plots within this paper and other findings of this study are available from the corresponding author upon reasonable request.

References:

Serlin, M. et al. Intrinsic quantized anomalous Hall effect in a moiré heterostructure. Science 367, 900–903. https://doi.org/10.1126/science.aay5533 (2020).

Haldane, F. D. M. Model for a quantum hall effect without landau levels: condensed-matter realization of the ‘parity anomaly’. Phys. Rev. Lett. 61, 2015–2018. https://doi.org/10.1103/PhysRevLett.61.2015 (1988).

Chang, C. Z. et al. Experimental observation of the quantum anomalous Hall effect in a magnetic topological insulator. Science 340, 167–170. https://doi.org/10.1126/science.1234414 (2013).

Checkelsky, J. G. et al. Trajectory of the anomalous Hall effect towards the quantized state in a ferromagnetic topological insulator. Nat. Phys. 10, 731–736. https://doi.org/10.1038/nphys3053 (2014).

Kou, X. et al. Scale-invariant quantum anomalous hall effect in magnetic topological insulators beyond the two-dimensional limit. Phys. Rev. Lett. https://doi.org/10.1103/PhysRevLett.113.137201 (2014).

Bestwick, A. J. et al. Precise quantization of the anomalous hall effect near zero magnetic field. Phys. Rev. Lett. https://doi.org/10.1103/PhysRevLett.114.187201 (2015).

Kou, X. et al. Metal-to-insulator switching in quantum anomalous Hall states. Nat. Commun. https://doi.org/10.1038/ncomms9474 (2015).

Feng, Y. et al. Observation of the Zero Hall plateau in a quantum anomalous Hall insulator. Phys. Rev. Lett. https://doi.org/10.1103/PhysRevLett.115.126801 (2015).

Chang, C. Z. et al. High-precision realization of robust quantum anomalous Hall state in a hard ferromagnetic topological insulator. Nat. Mater. 14, 473–477. https://doi.org/10.1038/nmat4204 (2015).

Kandala, A., Richardella, A., Kempinger, S., Liu, C. X. & Samarth, N. Giant anisotropic magnetoresistance in a quantum anomalous Hall insulator. Nat. Commun. https://doi.org/10.1038/ncomms8434 (2015).

Oh, S. The complete quantum hall trio. Science 340, 153–154. https://doi.org/10.1126/science.1237215 (2013).

Jalil, M. B. A., Tan, S. G. & Siu, Z. B. Quantum anomalous Hall effect in topological insulator memory. J. Appl. Phys. https://doi.org/10.1063/1.4916999 (2015).

Götz, M. et al. Precision measurement of the quantized anomalous Hall resistance at zero magnetic field. Appl. Phys. Lett. https://doi.org/10.1063/1.5009718 (2018).

Lian, B., Sun, X. Q., Vaezi, A., Qib, X. L. & Zhang, S. C. Topological quantum computation based on chiral Majorana fermions. Proc. Natl. Acad. Sci. 115, 10938–10942. https://doi.org/10.1073/pnas.1810003115 (2018).

Lachman, E. O. et al. Visualization of superparamagnetic dynamics in magnetic topological insulators. Sci. Adv. https://doi.org/10.1126/sciadv.1500740 (2015).

Lee, I. et al. Imaging Dirac-mass disorder from magnetic dopant atoms in the ferromagnetic topological insulator Crx(Bi0.1Sb0.9)2-xTe3. Proc. Natl. Acad. Sci. U. S. A. 112, 1316–1321. https://doi.org/10.1073/pnas.1424322112 (2015).

Wang, W. et al. Visualizing ferromagnetic domains in magnetic topological insulators. APL Mater. https://doi.org/10.1063/1.4921093 (2015).

Yasuda, K. et al. Quantized chiral edge conduction on domain walls of a magnetic topological insulator. Science 358, 1311–1314. https://doi.org/10.1126/science.aan5991 (2017).

Deng, Y. et al. Quantum anomalous Hall effect in intrinsic magnetic topological insulator MnBi2Te4. Science 367, 895–900. https://doi.org/10.1126/science.aax8156 (2020).

Yin, J. X. et al. Quantum-limit Chern topological magnetism in TbMn6Sn6. Nature 583, 533–536. https://doi.org/10.1038/s41586-020-2482-7 (2020).

Deng, H. et al. Observation of high-temperature quantum anomalous Hall regime in intrinsic MnBi$_2$Te$_4$/Bi$_2$Te$_3$ superlattice. Nat. Phys. 17, 36–42. https://doi.org/10.1038/s41567-020-0998-2 (2021).

Liu, C. et al. Robust axion insulator and Chern insulator phases in a two-dimensional antiferromagnetic topological insulator. Nat. Mater. 19, 522–527. https://doi.org/10.1038/s41563-019-0573-3 (2020).

Sharpe, A. L. et al. Emergent ferromagnetism near three-quarters filling in twisted bilayer graphene. Science 365, 605–608. https://doi.org/10.1126/science.aaw3780 (2019).

Polshyn, H. et al. Electrical switching of magnetic order in an orbital Chern insulator. Nature 588, 66–70. https://doi.org/10.1038/s41586-020-2963-8 (2020).

Chen, S. et al. Electrically tunable correlated and topological states in twisted monolayer–bilayer graphene. Nat. Phys. https://doi.org/10.1038/s41567-020-01062-6 (2020).

Bez, R. Innovative technologies for high density non-volatile semiconductor memories. Microelectron. Eng. 80, 249–255. https://doi.org/10.1016/j.mee.2005.04.076 (2005).

Burr, G. W. et al. Access devices for 3D crosspoint memory. J. Vacuum Sci. Technol. B https://doi.org/10.1116/1.4889999 (2014).

Aziz, A., Jao, N., Datta, S. & Gupta, S. K. Analysis of functional oxide based selectors for cross-point memories. IEEE Trans. Circuits Syst. I Regul. Pap. 63, 2222–2235. https://doi.org/10.1109/TCSI.2016.2620475 (2016).

Virwani, K. et al. Sub-30nm scaling and high-speed operation of fully-confined Access-Devices for 3D crosspoint memory based on mixed-ionic-electronic-conduction (MIEC) materials. Int. Electron Dev. Meeting (IEDM) 2012, 2.7.1-2.7.4. https://doi.org/10.1109/IEDM.2012.6478967 (2012).

Hirose, S., Nakayama, A., Niimi, H., Kageyama, K. & Takagi, H. Resistance switching and retention behaviors in polycrystalline La-doped SrTiO3 ceramics chip devices. J. Appl. Phys. https://doi.org/10.1063/1.2975316 (2008).

Zhang, L., Govoreanu, B., Redolfi, A., Crotti, D., Hody, H., Paraschiv, V., Cosemans, S., Adelmann, C., Witters, T., Clima, S., Chen, Y. Y., Hendrickx, P., Wouters, D. J., Groeseneken, G. & Jurczak, M. High-drive current (>1MA/cm2) and highly nonlinear (>103) TiN/amorphous-Silicon/TiN scalable bidirectional selector with excellent reliability and its variability impact on the 1S1R array performance. International Electron Devices Meeting, (IEDM), 2014, 6–8, https://doi.org/10.1109/IEDM.2014.7047000 (2014).

Lee, W. et al. Varistor-type bidirectional switch (J MAX>10 7A/cm 2, selectivity∼10 4) for 3D bipolar resistive memory arrays. Symposium on VLSI Technology 37–38, 2012. https://doi.org/10.1109/VLSIT.2012.6242449 (2012).

Aziz, A., Shukla, N., Datta, S. & Gupta, S. K. Implication of hysteretic selector device on the biasing scheme of a cross-point memory array. International Conference on Simulation of Semiconductor Processes and Devices, SISPAD 425–428, 2015. https://doi.org/10.1109/SISPAD.2015.7292351 (2015).

Gopalakrishnan, K. et al. Highly scalable novel access device based on Mixed Ionic Electronic Conduction (MIEC) materials for high density phase change memory (PCM) arrays. Symposium on VLSI Technology 205–206, 2010. https://doi.org/10.1109/VLSIT.2010.5556229 (2010).

Shenoy, R. S. et al. Endurance and scaling trends of novel access-devices for multi-layer crosspoint-memory based on mixed-ionic-electronic-conduction (MIEC) materials. Symposium on VLSI Technology 2011, 94–95 (2011).

Burr, G. W. et al. Large-scale (512kbit) integration of multilayer-ready access-devices based on Mixed-Ionic-Electronic-Conduction (MIEC) at 100% yield. Symposium on VLSI Technology 41–42, 2012. https://doi.org/10.1109/VLSIT.2012.6242451 (2012).

Weinreb, S., Bardin, J. C. & Mani, H. Design of cryogenic SiGe low-noise amplifiers. IEEE Trans. Microw. Theory Tech. 55, 2306–2312. https://doi.org/10.1109/TMTT.2007.907729 (2007).

Arakawa, T., Nishihara, Y., Maeda, M., Norimoto, S. & Kobayashi, K. Cryogenic amplifier for shot noise measurement at 20 mK. Appl. Phys. Lett. https://doi.org/10.1063/1.4826681 (2013).

Ivanov, B. I., Trgala, M., Grajcar, M., Ilichev, E. & Meyer, H. G. Cryogenic ultra-low-noise SiGe transistor amplifier. Rev. Sci. Instrum. 8, 2. https://doi.org/10.1063/1.3655448 (2011).

Dziuba, R. F., Field, B. F. & Finnegan, T. F. Cryogenic voltage comparator system for 2e/h measurements. IEEE Trans. Instrum. Meas. 23, 264–267. https://doi.org/10.1109/TIM.1974.4314288 (1974).

Tolpygo, S. K. Superconductor digital electronics: scalability and energy efficiency issues. Low Temp. Phys. 42, 361–379. https://doi.org/10.1063/1.4948618 (2016).

Yuh, P. F. A 2-kbit Superconducting memory chip. IEEE Trans. Appl. Supercond. 3, 3013–3021. https://doi.org/10.1109/77.257228 (1993).

Liu, Q. et al. Latency and power measurements on a 64-kb hybrid Josephson-CMOS memory. IEEE Trans. Appl. Supercond. 17, 526–529. https://doi.org/10.1109/TASC.2007.898698 (2007).

Feng, Y. J. et al. Josephson-CMOS hybrid memory with ultra-high-speed interface circuit. IEEE Trans. Appl. Supercond. 13, 467–470. https://doi.org/10.1109/TASC.2003.813902 (2003).

Nagasawa, S., Hinode, K., Satoh, T., Kitagawa, Y. & Hidaka, M. Design of all-dc-powered high-speed single flux quantum random access memory based on a pipeline structure for memory cell arrays. Supercond. Sci. Technol. https://doi.org/10.1088/0953-2048/19/5/S34 (2006).

Tahara, S. et al. 4-Kbit Josephson nondestructive readout ram operated at 580 psec and 6.7 mW. IEEE Trans. Magn. 27, 2626–2633. https://doi.org/10.1109/20.133751 (1991).

Kirichenko, A. F., Mukhanov, O.A. & Brock, D. K. A single flux quantum cryogenic random access memory. In Extended Abstract of 7th International Superconductive Electronics Conference, 1999, 124–127 (1999).

Braiman, Y., Neschke, B., Nair, N., Imam, N. & Glowinski, R. Memory states in small arrays of Josephson junctions. Phys. Rev. E 9, 4. https://doi.org/10.1103/PhysRevE.94.052223 (2016).

Nair, N., Jafari-Salim, A., D’Addario, A., Imam, N. & Braiman, Y. Experimental demonstration of a Josephson cryogenic memory cell based on coupled Josephson junction arrays. Supercond. Sci. Technol. https://doi.org/10.1088/1361-6668/ab416a (2019).

Collaudin, B. & Rando, N. Cryogenics in space: a review of the missions and of the technologies. Cryogenics 40, 797–819. https://doi.org/10.1016/S0011-2275(01)00035-2 (2000).

Author information

Authors and Affiliations

Contributions

S.A. and M.S.H conceived the idea. S.A. performed the simulations and array design. M.S.H. and A.A. analyzed the results. A.A. supervised the project. All authors commented on the results and wrote the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary Information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Alam, S., Hossain, M.S. & Aziz, A. A non-volatile cryogenic random-access memory based on the quantum anomalous Hall effect. Sci Rep 11, 7892 (2021). https://doi.org/10.1038/s41598-021-87056-7

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-021-87056-7

This article is cited by

-

Cryogenic memory technologies

Nature Electronics (2023)

-

High-Tc Superconducting Memory Cell

Journal of Superconductivity and Novel Magnetism (2022)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.