Abstract

A new method has been established and employed to create a random nanophotonic crystal (NPhC) structure without photolithography on the unpolished side of a single-side-polished sapphire substrate. This nano structure has potential use in enhancing the light-extraction efficiency (LEE) of deep ultraviolet light-emitting diodes (DUV-LEDs), and has never been built for DUV-LED applications before. Two mask layers in the nano scale (Au and SiO2) were used to create the NPhC and observed using scanning electron microscopy to have an average height of 400 nm and various sizes from 10 to 200 nm. Finally, a conventional DUV-LED and a DUV-LED device with NPhC were simulated using 2D Lumerical Finite-Difference Time-Domain (FDTD) for comparison. The results show that the LEE of the DUV-LED device with this NPhC integrated was significantly directly enhanced by up to 46% and 90% for TE and TM modes, respectively, compared to the conventional DUV-LED device. Thus, this NPhC is believed to be a new, key technique to enhance the LEE of DUV-LEDs.

Similar content being viewed by others

Introduction

Single crystal sapphire (Al2O3) wafer has become one of the most popular substrates for growing III–V semiconductor materials for optoelectronic and power electronic devices since its initial development in the 1960s1. Sapphire substrate in particular is the most widely used in III-Nitride semiconductor materials for light-emitting diodes (LEDs)2, deep ultraviolet LEDs (DUV-LEDs)3,4,5,6, laser diodes7 and high electron mobility transistors8,9 compared to other substrates such as SiC10,11 and Si12,13,14,15, due to the low lattice mismatch, large diameter, high optical transparency, high thermal stability and corrosion resistance, low cost, etc16,17,18,19. However, sapphire substrates pose many other problems such as cutting and polishing after chip growth and fabrication due to the high hardness and its orientation. For DUV-LEDs that emit from the back side, internal reflection from the unpolished SSP sapphire surface reduces the light-extraction efficiency (LEE) significantly, in addition to losses due to low reflectivity on the polished top side of the device. Recently, many techniques have been advanced to increase the LEE such as using a super-lattice hole-spreading layer with an Al reflector20; flip chip DUV-LEDs21 with a roughened AlN template surface22; highly reflective photonic crystals on a p-AlGaN contact layer on top of the DUV-LED structure23; and highly reflective layers and a patterned sapphire substrate24. However, improving the LEE by making a nanophotonic crystal (NPhC) on the unpolished side of the single-side-polished (SSP) sapphire substrate has not been done before (the polished side sapphire substrate is for semiconductor growth and the unpolished side is for creating NPhC, where the UV light transmits to the air). In this work, we will introduce an etching technique that needs neither a photoresist nor photolithography to etch and create nano features on a c-sapphire substrate by using inductively coupled plasmas (ICP) to create a NPhC with various sizes down to 10 nm. This method is a simple and easy way to obtain NPhC on the unpolished side of the SSP sapphire substrate, as compared to other methods such as nanoimprint lithography25,26 that are limited to create patterns on the front (polished) side and in a limited area. The etching process used in this work combined Boron trichloride (BCl3), Hydrogen bromide (HBr), and Argon (Ar) gases with two nanomask layers. The nanomask formation processes and the resulting etch profile were observed by scanning electron microscopy (SEM). To prove that this NPhC can be used to enhance the LEE of DUV-LEDs, a 2D Lumerical Finite-Difference Time-Domain (FDTD) simulation was used to model a DUV-LED device with this NPhC as well as a conventional device for comparison.

Materials and methods

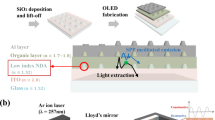

An SSP 2-inch c-sapphire substrate was first cleaned by treatment for 60 s in each of acetone and then isopropyl alcohol, then for 180 s in de-ionized water. After, a 300 nm-thick layer of SiO2 was vapor-deposited on the unpolished side of the substrate (Fig. 1a). The substrate was then loaded into an e-Beam evaporator system to deposit a 10 nm-thick Au layer on the top (Fig. 1b). The deposition rates are approximately 1.1 and 1.0 nm/sec for SiO2 and Au, respectively. Next, the sapphire substrate was placed in a rapid thermal annealing (RTA) furnace at 700 °C for 5 min to form the first multi-Au nanomask (nanoparticle-like)27 as shown in Fig. 1c. After that, the SiO2 was etched to create the second nanomask (Fig. 1d) using reactive-ion etching (RIE). The residual Au nanomask was then removed using gold etchant, as shown in Fig. 1e. Finally, the sapphire substrate etching process was carried out in an ICP etching system (Oxford Plasma Lab System 100) using BCl3, HBr and Ar gases, and the SiO2 was removed using HF to leave the NPhC sapphire substrate (Fig. 1f).

Fabrication process of the NPhC on the unpolished side of SSP sapphire substrate. (a) A SiO2 is deposited on the unpolished side, (b) a thin Au layer is deposited over the SiO2, (c) the first Au nanomask forms under high temperature, (d) the Au nanomask was employed to etch the SiO2 nanomask, (e) Au nanomask removed, (f) sapphire etched through the SiO2 nanomask, and SiO2 removed to leave the final NPhC sapphire substrate.

Results and discussion

The etched sapphire substrate shown in this article was produced using optimal conditions including steps such as annealing and etching through both nanomasks. Figure 2a shows the unpolished side of the SSP sapphire substrate after a thin Au layer was annealed at a high temperature of 700 °C and the Au nanomask that formed under long exposure to that temperature. The Au nanomask particles range in sizes from less than 10 nm to around 200 nm and are mostly convex but irregular, as shown in Fig. 2b. The different sizes obtained may be due to the high roughness (0.8–1.2 µm) of the unpolished substrate surface, leading to variations in forces and in gold film thickness. We found that the larger Au nanoparticles tend to be located on the top of the hills while the smaller ones lie mostly on the hillsides or in valleys. This mask-making technique generates a random pattern, and the nanomask size is difficult to control because of the unpolished surface.

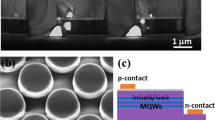

In order to get a perfectly anisotropic etching result for the SiO2 nano mask, RIE plasma etching was carried out with the RF power at 100 W and chamber pressure at 10 Torr. The gas flows were set at 40 and 5 sccm for C4F8 and O2, respectively. The etching rate was estimated at 4 nm/s. Figure 3a shows the perfectly vertical nanopillars achieved on the SiO2 surface (as the second nanomask) with the Au nanomask particles still on the top of each SiO2 pillar (Fig. 3b).

To prevent contamination, gold etchant was used to remove the Au nanomask. The sapphire substrate was then loaded into an ICP system to etch the sapphire substrate. During etching, the chamber pressure was kept at 4 mTorr together with the bias power of 100 W, with a constant flow of the BCl3 and HBr gases at a 4:1 ratio and maintained Ar at 3 sccm. The etching rate is estimated to be about 2 nm/s which is considered the best rate for forming the NPhC structure shown in Fig. 4. The structure comprises spikes of varying dimensions. Diameters were distributed with modes at 50, 100, 200, 300 and 400 nm; height was typically 400 nm; inter-spike spacing averaged 200 nm.

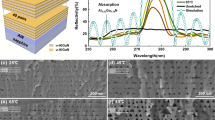

Because this is the first time such a NPhC structure has been created on a SSP sapphire substrate, we simulated its performance in a DUV-LED using the 2D FDTD method, comparing DUV-LEDs with and without the NPhC structure. The FDTD simulation was built to investigate the effect of the NPhC on LEE in particular, for both transverse electric (TE) and transverse magnetic (TM) polarization modes. Figure 5 shows two DUV-LED devices with 100 nm-thick Al reflectors on each p-type layer. The conventional DUV-LED device (Fig. 5a) differs from the device with NPhC only by not having the etched NPhC surface on the unpolished side of sapphire substrate (Fig. 5b). In the simulation model, we used a flat surface and integrated five different NPhC sizes periodically, as mentioned above. We could not make a rough surface to approximate as-received SSP sapphire substrate due to the limitation of the software. However, with a small spacing between each NPhC and high NPhC density, this should have no effect on the simulation result. A single Gaussian-shaped dipole source is applied at the middle of the multiple quantum wells (MQWs) in each structure. The emission and full-width at half-maximum wavelengths of the dipole source are set at 280 and 10 nm, respectively, and polarized in the parallel and perpendicular directions to the MQW plane to excite the TE and TM modes, respectively. The refractive indices of AlN, AlGaN and sapphire are 2.0, 2.6 and 1.8, respectively; these have a big impact on the LEE of DUV-LEDs28. LEE is basically defined as the ratio of emission power collected by monitors surrounding the device and main emission surface directions to the total emission power of the DUV-LED, and is determined by the Poynting vectors along each emission direction and the total Poynting vector29. Therefore, the Poynting vectors are used to determine the LEE of a DUV-LED device, calculated below the surface of the perfectly matched layers. The emission light from the back side of the DUV-LED device and from other sides will be collected for both DUV-LED devices with and without NPhC, for which the monitors were built around the device (black square line) at the edge of the yellow background in Fig. 5 with distance of 300 nm away from the structure.

Figure 6 shows the LEE result of the two DUV-LED devices, with and without NPhC, in both TE and TM modes at the emission wavelength of 280 nm. The simulation reveals a markedly higher LEE for the DUV-LED device with NPhC over the conventional structure. In the TE mode, LEE was increased by 46% (from 30 to 44%), and by 90% (3.8 to 7.3%) for the TM mode. This NPhC structure hence shows great promise for use in DUV-LED applications.

Figure 7 shows the cross-sectional electric field intensity (EFI) distribution for the TE and TM modes of the two DUV-LED devices. In the TE mode, the light can be emitted in the y and z directions since the dipole source is polarized in the x-axis. Figure 7b clearly shows the effect of the NPhC on the light distribution inside and outside the device: we can easily see the oscillation of the light inside the sapphire substrate and a significant enhancement to the emitted light at the interface of the NPhC structure and the air which could not be found in the DUV-LED without NPhC. The DUV-LED device with NPhC shows high uniformity in light distribution and brighter outside the device. Especially at the interface of the NPhC and air, light extraction can be seen clearly, as compared to the conventional DUV-LED does in the Fig. 7a. Thus, the NPhC has directly enhanced the light extraction efficiency in the TE mode much more than that of the conventional DUV-LED. For the TM mode, the dipole light source is polarized to the z-axis, so that the light is emitted mostly to the lateral directions as shown in Fig. 7c and d. In this case, too little light escaped at the bottom of the DUV-LED device to see strong oscillations as in the case of the TE mode. However, the effect of the NPhC inside the structure can also be seen from middle of device down to the NPhC-air interface. Overall, the NPhC significantly enhanced the LEE of DUV-LED device which can be easily trusted from the EFI result.

Conclusion

We have successfully established the most convenient technique, to date, for fabricating NPhC structures on a SSP sapphire substrate using neither photoresist nor photolithography. Unlike conventional photolithography, our technique can be applied to non-flat surfaces such as unpolished SSP sapphire substrates. A NPhC with features as small as 10 nm in diameter can be obtained by using this technique. Small features like this normally require complicated and costly techniques such as e-Beam lithography and nanoimprint lithography where the working area is usually limited. A NPhC structure of this type was integrated into a DUV-LED structure and compared with a conventional DUV-LED in the Lumerical FDTD simulation. The simulation result shows very impressive LEE improvements of 46% (TE) and 90% (TM) over the conventional DUV-LED structure, as well as compared to other techniques30,31. LEE enhancement should depend on the size, height, and also the spacing between NPhCs but more studies needed to understand this dependence. The nanophotonic crystal created using this technique promises to be useful in future high-LEE and high external quantum efficiency DUV-LED devices.

Data availability

Research data are not shared.

References

Maruska, H. P. & Tietjen, J. J. The preparation and properties of vapor-deposited single-crystal-line GaN. Appl. Phys. Lett. 15, 327–329 (1969).

Nakamura, S., Mukai, T. & Senoh, M. Candela-class high-brightness InGaN/AlGaN double-heterostructure blue-light-emitting diodes. Appl. Phys. Lett. 64, 1687–1689 (1994).

Hirayama, H., Kyono, T., Akita, K., Nakamura, T. & Ishibashi, K. High-efficiency 350 nm-band quaternary InAlGaN-based UV-LED on GaN/sapphire template. Phys. Status Solidi (C) 2, 2899–2902 (2005).

Hirayama, H. Recent progresses of AlGaN and InAlGaN-based deep-UV LEDs. In Conference on Lasers and Electro-Optics 1–2 (Baltimore, 2009). https://doi.org/10.1364/CLEO.2009.CMEE1.

Zhou, S., Xu, H., Hu, H., Gui, C. & Liu, S. High quality GaN buffer layer by isoelectronic doping and its application to 365 nm InGaN/AlGaN ultraviolet light-emitting diodes. Appl. Surf. Sci. 471, 231–238 (2019).

Hu, H. et al. Boosted ultraviolet electroluminescence of InGaN/AlGaN quantum structures grown on high-index contrast patterned sapphire with silica array. Nano Energy 69, 104427 (2020).

Shan, M. et al. Deep UV laser at 249 nm based on GaN quantum wells. ACS Photon. 6, 2387–2391 (2019).

Luong, T.-T., Ho, Y.-T., Tran, B. T., Woong, Y. Y. & Chang, E.-Y. Barrier strain and carbon incorporation-engineered performance improvements for AlGaN/GaN high electron mobility transistors. Chem. Vap. Dep. 21, 33–40 (2015).

Luong, T.-T. et al. Performance improvements of AlGaN/GaN HEMTs by strain modification and unintentional carbon incorporation. Electron. Mater. Lett. 11, 217–224 (2015).

Hirayama, H. Quaternary InAlGaN-based high-efficiency ultraviolet light-emitting diodes. J. Appl. Phys. 97, 091101 (2005).

Hirayama, H. et al. Marked enhancement of 320–360 nm ultraviolet emission in quaternary InxAlyGa1−x−yN with In-segregation effect. Appl. Phys. Lett. 80, 207–209 (2002).

Tran, B. T. et al. Direct growth and controlled coalescence of thick AlN template on micro-circle patterned Si substrate. Sci. Rep. 5, 14734 (2015).

Tran, B. T. et al. Performance improvement of AlN crystal quality grown on patterned Si(111) substrate for deep UV-LED applications. Sci. Rep. 6, 35681 (2016).

Tran, B. T. et al. High-quality AlN template grown on a patterned Si(111) substrate. J. Cryst. Growth 468, 225–229 (2017).

Tran, B. T. & Hirayama, H. Growth and fabrication of high external quantum efficiency AlGaN-based deep ultraviolet light-emitting diode grown on pattern Si substrate. Sci. Rep. 7, 12176 (2017).

Duboz, J.-Y. GaN as seen by the industry. Comptes Rendus de l’Académie des Sci. Ser. IV Phys. 1, 71–80 (2000).

Shinkosha Co., Ltd. (accessed 24 June 2020); https://www.shinkosha.com/scube_e/use.html.

Park, H. & Chan, H. M. A novel process for the generation of pristine sapphire surfaces. Thin Solid Films 422, 135–140 (2002).

Ambacher, O. Growth and applications of group III-nitrides. J. Phys. D Appl. Phys. 31, 2653–2710 (1998).

Maeda, N., Jo, M. & Hirayama, H. Improving the light-extraction efficiency of AlGaN DUV-LEDs by using a superlattice hole spreading layer and an Al reflector. Phys. Status Solidi (A) 215, 1700436 (2018).

Lee, T. H. et al. Smart wide-bandgap omnidirectional reflector as an effective hole-injection electrode for deep-UV light-emitting diodes. Adv. Opt. Mater. 8, 1901430 (2020).

SaifAddin, B. K. et al. Fabrication technology for high light-extraction ultraviolet thin-film flip-chip (UV TFFC) LEDs grown on SiC. Semicond. Sci. Technol. 34, 035007 (2019).

Kashima, Y. et al. High external quantum efficiency (10%) AlGaN-based deep-ultraviolet light-emitting diodes achieved by using highly reflective photonic crystal on p-AlGaN contact layer. Appl. Phys. Express 11, 012101 (2017).

Takano, T. et al. Deep-ultraviolet light-emitting diodes with external quantum efficiency higher than 20% at 275 nm achieved by improving light-extraction efficiency. Appl. Phys. Express 10, 031002 (2017).

Guo, X. et al. Fabrication of wafer-scale nanopatterned sapphire substrate by hybrid nanoimprint lithography. J. Vac. Sci. Technol. B 32, 06FG06 (2014).

Chen, H., Zhang, Q. & Chou, S. Y. Patterning of light-extraction nanostructures on sapphire substrates using nanoimprint and ICP etching with different masking materials. Nanotechnology 26, 085302 (2015).

Liang, E.-Z., Huang, C.-J. & Lin, C.-F. Use of SiO2 nanoparticles as etch mask to generate Si nanorods by reactive ion etch. J. Vac. Sci. Technol. B 24, 599–603 (2006).

Ryu, H.-Y. Large enhancement of light extraction efficiency in AlGaN-based nanorod ultraviolet light-emitting diode structures. Nanoscale Res. Lett. 9, 58 (2014).

Kolbe, T. et al. Optical polarization characteristics of ultraviolet (In)(Al)GaN multiple quantum well light emitting diodes. Appl. Phys. Lett. 97, 171105 (2010).

Cheng, L., Bryan, M., Yu Kee, O., Matthew, H. & Jing, Z. Analysis on light extraction property of AlGaN-based flip-chip ultraviolet light-emitting diodes by the use of self-assembled SiO2 microsphere array. Proc. SPIE 10918, 109180Q (2019).

Zhang, Y. et al. Effects of inclined sidewall structure with bottom metal air cavity on the light extraction efficiency for AlGaN-based deep ultraviolet light-emitting diodes. IEEE Photon. J. 9, 1–9 (2017).

Author information

Authors and Affiliations

Contributions

T.B.T. conceptualized the idea, experimental, and simulation plans. T.B.T. and F.A. carried out the simulations. T.B.T. and Q.H.L. carried out the experimental part and data analyses. All authors contributed to the writing, discussion, and approved the final version of the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Tran, T.B., AlQatari, F. & Luc, QH. Nanophotonic crystals on unpolished sapphire substrates for deep-UV light-emitting diodes. Sci Rep 11, 4981 (2021). https://doi.org/10.1038/s41598-021-84426-z

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-021-84426-z

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.