Abstract

We present a new method for thin-film synthesis of the superconducting A15 phase of vanadium silicide with critical temperature higher than 13 K. Interdiffusion between a metallic vanadium film and the underlying silicon device layer in a silicon-on-insulator substrate, at temperatures between 650 and 750 °C, favors formation of the vanadium-rich A15 phase by limiting the supply of available silicon for the reaction. Energy dispersive X-ray spectroscopy, X-ray photoelectron spectroscopy, and X-ray diffraction verify the stoichiometry and structure of the synthesized thin films. We measure superconducting critical currents of more than 106 amperes per square centimeter at low temperature in micron-scale bars fabricated from the material, and an upper critical magnetic field of 20 T, from which we deduce a superconducting coherence length of 4 nm, consistent with previously reported bulk values. The relatively high critical temperature of A15 vanadium silicide is an appealing property for use in silicon-compatible quantum devices and circuits.

Similar content being viewed by others

Introduction

In the early 1950s, the cubic A15 phase (A3B) was discovered to be superconducting, with the notable example of A15 vanadium silicide (V3Si) briefly having the highest known critical temperature (Tc) of any material (17.1 K)1,2. Other A15 superconductors were soon found to have higher Tc [e.g., Nb3Sn (18 K)3, Nb3Ge (23 K)4], and the later discovery of cuprate perovskites5,6 heralded an era of intense study of so-called high-Tc superconductivity—leaving the material V3Si largely unexplored. As a silicide, V3Si is also appealing for its compatibility with silicon technology. In microelectronic devices, transition metal silicides are thoroughly studied and used for low-resistance metallic contacts to field-effect transistors7,8,9,10. V3Si is an s-wave, type-II superconductor with isotropic energy gap, suitable for superconducting devices such as Josephson junctions and superconducting quantum interference devices (SQUIDs)11,12. Furthermore, geometrical lattice matching analysis shows that V3Si forms a high-quality, epitaxial interface with Si with very small lattice mismatch (0.4%) and common cell area (40 Å2)13.

In this work, we report a new method for synthesis of phase pure, superconducting V3Si thin films on silicon dioxide/silicon substrates (SiO2/Si)—a process amenable to fabrication of superconductor-on-insulator devices leveraging silicon technology, and potentially compatible with silicon CMOS fabrication. In the bulk, V3Si is typically synthesized by melting together a stoichiometric mixture (3:1) of elemental vanadium (V) and Si in an inert atmosphere14. Thin films have been previously prepared by vapor phase deposition, including electron-beam co-evaporation of V and Si15, magnetron sputtering from a stoichiometric target16, and molecular beam epitaxy17. In silicon microelectronics, transition metal silicides are formed by silicidation—the process of annealing metal films deposited on silicon8. However, silicidation of V deposited on Si typically forms the Si-rich vanadium silicide phase (VSi2), which is not superconducting, due to the excess supply of available Si during the reaction18,19. Silicidation of V deposited on thermally-grown SiO2 can form the A15 phase V3Si under the right conditions18,19, presumably because diffusion of Si out of SiO2 is slow enough to permit formation of the V-rich phase. However, this process also results in oxygen from the SiO2 reacting with V to form vanadium oxides that are mixed with V3Si in the final structure.

Results and discussion

Thin film synthesis

Here, we synthesize phase-pure, vanadium-rich V3Si thin films by silicidation, by reacting only the thin Si device layer of a silicon-on-insulator (SOI) wafer (Fig. 1). By optimizing the silicidation anneal conditions, we completely convert the Si device layer into V3Si without reacting with the underlying SiO2, leaving a sharp and smooth V3Si/SiO2 interface. In our experiments, we start with SOI wafers having a 20-nm Si (100)-oriented device layer on top of a 140 nm thick thermal SiO2. Stoichiometric conversion of the entire 20 nm thick Si layer to V3Si by silicidation requires the number of V atoms supplied by a 42 nm thick film (see “Methods” section). Most typically, we deposit 90 nm of V—which provides an oversupply of V to ensure complete silicidation of the Si device layer. Prior to annealing, we observe a sharp V/Si interface from cross-sectional scanning electron microscope (SEM) images (Fig. 2a). The samples are annealed in high vacuum (10−7 Torr) for 15 min, at temperatures (T) ranging from 650 °C to 900 °C. The V/Si interface disappears after annealing at sufficiently high temperature (Fig. 2b), due to V-Si interdiffusion. Silicidation at T = 800 °C or lower maintains a sharp, smooth interface at the underlying SiO2 layer, while higher T roughens this interface, indicating a reaction with the SiO2 (Fig. 2c).

Cross-sectional SEM images of: (a) V film deposited onto a SOI substrate, and similar samples after annealing in vacuum at (b) 700 °C and (c) 900 °C. (d) HAADF STEM image of the film annealed at 700 °C. (e, f) EDX mapping of the area shown in (d), denoting location of (e) Si and (f) V. (g) Overlapped maps (e) and (f) show the vanadium silicide region contains both V and Si. (h) Quantitative EDX analysis shows a 3:1 V:Si ratio within the V3Si layer.

Scanning transmission electron microscopy (STEM) reveals more details of the silicidation process. High-angle annular dark field (HAADF) cross-sectional images of a sample annealed at 700 °C (Fig. 2d–f) show two distinct regions within the V-Si layer: an upper, porous region and an underlying, denser layer (Fig. 2d). Energy dispersive X-ray spectroscopy (EDX) shows that the top layer is pure V and the bottom layer contains both V and Si (Fig. 2e–g), consistent with our supplying excess V for the silicidation reaction. The porosity of the V layer is a result of deposition by thermal evaporation, as deposited V atoms quickly lose kinetic energy on the cold substrate and have insufficient mobility to form close-packed films. Quantitative analysis of the EDX maps shows that the bottom layer contains V and Si in a 3:1 ratio (Fig. 2h). X-ray diffraction (XRD) confirms formation of the A15 phase of V3Si for samples annealed at 700 °C, along with impurities of VSi2 and V5Si3 (Fig. 3). Annealing at 600 °C shifts the broad V (110) peak at 42° to 40°, which is matched to V5Si3 (102) but is very broad and likely reflects an intermediate amorphous phase formed during interdiffusion. The presence of VO (200) peak in all samples suggests partial oxidation of the deposited V due to air exposure. For any sample annealed at less than 800 °C, we do not expect reaction between vanadium and SiO2, which is evident from the sharp interface between the V/Si layer and the SiO2 layer (Fig. 2b). According to the EDX maps, the V3Si layer is about 50 nm in thickness, which matches closely the thickness expected from stoichiometric conversion of Si (52 nm, see “Methods” section). The dense V3Si layer suggests that V is the predominant diffusion species, i.e., that silicidation occurs primarily by V diffusing into the Si lattice. Significant Si diffusion would result in the silicide inheriting the porous appearance of the deposited V layer. Our observation is consistent with those of previous studies, which noted an ‘ordered Cu3Au rule’20, suggesting that majority atoms are the most mobile ones in the class of A3B compounds21.

X-ray diffraction spectra (XRD) of V films deposited on SOI, before annealing, and after vacuum annealing at 600 °C and 700 °C. The pattern after annealing at 700 °C shows the formation of the A15 V3Si phase. The 600 °C pattern shows a transition from metallic V to vanadium silicide. Due to exposure to air during sample handling, vanadium oxide (VO) is also formed and evident in the diffraction patterns.

Profiling the vanadium silicide film by sequential argon ion milling and X-ray photoelectron spectroscopy (XPS) verifies its composition (Fig. 4). The film top surface is composed of excess V that has been oxidized upon air exposure, with the V 2p3/2 peak positioned at 515.6 eV, corresponding to a V3+ oxidative state (Fig. 3a, black color). Beginning with spectra taken from 12 nm below the top surface, this peak shifts to 513 eV, which corresponds to elemental V (Fig. 4a, red color). The emergence of the Si 2p peak at 99.0 eV (Fig. 4b, green color) at a depth of 70 nm and beyond indicates the conversion to V3Si. In this region, the Si 2p peak position is very close to elemental Si (99.4 eV), while the V 2p3/2 peak remains at 513 eV, consistent with the metallic nature of V in A15 V3Si22. By analyzing the peak areas and sensitivity factors associated with V 2p3/2 and Si 2p elements in the V3Si region, at a depth of 77 nm (Fig. 4, blue color), the relative elemental ratio between V and Si is obtained at 3:1, consistent with EDX measurements (Fig. 2h). The O 1s peak at 531 eV across all depths indicates the presence of vanadium oxide (VO) in both metallic V and vanadium silicide region due to exposure to air.

Depth-profiled X-ray photoelectron spectra of a V3Si thin film, probed from the film top surface (upper curve) toward the bottom (lower curve). (a) the V 2p and O 1s levels, and (b) the Si 2p level. Depth-profiling is carried out by Ar ion milling. The depth values are calculated by assuming a uniform ion mill rate. Offsets are applied for clarity of viewing.

Transport measurements

Four-probe resistance measurements of V3Si films versus T reveal their metallic nature and the superconducting transition temperature (Tc). We measure the film in-plane resistance using a constant-current bias of 50 µA and vary T at a rate of ~ 1 K min−1 with no magnetic field. The sheet resistance of a 50 nm thick V3Si film silicided at 700 °C decreases from 2.8 to 1.0 Ω/sq upon cooling from room T to 20 K, a resistance ratio of 2.8 (Fig. 5a, inset). These values reflect the parallel normal state resistance of both the V3Si and the overlaying metallic V layer (also about 50 nm thick). At Tc = 13.75 K, the film resistance abruptly decreases to zero with a transition width of 0.3 K, marking the onset of superconductivity. Films silicided at T between 650 and 750 °C all showed superconducting transitions, with Tc decreasing with decreasing silicidation T (Fig. 5a). We do not observe a superconducting phase transition in films silicided at T ≤ 600 °C measured to temperatures as low as 4 K (Fig. 5a, inset). The critical current density is determined from voltage-current measurements of strips fabricated from V3Si thin film annealed at 700 °C. The strips are 30 µm in width and are patterned using photolithography, with etching performed in an argon ion mill (2.5 mA/cm2 beam density), and electrical contacts deposited by e-beam evaporation of 10 nm titanium and 300 nm gold. The voltage-current behavior of strips patterned from a V3Si film change from linear behavior above Tc to non-linear near the superconducting transition (Fig. 5b, inset). Films display sharp, fully developed, critical currents at T < Tc, which increase as T is further reduced. At T = 5 K, the critical current density (jc) is 8.7 × 105 A cm−2, slightly higher than previous reports taken on V3Si single crystals23. This is likely due to the presence of impurity phases acting as flux-pinning centers, which lead to the observed higher critical current densities. Because the Tc of metallic V is 5.4 K for single crystals24, and lower for amorphous films deposited from the vapor phase25, the only contributions from the 50-nm-thick amorphous V film to jc that we would expect within the range of measured temperatures (5–15 K) is a proximity effect induced superconducting layer near the V3Si that serves to increase the effective thickness that carries supercurrent, which is taken into account in the main panel of Fig. 5b.

(a) Electrical resistance versus temperature with no magnetic field, for vanadium silicide films annealed at 650 °C (red), 700 °C (blue), and 750 °C (magenta), normalized against normal state resistance at 20 K (inset). Electrical resistance from room temperature to 4 K, for vanadium silicide films annealed at 600 °C (black) and 700 °C (blue). No superconductivity is observed in the 600 °C sample, consistent with the absence of a V3Si phase. (b) Critical current density (jc) of a 30 μm wide bar fabricated from V3Si thin film annealed at 700 °C (inset). Representative voltage-current curves used to determine the critical current density (T = 5–15 K).

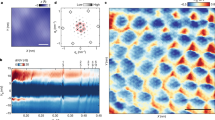

The A15 phase of vanadium silicide is a known type II superconductor that undergoes phase transitions at two different applied magnetic fields. At a lower critical magnetic field (Hc1) the superconducting order parameter is locally suppressed and the material supports magnetic vortices, and at an upper critical field (Hc2) the material reverts to the normal state. We measured the V3Si film resistance versus T in a series of increasing applied magnetic fields (H) in order to determine Hc2(0), the upper critical field at 0 K. The Tc of a V3Si film silicided at 700 °C and having Tc(0) ~ 13 K is continuously suppressed with increasing magnetic field (Fig. 6). For each H, we determine the corresponding Tc(H) using the criteria R/RN = 0.5 (midpoint Tc), where RN is the normal state resistance. In the color map shown in Fig. 5, the dependence of Hc2 on T appears as a narrow white region separating normal and superconducting behaviors. Because the highest magnetic fields available in our experiment (9 T) are insufficient to completely suppress superconductivity in our films, we deduce Hc2(0) for the material indirectly using the Werthamer-Helfand-Hohenberg model, which gives:

where \(\gamma \approx 0.5772\) is Euler’s constant26. A linear fit to the Hc2 – T relation in the range of 0 T < μ0Hc2 ≤ 1 T provides both the tangent term in Eq. (1) and zero field Tc(0), respectively, as the slope and the T-axis intercept (Fig. 5). From this analysis, we obtain μ0Hc2(0) = 20 T, which is consistent with the previously-reported bulk value of Hc2 = 23.5 T for V3Si27. Knowing \({H}_{c2}\left(0\right)\), we can also calculate the superconducting coherence length \(\xi \left(0\right)\) in our V3Si to be 4 nm, using the relation \({{\mu }_{0}H}_{c2}\left(0\right)= {\Phi }_{0}/2\pi {\xi }^{2}\left(0\right)\)28, where \({\Phi }_{0}=h/2e\) is the magnetic flux quantum, also consistent with previous reports29.

Magnetic field dependence of superconducting critical temperature. The white region separating the normal state (red) and superconducting state (blue) are separated by a thin white region denoting the upper critical field, Hc2(T). A linear fit to Hc2(T) near zero applied field (dashed line) is used to calculate Hc2(0) using Eq. (1).

Summary and outlook

In summary, we have described a new method for synthesis of the A15 phase of vanadium silicide by silicidation of metallic vanadium layers deposited on silicon-on-insulator substrates. The limited supply of silicon available for silicidation facilitates formation of the superconducting, vanadium-rich A15 phase. V3Si thin films synthesized on silicon-on-insulator substrates are type-II superconductors with Tc > 13 K. The relatively high Tc is an appealing property for use in silicon-compatible quantum devices and circuits.

Methods

Fabrication of V3Si thin films

The substrates, which are silicon-on-insulator (SOI) wafers with a 20 nm Si device layer and a 140 nm oxide SOI wafer, are dipped in a 10:1 buffered oxide etch (BOE) for 1 min to remove the native silicon oxide. Immediately after the oxide stripping, vanadium layers of different thicknesses are deposited by thermal evaporation in high vacuum (~ 10−7 Torr). After metal deposition, the substrate is annealed in high vacuum for 15 min, at temperatures ranging from 650 °C to 900 °C, to form V3Si by V-Si interdiffusion.

Vanadium thickness for 3:1 V:Si stoichiometry

The molar volume (Vm) of a substance is given by \({V}_{m}=M/\rho\), where M and ρ are, respectively, the substance’s molar mass and volumetric mass density. For crystalline Si, MSi = 28.085 g mol−1 and ρSi = 2.33 g cm−3, which gives Vm, Si = 12.05 cm3 mol−1. For V metal, MV = 50.94 g mol−1 and ρV = 6.0 g cm−3, which gives Vm, V = 8.49 cm3 mol−1. As such, the stoichiometric conversion of one unit volume of Si to V3Si requires 3 × Vm, V/Vm, Si = 2.11. For a 20 nm layer of Si, this corresponds to 42 nm of V. After the conversion, with \({M}_{{\mathrm{V}}_{3}\mathrm{Si}}=180.9\) g mol−1 and \({\rho }_{{\mathrm{V}}_{3}\mathrm{Si}}=5.77\) g cm−3, a similar calculation gives an expected thickness of 52 nm for the V3Si layer.

Scanning transmission electron microscopy (STEM) imaging

The specimen for STEM studies is a 40 nm-thick vertical cross-sectional slice of the silicide film mounted on a copper grid using the in situ focused ion beam milling and lift-out technique (Helios 600 dual beam FIB). High-angle annular dark field (HAADF) and energy dispersive X-ray spectroscopy (EDX) mapping images are collected over the same area simultaneously, using an FEI Talos F200X microscope.

Transport measurements on V3Si thin films

Electrical transport measurements are performed in either a closed-cycle cryocooler or a top loading He-3 cryostat equipped with a 9 T magnet. Resistance is determined by delta mode averaging with a DC bias current provided by a source meter and sample voltage measured with a nanovoltmeter. Measurements of the T-dependence of the upper critical field are made by constant field temperature sweeps and verified by constant temperature magnetic field sweeps. The critical current density is determined from voltage-current measurements of strips fabricated from V3Si thin film annealed at 700 °C. The strips are 30 µm in width and are patterned by standard photolithography, with etching performed in an argon ion mill (2.5 mA/cm2 beam density), and electrical contacts deposited by e-beam evaporation of 10 nm Ti and 300 nm Au, followed by liftoff.

References

Hardy, G. F. & Hulm, J. K. Superconducting silicides and germanides. Phys. Rev. 89, 884–884. https://doi.org/10.1103/PhysRev.89.884 (1953).

Hardy, G. F. & Hulm, J. K. The superconductivity of some transition metal compounds. Phys. Rev. 93, 1004–1016. https://doi.org/10.1103/PhysRev.93.1004 (1954).

Matthias, B. T., Geballe, T. H., Geller, S. & Corenzwit, E. Superconductivity of Nb3Sn. Phys. Rev. 95, 1435–1435. https://doi.org/10.1103/PhysRev.95.1435 (1954).

Matthias, B. T., Geballe, T. H., Willens, R. H., Corenzwit, E. & Hull, G. W. Superconductivity of Nb3Ge. Phys. Rev. 139, A1501–A1503. https://doi.org/10.1103/PhysRev.139.A1501 (1965).

Bednorz, J. G. & Müller, K. A. Possible highTc superconductivity in the Ba−La−Cu−O system. Z. Phys. B 64, 189–193. https://doi.org/10.1007/BF01303701 (1986).

Wu, M. K. et al. Superconductivity at 93 K in a new mixed-phase Y–Ba–Cu–O compound system at ambient pressure. Phys. Rev. Lett. 58, 908–910. https://doi.org/10.1103/PhysRevLett.58.908 (1987).

Murarka, S. P. Refractory silicides for integrated circuits. J. Vac. Sci. Technol. 17, 775–792. https://doi.org/10.1116/1.570560 (1980).

Lavoie, C., d’Heurle, F. M., Detavernier, C. & Cabral, C. Towards implementation of a nickel silicide process for CMOS technologies. Microelectron. Eng. 70, 144–157. https://doi.org/10.1016/s0167-9317(03)00380-0 (2003).

Yamada, K., Tomita, K. & Ohmi, T. Formation of metal silicide-silicon contact with ultralow contact resistance by silicon-capping silicidation technique. Appl. Phys. Lett. 64, 3449–3451. https://doi.org/10.1063/1.111238 (1994).

Gambino, J. P. & Colgan, E. G. Silicides and ohmic contacts. Mater. Chem. Phys. 52, 99–146. https://doi.org/10.1016/S0254-0584(98)80014-X (1998).

Faley, M. I. et al. High-Tc SQUID biomagnetometers. Supercond. Sci. Technol. 30, 083001 (2017).

Cho, E. Y. et al. YBa2Cu3O7−δ superconducting quantum interference devices with metallic to insulating barriers written with a focused helium ion beam. Appl. Phys. Lett. 106, 252601. https://doi.org/10.1063/1.4922640 (2015).

Zur, A., McGill, T. C. & Nicolet, M. A. Transition-metal silicides lattice-matched to silicon. J. Appl. Phys. 57, 600–603. https://doi.org/10.1063/1.334743 (1985).

Greiner, E. S. & Mason, H. Preparation of single crystals of V3Si. J. Appl. Phys. 35, 3058–3059. https://doi.org/10.1063/1.1713170 (1964).

Orlando, T. P., McNiff, E. J., Foner, S. & Beasley, M. R. Critical fields, Pauli paramagnetic limiting, and material parameters of Nb3Sn and V3Si. Phys. Rev. B 19, 4545–4561. https://doi.org/10.1103/PhysRevB.19.4545 (1979).

Osamu, M. & Hisataka, T. V3Si thin-film synthesis by magnetron sputtering. Jpn. J. Appl. Phys. 21, L149 (1982).

Croke, E. T., Hauenstein, R. J. & McGill, T. C. Growth of superconducting V3Si on Si by molecular beam epitaxial techniques. Appl. Phys. Lett. 53, 514–516. https://doi.org/10.1063/1.100621 (1988).

Kräutle, H., Nicolet, M. A. & Mayer, J. W. Kinetics of silicide formation by thin films of V on Si and SiO2 substrates. J. Appl. Phys. 45, 3304–3308. https://doi.org/10.1063/1.1663776 (1974).

Tu, K. N., Ziegler, J. F. & Kircher, C. J. Formation of vanadium silicides by the interactions of V with bare and oxidized Si wafers. Appl. Phys. Lett. 23, 493–495. https://doi.org/10.1063/1.1654972 (1973).

Milanese, C., Buscaglia, V., Maglia, F. & Anselmi-Tamburini, U. Reactive diffusion in the system vanadium–silicon. Acta Mater. 50, 1393–1403. https://doi.org/10.1016/S1359-6454(01)00445-1 (2002).

d’Heurle, F. M. & Gas, P. Kinetics of formation of silicides: a review. J. Mater. Res. 1, 205–221. https://doi.org/10.1557/JMR.1986.0205 (1986).

Mattheiss, L. F. & Weber, W. Electronic structure of cubic V3Si and Nb3Sn. Phys. Rev. B 25, 2248–2269. https://doi.org/10.1103/PhysRevB.25.2248 (1982).

Eckert, D. & Berthel, K. H. The lower critical field Hc1 of V3Si. Cryogenics 15, 479–480. https://doi.org/10.1016/0011-2275(75)90024-7 (1975).

Sekula, S. T. & Kernohan, R. H. Magnetic properties of superconducting vanadium. Phys. Rev. B 5, 904–911. https://doi.org/10.1103/PhysRevB.5.904 (1972).

Kuz’menko, V. M., Lazarev, V. G., Mel’nikov, V. I. & Sodovtsov, A. I. Superconductivity of amorphous vanadium. Sov. Phys. JETP 40, 396–399 (1975).

Werthamer, N. R., Helfand, E. & Hohenberg, P. C. Temperature and purity dependence of the superconducting critical field, Hc2. III. Electron spin and spin-orbit effects. Phys. Rev. 147, 295–302. https://doi.org/10.1103/PhysRev.147.295 (1966).

Otto, G., Saur, E. & Wizgall, H. Critical data of some A15 type superconductors in transverse fields up to 230 kOe. J. Low Temp. Phys. 1, 19–28. https://doi.org/10.1007/bf00628331 (1969).

Tinkham, M. Introduction to Superconductivity 2nd edn. (McGraw Hill, New York, 1996).

Sonier, J. E. et al. Shrinking magnetic vortices in V3Si due to delocalized quasiparticle core states: confirmation of the microscopic theory for interacting vortices. Phys. Rev. Lett. 93, 017002. https://doi.org/10.1103/PhysRevLett.93.017002 (2004).

Acknowledgements

This research used resources of the Center for Functional Nanomaterials, which is a U.S. DOE Office of Science User Facility, at Brookhaven National Laboratory under Contract No. DE-SC0012704 and was also supported by the US Department of Energy, Basic Energy Sciences, Materials Sciences and Engineering Division. R. S. Li is supported by a BNL Laboratory Research and Development Project No. 19-008.

Author information

Authors and Affiliations

Contributions

C.T.B. and M.L. designed the study. W.Z., R.L., and M.L. deposited and prepared the samples. A.B. conducted low temperature transport characterization and data analysis. K.K. prepared cross-sectional TEM specimens and performed TEM analysis. X.T. performed XPS analysis. W.Z., R.L., M.L., and C.T.B. wrote the manuscript. All the authors discussed the results and reviewed the manuscript.

Corresponding authors

Ethics declarations

Competing interests

Two authors (C. T. B. and M. L.) are named inventors on a provisional patent application filed by Brookhaven Science Associates, application number US2019-005-01, currently under evaluation by the US Patent Office. Part of that application details the silicide synthesis method described in this manuscript. All other author do not have any conflict of interest.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Zhang, W., Bollinger, A.T., Li, R. et al. Thin-film synthesis of superconductor-on-insulator A15 vanadium silicide. Sci Rep 11, 2358 (2021). https://doi.org/10.1038/s41598-021-82046-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-021-82046-1

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.