Abstract

Ferroelectrics offer a promising material platform to realize energy-efficient non-volatile memory technology with the FeFET-based implementations being one of the most area-efficient ferroelectric memory architectures. However, the FeFET operation entails a fundamental trade-off between the read and the program operations. To overcome this trade-off, we propose in this work, a novel device concept, Mott-FeFET, that aims to replace the Silicon channel of the FeFET with VO2- a material that exhibits an electrically driven insulator–metal phase transition. The Mott-FeFET design, which demonstrates a (ferroelectric) polarization-dependent threshold voltage, enables the read current distinguishability (i.e., the ratio of current sensed when the Mott-FeFET is in state 1 and 0, respectively) to be independent of the program voltage. This enables the device to be programmed at low voltages without affecting the ability to sense/read the state of the device. Our work provides a pathway to realize low-voltage and energy-efficient non-volatile memory solutions.

Similar content being viewed by others

The electric-field (E-field) induced non-volatile polarization switching in ferroelectrics makes them a promising candidate for developing non-volatile memory (NVM) technology. Conventionally, ferroelectric-based random-access memory (RAM) was realized using traditional ferroelectrics such as PZT, and showed energy-efficient operation, fast read as well as high endurance1,2. However, this ferroelectric memory technology was challenging to scale since ferroelectrics such as PZT typically exhibit a significant degradation in the ferroelectric response when the film thickness is scaled below 50 nm3. Consequently, the recent discovery of ferroelectricity in highly scaled HfO2- a material that is compatible with CMOS process technology- has generated immense interest in revisiting ferroelectric memory technology4,5. Particularly, the ability to integrate the ferroelectric directly into the gate of a field effect transistor (FET) has motivated active investigation of FeFET (Ferroelectric FET)-based non-volatile memory6. However, the FeFET design entails a fundamental trade-off between the programming and the read/sensing characteristics7,8,9. The objective of this work is to propose a pathway to overcome this trade-off and help reduce the programming voltage (at a fixed read current ratio) by replacing the Silicon channel by an alternate channel material, VO2 (vanadium dioxide), that exhibits the phenomenon of electrically driven insulator-to-metal transition (IMT).

A conventional FeFET involves a fundamental trade-off between the program voltage (write operation), and the MW (memory window) along with the corresponding read current distinguishability, expressed as Ibit_1/Ibit_0 (Ibit_1 and Ibit_0 are the sense currents measured corresponding to bit 1 and 0, respectively). Increasing the memory window and the corresponding Ibit_1/Ibit_0 requires the application of a significantly larger programming voltage. This is because in the FeFET configuration, the ferroelectric typically operates on a minor loop (not saturation loop) of the polarization versus voltage characteristics and improving the MW entails increasing the hysteresis by the application of a larger programming voltage. Moreover, these contending factors can become even more critical while operating the cell in a memory array where the parasitic currents from half-selected cells can further compromise the read distinguishability. Additionally, the larger program voltage also results in extremely large electric-fields (in excess of 10 MV/cm) across the interlayer (IL) between the ferroelectric and the Silicon channel which can adversely impact the reliability and the endurance of the device8. These trade-offs have been quantitatively analyzed in prior works7,9 including those by the authors8,10.

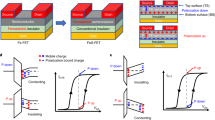

To illustrate the concept of the Mott-FeFET, we first develop models for the individual components of the device, namely, the ferroelectric HfO2 and the VO2 channel. Figure 1a shows the simulated polarization versus voltage characteristics of the ferroelectric HfO2 (f-HfO2) considered in this work. These characteristics have been simulated using the phenomenological Preisach’s model11 and have been calibrated to experimental data on 10 nm thick f-HfO2 films (in a metal/ferroelectric/metal capacitor configuration) reported by S. Mueller et al.12.

Modeling electrical response of the ferroelectric and VO2. (a) Polarization versus voltage characteristics of the ferroelectric HfO2 simulated using the Preisach’s model, and calibrated to the experimental data reported by Mueller et al.12 (b) Two-dimensional resistive network used to model the filamentary switching behavior across the IMT in VO2. (c) Evolution of the insulating and metallic phases across the electrically driven IMT in VO2 clearly showing the filamentary switching; the phases are indicated on the black IV curve in next panel. (d) Modulation of the threshold voltage for the IMT as a function of the applied electric field. Schematic of the device considered is also shown (inset) (e) Phase diagram of VO2 (f) Parameters used for simulation of VO2.

Next, we consider the electronically driven IMT in VO2. We note that while other oxides such as NbO213, SmNiO314 among others also demonstrate similar electronically driven IMT behavior, VO2 was our choice of IMT material in this work since it exhibits a large ROFF/RON ratio (> 104)15, and more importantly, the modulation of the threshold voltage of the electrical IMT with gate electric field, critical to the Mott-FeFET operation, has been experimentally demonstrated in this material system16,17.

Two-terminal VO2 devices exhibit an electrically induced IMT that is characterized by an abrupt change in resistance at a particular applied voltage (VT: threshold voltage) as the device transitions from the insulating to the metallic state18. The transition is volatile, and the device returns back to the insulating state (metal-to-insulator transition; MIT) when the applied voltage subsequently drops below a threshold (VH: hold voltage), accompanied by hysteresis (VT-VH). To simulate the electronically induced IMT in VO2, we model the two-terminal VO2 device as a network of resistors that represent domains (Fig. 1b), as proposed in prior work19. Each resistance in this 2D network can undergo an IMT and MIT (metal to insulator transition) with a certain probability that is dependent on the voltage. Using the approach proposed by Madan et al.15 and Poklonski et al.20, we model the switching probability for a domain using the following equations:

And,

where PMIT and PIMT are the probabilities of a domain undergoing MIT and IMT, respectively. Eb and Ec are energy barriers as defined in Fig. 1e, and γ is a geometric factor15.

It can be observed that applying a voltage increases the probability of a domain undergoing IMT. Additionally, we also consider a gaussian distribution for the resistance values representing a domain to account for the heterogeneity in the film. The parameters for the IMT in VO2 are shown in the table in Fig. 1f. A detailed discussion of the electronic IMT in VO2 has been included in supplement S3.

The voltage-induced IMT in the device can be explained as follows. Initially, all the domains are in the insulating state (at zero bias). As the voltage across the device is increased, a few domains (probabilistically) undergo IMT, serving as the nucleation centers for the metallic phase. As the domain transitions to the metallic state, the voltage drop across the domain reduces, leading to a corresponding increase in the voltage drop across other domains, which in turn, increases their probability of switching. This process generates an avalanching effect that eventually creates a metallic filamentary bridge between the electrodes, resulting in an abrupt change in resistance of the device; the width of the filament depends on the current passing through the device- an effect that is captured by our model as well (Fig. 1c). Furthermore, the presence of filamentary conduction has been experimentally shown in prior work21. Similar (albeit weaker) avalanching behavior is observed during MIT leading to an abrupt increase in resistance as the device turns OFF. We also note that the switching in VO2 is stochastic (see supplement S1a) which consequently has important implications for the design of the memory array.

Additionally, in the three-terminal device configuration with a gate dielectric, Kim et al.16, and Tabib-Azar et al.17 experimentally demonstrated that the threshold voltage of the VO2 channel can be modulated by applying an electric field across the gate—a property crucial to the Mott-FeFET operation. We note that the gate-field alone does not induce the IMT but aids the transition. We model this behavior phenomenologically by modifying Eq. (1) to include the effect of surface potential induced by the gate: \(P_{IMT} = e^{{\frac{{ - \left( {E_{b} - \frac{q\Delta V}{\gamma } - \alpha q\psi_{s} } \right)}}{kT}}}\). Here, Ψs is the VO2 surface potential due to the gate and α is the coupling constant introduced between the gate-induced surface potential and the IMT transition in the VO2 device (set to 0.5). Since the gate-field alone does not induce the transition but modifies the threshold voltage (VT), we model this effect as the surface potential modulating the probability of the domain switching, which subsequently, manifests as the change in the (drain-to-source) VT required to induce the IMT, as shown in Fig. 1d. Additionally, we do not consider this effect in the MIT characteristics since the operation of our proposed device as a memory cell does not rely on the MIT, as well as due to the absence of experimental data. We also emphasize that while the proposed model can explain the experimental behavior shown by Kim et al.16 and Tabib-Azar et al.17, it is important to qualify that model is phenomenological in nature; the exact physics of the electrically induced Mott-Peierls IMT in VO2 still remains an active, ongoing investigation.

Another important aspect of the gate electric-field induced modulation is that while it has a significant influence on the threshold voltage for the IMT (by influencing the nucleation dynamics of the metallic phase), its impact on the metallic and insulating states is minimal. This because the high conductance state of the VO2 is essentially metallic in nature which limits the penetration of the gate field. Furthermore, the impact of the electric field on the resistivity of insulating state is also expected to be minimal22. This can be attributed to the formation of small polarons that result from the gate-induced charge coupling to the lattice, as shown in our prior work23, as well as in other works24. These polarons screen the electric field, and subsequently, limit its penetration to a few (1–2) monolayers, resulting in minimal effect on the conductivity. This ensures that for a current sensing-based reading scheme, the read distinguishability i.e., Ibit_1/Ibit_0 would essentially be constant, irrespective of the programming voltage / field applied at the gate. This behavior is fundamentally different from that of a conventional Si transistor where the gate field strongly controls the channel resistance, and consequently, the channel current.

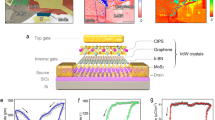

The Mott-FeFET design (Fig. 2a) aims to integrate the non-volatile polarization switching in the ferroelectric gate with the abrupt resistance switching across the electrically driven IMT in VO2 channel. The expected operation of the Mott-FeFET can be described as follows: the polarization state (up or down) of the ferroelectric gate is used to represent the information bit to be stored and can be programmed (write operation) by applying the program voltage across the gate of the device (details of the polarity are discussed in the array operation). The resulting surface potential associated with the (different) polarization states of the ferroelectric modulates the threshold voltage (VT,1, VT,0) of the IMT in the VO2 channel i.e., one polarization state results in a larger threshold voltage than the other state, creating a memory window (ΔVT = VT,0 − VT,1) as shown in Fig. 2b. Subsequently, the state of the memory can be sensed by applying an appropriate read voltage VREAD such that VT,1 < VREAD < VT,0. This ensures that if the memory cell is in state 1, a large drain current, corresponding to the metallic state of VO2, will be sensed whereas state 0 will produce a significantly smaller drain current owing to the insulating nature of the channel. Therefore, the VO2 channel can be considered as a ‘selector’ whose threshold voltage depends on the state of the memory (i.e., ferroelectric gate).

Mott-FeFET operation. (a) Schematic of the proposed Mott-FeFET. (b) Ids versus Vds characteristics of the VO2 channel as a function of the ferroelectric polarization. (c) Observed ratio between read currents corresponding to state 1 and 0, as a function of the applied program voltage. It can be observed that ION/IOFF ratio, unlike in a conventional FeFET remains constant.

We explore the operation of the proposed Mott-FeFET by integrating the models developed above for the individual components, namely, polarization switching in the ferroelectric and the electronically induced abrupt resistance switching in VO2. Moreover, the ferroelectric polarization interacts with the VO2 channel through the surface potential which is calculated by modeling the capacitance response of the gate stack. The surface potential, which depends on the state of polarization of the ferroelectric, subsequently, modulates the probability of the switching (from insulating to metallic state) in the VO2 domains, resulting in a ferroelectric polarization state dependent IMT threshold voltage. A finite interlayer at the interface between the ferroelectric and the VO2 is also considered. Using this framework, we simulate the characteristics of the Mott-FeFET, as shown in Fig. 2b. It can be observed that the threshold voltage for the IMT in the VO2 channel varies by ~ 0.5 V, opening a memory window that can facilitate its use as a non-volatile storage element.

We note that while the memory window (i.e., ΔVT = VT,0 − VT,1) is sensitive to the polarization, which in turn depends on the voltage used to program the ferroelectric, the Ibit_1/Ibit_0 ratio (within the memory window) is almost insensitive to the program voltage of the ferroelectric, as observed in Fig. 2c. This is because the current distinguishability is primarily decided by the ROFF and RON of the VO2 which are relatively insensitive to the gate-field, as discussed above. The insensitivity of the Ibit_1/Ibit_0 ratio to the program voltage can facilitate scaling of the program voltage without adversely impacting the read/sense characteristics and margins.

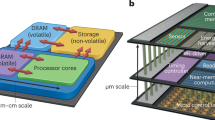

Next, we evaluate the operation of the Mott-FeFET as a memory element in a non-volatile memory array. We consider the NOR memory architecture as shown in Fig. 3a, where the basic building block of the array consists of the Mott-FeFET as the memory element whose gate is connected to a simple MOSFET, which functions as the access device. This architecture, which consists of a separate word-line to read (WLR) from, and write (WLW) to, a cell is similar to that proposed for FeFET-based memory arrays25. A phenomenological Verilog-A model is used to simulate the Mott-FeFET whereas the DGXFET NMOS model, available in the IBM 65 nm CMOS 10LPe process, is used for the transistor.

Mott-FeFET array operation. (a) Schematic of the proposed Mott-FeFET-based memory array. (b) Biasing scheme for WLWs, WLRs, BLs and SLs to access a memory cell (M22 here). The results presented here are for a 3 × 3 array. Time dynamics of the bias voltages applied across WLW2 and BL2 during (c) write ‘0’ and (d) write ‘1’ operations in the M22 cell. During write operation, the other WLWs and BLs are biased at VDD and 0 V, respectively, and all the WLRs and SLs are biased at 0 V. Time evolution of the ferroelectric polarization for (e) write ‘1’ → ‘0’ and (f) write ‘0’ → ‘1’ operations in the M22 cell. (g) Temporal dynamics of the bias voltages of WLW2 and WLR2 for read operation of the cells in the second row. The bias voltages for other WLWs, WLRs, BLs and SLs are kept constant at specific levels (shown in (b)). (h) SL currents during read operation. This array architecture facilitates reading the entire row in one cycle. Here, we only read the second row. M21 and M23 cells were initialized with logic ‘0’ and M22 with logic ‘1’ before read operation. The effect of the stored memory state is observed in the corresponding SL currents. SL1 and SL3 currents are 450 nA due to logic ‘0’ in M21 and M23 and SL2 current is 225 µA due to logic ‘1’ stored in M22.

The biasing scheme for reading from-, and writing to-, a particular cell of the memory array is designed to facilitate successful reading and writing operations, without disturbing other cells in the array. Here, we consider the illustrative example of accessing the M22 cell in a 3 × 3 array. The corresponding biasing conditions are shown in Fig. 3b. Figure 3c,d show the bias voltages applied to WLW2 and BL2 (connected with M22) for the write ‘0’ and write ‘1’ operations, respectively. The bias conditions for the other WLWs, BLs, WLRs, and SLs are in accordance with those listed in the table in Fig. 3b. The WLW2 is asserted to turn ON the access transistors of the second row, and a suitable programming voltage (\(\pm\) VWRITE) is applied to the BL2 with the objective to facilitate sufficient bias at the gate of the ferroelectric to modulate the polarization, as needed. Figure 3e,f show the evolution of the ferroelectric polarization during write ‘1’ → ‘0’ and write ‘0’ → ‘1’ operations, respectively. The appropriate choice of bias conditions eliminates the possibility of the accidental write into the other cells of the array (details discussed in supplement S4).

The proposed array architecture also facilitates reading all the cells in a row in one cycle. To illustrate this, we initially store ‘0’ in M21 and M23 and ‘1’ in M22 cells belonging to the second row of the 3 × 3 array. To read from a cell, we utilize the IDS − VDS characteristics of Mott-FeFET (at zero gate bias) shown in Fig. 2b. Figure 3g shows the bias conditions for the WLW2 and WLR2 and the corresponding SL currents are shown in Fig. 3h. It can be observed that the SL connected to the cell with logic ‘0’ generates ~ 450 nA whereas the logic 1 produces a current of ~ 225 µA on SL. This difference in the SL current is used for the sensing of the stored memory states using current sense amplifiers26,27 (see supplement S4 for more details on the sensing mechanism).

Discussion

The goal of this work is to propose and elucidate a new device concept, Mott-FeFET, that aims to overcome the read–write trade-offs in conventional Silicon FeFET designs by leveraging the unique properties of IMT. It showcases an example of how novel functional materials and their properties (here, the IMT in VO2) can be used to overcome the design challenges of Silicon devices. While the focus of the work is primarily to describe the operational characteristics and functional properties of the Mott-FeFET, it is important to note that the physical realization of such a device would inevitably need to address important challenges such as the integration of the f-HfO2 on VO2 while retaining their functional properties, the role of the interfacial layer and interface states among others; overcoming these concerns will be critical to the eventual practicality of such a device. Additionally, we also note that the underlying physics of the electrically induced IMT in VO2 as well as how an external electric field affects the IMT still remains to be fully understood. However, the present work helps nucleate the new device concept, and motivates the investigation of the above questions, which can subsequently, enable energy-efficient and high performance non-volatile random-access memory.

Methods

The Mott-FeFET was simulated using the Xyce Parallel Electronic Simulator28-a SPICE-compatible circuit simulator provided by Sandia National Laboratory, interfaced with MATLAB; the 2D resistive network was implemented in Xyce whereas the domain switching was analyzed in MATLAB. The experimentally calibrated ferroelectric characteristics were simulated using the Preisach model implemented in MATLAB. For array-level simulations, a phenomenological compact model was utilized for the individual memory elements. This compact model was implemented in Verilog-A and was calibrated with the polarization dynamics and electrical characteristics obtained from the physics-based predictive model for Mott-FeFET. The DGXFET NMOS model from the IBM 65 nm CMOS 10LPe process was utilized to simulate the access transistors in the memory array.

References

Kato, Y. et al. Overview and future challenge of ferroelectric random access memory technologies. Jpn. J. Appl. Phys. 46, 2157–2163 (2007).

Arimoto, Y. et al. Current status of ferroelectric random-access memory. MRS Bull. 29, 823–828 (2004).

Zambrano, R. Challenges for integration of embedded FeRAMs in the sub-180 nm regime. Integr. Ferroelectr. 53, 247–255 (2003).

Park, M. H. et al. Review and perspective on ferroelectric HfO2-based thin films for memory applications. MRS Commun. 8, 795–808 (2018).

Müller, J. et al. Ferroelectric hafnium oxide based materials and devices: Assessment of current status and future prospects. ECS J. Solid State Sci. Technol. 4, N30–N35 (2015).

Keshavarzi, A. et al. FerroElectronics for edge intelligence. IEEE Micro 40, 33–48 (2020).

Deng, S. et al. Guidelines for ferroelectric FET reliability optimization: Charge matching. IEEE Electron Device Lett. 41, 1348–1351 (2020).

Jerry, M. et al. A threshold switch augmented hybrid-FeFET (H-FeFET) with enhanced read distinguishability and reduced programming voltage for non-volatile memory applications. In 2018 IEEE Symposium on VLSI Technology 129–130 (IEEE, 2018).

Deng, S. et al. Overview of ferroelectric memory devices and reliability aware design optimization. In Proceedings of the 2021 on Great Lakes Symposium on VLSI 473–478 (ACM, 2021).

Mallick, A. et al. Evaluation of bulk and SOI FeFET architecture for non-volatile memory applications. IEEE J. Electron Devices Soc. 7, 425–429 (2019).

Jiang, B. et al. Computationally efficient ferroelectric capacitor model for circuit simulation. In Symposium on VLSI Technology 141–142 (IEEE, 1997).

Mueller, S. et al. Performance investigation and optimization of Si:HfO2 FeFETs on a 28 nm bulk technology. In 2013 Joint IEEE International Symposium on Applications of Ferroelectric and Workshop on Piezoresponse Force Microscopy (ISAF/PFM) 248–251 (IEEE, 2013).

Nandi, S. K. et al. Threshold current reduction for the metal–insulator transition in NbO2−x-selector devices: The effect of ReRAM integration. J. Phys. D. Appl. Phys. 48, 195105 (2015).

Shukla, N. et al. Electrically induced insulator to metal transition in epitaxial SmNiO3 thin films. Appl. Phys. Lett. 105, 012108 (2014).

Madan, H. et al. Quantitative mapping of phase coexistence in mott-peierls insulator during electronic and thermally driven phase transition. ACS Nano 9, 2009–2017 (2015).

Kim, H.-T. et al. Mechanism and observation of Mott transition in VO2-based two- and three-terminal devices. New J. Phys. 6, 52–52 (2004).

Tabib-Azar, M. et al. Nano-particle VO2 insulator-metal transition field-effect switch with 42 mV/decade sub-threshold slope. Electronics 8, 151 (2019).

Shukla, N. et al. Synchronized charge oscillations in correlated electron systems. Sci. Rep. 4, 4964 (2015).

Driscoll, T. et al. Current oscillations in vanadium dioxide: Evidence for electrically triggered percolation avalanches. Phys. Rev. B 86, 094203 (2012).

Poklonski, N. A. et al. Simulation of dc conductance of two-dimensional heterogeneous system: Application to carbon wires made by ion irradiation on polycrystalline diamond. Phys. Status Solidi 243, 1212–1218 (2006).

Freeman, E. et al. Nanoscale structural evolution of electrically driven insulator to metal transition in vanadium dioxide. Appl. Phys. Lett. 103, 263109 (2013).

Sengupta, S. et al. Field-effect modulation of conductance in VO2 nanobeam transistors with HfO2 as the gate dielectric. Appl. Phys. Lett. 99, 062114 (2011).

Martens, K. et al. Field effect and strongly localized carriers in the metal-insulator transition material VO2. Phys. Rev. Lett. 115, 196401 (2015).

Yajima, T. et al. Modulation of VO2 metal–insulator transition by ferroelectric HfO2 gate insulator. Adv. Electron. Mater. 6, 1901356 (2020).

George, S. et al. Nonvolatile memory design based on ferroelectric FETs. In Proceedings of the 53rd Annual Design Automation Conference 1–6 (ACM, 2016).

Chang, M.-F. et al. An offset-tolerant fast-random-read current-sampling-based sense amplifier for small-cell-current nonvolatile memory. IEEE J. Solid-State Circuits 48, 864–877 (2013).

Aziz, A. et al. Low power current sense amplifier based on phase transition material. In 2017 75th Annual Device Research Conference (DRC) 1–2 (IEEE, 2017).

Keiter, E. R. et al. Xyce Parallel Electronic Simulator Users’ Guide, Version 6.8 (Sandia National Laboratories, 2017).

Acknowledgements

This work was supported by NSF Grant 1914730.

Author information

Authors and Affiliations

Contributions

J.V., R.S.S.K. performed the device simulations. S.A. and N.A. performed the array simulations. J.V. and N.S. conceived the idea. A.A. and N.S. supervised the study. All authors took part in writing the manuscript, discussed the results and commented on the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary Information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Vaidya, J., Kanthi, R.S.S., Alam, S. et al. A three-terminal non-volatile ferroelectric switch with an insulator–metal transition channel. Sci Rep 12, 2199 (2022). https://doi.org/10.1038/s41598-021-03560-w

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-021-03560-w

This article is cited by

-

High-sensitive MIS structures with silicon nanocrystals grown via solid-state dewetting of silicon-on-insulator for solar cell and photodetector applications

Journal of Materials Science: Materials in Electronics (2022)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.