Abstract

In this paper, we combine inverse design concept and direct binary search algorithm to demonstrate three ultra-compact high efficiency and low crosstalk on-chip integrated optical interconnection basic devices in the entire wavelength range of 1,400–1600 nm based on silicon-on-insulator platform. A 90-degree waveguide bend with a footprint of only 2.4 × 2.4 μm2 is designed, whose transmission efficiency up to 0.18 dB. A waveguide crossing with a footprint of only 2.4 × 2.4 μm2 is designed, which can provide insertion loss of less than 0.5 dB and crosstalk (CL) of lower than − 19 dB. A same direction waveguide crossing with footprint of only 2.4 × 3.6 μm2 is designed, which can provide the insertion loss of less than 0.56 dB and the crosstalk of lower than − 21 dB. Then, we use them to form several ultra-compact optical interconnect basic structures and performed the simulation calculation. They overall achieve high performance. This will significantly improve the integration density.

Similar content being viewed by others

Introduction

The concept of integrated photonics was introduced in 1969 by Miller1, which made a great contribution to the on-chip integrated optical interconnection. On-chip integrated optical interconnection is an emerging technique for large capacity data communications. The waveguide bends and crossings are one of the most critical components of optical interconnection. There are many waveguide bends and crossings designed by conventional approaches. A 5 μm radius 90-degree circular bend with 400 × 220 nm silicon strip waveguide was designed2. Although the loss of the circular bend is 0.023 dB in FDTD simulation, the design method need a lot of complicated artificial adjustment experiments. A 90-degree partial Euler bends with an effective radius of 50 µm was fabricated on a silicon nitride photonic3. The bend loss was within 0.2 dB, but it was only limited to the wavelength of 850 nm and had a large footprint. A 275 µm radius circular bend was designed using a silicon waveguide4, which achieved very low loss. Unfortunately the length of the radius and waveguide is too long. Bogaerts et al.5 proposed a 90-degree adiabatic bend for silicon waveguides. The total bend loss was 0.001 dB. However, the curve radius and circular wire section were up to 5 µm and 25 µm, respectively. Other waveguide bends with 2µm6, 4µm7, 10µm8 radius were designed using a straight waveguide. Although the loss was below 0.3 dB loss, they had a large footprint and need a very long waveguide. Various studies have also been conducted on waveguide crossings. A low-loss waveguide crossing using the self-imaging properties of multimode interference (MMI) structures was designed9, which achieved a loss of only 0.009 dB. But, the length is also fairly long (> 140 µm in the case). A multimode-interference (MMI)-based crossing in high-index-contrast silicon wire waveguides was reported, which had an MMI crossing of ~ 0.4 dB insertion loss10. However, its large 13 × 13µm2 footprint may be an issue for dense integration. Recently there have been reports attempting to further reduce the footprint with successful demonstrations with a 6 × 6µm2 11,12,13,14. Note that − 1.7 dB insertion loss was achieved with only − 40 dB cross talk11. Insertion loss was lower than 0.2 dB and crosstalk loss was below 40 dB in a broad bandwidth of 20 nm12. Average insertion loss was 0.18 ± 0.03 dB and crosstalk was − 41 ± 2 dB13. The waveguide crossing only operated at 1550 nm and 1310 nm, the results showed transmission insertion loss of − 0.028 ± 0.009 dB only for the 1550 nm device and − 0.017 ± 0.005 dB only for the 1310 nm device. Both crossings show crosstalk lower than − 37 dB14. Another waveguide crossing showed an insertion loss of 1.82 dB as well as a crosstalk of < − 18 dB from 1,510 to 1600 nm15. However, the footprint of the device was as compact as 21 × 21 μm2. A dual-mode waveguide crossing is proposed. The characterization results for the fabricated device show that low insertion loss below 1.5 dB and low crosstalk below − 18 dB can be achieved16. But, it must need two waveguide crossing to achieve the function. Han et al.17 used particle swarm optimization algorithm to design a SOI waveguide crossing with a footprint of only ~ 1 × 1 μm2. Although it has an insertion loss < 0.175 dB and crosstalk around − 30 dB for the C-band, the designed method needs complex calculations and long-time simulation, and the number of iterations is set 500. A waveguide cross was designed that insertion loss and crosstalk were less than 0.6 dB and − 24 dB from 1530 to 1590 nm, respectively18. However, the fabricated device still occupied a footprint of 4.8 × 4.8 μm2. Although traditional methods have been used to design devices with good performance, the footprint is always large that has a negative impact on dense integration, and the design of such devices rely heavily on the intuition and experience of the designer and cannot manually achieve a full-parameter space design. Therefore, we should use other methods to design waveguide bends and crossings. This method must be simple and feasible. It should greatly reduce the footprint of the device and achieve superior high performance.

In recent years, the inverse design method and DBS algorithm of ultra-compact silicon photonic devices have drawn more and more attentions19,20,21,22,23,24,25. The best-known institutions for inverse design research are the University of Utah and Stanford. The University of Utah achieved the inverse design of integrated nano-photonic polarization beam splitters by combining DBS algorithm and the current commercial software19. The Stanford used alternating directions method of multipliers (ADMM) to design a wavelength demultiplexer of 1300 nm/1500 nm20. For other optical device designs like flat optics and holograms, the inverse design also has a wide range of application26,27,28,29. Learning from their train of thought, Harbin Institute of Technology30,31,32, Huazhong University of Science and Technology33,34,35, National University of Defense Technology36,37,38,39,40 designed a variety of on-chip optical devices and achieved a good performance. One of the ways to realize inverse design is combining DBS algorithm and commercially available simulation software capable of implementing FDTD solutions, such as Lumerical FDTD Solutions41. Inspired by them, we used inverse design and DBS algorithm to design waveguide bends and crossings.

In this paper, based on SOI platform, we successfully demonstrated a 90-degree waveguide bend, a waveguide crossing and a same direction waveguide crossing in the entire wavelength range of 1,400–1600 nm by using DBS algorithm. Their footprints are only 2.4 × 2.4 μm2, 2.4 × 2.4 μm2, 2.4 × 3.6μm2 respectively. The transmission efficiency of the 90-degree waveguide is > 0.5 dB in the entire wavelength range of 1,440–1640 nm and up to 0.18 dB at some wavelengths. The waveguide crossing can provide insertion loss of less than 0.5 dB. The same direction waveguide crossing can provide the insertion loss of less than 0.56 dB. The measured crosstalk of the two crossings is lower than ‒19 dB and ‒21 dB respectively. Meanwhile, four kinds of optical interconnection modes are designed with the proposed bending and crossing, which realize the superior performance. Compared with traditional optical interconnection, the integration density and benefit various on-chip optical systems are greatly improved.

Results

Optical interconnection component

A 90-degree waveguide bend

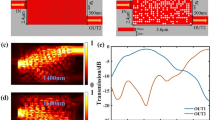

Based on the “design method”, we first design a 90-degree waveguide bend on a silicon-on-insulator (SOI) substrate with 220 nm silicon on top of 3 μm buried oxide. As shown in Fig. 1a–c, the computation domain is 2.4 × 2.4 μm2, where the optimization region is divided into 20 × 20 pixels and each pixel is a square of 120 nm × 120 nm with a central circular hole. The hole has a diameter of 90 nm and a depth of 220 nm, which can be fabricated with an electron-beam lithography (EBL) system (Vistec EBPG 5000 Plus).

Design and simulation results of the 90-degree waveguide bend. (a) Initial silicon slab before design optimization. (b) Final optimized structure. (c) Isometric view. (d) Simulated optical field distributions. (e) Simulated normalized transmission spectra. Here, we have plotted the electromagnetic energy density U = ϵ|E|2 + μ|H|2. An animated version of d is available in Supplementary Video S1.

Each pixel can occupy two states: silicon or air. The white and red regions of the pixel denote the etched area where no silicon remains on top of the oxide and the unetched area where the 220 nm silicon remains, respectively. At the beginning, all the pixel states are chosen to be silicon, and the excitation the TE0 mode in the wavelength range of 1,400–1600 nm. Then the state of each pixel is altered one by one, and the figure-of-merit (FOM) is inspected. Here the FOM is defined as:

where \({\text{T}}_{{{\text{out}}\_{\text{port}}}}\) is the transmission efficiency of the final structure at the wavelength of 1550 nm as the input light source is TE0 mode, which is calculated by 3D FDTD with 40 nm × 40 nm × 40 nm grid size and 8 layers PML. If the FOM is improved, the pixel state is retained. If not, the pixel state is reversed and the algorithm proceeds to the next pixel. One iteration ends after all the pixel states are inspected. Then the iterations continue until the FOM does not improve further.

We perform the device design and optimization using an eight-core desktop. For the 90-degree waveguide bend, it takes ~ 24 h on average to get the final results after 4 iterations. Given that fabrication variations can have a significant impact on real-world device performance, we characterize the same bends with a ± 10% variation in pillar diameter by simulation. The simulated optical field profile of the device when the continuous wave is launched from input port is shown in Fig. 1d. Figure 1e shows the calculated normalized transmission efficiency. The simulated normalized transmission efficiency of the bend is < 0.5 dB in the entire range of 1,400–1600 nm and up to 0.18 dB at some wavelength. As we can show, a ± 10% variation in pillar diameter doesn't affect largely on the 90-degree waveguide bend. It is seen from the Table 1 that the waveguide bend we designed has very low loss losses and a relatively small footprint compared with other waveguide bends. The method we used is feasible and auto-actuated.

Waveguide crossing

-

A waveguide crossing

The on-chip optical interconnection inevitably needs to address the waveguide cross-connect problem. Herein, we design a waveguide crossing with a footprint of only 2.4 × 2.4 μm2 using the same process as the bend, which has a quadrature symmetry. The structural schematic diagram of the device is described in Fig. 2a,b, the crossing has two input ports labeled as I1 and I2, and two output ports labeled as O1‒O2, respectively. The widths of the two input waveguides and the output waveguide are 480 nm.

Design and simulation results of the waveguide crossing. (a) Initial silicon slab before design optimization. (b) Final optimized structure. (c), (d) Simulated optical field distributions. (e), (f) Simulated normalized transmission spectra. Here, we have plotted the electromagnetic energy density U = ϵ|E|2 + μ|H|2. An animated version of (c) is available in Supplementary Video S2.

This design region is also divided into 20 × 20 discrete pixels with minimum feature size of 90 nm. In the optimizing process, we use the TE0 mode in the wavelength range of 1,400–1600 nm as the only one light source placed at I1 port. The FOM of the crossing for inverse design is defined as:

where T1(i,j) and T1(i,j + 1) represent the average transmission of O1 port in the ith iterate of jth and (j + 1)th pixel, respectively. T2(i,j) and T2(i,j + 1) represent the average transmission of O2 port in the ith iterate of jth and (j + 1)th pixel, respectively. All the transmissions are calculated by 3D FDTD with 40 nm × 40 nm × 40 nm grid size and 8 layers PML. Actually, the first term in the right of Eq. (2) is used to optimize average insertion loss (IL) and the second one is employed to minimize the crosstalk (CT). If FOM = 1, it means IL is improved and CT descend, the pixel state is retained. If not, the pixel state is reversed.

It takes about 36 h after 4 iterations to get the optimized crossing on an eight-core desktop. To investigate the manufacturing error of the crossing, we test the same crossing with a ± 10% variation in pillar diameter. Figure 2c,d shows the simulated optical. The simulated ILs and CTs spectra at O1and O2 ports are plotted in Fig. 2e,f when the continuous wave is launched from input ports I1 and I2, respectively. The simulated CTs for the crossing and the same crossings with ± 10% diameter are < − 19 dB, < − 18 dB, < − 19 dB, respectively. The simulated ILs for all devices are ~ 0.5 dB from 1,400 to 1,600 nm wavelength range. A ± 10% variation in pillar diameter had nearly negligible impact on the IL. Due to a symmetric structure, the results obtained as the light source placed at I1 and I2 ports are consistent.

-

A same direction waveguide crossing

Here, we design another same direction waveguide crossing. As shown in Fig. 3a,b, the inverse design region composed of 20 × 30 discrete pixels occupies a compact footprint of only 2.4 × 3.6 μm2. The crossing is optimized using the same process as the waveguide crossing. The FOM is also defined as Eq. (2). It takes about 48 h after 5 iterations to get the final optimized structure on an eight-core desktop. Figure 3c,d shows the simulated optical and Fig. 3e,f shows the calculated ILs and CTs spectra when the continuous wave is launched from I1 and I2 ports, respectively. For the final crossing, the average IL is ~ 0.56 dB and the CT is < − 21 dB within the wavelength range from 1,400‒1600 nm. Even though the diameter of the crossing changes with a ± 10% variation, the IL and CT curves are still quite consistent. Table 2 summarizes results from some existing literature. It is seen that the waveguide crossings we designed have a small footprint. In contrast with other waveguide crossings, the measured insertion loss and crosstalk are relatively low.

Design and simulation results of the same direction waveguide crossing. (a) Initial silicon slab before design optimization. (b) Final optimized structure. (c), (d) Simulated optical field distributions. (e), (f) Simulated normalized transmission spectra. Here, we have plotted the electromagnetic energy density U = ϵ|E|2 + μ|H|2. An animated version of (c) is available in Supplementary Video S3.

Optical interconnection integrated structures

In principle, the optical signal can be delivered to any chip locations via any routing path provided the low loss bending and crossing are available. For a proof-of-concept demonstration, we arbitrarily design four optical interconnection integrated structures with the proposed waveguide bend and crossings.

The first structure consists of four waveguide crossings, which is named “2_2_2_2” structure. The schematic diagram of this structure is shown in Fig. 4a, its footprint is 2.4 × 5.3 μm2, the span between the four crossings is 500 nm, and the input waveguides and the output waveguide are 480 nm. We define input ports I1–I4 and output ports O1‒O4, respectively. Figure 4b–e shows the simulated optical field when the continuous wave is launched from I1-I4 ports, respectively. The match IL and CT spectra are plotted in Fig. 4f–i. The result curves in Fig. 4f,h, and g,i are consistent due to the symmetric structure. The average IL is ~ 1 dB and the CTs are < − 18 dB within the wavelength range from 1,400 to 1600 nm.

The second structure with a footprint of 8.2 × 8.2 μm2 consists of nine waveguide crossings, which is named “3_3_3_3” structure. The relevant specific parameters of this structure are shown in Fig. 5a. We define input ports I1–I6 and output ports O1‒O6, respectively. Figure 5b–d and h–j show the simulated optical field when the continuous wave is launched from I1-I6 ports, respectively. The match IL and CT spectra are plotted in Fig. 5e–g and k–m. The result curves in Fig. 5e and k, f and l, g and m are consistent due to the symmetric structure. The average IL for all output ports is 2.5 dB from 1,400 to 1,600 nm. The CTs are measured to be < − 16 dB within the same wavelength range.

The third structure with a footprint of 7.7 × 6.14 μm2 consists of three same direction waveguide crossings, which is named “4_4” structure. The labels of input ports and output ports and other relevant specific parameters of this structure are shown in Fig. 6a. Figure 6b–e shows the simulated optical field when the continuous wave is launched from I1-I4 ports, respectively. The match IL and CT spectra are plotted in Fig. 6f–i. The result curves in Fig. 6f and i, g and h are consistent due to the symmetric structure. When the input waves from I1 or I4 input ports, the losses come from the one times cross connection, and the average IL is ~ 0.6 dB and the CTs are < − 20 dB within the wavelength range from 1,400 to 1600 nm. When the input waves from I2 or I3 input ports, the losses come from the two times cross connection, and the average IL is ~ 1.2 dB from 1,400 to 1,600 nm, the CTs are measured to be < − 16 dB within the same wavelength range.

The fourth structure with a footprint of 10.12 × 10.12 μm2 consists of three waveguide bends and three waveguide crossing, which is named “3_3” structure. The relevant specific parameters of this structure are shown in Fig. 7a. We define input ports I1–I3 and output ports O1‒O3, respectively. Figure 7b–d shows the simulated optical field when the continuous wave is launched from I1-I3 ports, respectively. The match IL and CT spectra are plotted in Fig. 7e–g. The average ILs for O1, O2 and O3 output ports are ~ 2.5 dB, ~ 2 dB and ~ 3 dB from 1,500 to 1,580 nm, respectively. The CTs are for O1, O2 and O3 output ports measured to be < − 27 dB, < − 25 dB and < − 21 dB within the same wavelength range, respectively.

The above is a few examples of optical interconnect structures using the waveguide bend and crossings. It is obviously that the number of devices contributes to the losses of the structures. The more devices we use, the greater the losses. The minimum intervals between all devices is 500 nm making sure there is not any out-of-plane light coupling.

Discussion

In this paper, we use inverse design concept and DBS algorithm to design ultra-compact high efficiency and low crosstalk waveguide bend and crossings for optical interconnection based on SOI platform. The footprints of them are only 2.4 × 2.4 μm2, 2.4 × 2.4 μm2 and 2.4 × 3.6 μm2 respectively. The waveguide bend realizes the 90 degree bending of light, up to 0.18 dB transmission efficiency. The ILs and CTs of the waveguide crossings are less than 0.5 dB, 0.56 dB, − 19 dB and − 21 dB, respectively. Furthermore, we arbitrarily design four optical interconnection integrated structures with the proposed waveguide bend and crossings. All of them exhibit high performances. Actually, more optical interconnect structures can be achieved to deliver optical signal using them. The ultra-compact structures will significantly improve the integration density and benefit various on-chip optical systems. Meantime, our design thought and algorithm flow can also be applied to the research and design of other on-chip photonic devices, such as the optical power beam splitter, the mode division multiplexer, the wavelength division multiplexer, etc.

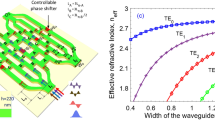

Design method

The overall design idea of inverse design: Firstly, setting the target performance of the devices. Then, according to the set performance requirements, the devices are designed and optimized by using various optimization algorithms. Here, we use DBS algorithm to design the devices. The general process is as follows:

-

(1)

Dividing pixels: The optimized region is divided into a certain number of pixels. The geometry of each pixel can be circle, square, or other complex shapes. The minimum feature size can be determined according to the fabrication capability. In this paper, each pixel is a square of 120 nm × 120 nm with a central circular hole. The hole has a diameter of 90 nm.

-

(2)

Establishing the initial pixel states: Each pixel can occupy two states: silicon or air. For the initial pattern of the devices, all the pixel states are chosen to be silicon in this paper.

-

(3)

Defining figure-of-merit (FOM): the FOM is used to see if the pixel state is witched. Different FOMs are defined according to different devices. In this paper, the FOM is defined as Eqs. (1) or (2).

-

(4)

Witching the pixel state: the state of each pixel is altered one by one, and the FOM is inspected. The pixel state is retained if the FOM is improved. If not, the pixel state is reversed and the algorithm proceeds to the next pixel. One iteration ends after all the pixel states are inspected.

-

(5)

Iterative refinement: The iterations continue until the FOM does not improve further.

Data availability

All data generated or analyzed during this study are included in this article.

References

Miller, S. E. Integrated optics: an introduction. Bell Labs Tech. J. 48(7), 2059–2069 (1969).

Bahadori, M., Bahadori, M., Cheng, Q. & Bergman, K. Universal design of waveguide bends in silicon-on-insulator photonics platform. J. Lightw. Technol. 37(13), 3044–3054 (2019).

Vogelbacher, F. et al. Analysis of silicon nitride partial Euler waveguide bends. Opt. Exp. 27(22), 31394–31406 (2019).

Hu, Z. & Lu, Y. Computing optimal waveguide bends with constant width. J. Lightw. Technol. 25(10), 3161–3167 (2007).

Bogaerts, W. & Selvaraja, S. K. Compact single-mode silicon hybrid rib/strip waveguide with adiabatic bends. IEEE Photon. J. 3(3), 422–432 (2011).

Vlasov, Y. A. & McNab, S. J. Losses in single-mode silicon-on-insulator strip waveguides and bends. Opt. Exp. 12(8), 1622 (2004).

Fujisawa, T., Makino, S., Sato, T. & Saitoh, K. Low-loss, compact, and fabrication-tolerant Si-wire 90° waveguide bend using clothoid and normal curves for large scale photonic integrated circuits. Opt. Exp. 25(8), 9150–9159 (2017).

Cherchi, M., Ylinen, S., Harjanne, M., Kapulainen, M. & Aalto, T. Dramatic size reduction of waveguide bends on a micron-scale silicon photonic platform. Opt. Exp. 21(15), 17814 (2013).

Liu, H., Tam, H., Wai, P. & Pun, E. Low-loss waveguide crossing using a multimode interference structure. Opt. Commun. 241(1), 99–104 (2004).

Chen, H. & Poon, A. W. Low-loss multimode-interference-based crossings for silicon wire waveguides. IEEE Photon. Technol. Lett. 18(21), 2260–2262 (2006).

Bogaerts, W., Dumon, P., Van, T. D. & Baets, R. Low-loss, low-crossing-talk crossings for silicon-oninsulator nanophotonic waveguides. Opt. Lett. 32(19), 2801–2803 (2007).

Sanchis, P. et al. Highly efficient crossing structure for silicon-on-insulator waveguides. Opt. Lett. 34(18), 2760–2762 (2009).

Zhang, Y. et al. A CMOS-compatible, low-loss, and low-crossingtalk silicon waveguide crossing. IEEE Photon. Technol. Lett. 25(5), 422–425 (2013).

Ma, Y. et al. Ultralow loss single layer submicron silicon waveguide crossing for SOI optical interconnect. Opt. Exp. 21(24), 29374–29382 (2013).

Sun, C., Yu, Y. & Zhang, X. Ultra-compact waveguide crossing for a mode-division multiplexing optical network. Opt. Lett. 42(23), 4913–4916 (2017).

Xu, H. & Shi, Y. Dual-mode waveguide crossing utilizing taper-assisted multimode-interference couplers. Opt. Lett. 41(23), 5381–5384 (2016).

Han, H. et al. High performance ultra-compact SOI waveguide crossing. Opt. Exp. 26(20), 25602–25610 (2018).

Chang, W. et al. Ultracompact dual-mode waveguide crossing based on subwavelength multimode-interference couplers. Photon. Res. 6(20), 660–665 (2018).

Shen, B., Wang, P., Polson, R. & Menon, R. An integrated-nanophotonics polarization beamsplitter with 2.4 × 2.4 μm2 footprint. Nat. Photon. 9(6), 378 (2015).

Lu, J. & Vučković, J. Nanophotonic computational design. Opt. Exp. 21(11), 13351–13367 (2013).

Meem, M. et al. Broadband lightweight flat lenses for long-wave infrared imaging. PNAS 43, 21375–21378 (2019).

Meem, M., Meem, A. & Menon, R. Multi-plane, multi-band image projection via broadband diffractive optics. Appl. Opt. 59(1), 38–44 (2019).

Xiao, T. et al. Diffractive spectral-splitting optical element designed by adjoint-based electromagnetic optimization and fabricated by femtosecond 3D direct laser writing. ACS Photon. 3(5), 886–894 (2016).

Su, L., Piggott, A. Y., Sapra, N. V., Petykiewicz, J. & Vuckovic, J. Inverse design and demonstration of a compact on-chip narrowband three-channel wavelength demultiplexer. ACS Photon. 5(2), 301–305 (2018).

Sapra, N. V. et al. Inverse design and demonstration of broadband grating couplers. IEEE J. Sel. Top. Quantum Electron. 25(3), 1–7 (2019).

Shen, B., Polson, R. & Menon, R. Metamaterial-waveguide bends with effective bend radius < λ0/2. Opt. Lett. 40(24), 5750–5753 (2015).

Majumder, A., Shen, B., Shen, R. & Menon, R. Ultra-compact polarization rotation in integrated silicon photonics using digital metamaterials. Opt. Exp. 25(17), 19721–19731 (2017).

Tahersima, M. H. et al. Deep neural network inverse design of integrated photonic power splitters. Sci. Rep. 9, 1368 (2019).

Turduev, M. et al. Ultracompact photonic structure design for strong light confinement and coupling into nanowaveguide. J. Lightw. Technol. 36(14), 2812–2819 (2018).

Xu, K. et al. Integrated photonic power divider with arbitrary power ratios. Opt. Lett. 42(4), 855–858 (2017).

Xie, H. et al. Inversely designed 1 × 4 power splitter with arbitrary ratios at 2-μm spectral band. IEEE Photon. J. 10(4), 1–6 (2018).

Liu, Y. et al. Arbitrarily routed mode-division multiplexed photonic circuits for dense integration. Nat. Commun. 10(1), 1–7 (2019).

Lu, L., Liu, D., Yan, M. & Zhang, M. Subwavelength adiabatic multimode Y-junctions. Opt. Lett. 44(19), 4729–4732 (2019).

Chang, W. et al. An ultra-compact multimode waveguide crossing based on subwavelength asymmetric Y-junction. IEEE Photon. J. 10, 1–8 (2018).

Chang, W. et al. Ultra-compact mode (de)multiplexer based on subwavelength asymmetric Y-junction. Opt. Exp. 26(7), 8162–8170 (2018).

Huang, J. et al. Ultra-compact broadband polarization beam splitter with strong expansibility. Photon. Res. 6(6), 574–578 (2018).

Huang, J. et al. Implementation of on-chip multi-channel focusing wavelength demultiplexer with regularized digital metamaterials. Nanophotonics. 9(1), 159–166 (2019).

Li, Z., Zhang, Z., Huang, J. & Yang, J. genetically designed ultra-compact wideband multiple-use reflectors with high reflectivity appling to optics communication. ICCT(2019). 724–728. https://doi.org/10.1109/ICCT46805.2019.8947154 (2019).

Han, J., et al. Inverse designed ultra-compact dual-channel wavelength demultiplexer with plasmonic subwavelength structure. ACPC(2019). Paper M4A. 283 (2019).

Ma, H., Huang, J., Zhang, K. & Yang, J. Arbitrary-direction, multichannel and ultra-compact power splitters by inverse design method. Opt. Commun. 462, 125329. https://doi.org/10.1016/j.optcom.2020.125329 (2020).

Lumerical FDTD Solutions. https://www.lumerical.com.

Acknowledgements

This work was supported by the National Natural Science Foundation of China (60907003, 61805278, 61661004), the Guangxi Science Foundation (2017GXNSFAA198227), the Foundation of NUDT (JC13-02-13, ZK17-03-01), the Hunan Provincial Natural Science Foundation of China (13JJ3001), and Program for New Century Excellent Talents in University (NCET) (NCET-12-0142).

Author information

Authors and Affiliations

Contributions

Z.L. and G.L. contributed equally to this work. Z.L. and G.L. finished the algorithm and English writing of the paper together; Z.L. designed and performed the analysis, and prepared the figures/tables; J.Y., J.H., C.Y., Y.Q. and W.X. contributed to manuscript preparation; J.Y. and J.H. conceptualized and coordinated the study; J.Y. and Z.Z. supervised the project. H.H. participated in the revision of the paper.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Li, Z., Li, G., Huang, J. et al. Ultra-compact high efficiency and low crosstalk optical interconnection structures based on inverse designed nanophotonic elements. Sci Rep 10, 11993 (2020). https://doi.org/10.1038/s41598-020-68936-w

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-020-68936-w

This article is cited by

-

Optimizing bend loss in optical waveguide channel routing on photonic integrated circuits

Journal of Computational Electronics (2022)

-

Inverse-designed ultra-compact high efficiency and low crosstalk optical interconnect based on waveguide crossing and wavelength demultiplexer

Scientific Reports (2021)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.