Abstract

We report transport measurements of dual gated MoS2 and WSe2 devices using atomic layer deposition grown Al2O3 as gate dielectrics. We are able to achieve current pinch-off using independent split gates and observe current steps suggesting possible carrier confinement. We also investigated the impact of gate geometry and used electrostatic potential simulations to explain the observed device physics.

Similar content being viewed by others

Introduction

Two-dimensional transition metal dichalcogenides (2D TMDCs) have attracted increasing interest for creating novel quantum electronics due to their intriguing properties1,2,3. Notably, these atomically thin materials provide natural charge confinement in one spatial dimension and can also possess a sizable bandgap, offering unique opportunities for fabricating novel electrostatically gated devices for quantum information processing4,5. The smooth confinement potential minimizes edge and defect states that can otherwise arise from using physical etching processes. Recently, theoretical works have explored exploiting spin and valley states in 2D TMDCs to create electrostatically gated spin-valley qubits6,7,8. This is promising due to the broken spatial inversion symmetry in 2D TMDCs and strong spin-valley coupling that can allow for concurrently valley and spin-polarized charge carriers with long coherence times. Furthermore, valley-dependent optical selection rule in 2D TMDCs suggests the possibility of creating optically controllable spin-valley qubits in 2D TMDCs8,9,10.

The first step towards such TMDC quantum devices is to demonstrate effective carrier confinement with electrostatically tunable confinement potentials. However, it is technically challenging to implement effective carrier confinement in 2D TMDCs due to issues such as residual disorder, low mobility and non-ohmic contacts to the TMDC11. While van-der-Waals heterostructure devices utilizing encapsulated hexagonal boron nitride (hBN) have demonstrated effective carrier confinement with electrostatic gates and superior performance, scalability can be limited. Carrier confinement has been demonstrated in MoS2 devices using hBN at temperatures up to 4 K12,13,14,15,16. WSe2 devices using ALD oxides have demonstrated carrier confinement only at 240 mK17. Measurements at such millikelvin temperatures can be a costly experimental challenge. Here, we present our work on 2D MoS2 and WSe2 devices encapsulated with atomic layer deposition (ALD) Al2O3 using a 4 K cryostat. We observe current pinch-off and current steps up to 25 K suggesting carrier confinement while demonstrating independent split top gate control over the current flow. Using electrostatic potential simulations, our device physics can be consistently explained by the electrostatic potential variations resulting from the combination of our device geometries and applied gate voltages.

Experiment

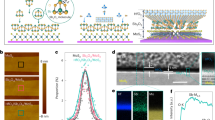

The device fabrication process is illustrated in Fig. 1a. SEM images of the fabricated devices are shown in Fig. 1b (MoS2) and 1c (WSe2). We fabricated our devices by mechanically exfoliating flakes from bulk crystals. These flakes are deposited on to heavily doped silicon substrates with a 285 nm layer of SiO2 on top. The substrates also function as global back gates for tuning the overall carrier densities in the conducting materials. We next optically identified appropriate few-layer flakes of suitable size for device fabrication. Using standard e-beam lithography and e-beam evaporation, we deposited 10/80 nm of Ti/Au metal as source-drain electrodes. We maximized the contact areas of the electrodes in order to achieve good ohmic contact. After lift-off, the samples are annealed at 200 °C in forming gas H2/Ar atmosphere for 2 hours to improve the contacts and remove residual resist18.

Device fabrication. (a) Schematic of the device fabrication process. SEM images of the few-layer (b) MoS2 and the (c) WSe2 devices. The insets show closeups of the split gate geometries. They are labelled TG, MG and PG. Scale bars are 10 μm and 500 nm (insets). SEM images of the ALD growth (d) without and (e) with an Al seed layer. Scale bars are (d) 10 μm (e) and 500 nm.

To form local top gates essential for inducing carrier confinement, a suitable dielectric layer is required. We used a Beneq TFS200 ALD system with precurors Trimehylaluminium (TMA) and water at a temperature of 200 °C to deposit 33 nm of Al2O3 high-k dielectric. While 2D TMDCs offer a pristine surface and lack of dangling bonds, this negatively affects the ALD process as it results in island-type growth which leads to poor dielectric coverage and gate leakage (Fig. 1d). To circumvent this problem, we first deposited a 1 nm thick Al seed layer via thermal evaporation prior to ALD growth which results in uniform ALD coverage19. The two top split gates were subsequently defined using e-beam lithography and e-beam evaporation to deposit 5/30 nm of Ti/Au metal. After lift-off, the devices were annealed once again at 200 °C in forming gas H2/Ar atmosphere for 2 hours.

Results and Discussion

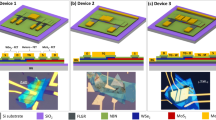

We measured a total of three devices labelled D1, D2 and D3. As the WSe2 flake obtained is sufficiently large, we patterned two devices with different geometries on the same flake (D2, D3) (Fig. 1c inset). D2 was patterned with a gap in the center of the gate labelled MG. Previous works on 2DEG quantum dots have raised the necessity of having independent gates to control multiple tunneling barriers, resulting in gaps between the confinement gates12,14. It remains unclear how gaps in device geometries can impact the transport properties and confinement potential of the device. We investigated the influence of this gap by comparing the characteristics of D2 and D3. While the lithographically defined gate geometries suggest that tunnelling barriers will likely be formed in the two gaps between the gates PG and MG (insets of Fig. 1b,c), our simulations, discussed later, show that the actual electrostatic potential profile can be different from the gate geometries.

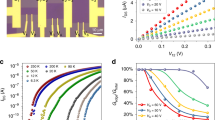

We first measured transport without using the top local split gates. All measurements were performed in a closed-cycle Janis cryostat using low-noise Stanford Research Systems SRS928 voltage sources and an AlazarTech ATS9440 DAQ at 4 K, unless otherwise stated. After cooling to 4 K, the devices were illuminated using a 660 nm light-emitting diode to reduce defect-related impurity traps and improve the carrier homogeneity. All subsequent measurements are performed with the light emitting diode turned off14,20. Figure 2 shows the transport properties of devices D1 and D2. For both MoS2 D1 and WSe2 D2, we recorded linear current I versus source-drain voltage VSD curves at various back gate voltages VBG indicating ohmic contacts that are important so that the contacts do not dominate device operation (Fig. 2a,c). Characteristic n-type semiconducting behaviors are observed for both devices (Fig. 2b,d), but with different turn on voltages. WSe2 D2 and D3 (Supplementary Material) have more positive turn on voltages compared to MoS2 D1, which leads to distinct operating top gate voltages for the two materials, as will be shown in the subsequent sections.

Transport properties. Current I vs source-drain voltage VSD curves at various applied back gate voltages VBG for (a) MoS2 (D1) and (c) WSe2 (D2). Current I vs back-gate voltage VBG curves for (b) MoS2 (D1) and (d) WSe2 (D2). The current starts to increase at 23 V for MoS2 D1 and 84 V WSe2 D2 as the devices are turned on.

To achieve carrier confinement, the carrier densities in our TMDCs should be locally tunable with the top gates. Figure 3a shows the current I through MoS2 D2 as a function of both the applied back gate voltage VBG and top gate voltage VTG. In this measurement, the same voltage VTG was applied to both the split gates (inset of Fig. 1b). The current through the device depends on both VBG and VTG and can be pinched off when sufficiently negative VTG was applied (lower left dark region). The required VTG to achieve pinch-off becomes increasingly negative at more positive VBG, i.e. at higher carrier densities.

Top gate control. (a) Current I vs top gate voltage VTG and back gate voltage VBG for MoS2 D1. The current can be smoothly tuned by both VTG and VBG. The dark lower left region highlights the voltage space when the conducting channel of the device is pinched off. (b) I vs VTG at various applied VBG, where current steps can be observed, suggesting the formation of a quantum constriction. (c) Current I vs top gate voltages VMG and VPG at VBG = 105 V for WSe2 D2 (see Fig. 1c inset). The current through the device can be independently controlled by the split top gates PG and MG. (d) Current I vs VPG at fixed VBG and VMG taken at different temperatures. The current steps are visible up to 25 K. (e) I vs VPG at various applied VMG and fixed VBG = 105 V, where similar current steps are observed.

In dual gated systems, signatures of quantum confinement reported in literature are the following. (1) Regular and periodically spaced Coulomb diamonds/conductance peaks which occur in quantum dots with two tunnelling barriers12,14,17,21. (2) Multiple regularly spaced step like features in multiples of e2/h that occur in quantum constrictions with symmetric top gates reflecting conductance quantisation13,22. (3) Few/single current steps in device geometries with asymmetric top gates that occurs at similar conductance for several back-gate voltages14,15.

From the I vs VTG curves for fixed VBG (Fig. 3b), we observe current steps of similar conductances at multiple VBG suggesting possible carrier confinement as the width of the conducting channel is reduced with increasing VTG, similar to measurements reported in other works13,14,15. Small current peaks are also observed. Such peaks have been observed in other material systems and can have various origins such as universal conductance fluctuations, Fabry perot oscillations and single-electron tunnelling12,14,17,21,23,24,25,26,27,28. Carrier disorder in our devices can also possibly lead to the observed peaks14. Figure 3 presents two-terminal measurements and can include significant contact resistance. Subtracting these parasitic resistances is difficult as they can be strongly gate and bias voltage dependent. Similar issues have been observed in refs 14,15,22, where the authors likewise observe steps at conductances smaller than the quantum conductance. We note that in order to gain deeper insight and demonstrate exact quantization, further improvements in the device and material quality (carrier homogeneity, impurities, dielectric interfaces and contact quality) as well as the optimization of device geometry and experimental setup (e.g. 4-probe, lower temperatures) will be required and represent on going efforts in the group.

We next performed similar measurements on our WSe2 devices D2 (Fig. 3c,d) and D3 (Supplementary Material). To confirm that the current through the device is due to electrostatic modification of the carrier density by the top gates, we measured the device current while applying independent voltages VMG and VPG to the top gate electrodes MG and PG (inset Fig. 1c). Figure 3c shows I as a function of VMG and VPG at a fixed VBG = 105 V. We observe that the current is pinched off only when both VMG and VPG are sufficiently negative, leading to the rectangular dark pinch-off region in the lower left of Fig. 3c. The edges of this rectangular pinch-off region are non-diagonal, indicating that current can be independently tuned with minimal cross-capacitance. We note that the top gate voltages applied in WSe2 devices D2 and D3 (~−8.5 V) are smaller than the devices applied in MoS2 D1 (~−16.5 V). This difference in applied top gate voltages is due to the different turn on voltages for MoS2 and WSe2 (Fig. 2b,d). The larger VBG required to turn on WSe2 compared to MoS2 consequently means that lower voltages are required to deplete the carrier distribution under the top gate electrodes. Thus, even though similar device architectures can be applied across different 2D TMDC materials to achieve carrier confinement, design considerations should take into account intrinsic material properties such as material doping levels that can depend on the dielectric type.

When varying a single gate voltage VPG, similar current steps observed in MoS2 D1 are likewise discerned in WSe2 D2 (Fig. 3e). At larger VMG (VMG = −6.5 V to −8.5 V), the steps occur at similar conductances, suggesting the formation of a carrier constriction. At smaller VMG (VMG = −5 V to −6.5 V), the conductance of the current steps deviates, likely due to the constriction being ill defined as a result of the smaller applied VMG. Figure 3d shows the temperature dependence of the I versus VPG curves taken at different temperatures from 4 K to 40 K. The current steps gradually smear out with increasing temperature, consistent with thermal broadening of the electron energy distribution.

Similar pinch-off characteristics are observed in device D3 but with two main differences. Firstly, to achieve current pinch-off, a more negative VPG ≈ −6.5 V was required for D3 compared to D2 (VPG ≈ −3.5 V, VMG for both D2 and D3 are similar at ≈−6.5 V). Secondly, there are no obvious current steps in D3. These differences can be due factors including inhomogeneity of the carrier distribution or the electrostatic potential landscape. A more interesting possibility is the difference in the gate geometries between D2 and D3; D2 is fabricated with a gap in the middle of the gate MG. We further investigated this possibility through simulations of the electrostatic potentials. While we can control current flow using our split top gates MG and PG and observe possible carrier confinement in the TMDC, the exact geometries of any quantum constrictions are difficult to extract from the transport measurements. To gain a deeper insight into our device physics and the geometries of possible quantum constrictions, we used the commercial software COMSOL to perform a finite element analysis simulation of the electrostatic potential profiles.

We begin by investigating how the electrostatic potential in WSe2 D2 is dependent on gate electrodes MG and PG. Figure 4a shows the electrostatic potential profiles for WSe2 D2 at different VMG and VPG corresponding to the positional labels marked A–D in Fig. 3c. We note that the actual device potentials are not easily calculated due to difficulty in determining the actual WSe2 intrinsic doping. Nevertheless, the simulations suggest how the electron density profiles depend on the gates. At position A, the electrostatic potential profile shows no available conduction channel resulting in complete current pinch-off. When VPG is made less negative relative to VMG, a conduction channel (arrow in panel B) is opened. The formation of this quantum constriction is marked by the conduction step in the current (Fig. 3d). At position C, when VMG is less negative relative to position A for the same VPG, the barrier potential decreases slightly and a possible parallel conductance channel (arrows in Fig. 4a, panel C) can open, leading to increased current. Finally, when both VPG and VMG are made less negative at position D compared to A, current flow is no longer limited by the constrictions and the device operates in a field effect regime.

Electrostatic potential simulations. Top gate geometries are overlaid as dotted green lines. (a) Electric potential simulations U(x, y) of WSe2 device D2, The color scale is in arbitrary units as the potential is generally tunable with the back-gate. Darker colors correspond to more positive U and lower electron density. Panels (A–D) show U(x, y) with top gate voltages corresponding to the labels in Fig. 3c. A - device pinched off, B - conductance through one quantum constriction, (C) conductance through two possible quantum constrictions. D - field effect regime. (b) Potential barrier height vs xgap, size of the gap in the gate MG. Insets - closeups of U with the position of barrier height indicated (Supplementary Fig. 2). (c) Dependence of U(x, y) on the ALD dielectric layer. All top gate voltages are set to 0 V.

We next investigated the difference in transport characteristics of WSe2 D2 and D3. Our simulations show that the presence of the gap in gate MG of device D2 may lead to stronger carrier confinement. Figure 4b shows the potential barrier of the constriction (arrows) as a function of the MG gap size xgap for the same applied gate voltages. This is a possible reason why no obvious current steps are measured in D3 (xgap = 0 nm), and a more negative VPG compared to D2 is required to pinch off the current.

Finally, the potential can be more sharply defined by reducing the thickness of the ALD Al2O3 to obtain quantum dots (Fig. 4c). This can also be achieved with a higher-k dielectric such as HfO2. At the same thickness of 33 nm, a HfO2 dielectric produces an electrostatic potential profile with only a single quantum constriction. Such flexibility is a possible advantage of ALD dielectrics. TMDC based quantum devices can be designed with desired properties by precise control of the ALD dielectric type and thickness.

Conclusion

Electrostatic control over carrier confinement is a crucial step towards realizing novel TMDC-based quantum electronics such as spin-valley qubits. We present measurements and simulations of 2D MoS2 and WSe2 devices with local split top gates. Our devices are made using ALD grown Al2O3. We can achieve current pinch-off and observe current steps and peaks suggesting possible carrier confinement at 4 K, similar to measurements at lower temperatures of more complex van-der-Waals heterostructure TMDC devices based on exfoliated hexagonal boron nitride. Our device physics and transport characteristics can be explained through simulations of the electrostatic potential variations resulting from the combination of the device geometries and applied gate voltages. Future work can explore the possibility of using large-area TMDC sheets grown with chemical vapour deposition. With further improvements in ALD growth and contact quality, scalable TMDC quantum devices fabricated using CMOS-compatible technology remain a distinct possibility.

Change history

25 August 2021

A Correction to this paper has been published: https://doi.org/10.1038/s41598-021-96557-4

References

Fiori, G. et al. Electronics based on two-dimensional materials. Nature Nanotechnology 9, 768 (2014).

Novoselov, K. S., Mishchenko, A., Carvalho, A. & Castro Neto, A. H. 2D materials and van der Waals heterostructures. Science 353 (2016).

Stanford, M. G., Rack, P. D. & Jariwala, D. Emerging nanofabrication and quantum confinement techniques for 2D materials beyond graphene. npj 2D Materials and Applications 2, 20 (2018).

Kormányos, A., Zólyomi, V., Drummond, N. D. & Burkard, G. Spin-orbit coupling, quantum dots, and qubits in monolayer transition metal dichalcogenides. Physical Review X 4, 1–16 (2014).

Luo, G. et al. Quantum dot behavior in transition metal dichalcogenides nanostructures. Frontiers of Physics 12 (2017).

Pearce, A. J. & Burkard, G. Electron spin relaxation in a transition-metal dichalcogenide quantum dot. 2D Materials 4, 025114 (2017).

Széchenyi, G., Chirolli, L. & Pályi, A. Impurity-assisted electric control of spin-valley qubits in monolayer MoS2. 2D Materials 5, 035004 (2018).

Wu, Y., Tong, Q., Liu, G.-B., Yu, H. & Yao, W. Spin-valley qubit in nanostructures of monolayer semiconductors: Optical control and hyperfine interaction. Phys. Rev. B 93, 045313 (2016).

Zeng, H., Dai, J., Yao, W., Xiao, D. & Cui, X. Valley polarization in MoS2 monolayers by optical pumping. Nature Nanotechnology 7, 490 (2012).

Mak, K. F., He, K., Shan, J. & Heinz, T. F. Control of valley polarization in monolayer MoS2 by optical helicity. Nature Nanotechnology 7, 494 (2012).

Lee, K., Kulkarni, G. & Zhong, Z. Coulomb blockade in monolayer MoS2 single electron transistor. Nanoscale 8, 7755–7760 (2016).

Pisoni, R. et al. Gate-tunable quantum dot in a high quality single layer MoS2 van der Waals heterostructure. Applied Physics Letters 123101, 2016–2019 (2018).

Pisoni, R. et al. Gate-defined one-dimensional channel and broken symmetry states in MoS2 van der Waals heterostructures. Nano Letters 17, 5008–5011 (2017).

Wang, K. et al. Electrical control of charged carriers and excitons in atomically thin materials. Nature Nanotechnology 13, 128–132 (2018).

Sharma, C. H. & Thalakulam, M. Split-gated point-contact for electrostatic confinement of transport in MoS2/h-BN hybrid structures. Scientific Reports 7, 1–6 (2017).

Marinov, K., Avsar, A., Watanabe, K., Taniguchi, T. & Kis, A. Resolving the spin splitting in the conduction band of monolayer MoS2. Nature Communications 8, 1–7 (2017).

Song, X.-X. et al. A gate defined quantum dot on the two-dimensional transition metal dichalcogenide semiconductor WSe2. Nanoscale 7, 16867–16873 (2015).

Lim, Y.-F. et al. Modification of vapor phase concentrations in MoS2 growth using a NiO foam barrier. ACS Nano 12, 1339–1349 (2018).

Kim, H. G. & Lee, H.-B.-R. Atomic layer deposition on 2D materials. Chemistry of Materials 29, 3809–3826 (2017).

Zhang, Z.-Z. et al. Electrotunable artificial molecules based on van der waals heterostructures. Science Advances 3, 10 (2017).

Song, X.-X. et al. Temperature dependence of Coulomb oscillations in a few-layer two-dimensional WS2 quantum dot. Scientific Reports 5, 16113 (2015).

Epping, A. et al. Quantum transport through MoS2 constrictions defined by photodoping. Journal of Physics: Condensed Matter 30, 205001 (2018).

Lee, P. A. & Stone, A. D. Universal conductance fluctuations in metals. Phys. Rev. Lett. 55, 1622–1625 (1985).

Datta, S. Electronic Transport in Mesoscopic Systems (1995).

Liang, W. et al. Fabry - Perot interference in a nanotube electron waveguide. Nature 411, 665 (2001).

Kouwenhoven, L. P. et al. Excitation spectra of circular, few-electron quantum dots. Science 278, 1788–1792 (1997).

Hanson, R. et al. Spins in few-electron quantum dots. Reviews of Modern Physics 79, 1217–1265 (2007).

Kotekar-Patil, D., Nguyen, B.-M., Yoo, J., Dayeh, S. A. & Frolov, S. M. Quasiballistic quantum transport through Ge/Si core/shell nanowires. Nanotechnology 28, 385204 (2017).

Acknowledgements

This work was supported by the A*STAR (Singapore) QTE Grant No. A1685b0005. The authors would like to thank D. Kotekar-Patil for useful discussion.

Author information

Authors and Affiliations

Contributions

C.S.L. and K.E.J.G. conceived the experiments, C.S.L., J.Y.C., D.T., H.K., J.D., S.L.W., Z.E.O. and Y.F.L., conducted the experiments, C.S.L., J.Y.C. and K.E.J.G. analysed the results. All authors reviewed the manuscript.

Corresponding author

Ethics declarations

Competing Interests

The authors declare no competing interests.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

The original online version of this Article was revised: The original version of this Article contained an error in Figure 3b, where the y-axis “/(nA)” now reads: “/(μA)”.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Lau, C.S., Chee, J.Y., Thian, D. et al. Carrier control in 2D transition metal dichalcogenides with Al2O3 dielectric. Sci Rep 9, 8769 (2019). https://doi.org/10.1038/s41598-019-45392-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-019-45392-9

This article is cited by

-

Van der Waals enabled formation and integration of ultrathin high-κ dielectrics on 2D semiconductors

npj 2D Materials and Applications (2024)

-

Anomalous conductance quantization of a one-dimensional channel in monolayer WSe2

npj 2D Materials and Applications (2023)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.