Abstract

In this work, we have successfully demonstrated the junctionless (JL) transistors with two-dimensional-like (2D-like) nano-sheet (NS) material, amorphous indium tungsten oxide (a-IWO), as an active channel layer. The influences of the different gate insulator (GI) materials and the scalings of GI thickness, a-IWO channel thickness, and channel lengths on the a-IWO NS JL transistors (a-IWO NS-JLTs) have been studied for the purposes of low operation voltage (gate voltage ≤2V) and high performance. The 2D-like a-IWO NS-JLTs exhibit low operation voltage, low source/drain (S/D) contact resistance (RC) and other key electrical characteristics, such as high field-effect mobility (μFE), near ideal subthreshold swing (S.S.), and large ON/OFF currents ratio (ION/IOFF). The remarkable device characteristics also make the proposed 2D-like a-IWO NS-JLTs promising for system-on-panel (SoP) and vertically stacked (VS) hybrid CMOS applications.

Similar content being viewed by others

Introduction

As devices scaling continues, Si-based ultra-thin body (UTB) field-effect transistors (FETs) and FinFET with low leakage currents and good gate controllability allow gate/channel length reduction through Fin (body) thickness scaling1,2. Furthermore, the single crystalline silicon (Si)/polycrystalline silicon (poly-Si)-based nanowires (NWs) and nano-sheet (NS) junctionless (JL) devices with low operation voltage and near ideal subthreshold characteristics have been proposed and demonstrated for lower thermal budgets and easier processes3,4,5,6. Since the gradient of a doping concentration is absent, the issues of the sharp doping profile formation and the impurities diffusion are completely eliminated5. Nevertheless, FETs/FinFET with sub-5nm technology node require sub-3nm-thick body for better channel controllability7. Most Si-based devices with such an ultra-thin body thickness will face several challenges, including the control of channel thickness (Tch), high source/drain (S/D) parasitic resistance (RSD), and uniform S/D and channel heavy doping for JL FETs devices6. Therefore, as Si-based CMOS scaling approaches its limits (Tch < 5 nm), it is highly urgent and desirable to investigate other ultra-thin/two-dimensional (2D) channel materials with relatively wide band gaps and high mobility. Such ultra-thin/2D channel materials can potentially suppress short channel effects (SCEs) and achieve high ON/OFF currents ratio (ION/IOFF) owing to good gate electrostatics and low leakage currents for digital circuit applications8.

Recently, indium oxide (InOx)-based transparent amorphous oxide semiconductor thin film transistors (TAOS TFTs) with wide band gaps have been developed and applied not only for display but also for other applications, like flexible electronics, optoelectronics, and mobile electronics owing to superior uniformity, low-temperature processes, and high field-effect mobility (μFE)9. In the last few years, the vertically stacked (VS) hybrid complementary metal-oxide-semiconductor (CMOS) consisted of low-temperature c-axis aligned crystalline In-Ga-Zn-O (CAAC-IGZO) FETs with 60 nm technology node and p-channel Si MOSFETs with 65 nm technology node have been successfully fabricated and demonstrated10,11,12. Back-end of line (BEOL) compatible nano-scaled CAAC-IGZO FETs with ultra-low OFF-state currents (IOFF) and SCEs immunity are promising candidates for low power large-scale integration (LSI) and internet of things (IoT) applications12. Although CAAC-IGZO FETs exhibit a μFE ~10 cm2/V-s, the μFE and subthreshold swing (S.S.) of CAAC-IGZO FETs are degraded by increasing channel width10. Consequently, further improvements in μFE and the stability of the TAOS TFTs are urgently required to broaden their range of potential applications. To achieve these targets, an amorphous indium tungsten oxide (a-IWO) semiconducting material with high mobility and stability, which is free from both Ga and Zn, was studied for an alternative choice to a-IGZO TFTs13,14,15. We have successfully fabricated and demonstrated the low thermal budget 2D-like a-IWO NS JL transistors (a-IWO NS-JLTs) in bottom metal gate (BMG) configurations with high μFE ~25.3 cm2/V-s, near ideal S.S. ~63 mV/dec., and improved hysteresis characteristics for the first time16. The thickness of conductive a-IWO NS channel can be well controlled by radio-frequency (RF) magnetron sputtering at room temperature. The a-IWO NS-JLTs with metal S/D electrodes exhibit ultra-low leakage currents owing to the wider band gap of a-IWO compared to Schottky-barrier Si devices with high leakage currents17. Furthermore, the RSD also can be significantly reduced by using metal S/D electrodes.

In this work, we will study the influences of the different gate insulator (GI) materials and the scalings of GI thickness, a-IWO channel thickness, and channel lengths on the electrical characteristics and performances of a-IWO NS-JLTs. In addition, a low power and high performance CMOS inverter based on low temperature devices is the basic and essential component in digital circuits for the pressing applications such as wearable electronics and IoT technology. Although some hybrid CMOS inverters constructed by low temperature n-channel TAOS and p-channel poly-Si TFTs had been studied and realized, the electrical characteristics of TFTs were performed with high operation voltage, poor S.S, and large IOFF in these previous studies18,19. A conceptual VS hybrid CMOS structure consisted of BEOL compatible n-channel a-IWO NS-JLTs and p-channel poly-Si TFTs will be proposed and characterized in this work. The matched electrical characteristics of n- and p-channel devices with low operation voltage and low IOFF are exhibiting the promising candidate for future VS Hybrid CMOS applications.

Methods

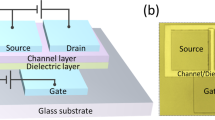

The structure diagram of proposed BMG a-IWO NS-JLTs is schematically shown in Fig. 1(a). The proposed devices can be fabricated on Si wafers with 550-nm-thick buffer thermal SiO2 or on glass substrates16. Firstly, a layer of 25-nm-thick Mo film was deposited subsequently by the direct current (DC) sputtering and patterned as the gate electrode through photolithography. Secondly, a layer of 10-nm or 20-nm or 30-nm-thick HfO2 was deposited by atomic layer deposition (ALD) as the gate insulator (GI). Next, a layer of 4-nm or 10-nm-thick a-IWO channel was deposited by RF magnetron sputtering of an In-W-O (contained 4 wt.% of WO3) ceramic plate target at room temperature. Then, the a-IWO channel active layer was patterned through photolithography. Thirdly, a layer of 25-nm-thick Mo film was deposited by DC sputtering and patterned as the source/drain (S/D) electrodes using the lift-off technique. Finally, after channel passivation processes, contact holes to the gate and S/D electrodes were patterned and opened through photolithography.

To investigate the influences of different GI materials on the devices, the a-IWO NS-JLTs in bottom Si-sub gate (BSG) configurations with a-IWO NS channel = 4 nm were also fabricated on a heavily doped n-type Si wafer with 30-nm-thick high-quality thermal SiO2 GI, as shown in Fig. 1(b). Additionally, the low metal contamination Ni-induced lateral crystallization (LC-NILC) poly-Si TFTs with 50-nm-thick poly-Si channel and 10-nm-thick HfO2 GI were also fabricated on Si-substrates to study the OFF-state electrical characteristics for VS hybrid CMOS applications. The detail LC-NILC processes were shown in our previous work20.

Results and Discussion

Figure 1(c) displays the cross-sectional transmission electron microscope (TEM) images of proposed BMG a-IWO NS-JLTs. The thickness of a-IWO NS channel and HfO2 GI are 4 nm and 10 nm, respectively. In general, the surface of a-IWO film deposited by means of magnetron sputtering is extremely flat13. The interfacial layer (IL) was consequently formed and found during deposition of HfO2 GI on the channel in the conventional top-gate devices. Since the deposition of HfO2 GI was made before the deposition of a-IWO NS channel in the proposed BMG a-IWO NS-JLTs, the IL between the HfO2 GI and the a-IWO NS channel is negligible, resulting in near ideal S.S. and improved hysteresis characteristics16.

Figure 2 exhibits the transfer characteristics of a-IWO NS-JLTs with different GI materials, different HfO2 GI thickness, and different a-IWO channel thickness. In JL configurations, the doping or carrier concentration of the source/drain (S/D) and channel is uniform, heavy, and homogenous, which significantly reduces thermal budgets of processes and simplifies fabrication5. However, there are more negative VTH and worse subthreshold characteristics in JL devices with thicker thickness of channel (a-IWO channel = 10 nm) or under poorer gate controls (HfO2 GI = 30 nm for BMG and SiO2 GI = 30 nm for BSG) in Fig. 2 21. Among these devices, the transfer characteristics of BSG a-IWO NS-JLTs with a-IWO channel = 4 nm and SiO2 GI = 30 nm exhibit the weakest gate control on channel, resulting in the absence of an OFF-state within VGS = −2V ~ VGS = 2V. The ON-state currents (ION) and S.S. of BMG a-IWO NS-JLTs are enhanced by shrinking the HfO2 GI thickness (HfO2 GI = 10 nm) thanks to the better gate controllability. Although BMG a-IWO NS-JLTs with HfO2 GI = 10 nm and a-IWO channel = 10 nm have the highest ION and μFE, the most positive VTH, highest ION/IOFF, and steepest S.S. are accomplished in BMG a-IWO NS-JLTs with HfO2 GI = 10 nm and a-IWO channel = 4 nm for low operation voltage applications. Therefore, we will focus the BMG a-IWO NS-JLTs with HfO2 GI = 10 nm and a-IWO channel = 4 nm in the latter discussions.

The transfer characteristics of a-IWO NS-JLTs with different GI materials, different HfO2 GI thickness, and different a-IWO channel thickness. The most positive VTH, highest ION/IOFF, and steepest S.S. (~63 mV/dec.) are accomplished in BMG a-IWO NS-JLTs with HfO2 GI = 10 nm and a-IWO channel = 4 nm.

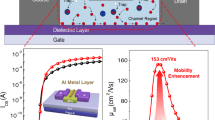

In order to enhance the ION, it is necessary to improve both of μFE and the contact resistance (RC) between S/D metal electrodes and TAOS channel. The normalized output characteristics of a-IWO NS-JLTs with (a) channel length (L) = 40 μm and (b) L = 5 μm are shown in Fig. 3. It is noted that as the thickness of HfO2 GI scaling down from 30 nm to 10 nm, the driving currents of a-IWO NS-JLTs with 10-nm-thick HfO2 GI operated at gate overdrive voltage (VGS − VTH) = 2V are enhanced more than 3 times of magnitude compared with the one with 30-nm-thick HfO2 GI. The significant enhancements in driving currents are attributable to the improvements in RC between the S/D metal electrodes and the a-IWO NS channel.

Transmission line model (TLM) measurement can be used to extract the RC of metal-semiconductor junction22. Figure 4(a) demonstrates the plot of total resistance (RTotal) versus channel length (L) (RTotal − L) at VGS − VTH = 2V. Figure 4(b) displays the results of the extracted width-normalized RC under different VGS − VTH for the a-IWO NS-JLTs with different thicknesses of HfO2 GI. The width-normalized RC in the inset of Fig. 4(b) is plotted in logarithm scale. The RC is significantly improved by elevating the vertical electric-field between the gate and the overlapped S/D electrodes via increasing VGS − VTH and scaling down the thickness of HfO2 GI, especially in VGS − VTH = 2V and HfO2 GI = 10 nm.

The extraction of RC from the plot of RTotal − L and the diagrammatic explanation of RC in relation to the gate voltage and the thickness of HfO2 GI. (a) The plot of RTotal − L at VGS − VTH = 2V; (b) the results of the extracted width-normalized RC under different VGS − VTH in a-IWO NS-JLTs with different thicknesses of HfO2 GI; (c) the schematic structure of gate-to-source overlap region; (d) the illustration of band diagram along A-A’. The RC is significantly improved by increasing VGS − VTH and scaling down the thickness of HfO2 GI, especially in VGS − VTH = 2V and HfO2 GI = 10 nm.

Figure 4(c) shows the schematic structure of the gate-to-source overlap region and Fig. 4(d) illustrates of band diagram along A-A’. As shown in Fig. 4(c), when S/D electrodes contact with a-IWO NS layer, the RC related to Schottky barrier between S/D metal electrode and a-IWO NS channel is formed. Since the potential energy of a-IWO NS channel at S/D electrodes contact can be modulated by the gate voltage, the Schottky barrier becomes narrower as the gate voltage increases, as shown in Fig. 4(d). Higher vertical electric-field enhances more electrons tunneling behavior in addition to thermionic electron injection23. The RC is decreased with increasing gate voltage and scaling down the thickness of HfO2 GI, resulting in higher ION. The electrical mechanism can be summarized that the increase of the gate voltage will decrease the Schottky barrier height and make Schottky barrier narrower, resulting in the significant reduction of the value of RC. If a positive gate voltage is applied, it will modify the Fermi level in a-IWO NS layer and make the a-IWO NS channel more conductive and resultantly decreasing channel resistance (Rch). The vertical electric-field enhanced by scaling down the thickness of HfO2 GI also reduces the RC at the metal-semiconductor interface.

It is well known that the poly-Si transistors are BEOL compatible devices for three-dimensional integrated circuits (3-D ICs) applications4,5,6. The low-temperature BEOL TAOS TFTs and poly-Si TFTs are the suitable platforms enabling monolithic 3-D integration with hybrid CMOS technologies. One of the major challenges to integrate the TAOS and poly-Si-based CMOS technologies is on their mismatched operation voltages (VDD)24. For a low and matched operation voltage, the small S.S and real ION/IOFF under small gate operation voltage are critical. Figure 5 displays transfer characteristics of a-IWO NS-JLTs with different channel lengths. The extracted VTH roll-off of a-IWO NS-JLTs with different channel lengths is also plotted in the inset of Fig. 5. As the channel length scaling down, the VTH roll-off is a key parameter to verify the gate controllability over the channel region. The a-IWO NS-JLTs with different channel lengths have almost identical S.S. ~63 mV/dec. and similar IOFF characteristics, where the ION is nearly proportional to channel length. Thus, the value of ION/IOFF larger than 1 × 109 can be obtained for the device with 5 μm channel length at an operation conditions of VGS − VTH = 3V and VDS = 0.1V. The a-IWO NS-JLTs with very small VTH roll-off exhibit high gate controllability and good SCEs immunity thanks to the combined use of 2D-like a-IWO NS channel and thinner HfO2 GI in devices.

For VS hybrid CMOS applications, the real IOFF under large drain operation voltage is the key parameter. The transfer characteristics of a-IWO NS-JLTs with W/L = 80 μm/5 μm and n-channel LC-NILC poly-Si TFTs with W/L = 40 μm/5 μm are shown in Fig. 6(a,b), respectively. In this work, the μFE of n-channel LC-NILC poly-Si TFTs is about twice as high as that of a-IWO NS-JLTs. In order to achieve electrically-matched ION, a wider channel width for the a-IWO NS-JLTs was studied. As shown in Fig. 6(a), the IOFF of a-IWO NS-JLTs with W = 80 μm operated at VDS = 0.1V and VDS = 1V, respectively, are almost identical and smaller than the measurement detection limit (~10−13A). The a-IWO NS-JLTs with near ideal S.S. can be operated at low voltage. The extremely high ION/IOFF ~ 1010 at VGS − VTH = 2.5V and VDS = 1V is accomplished in a-IWO NS-JLTs by virtue of the wide bandgap InOx-based NS channel. However, the n-channel LC-NILC poly-Si TFTs always suffer from higher gate-induced drain leakage (GIDL) currents and higher IOFF (=Imin at VDS = 1V) due to poly-Si film with small bandgap and grain boundaries, resulting in poorer ION/IOFF ~ 108 at VGS − VTH = 2.5V and VDS = 1V shown in Fig. 6(b). The a-IWO NS-JLTs with near ideal S.S., lower GIDL, and higher ION/IOFF are more suitable for low-power VS hybrid CMOS applications compared with the n-channel LC-NILC poly-Si TFTs.

The transfer characteristics of a-IWO NS-JLTs and LC-NILC poly-Si TFTs with different VDS for VS hybrid CMOS applications. (a) The transfer characteristics of a-IWO NS-JLTs with W/L = 80 μm/5 μm; (b) the transfer characteristics of n-channel LC-NILC poly-Si TFTs with W/L = 40 μm/5 μm; (c) the conceptual schematic of VS hybrid CMOS structure; (d) the transfer characteristics of a-IWO NS-JLTs and p-channel LC-NILC poly-Si TFTs. The extremely high ION/IOFF ~ 1010 at VDS = 1V and VGS − VTH = 2.5V is accomplished in a-IWO NS-JLTs by virtue of the wide bandgap InOx-based NS channel. The experimental electrical characteristics of n-channel a-IWO NS-JLTs and p-channel LC-NILC poly-Si TFTs exhibit matched electrical characteristics, low operation voltage, and low IOFF.

Figure 6(c) illustrates the conceptual schematic of VS hybrid CMOS structure and Fig. 6(d) displays the transfer characteristics of a-IWO NS-JLTs and p-channel LC-NILC poly-Si TFTs. The proposed VS hybrid CMOS structure is constructed by the high-temperature p-channel LC-NILC poly-Si TFTs underneath and top low-temperature n-channel a-IWO NS-JLTs. The match of electrical characteristics with low IOFF for a-IWO NS-JLTs and LC-NILC poly-Si TFTs is respectively observed to meet the requirement for hybrid CMOS applications. They are exhibiting low operation voltages and offer new opportunities of designing BEOL CMOS devices for LSI logic circuits.

The technology potential for low-temperature processes applications on a glass substrate had been demonstrated16. In JL devices, the path of current transport is concentrated in the center of heavy uniform doping channel, which reduces the effects at the oxide/channel interface, resulting in near ideal subthreshold characteristics6. It is well known that μFE is significantly decreasing as scaling channel thickness. The proposed 2D-like BMG a-IWO NS-JLTs with μFE ~ 25.3 cm2/V-s exhibit near ideal S.S. and improved hysteresis characteristics because of the NS channel, JL configurations, and the good interface characteristics between the HfO2 GI and the a-IWO NS channel16.

Conclusion

In summary, we have studied the influences of the different GI materials and the scalings of GI thickness, a-IWO NS channel thickness, and channel lengths on the electrical characteristics and performances of the 2D-like a-IWO NS-JLTs. Since a-IWO NS-JLTs are fabricated by using Ga-free a-IWO thin films, the material costs can be minimized compared with typically adopted a-IGZO. The Ga- and Zn-free a-IWO NS channel layers with low cost, high mobility, and good stability could be a promising alternative to a-IGZO for the advanced oxide-based TFT technology. Also, the 2D-like BMG a-IWO NS-JLTs significantly minimize the IL thickness, resulting in near ideal S.S. and improved hysteresis characteristics. The 2D-like BMG a-IWO NS-JLTs with small VTH roll-off, large ION/IOFF, near ideal S.S., high μFE, low RC, and low operation voltage appears highly promising potentials for system-on-panel (SoP) and VS hybrid CMOS applications in the future.

References

Choi, Y. K. et al. Ultrathin-body SOI MOSFET for deep-sub-tenth micron era. IEEE Electron Device Lett. 21, 254–255, https://doi.org/10.1109/55.841313 (2000).

Hisamoto, D. et al. FinFET—a self-aligned double-gate MOSFET scalable to 20 nm. IEEE Trans. Electron Devices 47, 2320–2325, https://doi.org/10.1109/16.887014 (2000).

Colinge, J. P. et al. Nanowire transistors without junctions. Nature Nanotechnol. 5, 225–229, https://doi.org/10.1038/nnano.2010.15 (2010).

Chen, H. B. et al. Performance of GAA poly-Si nanosheet (2 nm) channel of junctionless transistors with ideal subthreshold slope, In VLSI Symp. Tech. Dig. T232–T233 (2013).

Kuo, P. Y., Lu, Y. H. & Chao, T. S. High-performance GAA sidewall-damascened sub-10-nm in situ n+-doped poly-Si NWs channels junctionless FETs. IEEE Trans. Electron Devices 61, 3821–3826, https://doi.org/10.1109/TED.2014.2354436 (2014).

Kuo, P. Y., Lin, J. Y., Chao, T. S. Implantation free GAA double spacer poly-Si nanowires channel junctionless FETs with sub-1V gate operation and near ideal subthreshold swing, In Proc. IEEE Int. Electron Devices Meeting 133–136, https://doi.org/10.1109/IEDM.2015.7409639 (2015).

Chen, M. C. et al. TMD FinFET with 4 nm thin body and back gate control for future low power technology, In Proc. IEEE Int. Electron Devices Meeting 831–834, https://doi.org/10.1109/IEDM.2015.7409813 (2015).

Liu, W. et al. Role of metal contacts in designing high-performance monolayer n-type WSe2 field effect transistors. Nano Lett. 13, 1983–1990, https://doi.org/10.1021/nl304777e (2013).

Nomura, K. et al. Room-temperature fabrication of transparent flexible thin-film transistor using amorphous oxide semiconductors. Nature 432, 488–492, https://doi.org/10.1038/nature03090 (2004).

Kobayashi, Y. et al. Effect of surrounded-channel structure on electrical characteristics of c-axis aligned crystalline In–Ga–Zn–O field-effect transistor. IEEE Electron Device Lett. 36, 309–311, https://doi.org/10.1109/LED.2015.2399911 (2015).

Matsubayashi, D. et al. 20-nm-node trench-gate- self-aligned crystalline In-Ga-Zn-Oxide FET with high frequency and low off-state current, In Proc. IEEE Int. Electron Devices Meeting, 141–144, https://doi.org/10.1109/IEDM.2015.7409641 (2015).

Wu, S. H. et al. Performance boost of crystalline In-Ga-Zn-O material and transistor with extremely low leakage for IoT normally-off CPU application, In VLSI Symp. Tech. Dig. T166–T167, https://doi.org/10.23919/VLSIT.2017.7998144 (2017).

Aikawa, S. et al. Thin-film transistors fabricated by low-temperature process based on Ga- and Zn-free amorphous oxide semiconductor. Appl. Phys. Lett. 102, 102101, https://doi.org/10.1063/1.4794903 (2013).

Aikawa, S., Nabatame, T. & Tsukagoshi, K. Effects of dopants in InOx-based amorphous oxide semiconductors for thin-film transistor applications. Appl. Phys. Lett. 103, 172105, https://doi.org/10.1063/1.4822175 (2013).

Kizu, T. et al. Low-temperature processable amorphous In-W-O thin-film transistors with high mobility and stability. Appl. Phys. Lett. 104, 152103, https://doi.org/10.1063/1.4871511 (2014).

Kuo, P. Y., Chang, C. M. & Liu, P. T. Low thermal budget amorphous indium tungsten oxide nano-sheet junctionless transistors with near ideal subthreshold swing, In VLSI Symp. Tech. Dig. 21–22, https://doi.org/10.1109/VLSIT.2018.8510684 (2018).

Lin, H. C., Yeh, K. L., Huang, T. Y., Huang, R. G. & Sze, S. M. Ambipolar Schottky-barrier TFTs. IEEE Trans. Electron Devices 49, 3264–270, https://doi.org/10.1109/16.981216 (2002).

Jin, G. et al. Simple fabrication of a three-dimensional CMOS inverter using p-type poly-Si and n-type amorphous Ga–In–Zn–O thin-film transistors. IEEE Electron Device Lett. 32, 1236–1238, https://doi.org/10.1109/LED.2011.2161258 (2011).

Chen, C. D. et al. Integrating poly-silicon and InGaZnO thin-film transistors for CMOS inverters. IEEE Trans. Electron Devices 64, 3668–3671, https://doi.org/10.1109/TED.2017.2731205 (2017).

Kuo, P.-Y., Wang, J.-L., Li, Z.-H. & Liu, P.-T. Symmetric Ni-induced lateral crystallization Poly-Si TFTs with low metal contaminations, In Proc. 2018 International Conference on Solid State Devices and Materials, 791–792 (2018).

Lin, J. Y., Kuo, P. Y., Lin, K. L., Chin, C. C. & Chao, T. S. Junctionless poly-Si nanowire transistors with low-temperature trimming process for monolithic 3-D IC application. IEEE Trans. Electron Devices 63, 4998–5003, https://doi.org/10.1109/TED.2016.2615805 (2016).

Reeves, G. K. & Harrison, H. B. Obtaining the Specific contact resistance from transmission line model measurements. IEEE Electron Device Lett. 3, 111–113, https://doi.org/10.1109/EDL.1982.25502 (1982).

Wang, W. et al. Analysis of the contact resistance in amorphous InGaZnO thin film transistors. Appl. Phys. Lett. 107, 063504, https://doi.org/10.1063/1.4928626 (2015).

Chi, L. J., Yu, M. J., Chang, Y. H. & Hou, T. H. 1-V full-swing depletion-load a-In–Ga–Zn–O inverters for back-end-of-line compatible 3D integration. IEEE Electron Device Lett. 37, 441–444, https://doi.org/10.1109/LED.2016.2535124 (2016).

Acknowledgements

The authors would like to thank the Nano Facility Center of National Chiao Tung University (NCTU) and Taiwan Semiconductor Research Institute (TSRI) for the processes support. This work was supported by the Ministry of Science and Technology, Taiwan, under Contract: MOST 106-2221-E-009-107-MY3 and Applied Materials Taiwan, under Contract: 107C061.

Author information

Authors and Affiliations

Contributions

P.Y. Kuo designed experiments and directed the research direction including experimental and theoretical investigations for the devices. C.M. Chang and I.H. Liu fabricated the devices and measured the electrical characteristics of devices. P.Y. Kuo and P.T. Liu wrote the main manuscript text. P.T. Liu supervised all experiments.

Corresponding author

Ethics declarations

Competing Interests

The authors declare no competing interests.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Kuo, PY., Chang, CM., Liu, IH. et al. Two-Dimensional-Like Amorphous Indium Tungsten Oxide Nano-Sheet Junctionless Transistors with Low Operation Voltage. Sci Rep 9, 7579 (2019). https://doi.org/10.1038/s41598-019-44131-4

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-019-44131-4

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.