Abstract

Pt/LiCoO2/SiO2/Si stacks with different SiO2 thicknesses are fabricated and the influence of SiO2 on memristive behavior is investigated. It is demonstrated that SiO2 can serve as Li ion trapping layer benefiting device retention, and the thickness of SiO2 must be controlled to avoid large SET voltage and state instability. Simulation model based on Nernst potential and diffusion potential is postulated for electromotive force in LiCoO2 based memristors. The simulation results show that SiO2 trapping layer decreases the total electromotive field of device and thereby prevents Li ions from migrating back to LiCoO2. This model shows a good agreement with experimental data and reveals the Li ion trapping mechanism of SiO2 in LiCoO2 based memristors.

Similar content being viewed by others

Introduction

Boasting high memory density and energy efficiency, memristors are promising alternatives to complementary metal oxide semiconductors (CMOS) for high-density storage and high-performance computing1,2,3. Neural networks based on crossbar arrays of filamentary memristors or phase change memories have been reported and successfully implemented in image recognition and word classification4,5,6,7,8,9. Despite significant progresses, these devices still suffer from several limitations such as excessive “write” noise as well as high switching voltages and currents10,11,12. LiCoO2 based memristors are expected to overcome several limitations. A major advantage of LiCoO2 based memristors is that the intercalation and extraction of Li ions in LiCoO2 are highly reversible leading to high device stability13,14. Moreover, Li ions migration in LiCoO2 based memristors is similar to information exchange processes between synapses and neurons in the brain15. With a low energy barrier for Li ions transporting, LiCoO2 based memristors have a smaller threshold voltage and are expected to satisfy low-power consumption requirement in high performance computing16,17.

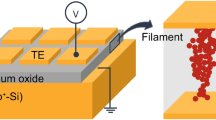

Generally, LiCoO2 based memristors operate by a common electrochemical reaction between LiCoO2 and Si18,19. The conductivity of LiCoO2 changes as a function of Li ions concentration20,21. Under a positive electrical field, Li ions migrate from LiCoO2 to Si and the variation of Li ions concentration in LiCoO2 produces a resistive switching (RS) behavior. The RS processes corresponding to Li ions migration out of Li-based oxide have been experimentally verified22,23. Furthermore, the electrochemical reaction between LiCoO2 and Si produces an electromotive force (EMF) which in LiCoO2 based memristors can cause electrical short circuit between LixCoO2 and LixSi decreasing device retention24. It has been reported that SiO2 between LiCoO2 and Si can work as solid state electrolyte allowing transport of Li ions and trap Li ions when external voltage is removed thus increasing device retention23,24. SiO2 has been also reported to be a promising candidate for the electrolyte or controllable barrier layer in CMOS and Li-ion batteries, which can be used to modulate the Li ions transporting23,24,25,26,27. However, the influence of SiO2 on memristive behavior in LiCoO2 based memristors has not been investigated and the Li ion trapping mechanism of SiO2 in LiCoO2 based memristors remains to be revealed.

In this work, Pt/LiCoO2/SiO2/Si stacks with different SiO2 thicknesses are produced and the corresponding memristive properties such as electrical properties, stabilities and retentions are investigated. SiO2 serves as a trapping layer for Li ions and is favorable for device retention. It is also necessary to control the SiO2 thickness to an appropriate range for higher durability and state stability. A simulation model for EMF in LiCoO2 based memristors is proposed to explain the influence of SiO2 on Pt/LiCoO2/SiO2/Si stacks. The origins of EMF include Nernst potential and diffusion potential. Thus, this model is based on Nernst potential and diffusion potential and the total electromotive fields of device are calculated. It can be seen that SiO2 trapping layer can decrease electromotive field of Pt/LiCoO2/SiO2/Si stacks. This model is consistent with the experimental results and reveals the Li ion trapping mechanism of SiO2 in LiCoO2 based memristors.

Methods

The 40 nm LiCoO2 films were deposited on highly doped p-type Si (111) or SiO2/Si substrates by pulse laser disposition (PLD) using a stoichiometric LiCoO2 target. LiCoO2 layer was fabricated in O2 (10 Pa) atmosphere at 550 °C to obtain R-3m LiCoO2 phase through a KrF laser (LightMachinery IPEX-800, λ = 248 nm and τ = 25 ns) operated at 3 Hz with a fluence of ≈1.3 J cm−2. SiO2 layers were formed by thermal oxidization in an oxygen environment at 900 °C. The thickness of SiO2 layer was determined by profilometry. The SiO2 layers had thicknesses of 10 nm, 20 nm and 40 nm (\({d}_{Si{O}_{2}}:\,{d}_{LiCo{O}_{2}}=1:\,4,\,1:\,2,\,1:\,1\)) in order to investigate the influence of the SiO2 thickness on the memristive behavior of Pt/LiCoO2/SiO2/Si stacks. The LiCoO2 deposition was carried out under same conditions to obtain same Li ions concentration and layer thickness. To avoid introducing other metal ion such as Ag+ or Cu2+, noble Pt was used as the top electrodes. The 80 nm thick Pt top electrodes were prepared by magnetron sputtering in pure Ar with a metal mask covering the LiCoO2 layer. The diameter of the top electrode was 1 mm.

The electrical and memristive properties were measured by the voltage sweeping mode on Keithley 4200-SCS semiconductor parameter analyzer at room temperature. The voltages were applied to the Pt top electrode with Si substrate grounded. The cycle tests were collected continually by the direct-current (DC) voltage sweeping mode. The retention tests were conducted after the devices switching to LRS, and the read voltage is 0.1 V. The LiCoO2 layers were analyzed with a LabX XRD-6000 using Cu Kα radiation and operating at 40 kV and 30 mA. The scanning rate was 5°/min.

Results

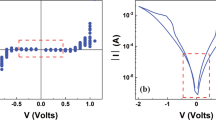

The Pt/LiCoO2/SiO2/Si stacks with different SiO2 thicknesses of 10 nm, 20 nm and 40 nm are fabricated and samples without SiO2 are also prepared for comparison. The corresponding I-V curves of different samples are shown in Fig. 1. The I-V curve of sample (a) displays gradual RS processes without definite Vset and Vreset, corresponding to homogeneous RS in LiCoO224. On the contrary, samples (b), (c) and (d) exhibit abrupt current increases similar to RS behavior of electrochemical metallization (ECM)10, as shown in Fig. 1(b–d) (More I-V curves during cycle tests are shown in supporting information, Fig. S3). Hence, samples with and without SiO2 characterize different memristive properties which may be attributed to different transport processes of Li ions in SiO2 and LiCoO2.

In order to investigate the device stabilities, durability tests are conducted on the different samples. As shown in Fig. 2, the VSET and VRESET of samples with 20 nm are more stable. To evaluate the dispersion degree, corresponding coefficients of variation (CV) are calculated. CV is defined by28

where σ is the standard deviation and μ is the average of several data. The ranges of SET voltage and CV of different samples are summarized in Table 1 (For each SiO2 thickness, 15 points of the sample are measured). Samples with 20 nm show smaller CV than other samples consistent with Fig. 2. To study state stability, the resistances of different samples at HRS and LRS for 128 cycles are also measured. Figure 3 plots the RHRS and RLRS of different samples during 128 cycles. The RHRS of samples (a) and (b) show two orders of magnitude fluctuations while those of samples (c) and (d) are within one order of magnitude. The RLRS of sample (c) shows the smallest fluctuation. The CV of RHRS and RLRS are also calculated in Table 2 (For each SiO2 thickness, 15 points of the sample are measured). As the SiO2 thickness is increased, CV of RHRS decreases and sample (c) has the smallest CV of RLRS. However, sample (d) shows several RS failures during the durability test. Hence, samples with 20 nm SiO2 characterize the best stability. SiO2 with appropriate thickness is favorable for state stability but SiO2 that is too thick decreases the state stability.

Retention of Pt/LiCoO2/SiO2/Si stacks with different SiO2 thicknesses is also assessed at a read voltage of 0.1 V to evaluate ability of data storage. Figure 4 shows that Pt/LiCoO2/SiO2/Si stacks without SiO2 maintain retention characteristic of ~103 s whereas samples with SiO2 show good retention characteristics up to 105 s. As SiO2 thickness is increased, device retention increases from 104 to 105 s. In terms of Pt/LiCoO2/SiO2/Si stacks, EMF mainly drives Li ions from Si to LiCoO2 without an external voltage and therefore, SiO2 can decrease the influence of EMF on Pt/LiCoO2/SiO2/Si stacks leading to high retention.

Discussion

To understand the mechanism of trapping of Li ions in SiO2, it is necessary to investigate the Li ions transporting processes in the Pt/LiCoO2/SiO2/Si stacks. The schematic of Pt/LiCoO2/SiO2/Si stacks and Li ions transporting processes are shown in Fig. 5(a). The Li ions transporting processes in LiCoO2, SiO2 and Si have been experimentally verified and reported for Li-ion battery22,24,25,26. The electrochemical reactions involving Li ions in Pt/LiCoO2/SiO2/Si stacks are as follows:

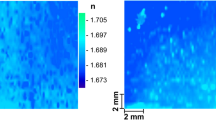

At a positive voltage, Li ions are extracted from LiCoO2 and migrate in the interval positions of SiO2 finally forming LixSi in Si substrate. The LiCoO2 acts as Li ions source and RS layer, SiO2 allows Li ions transportation, and Si is used to store Li ions. The LiCoO2 layers are annealed at 550 °C to obtain R-3m phase (seen in Fig. S1) which is hexagonal layered structure with a uniform Li ions distribution19,20. Owing to the uniform Li ions distribution in crystalline R-3m LiCoO2, the RS processes occur in the entire LiCoO2 layer displaying gradual current changes. In contrast to layered structure LiCoO2, SiO2 is amorphous with non-uniformity, and the Li ions intercalation processes are inhomogeneous and occur in some partial regions of SiO2. Therefore, the memristive behavior of samples without SiO2 shows gradual current changes while samples with SiO2 exhibit abrupt resistance jumps. Furthermore, it has been reported in Li-ion batteries that insertion of Li ions in Si strongly strains the crystalline lattice thus harming the device stability, the SiO2 can work as a buffer layer to decrease the crystalline lattice stress22,29 and trap Li ions decreasing resistance degradation without an external voltage23,24. However, thin SiO2 layer (≤10 nm) is generally rough exhibiting non-uniformity27, which may be adverse to device stability as shown in Fig. 3(b). And too thick SiO2, such as 40 nm, exhibit stronger Li ion trap effect which can cause several set failures and reduced performances, as shown in Fig. 3(d). Hence, SiO2 with the appropriate thickness improves the device stability.

After applying a positive voltage, Li ions transport from LiCoO2 to Si resulting in EMF between LiCoO2/SiO2 interface (\(s^{\prime} \)) and SiO2/Si interface (\(s^{\prime\prime} \)). Two factors mainly contribute to the EMF: (a) Nernst potential VN and (b) diffusion potential Vd30. SiO2 works as a Li ion trapping layer allowing Li ions to transport at a positive voltage while trapping Li ions and avoiding resistance degradation without an external voltage. According to the different SiO2 thickness (d2), two origins of EMF in Pt/LiCoO2/SiO2/Si stacks are shown in Fig. 5(b) and (c). When d2 ≤ Critical poin (D), SiO2 undergoes fully lithiation and exhibits homogeneous Li ions distribution, as shown in Fig. 5(b), and VEMF = VN. When d2 > D, the SiO2 acts as a RS layer and has an inhomogeneous Li ions distribution as shown in Fig. 5(c), VEMF = VN + Vd. Therefore, the influence of SiO2 trapping layer on EMF can be divided into two regions. According to the range of x1 in \({{\rm{Li}}}_{{{\rm{x}}}_{1}}{{\rm{CoO}}}_{2}\) and x2 in \({{\rm{Li}}}_{{{\rm{x}}}_{2}}{{\rm{SiO}}}_{2}\), the range of D between region I and region II can be calculated to be \(6.96\,{\rm{nm}} < {\rm{D}} < 13.91\,\mathrm{nm}\,\)(Calculation processes are shown in Supplementary Information). Figure 6(a) shows different tendencies in 0~10 nm region and 10~40 nm region. When \(0\,\mathrm{nm} < {{\rm{d}}}_{2}\le 10\,\mathrm{nm}\), the device retention rises rapidly with increasing SiO2 thickness and when \(10\,\mathrm{nm} < {{\rm{d}}}_{2}\le 40\,\mathrm{nm}\), device retention rises slightly with increasing SiO2 thickness, indicating that D is near to 10 nm which is consistent with the calculation. This can also explain the abnormal tendency of HRS in Figs. 1 and 3. The HRS of devices mainly consist of \({{\rm{R}}}_{{{\rm{Li}}}_{{\rm{x}}}{{\rm{CoO}}}_{2}}\) and \({{\rm{R}}}_{{{\rm{Li}}}_{{\rm{y}}}{{\rm{SiO}}}_{2}}\). For samples without SiO2, Li ions transport back to LiCoO2 after reset process and \({{\rm{R}}}_{{\rm{HRS}}}\approx {{\rm{R}}}_{{{\rm{LiCoO}}}_{2}}\). For samples with SiO2, the SiO2 would trap large amount of Li ions during reset process resulting in decrease of Li ion concentration in LiCoO2 and the retained Li ions in SiO2 enhance the conductivity. Therefore, the HRS of Pt/LiCoO2/SiO2 (10 nm)/Si is lower than Pt/LiCoO2/Si. Moreover, 10 nm SiO2 undergoes full lithiation while 20 nm and 40 nm SiO2 undergo partly lithiation. Full lithiated SiO2 would retain higher Li ion concentration and cause lower Li ion concentration in LiCoO2 and higher conductivity. Furthermore, thicker SiO2 means larger Li ion storage and stronger Li ion trap effect leading to lower Li ion concentration in LiCoO2, which may cause that the HRS of samples with 40 nm SiO2 is lower than that of samples with 20 nm SiO2.

(a) Experimental device retention as a function of SiO2 thickness (2 different regions are observed); (b) Simulated E-d2 characteristics in Pt/LiCoO2/SiO2/Si stacks without an external voltage (d2 ≤ 10 nm); (c) Simulated E-d2 characteristic in Pt/LiCoO2/SiO2/Si stacks without an external voltage (10 nm < d2 ≤ 40 nm)

The device retention is mainly relative to the electromotive field (E = VEMF/d2), thus the E-d2 characteristics are discussed. In region I, SiO2 behaves as solid-state electrolyte exhibiting a homogeneous Li ions distribution and VEMF = VN. EMF drives Li ions migration from LixSi to LixCoO2 and the main electrochemical reactions are as follows:

The Nernst potential is given by30:

\({V}^{0}\) is the difference in the standard potentials of these reactions, k is Boltzmann constant, T is temperature, e is electron charge, \({a}_{{M}^{z+}}\) denote the activity of the cations (a = γc, γ is activity coefficient). The amount of Li ions in Pt/LiCoO2/SiO2/Si stacks is constant:

where c0 denotes the initial concentration of Li ions in LiCoO2, c1, c2 and c3 are the concentration of Li ions in LixCoO2, SiO2 and Si, S is the cell size. d1, d2 and d3 are the thicknesses of LiCoO2, SiO2 and Si, respectively. The concentration of Li ions can be defined as \(\,c=\frac{\frac{\rho V}{M}}{V}=\frac{\rho }{M}\) (\(\rho \) is mass density, V is volume and M is the molar mass). Equation (8) can be written by:

where ρ1, ρ2 and ρ3 are mass densities of LiCoO2, SiO2 and Si, respective. M1, M2 and M3 are molar mass of LiCoO2, SiO2 and Si, respectively. x1, x2 and x3 are the atomic percent in \(L{i}_{{x}_{1}}Co{O}_{2}\), \(L{i}_{{x}_{2}}Si{O}_{2}\) and \(L{i}_{{x}_{3}}Si\). Due to low concentration of Li ions in LiCoO2 and SiO2 and small molar mass of lithium, the influences of Li ions on \(\rho \,and\,M\) are neglected. Thus, \({c}_{C{o}^{4+}}=\frac{{\rho }_{1}}{{M}_{1}}(1-{x}_{1})\), \({c}_{C{o}^{3+}}=\frac{{\rho }_{1}}{{M}_{1}}{x}_{1}\), \({c}_{L{i}^{+}}=\frac{{\rho }_{2}}{{M}_{2}}{x}_{2}\), \({c}_{Li}=\frac{{\rho }_{3}}{{M}_{3}}{x}_{3}\). Based on Equation (9) and γ assumed to be one, the electromotive field in region I (E1 = VEMF/d2) can be calculated by:

To facilitate the discussion of EMF, reference values are chosen according to previous reports, \({x}_{1}=0.7\), \({\rho }_{1}=2.5\,g/c{m}^{3}\), \({\rho }_{2}=2.648\,g/c{m}^{3}\), \({\rho }_{3}=2.329\,g/c{m}^{3}\), \({M}_{1}=97.87\,g/mol\), \({M}_{2}=60.086\,g/mol\),\(\,{M}_{3}=28.085\,g/mol\), \({V}^{0}=3.6\,V\), \({x}_{2}=2/3\)13,21,31,32. The thickness of different layers are measured, \({d}_{1}=40\,nm\), \({d}_{3}=550\,{\rm{\mu }}m\). D is simulated to be 10.43 nm, and the simulated E-d2 characteristics are shown in Fig. 6(b). E1 decreases rapidly with d2, and thereby device retention rises rapidly with increasing SiO2 thickness.

In region II, SiO2 acts as a RS layer and VEMF = VN + Vd. The main electrochemical reactions are as follows:

Nernst potential is given by30

Similarly, the amount of Li ions in Pt/LiCoO2/SiO2/Si stacks is constant:

It can be also written as:

The Li ions distribution in SiO2 is inhomogeneous, to simply the Li ions distribution in SiO2, it is assumed that Li ions in SiO2 follows constant-total-dopant diffusion and the Li ions distribution in SiO2 can be defined by33:

where Q is dopant number of average area, D′ is the diffusion coefficient, t is the diffusion time and y is the depth. Assuming diffusion length is equal to SiO2 thickness \((L=\sqrt{{D}^{\text{'}}{t}_{1}}={d}_{2})\), the total dopant is the amount of Li ions extracted from LiCoO2, thus \(Q=(1-{x}_{1})\,\frac{{\rho }_{1}}{{M}_{1}}{d}_{1}\). Herein, \({c}_{C{o}^{3+}}=\frac{{\rho }_{1}}{{M}_{1}}{x}_{1}\), \({c}_{C{o}^{4+}}=\frac{{\rho }_{1}}{{M}_{1}}(1-{x}_{1})\), \({c}_{S{i}^{3+}}={c}_{L{i}^{+}}\,=\) \(c({d}_{2},{t}_{1})=\frac{(1-{x}_{1})\,\frac{{\rho }_{1}}{{M}_{1}}{d}_{1}}{\sqrt{\pi }{d}_{2}}\exp (\,-\,\frac{1}{4})\), \({c}_{S{i}^{4+}}=\frac{{\rho }_{2}}{{M}_{2}}-{c}_{S{i}^{3+}}\). Based on Equations (15, 16) and assuming γ = 1, the electromotive field (EN) originating from Nernst potential can be calculated by:

In region II, Vd should be also taken in account. The diffusion potential formula is given by30:

where \(\bar{t}\) is ion transference number averaged throughout layer thickness, \({a}_{{s}^{\text{'}}}\) is the activity of Li ions at LiCoO2/SiO2 interface and \({a}_{{s}^{\text{'}}}\) is the activity of Li ions at SiO2/Si interface. According to Equation (16), \({c}_{{s}^{\text{'}}}=c(0,{t}_{1})\) and \({c}_{{s}^{\text{'}\text{'}}}=c({d}_{2},{t}_{1})\). The remaining reference values are \(\bar{t}=0.4\), \(T=298\,K\)30. Assuming γ = 1, the diffusion potential (\({V}_{d}\)) is calculated to be −2.5 × 10−3 V, which is much less than VN, meaning that Vd can be neglected. Thus VEMF ≈ VN, reference values are \({x}_{1}=0.7\), \({\rho }_{1}=2.5\,g/c{m}^{3}\), \({\rho }_{2}=2.648\,g/c{m}^{3}\), \({M}_{1}=97.87\,g/mol\), \({M}_{2}=60.086\,g/mol\), \({V}^{0}=1.4\,V\)13,21,31. The simulated E2-d2 characteristics are presented in Fig. 6(c), \({E}_{2}\) decreases with increasing of the SiO2 thickness. Thus, SiO2 works as a Li ion trapping layer. When external voltage is removed, the SiO2 trapping layer decreases the total electromotive field of device and maintains the states resistances.

With external voltage, Li ions transport from LiCoO2 to SiO2 and Si layers, which can produce a VEMF and exhibit a nanobattery-like behavior. The phenomenon is similar to the observation reported in other redox-based memristors23,24,34,35. It has also been demonstrated that VEMF is dependent on the chemistry and the transport properties of the materials system30,36,37. Thus, Li ion trapping mechanism, especially the relationship between electromotive field and SiO2 thickness in different regions, may be also adapted to other devices based on LiCoO2 and SiO2 material system such as Li-ion batteries and Li-ion based transistors. The critical point is actually relative to thickness and Li ion concentration of LiCoO2 layer, may change with fabrication parameters of devices.

Conclusion

The influence of SiO2 trapping layer on memristive behavior of Pt/LiCoO2/SiO2/Si stacks is investigated in terms of electrical properties, device stability and retention. For the LiCoO2 based memristors, the trapping layer benefits device retention. It is necessary to control the thickness of trapping layer to improve device properties. A model based on Nernst potential and diffusion potential is proposed to elucidate the Li ion trapping mechanism in SiO2 and two different relationships between the electromotive field and SiO2 thickness are found. According to this model, SiO2 trapping layer decreases the total electromotive field of device and hence prevents Li ions from migrating back to LiCoO2. These findings reveal the Li ion trapping mechanism of SiO2 in LiCoO2 based memristors and provide insights into the performance improvement of memristors and other devices based on LiCoO2 and SiO2.

Data Availability

The datasets generated and analysed during the current study are available from the corresponding author.

References

Strukov, D. B., Snider, G. S., Stewart, D. R. & Williams, R. S. The missing memristor found. Nature. 80, 453 (2008).

Agarwal, S. et al. Energy scaling advantages of resistive memory crossbar based computation and its application to sparse coding. Front. Neurosci. 9, 484 (2015).

Zhang, X. J., Huang, A. P., Hu, Q., Xiao, Z. S. & Chu, P. K. Neuromorphic computing with memristor crossbar. Phys. Status Solidi A. 1700875 (2018).

Tuma, T., Pantazi, A., Gallo, M. L., Sebastian, A. & Eleftheriou, E. Stochastic phase-change neurons. Nat. Nanotech. 11, 693 (2016).

Burr, G. W. et al. Experimental demonstration and tolerancing of a large-scale neural network (165000 synapses) using phase-change memory as the synaptic weight element. IEEE Trans. Electron Devices. 62, 3498–3507 (2015).

Prezioso, M. et al. Training and operation of an integrated neuromorphic network based on metal-oxide memristors. Nature. 521, 61–64 (2015).

Guo, X. et al. Modeling and experimental demonstration of a hopfield network analog-to-digital converter with hybrid CMOS/memristor circuits. Front. Neurosci. 9, 488 (2015).

Sheridan, P. M. et al. Sparse coding with memristor networks. Nat. Nanotech. 12, 784 (2017).

Yao, P. et al. Face classification using electronic synapses. Nat. Commun. 8, 15199 (2017).

Yang, J. J., Strukov, D. B. & Stewart, D. R. Memristive devices for computing. Nat. Nanotech. 8, 13–24 (2013).

Terai, M., Sakotsubo, Y., Kotsuji, S. & Hada, H. Resistance controllability of Ta2O5/TiO2 stack ReRAM for low-voltage and multilevel operation. IEEE Electron Device Lett. 31, 204–206 (2010).

Burr, G. W. et al. Neuromorphic computing using non-volatile memory. Adv. Phys. X. 2, 89–124 (2017).

Milewska, A. et al. The nature of the nonmetal–metal transition in LixCoO2 oxide. Solid State Ionics. 263, 110–118 (2014).

Huggins, R. A. Advanced Batteries: Materials Science Aspects. (Springer, 2009)

Greenlee, J. D., Petersburg, C. F., Daly, W. G., Alamgir, F. M. & Doolittle, W. A. In situ investigation of the channel conductance of a Li1−xCoO2, (0 < x <0.5) ionic-electronic transistor. Appl. Phys. Lett. 102, 213502 (2013).

Danilov, D., Niessen, R. A. H. & Notten, P. H. L. Modeling all-solid-state Li-ion batteries. J. Electrochem. Soc. 158, A215–A222 (2011).

Fuller, E. J. et al. Li-ion synaptic transistor for low power analog computing. Adv. Mater. 29, 1604310 (2017).

Moradpour, A. et al. Resistive switching phenomena in LixCoO2 thin films. Adv. Mater. 23, 4141–4145 (2011).

Svoukis, E. et al. Data storage applications based on LiCoO2 thin films grown on Al2O3 and Si substrates. Appl. Surf. Sci. 381, 22–27 (2016).

Ménétrier, M. et al. The insulator-metal transition upon lithium deintercalation from LiCoO2: electronic properties and 7Li NMR study. J. Mater. Chem. 9, 1135–1140 (1999).

Marianetti, C. A., Kotliar, G. & Ceder, G. A first-order Mott transition in Lix CoO2. Nat. Mater. 3, 627 (2004).

Zhang, Y., Li, Y., Wang, Z. & Zhao, K. Lithiation of SiO2 in Li-ion batteries: in situ transmission electron microscopy experiments and theoretical studies. Nano Lett. 14, 7161 (2014).

Nguyen, V. S. et al. Direct Evidence of Lithium Ion Migration in Resistive Switching of Lithium Cobalt Oxide Nanobatteries. Small. 14, 1801038 (2018).

Mai, V. H. et al. Memristive and neuromorphic behavior in a LixCoO2 nanobattery. Sci. Rep. 5, 7761 (2015).

Ostadhossein, A., Kim, S. Y., Cubuk, E. D., Qi, Y. & van Duin, A. C. Atomic insight into the lithium storage and diffusion mechanism of SiO2/Al2O3 electrodes of Li-ion batteries: ReaxFF reactive force field modeling. J. Phys. Chem. A. 120, 2114 (2016).

Sim, S., Oh, P., Park, S. & Cho, J. Critical thickness of SiO2 coating layer on core@shell bulk@nanowire Si anode materials for Li-ion batteries. Adv. Mater. 25, 4498–4503 (2013).

Ariel, N., Ceder, G., Sadoway, D. R. & Fitzgerald, E. A. Electrochemically controlled transport of lithium through ultrathin SiO2. J. Appl. Phys. 98, 3344 (2005).

Abdi, H. Coefficient of variation. Encyclopedia of research design. 1, 169–171 (2010).

Yan, N. et al. Hollow porous SiO2 nanocubes towards high-performance anodes for lithium-ion batteries. Sci. Rep. 3, 1568 (2013).

Valov, I. et al. Nanobatteries in redox-based resistive switches require extension of memristor theory. Nat. Commun. 4, 1771 (2013).

Milazzo, G., Caroli, S. & Sharma, V. K. Tables of standard electrode potentials. (New York: Wiley. 1978).

Ban, C. et al. Lithiation of silica through partial reduction. Appl. Phys. Lett. 100, 243905 (2012).

Crank, J. The Mathematics of Diffusion. (Oxford University Press, 1980).

Van den Hurk, J. et al. Physical origins and suppression of Ag dissolution in GeSx-based ECM cells. Phys. Chem. Chem. 16, 18217–18225 (2014).

Tappertzhofen, S. et al. Nanobattery Effect in RRAMs—Implications on Device Stability and Endurance. IEEE Electron Device Lett. 35, 208–210 (2014).

Valov, I. Redox-Based Resistive Switching Memories (ReRAMs): Electrochemical Systems at the Atomic Scale. Chem. Electro. Chem. 1, 26–36 (2014).

Valov, I. & Lu, W. D. Nanoscale electrochemistry using dielectric thin films as solid electrolytes. Nanoscale 8, 13828–13837 (2016).

Acknowledgements

This research was supported by the National Natural Science Foundation of China (Grant Nos 51872010, 11574017, 11574021 and 11604007), Special Foundation of Beijing Municipal Science & Technology Commission (Grant No. Z161100000216149), and City University of Hong Kong Strategic Research Grant (SRG) No. 7004644.

Author information

Authors and Affiliations

Contributions

Q.H. and R.M.L. contributed equally to this work. Q.H. and R.M.L. fabricated the devices, performed electrical measurement and film characterizations; R.M.L., Q.H., X.J.Z. and A.P.H. proposed the simulation model; All authors (including Q.G., M.W., H.L.S., Z.S.X.) discussed the results; Q.H. and R.M.L. wrote the main manuscript text and prepared figures and tables with the help of P.K.C. and A.P.H.; All authors reviewed the manuscript.

Corresponding author

Ethics declarations

Competing Interests

The authors declare no competing interests.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Hu, Q., Li, R., Zhang, X. et al. Lithium ion trapping mechanism of SiO2 in LiCoO2 based memristors. Sci Rep 9, 5081 (2019). https://doi.org/10.1038/s41598-019-41508-3

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-019-41508-3

This article is cited by

-

Artificial synapses with a sponge-like double-layer porous oxide memristor

NPG Asia Materials (2021)

-

Evidence of Biorealistic Synaptic Behavior in Diffusive Li-based Two-terminal Resistive Switching Devices

Scientific Reports (2020)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.