# SCIENTIFIC REPORTS

Received: 20 September 2018 Accepted: 8 February 2019 Published online: 06 March 2019

## **OPEN** A Novel Graphene Metal Semi-Insulator Semiconductor Transistor and Its New Super-Low Power Mechanism

Ping Li, R. Z. Zeng, Y. B. Liao, Q. W. Zhang & J. H. Zhou

The state-of-art Si Matel-Oxide-Semiconductor Field-Effect-Transistor (MOS-FET) meets the problem of the Power Consumption (P<sub>c</sub>) can not be effecively deceased quided by the Moore's Law as before. The GFET has the problem of the device can not be effectively turned off, since the band-gap of the graphene is zero. To solve these problems, noticing the amount of the carriers in the 2 dementional semiconductor material is limited, we propose a Matel-Semi-Insulator-Semiconductor Field-Effect-Transistor (MSIS-FET) to replace the traditional MOS-FET. We verify our idea by fabricating the graphene MSIS-FETs using the natural Aluminium-oxide (Al-oxide) as the semi-insulator gate dielectric. From MSIS-FETs fabricated, we obtain following experimental results. The graphene MSIS-FET is turned off very well, a recorded high Ids on/off ratio of 5 imes 10<sup>7</sup> is achieved. A saddle and close-loop shape transfer feature of Ids-Vgs is obtained first time for transistors. A non-volatile memory characteristics is observed. A carrier re-injection principle and a super-Low P<sub>c</sub> mechanism for semiconductor devices and integrated circuits (ICs) are found from the transfer feature of the graphene MSIS-FET. It is shown that the  $P_c$  of the semiconductor devices and (ICs) can be reduced by over three orders of magnitude by using this new mechanism.

Since the silicon (Si) MOS-FET was born, the fuction of the device gate was to induce the carriers (electrons or holes) in the semiconductor channel by applying an electric field to the channel through the gate dielcetric which was an insulator<sup>1</sup>. The operating principle of the Graphene-Field-Effect-Transistor (GFET) was similar to that of the Si MOS-FET, the gate dielcetric was still a insulator<sup>2,3</sup>. The present information technology based on the MOS-FET faces two problems which looks uncorrelated. The one is the Power Consumption  $(P_C)$  of the Integrated Circuit (IC) is becoming a big problem, along with the information technology enters the cloud calculation and big date era, resulted from that, with the channel length or feature size of the MOS-FET scaling down, the  $P_C$  can only be reduced linearly changed from previous squarely<sup>4–9</sup>. The second is that since the band-gap of the graphene is zero, the GFET can not be effectively turned off<sup>10–17</sup>. We think that the research discoveries from the GFET which is made from a single atomic layer can provide the solution to the first problem, because the substrate thickness of the Si Complementary-Metal-Oxide-Semicondector (CMOS) IC is becoming thin and thin. In decades, the feature size of the CMOS ICs using Si as the semiconducor material keeps being scaled down guided by the Moore's Law. Nowaday, the 7 nm technology has developped to the industral production<sup>6</sup>, the 5 nm<sup>7</sup> and even 3 nm<sup>8</sup> technology are in the research period. In the advanced FINFET, the channels are at the two sizes of the FIN, so the effective thickness of the Si substrate is the half width of the FIN<sup>9</sup>. When the FIN width goes down to 3 nm<sup>8</sup>, the effective thickness of the Si substrate is 1.5 nm which is less than the thickness of 3 atomic layers of Si  $(0.543 \times 3 \,\mathrm{nm})^{18}$ .

Many efforts were done to solve the turn-off problem of the GFET, for example, by the way of the Graphene-Nano-Ribben (GNR)<sup>19-22</sup> and bilayer graphene<sup>23-26</sup>. But only limited sucssesse were achieved resulting GFET can not be used in digital logic Very Large Scale Integration (VLSI) circuits up to now. Nobel prize winner, Dr. Novoselov predicted that the utility of graphene in logic circuits could be realized after 2025<sup>11</sup>. The highist ratio of the I<sub>ds</sub> on/off was achieved by the GNR<sup>20</sup> with the ratio value of  $1 \times 10^7$ . However, the GNR is too small

State Key Laboratory of Electronic Thin Films and Integrated Devices, University of Electronic Science and Technology of China, Chengdu, 610054, P. R. China. Correspondence and requests for materials should be addressed to P.L. (email: pli@uestc.edu.cn)

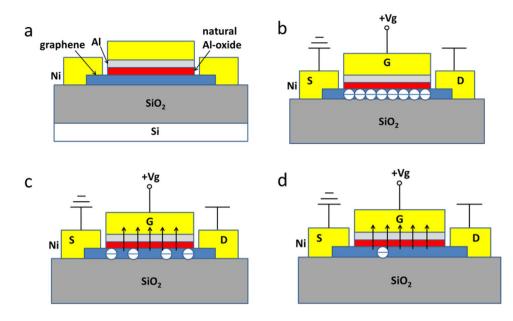

**Figure 1.** The schematic diagram of the graphene MSIS-FET and the electrons in the graphene channel with  $V_{gs}$  increasing during the turning-off procedure of the device. (a) The schematic diagram of the graphene MSIS-FET. (b) When the  $V_{gs}$  is low, a lot of electrons existing in the graphene. (c) When the  $V_{gs}$  is higher, less electrons existing in the grapheme. (d) When the  $V_{gs}$  is high enough, electrons seldom remaining in the grapheme.

to be applied to the VLSI circuits which need large chip area fabricated by the semiconductor planar process. Perhaps for this reason, people turned to investigate the devices made of 2D  $M_0S_2$  materials with the band-gap recently<sup>27-31</sup>.

Recongnizing the traditional methods to turn off the GFET had a lot of problems and noticing a fact which may be ignored by people, the number of carriers in the 2D semiconductor is much smaller than that in the 3D semiconductor, we propose a novel device structure named as the MSIS-FET correspoding to traditional MOS-FET. Namely, the semi-insulaor is used to replace the oxided layer or the insulator in the MOS-FET. We predicted that the graphene MSIS-FET could be turned off by the postive gate voltage  $V_{\rm gs}$  on which the electrons with negative charges in the channel would move toward the gate through the semi-insulaor gate dielectric.

Based on the analysis above, we fabricate the graphene MSIS-FET by using the natural Al-oxide as the gate dielectric. By testing the graphene MSIS-FETs fabricated, we obtain following experimental results. The graphene MSIS-FET with monolayer atom is turned off and on very well, the  $I_{ds}$  on/off ratio of  $5 \times 10^7$  is achieved which is about 5 times lager than the previous record of  $1 \times 10^7$  created by the GNR<sup>20</sup>. A saddle and close-loop shape transfer feature of  $I_{ds}$ -V<sub>gs</sub> is obtained which is obviously different from that of the semiconductor devices reported. A kind of the non-volatile memory characteristics is observed in the measurement of the graphene MSIS-FET, which gives out an important evidence to our turned-off thorey of the MSIS-FET device.

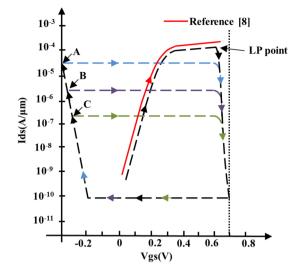

We find a carrier re-injection principle and a super-Low power mechanism from the tested features of the graphene MSIS-FET. In order to show how the super-low power mechanism works and the degree of the  $P_C$  reduction may be, the transfer features of the reported FINFET<sup>8</sup> and the Si MSIS-FET inferred from the graphene MSIS-FET are shown.

#### Theory and Experiments

**Turn-off principle of the MSIS-FET.** The schematic diagram of the graphene MSIS-FET is shown in Fig. 1a. Instead of using a layer of insulator, such as  $SiO_2$  or  $HaO_2$ , a layer of the natural Al-oxide is used as the gate dielectric. Figure 1b-d are the schematic diagrams for the gate extracting the electrons in the graphene channel with the positive gate voltage ( $V_{gs}$ ) increasing during the turning-off procedure of the graphene MSIS-FET.

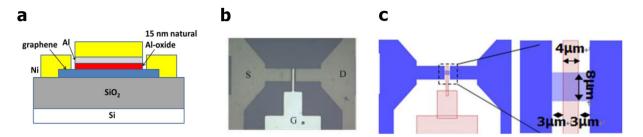

**Fabrication**. The fabrication process of the graphene MSIS-FET with the top gate is described in details in the Supplementary Information (S1). The photograph and layout with the key sizes are shown in Fig. 2.

Briefly speaking, the fabrication process of the graphene MSIS-FET with the top gate was a planar process like that for a semiconductor IC except for the transferring the graphene from a copper (Cu) substrate to the  $SiO_2/Si$  substrate<sup>32</sup>.

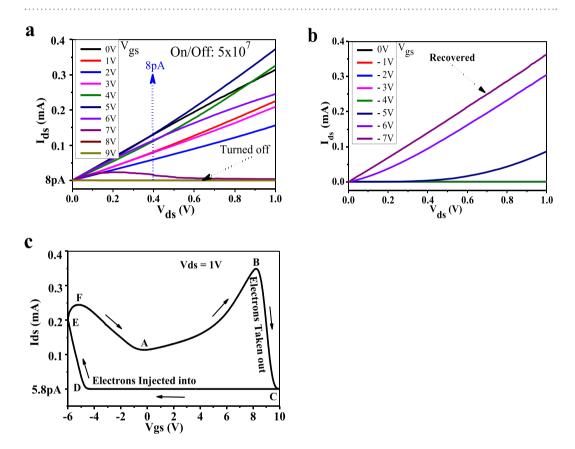

**Tests and discussions.** After the fabrication, the graphene MSIS-FETs with the top gate are tested by the semiconductor parameter analysor of Agilent 4155B. Shown in Fig. 3 are the measured features of the graphene MSIS-FET. From Fig. 3a, it can be seen that when  $V_{gs} = 9 V$ , the device is turned off very well,  $I_{ds}(off) = 8 pA$ ,  $I_{ds}(on) = 0.4 mA$ , the  $I_{ds}$  on/off ratio is  $5 \times 10^7$  which is about 5 times larger than the best reported ratio created by the GNR<sup>20</sup>. This experimental result has verifies that the graphene MSIS-FET can be turned off by a postive  $V_{gs}$ .

In order to verify the turn-off characteristics of the graphene MSIS-FET was caused by using the gate dielectric of the natural Al-oxide, the compaision experiments were done by fabricating both graphene transistors with the

**Figure 2.** The schematic diagram of the top-gate structure graphene MSIS-FET, photograph and the layout with the key sizes. (**a**) The schematic diagram of the top-gate structure graphene MSIS-FET with 15 nm natural Al-oxide. (**b**) The typical photograph of the top-gate structure graphene MSIS-FET. (**c**) The layout and key sizes of the top-gate structure graphene MSIS-FET.

natural Al-oxide and natural Al-oxide plus HaO<sub>2</sub> respectively. Both devices have the back-gate as shown in the schematic diagrams Fig. S1A,B of the Supplementary Information (S2). The tested results are shown in Fig. S2A,B, from which it can be seen that the graphene MSIS-FET with natural Al-oxide can be turned off, while the traditional GFET with the natural Al-oxide plus HaO<sub>2</sub> can not. Both devices have the same graphene material and sizes. The I<sub>gs</sub>-V<sub>gs</sub> features of two devices are shown in Fig. S3A,B. The I<sub>gs</sub>-V<sub>gs</sub> features of the top-gate graphene MSIS-FET is shown in Fig. S3C. From the figures, we can see that the resistance of the 5 nm natural Al-oxide is about  $1.9 \times 10^3$  MΩ, the resistance of the 15 nm natural Al-oxide is about  $1.8 \times 10^4$  MΩ, while the resistance of the 5 nm natural Al-oxide is quite large but it is not infinite, the natural Al-oxide is called as a semi-insulator.

After getting the results of the top gate devices in Fig. 3a and the back gate devices in Fig. S2, we observed that both top and back gate devices could not be turned on once more by any positive  $V_{gs}$  in about 24 hours. This phenomenon is similar to the performance of the floating gate non-volatile semiconductor memory, when the power supply is off, the state of device is keeping<sup>18</sup>. This experimental phenomenon provides a strong support to our turn-off principle because it indicates that, at this time, there are almost no electrons remaining in the graphene channel. The related tested results are shown and discussed in Supplementary Information (S3).

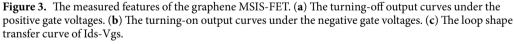

Figure 4. The diagram for description the super-low power mechanism of the MSIS-FET.

At this moment, observing the positive  $V_{gs}$  could not turn on the device again, we could not measure the Ids~Vgs transfer feature for the time being. We thought that if we were right, then the graphene MSIS-FET should be turned on by the negative  $V_{gs}$  injecting the electrons with the negative charges into the graphene which has a higher potential. So the negative  $V_{gs}$  was applied to the device and the tested result is shown in Fig. 3b, from which we can see that, when  $V_{gs} = -7$  V, the conductivity of the graphene MSIS-FET is restored. The device can be immediately turned on by this way after it is turned off.

Based on the above-mentioned turning off and on of the graphene MSIS-FET, we arranged a test by changing  $V_{gs}$  from -6V to +10V and then from +10V to -6V, the forward and backward  $I_{ds} \sim V_{gs}$  current curve at  $V_{ds} = 1V$  is shown in Fig. 3c which is called as the transfer feature of the device. For a conventional MOS-FET, the transfer feature can be tested immediately after the output feature (like Fig. 3a) is completed, however for the MSIS-FET, the transfer feature can only be obtained like the way of getting Fig. 3c. This fact, from one aspect, shows the difference between the MOS-FET and MSIS-FET.

For importance and convenience of discussions, LP point is named for the point B in Fig. 3c, (LP comes from word "Leaping" which means  $I_{ds}$  begins to jump down). The  $V_{gs}$  corresponding to the LP point is named  $V_{LP}$ . The appearance of the LP point for our graphene MSIS-FET is the result of the balance between the functions of the gate extracting electrons and inducing electrons. When  $V_{gs}$  is higher than the  $V_{LP}$  the function of the gate extracting electrons is stronger than that of inducing electrons, as a result, the  $I_{ds}$  gets deceasing, until  $V_{gs}$  reaches the value corresponding to the point C, the graphene MSIS-FET is turned off.

**Super-low power mechanism.** When we obtained the close-loop shape transfer feature of the graphene MSIS-FET shown in Fig. 3c, we understood that the turn-on procedure of the graphene MSIS-FET was a procedure of the carrier re-injection. This new carrier re-injection principle could be used to form the super-low power semiconductor devices and ICs, because, on the line DE in the Fig. 3c, people can chose any point to end the carrier re-injection. The point chosen by people is the closer to the point D, the smaller the I<sub>ds</sub> on-state will be.

In order to explain more clearly how the super-low power mechanism works, Fig. 4 is drawn. In the figure, the transfer features of the 3 nm FINFET comes from the ref.<sup>8</sup>. The performance of the Si MSIS-FET shown in Fig. 4 is inferred from the tested feature of our graphene MSIS-FET at the assumptions of the Si MSIS-FET has the same sizes as the 3 nm FINFET. Another assumption is that the Si MSIS-FET can be turned off in the same way as the graphene MSIS-FET.

Shown in Fig. 4 by the red line is the performance of the 3 nm N type Si FINFET<sup>16</sup>, it can be seen that if the  $V_{ds}$  is defined as 0.7 V, the  $I_{ds}$  is fixed at  $2 \times 10^{-4}$  A. The black line in Fig. 4 shows the turn-off and turn-on procedure of the Si MSIS-FET. At the beginning of the  $V_{gs}$  rising, the  $I_{ds}$  rises like the AB line in Fig. 3c. When the  $V_{gs}$  reaches the  $V_{LP}$  the  $I_{ds}$  reaches its maximum. When the  $V_{gs}$  exceeds  $V_{LP}$  the  $I_{ds}$  deceases rapidly, until  $V_{gs}$  reaches 0.7 V, the  $I_{ds}$  reaches its minimum, the device is turned off. The blue, purple and green lines indicate that by choosing different negative gate voltages during the turning on procedure, people can get the  $I_{ds}$  of the Si MSIS-FET,  $I_{dsMSIS-FET}$  equaling to 1/10 (the blue line), 1/100 (the purple line) or 1/1000 (the green line) of  $2 \times 10^{-4}$  A. As a result, the  $P_{C}$  can be reduced by orders of magnitude, since  $P_{C} = V_{ds} \times I_{dsMSIS-FET}$ . Therefore, the reduction of  $P_{C}$  of the Si MSIS-FET is in a leaping or revolutionary way.

The importance of the amount of  $P_C$  reduction discussed above can be understood by reviewing the way of the  $P_C$  reduction for a traditional Si MOS-FET guided by the Moore's Law. When the feature size is scaled down by a fact of 2, the  $P_C$  can only be reduced by 2~4 times<sup>4</sup>.

From Fig. 4, it can be seen that, for the Si MSIS-FET, the transfer feature has a shape close to the parallelogram. While for the graphene MSIS-FET, the transfer feature has a saddle shape as shown in the Fig. 3c. We predict that the transfer features of the MSIS-FETs made from 2D materials with band-gap such as MoS<sub>2</sub> and black

phosphorus will have the same shape as in Fig. 4. The difference between the features of the MSIS-FETs with and without the band-gap can be predicted as following.

Since the existance of the Dirac point in the graphene MSIS-FET, before the Vgs equals to the Dirac Voltage  $V_{Dirac}$ , the operating carriers are holes, after the Vgs equals to the  $V_{Dirac}$ , the operating carriers are electrons<sup>3</sup>, however, for the MSIS-FETs with the band-gap, for example, for the Si NMOS, the operating carriers are electrons at all the time. In short, since no Ids mimium point caused by the Dirac point existing in the Si MSIS-FET, the saddle shape will not appear in its transfer feature. It needs to point out that the top edge of the parallelogram may not be horizontal. It may has a positive or negative slope depended on which fuction of the gate extracting and inducing the carriers is stronger. If the extracting one is stronger, the top edge will be down to the left before the LP point. Reversely, if the inducing one is stronger, then the top edge will be up to the left before the LP point. The other 2D material MSIS-FETs beside the graphene MSIS-FET may also be important applications of the MSIS-FET, because they can also realize the super-low power based on the machanism found in this paper.

#### Conclusion

In this paper, we propose and experimentally demonstrate the graphene MSIS-FET. The graphene MSIS-FET is turned off and on very effectively by changing the polar of the  $V_{gs}$ . The saddle and close-loop transfer feature of the graphene MSIS-FET is measured first time. The non-volatile memory feature of the graphene MSIS-FET is observed which provides an evidence to our turn-off principle and may be used to form a new type semiconductor memory products.

The contribution of this paper to graphene electronics is that the planar fabrication process of the graphene MSIS-FET may let the graphene material be used much easier in the future. The most important contribution of this paper is the discoveries of the carrier re-injection principle and the super-low power mechanism of the graphene MSIS-FET by which the amount of electrons or holes in the semiconductor channel can be controlled first time by the people. The scientific significace of the MSIS-FET verified by our graphene MSIS-FET is that it makes people changing from passtively accepting the carrier amount in the MOS-FET channel fixed by the operating voltage to actively adjusting the carrier amount in the MSIS-FET channel, as a result, it creates a new way to realize the extremely low power semiconductor devices and ICs.

#### References

- 1. Sze, S. M. Physics of Semiconductor Devices, 2nd Edition, ISBN:0-471-05661-8, Wiley-Interscience, New York, 431-496 (1981).

- 2. Novoselov, K. S. et al. Electric field effect in atomically thin carbon films. Science 306, 666-669 (2004).

- 3. Schwierz, F. Graphene transistors. Nature Nanotech. 5, 487-496 (2010).

- Taur, Y. & Ning, T. H. Fundamentals of Modern VLSI Devices, 2nd Edition, ISBN:9781107635715, ambridge Univ. Press, New York. 219–220 (2009).

- 5. Sicard, E. Introducing 7-nm FinFET technology in microwind, https://hal.archives-ouvertes.fr/hal-01558775 (2017).

- 6. Chen, M., Jessie She, H. TSMC ramping up 7 nm chip production, https://www.digitimes.com/news/a20180622PD204.html (2018).

- Yang, F.-L. et al. 5 nm-gate nanowire Fin FET. In *Digest of Technical Papers. Symposium on VLSI Technology*. 196–197 (IEEE, 2004).

Thirunavukkarasu, V., Jhan, Y.-R., Liu, Y.-B. & Wu, Y.-C. Performance of inversion, accumulation, and junctionless mode n-type and

- p-type Bulk Silicon FinFETs with 3-nm Gate Length. *IEEE Electron Device Letters* 36, 645–647 (2015).

9. Tang, M., Prégaldiny, F., Lallement, C. & Sallese, J.-M. Explicit compact model for ultranarrow body FinFETs. *IEEE Transaction on Election Devices* 56, 1543–1547 (2009).

- 10. Schwierz, F. Graphene transistors: status, prospects, and problems. *Peoceeding of the IEEE* 101, 1567–1584 (2013).

- 11. Novoselov, K. S. et al. A roadmap for graphene. Nature 490, 192-200 (2012).

- 12. Liao, L. et al. High-speed graphene transistors with a self-aligned nanowire gate. Nature 467, 305-308 (2010).

- 13. Lin, Y.-M. et al. 100-GHz transistors from wafer-scale epitaxial graphene. Science 327, 662 (2010).

- 14. Meric, I. et al. Current saturation in zero-bandgap, top-gated graphene field-effect transistors. Nature nanotech. 3, 654–659 (2008).

- 15. Bai, J. *et al.* Top-gated chemical vapor deposition grown graphene transistors with current saturation. *Nano Lett.* **11**, 2555–2559 (2011).

- 16. Perebeinos, V. & Avouris, P. Inelastic scattering and current saturation in graphene. Physical Review B 81, 195442 (2010).

- 17. Feng, Z.-H. *et al.* An ultra clean self-aligned process for high maximum oscillation frequency graphene transistors. *Carbon* 75, 249–254 (2014).

- 18. Sze, S. M. Physics of Semiconductor Devices, 2nd Edition, ISBN:0-471-05661-8, Wiley-Interscience, New York. 848 (1981).

- 19. Son, Y. W., Cohen, M. L. & Louie, S. G. Energy gaps in graphene nanoribbons. Phys. Rev. Lett. 97, 216803 (2006).

- Li, X., Wang, X., Zhang, L., Lee, S. & Dai, H. Chemically derived, ultrasmooth graphene nanoribbon semiconductors. *Science* 319, 1229–1232 (2008).

- Wang, X. et al. Room-temperature all-semiconducting sub-10-nm graphene nanoribbon field-effect transistors. Phys. Rev. Lett. 100, 206803 (2008).

- Lin, M.-W. *et al.* Room-temperature high on/off ratio in suspended graphene nanoribbon field-effect transistors. *Nanotechnology* 22, 265201 (2011).

- Xia, F., Farmer, D. B., Lin, Y.-M. & Avouris, P. Graphene field-effect transistors with high on/off current ratio and large transport band gap at room temperature. *Nano Lett.* 10, 715–718 (2010).

- Szafranek, B. N., Schall, D., Otto, M., Neumaier, D. & Kurz, H. High on/off ratios in bilayer graphene field effect transistors realized by surface dopants. Nano Lett. 11, 26402643 (2011).

- Szafranek, B. N., Fiori, G., Schall, D., Neumaier, D. & Kurz, H. Current saturation and voltage gain in bilayer graphene field effect transistors. *Nano Lett.* 12, 1324–1328 (2012).

- Szafranek, B. N., Schall, D., Otto, M., Neumaier, D. & Kurz, H. Electrical observation of a tunable band gap in bilayer graphene nanoribbons at room temperature. *Appl. Phys. Lett.* 96, 112103 (2010).

- 27. Desai, S. B. et al. MoS<sub>2</sub> transistors with 1-nanometer gate lengths. Science **354**, 99–102 (2016).

- 28. Buscema, M. et al. Large and tunable photothermoelectric effect in single-layer MoS<sub>2</sub>. Nano Lett. **13**(2), 358–363 (2013).

- 29. Katagiri, Y. *et al.* Gate-tunable atomically thin lateral MoS<sub>2</sub> Schottky junction patterned by electron beam. *Nano Lett.* **16**, 3788–3794 (2016).

- Fan, Z.-Q. et al. In-plane Schottky-barrier field-effect transistors based on 1T/2H heterojunctions of transition-metal dichalcogenides. Physical Review B 96, 165402 (2017).

- Fan, Z.-Q., Jiang, X.-W., Chen, J. & Luo, J.-W. Improving performances of In-Plane transition-metal dichalcogenide Schottky barrier field-effect Transistors. ACS Appl. Mater. Interfaces 10, 19271–19277 (2018).

- 32. Zhou, J. et al. Growth and properties of large-area sulfur-doped graphene films. J. Mater. Chem. C 5, 7944–7949 (2017).

### Acknowledgements

This work was supported by the foundation of the advanced technology of the industry and information ministry of P.R. China (Grant No. 51308040203). This work was supported by startup fund of State Key Laboratory of Electronic Thin Films and Integrated Devices at University of Electronic Science and Technology of China.

#### **Author Contributions**

Ping Li provides the theory about the structure and the turn-off principle of the graphene MSIS-FET device. R.Z. Zeng fabricates the top gate graphene MSIS-FET device and realized the high ratio of the  $I_{ds}$  on and off. Y.B. Liao provides the theory about the carrier re-injection and super-low power mechanism of the MSIS-FET device. Q.W. Zhang fabricates the back gate graphene MSIS-FET and the GFET devices for the comparisons and observes the non-volatile memory feature of the graphene MSIS-FET. The contributions of Ping Li, R.Z. Zeng, Y.B. Liao, Q.W. Zhang are equal. J.H. Zhou provides the graphene materials.

#### **Additional Information**

Supplementary information accompanies this paper at https://doi.org/10.1038/s41598-019-40104-9.

Competing Interests: The authors declare no competing interests.

**Publisher's note:** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

© The Author(s) 2019