Abstract

A vertical spin metal-oxide-semiconductor field-effect transistor (spin MOSFET) is a promising low-power device for the post scaling era. Here, using a ferromagnetic-semiconductor GaMnAs-based vertical spin MOSFET with a GaAs channel layer, we demonstrate a large drain-source current IDS modulation by a gate-source voltage VGS with a modulation ratio up to 130%, which is the largest value that has ever been reported for vertical spin field-effect transistors thus far. We find that the electric field effect on indirect tunneling via defect states in the GaAs channel layer is responsible for the large IDS modulation. This device shows a tunneling magnetoresistance (TMR) ratio up to ~7%, which is larger than that of the planar-type spin MOSFETs, indicating that IDS can be controlled by the magnetization configuration. Furthermore, we find that the TMR ratio can be modulated by VGS. This result mainly originates from the electric field modulation of the magnetic anisotropy of the GaMnAs ferromagnetic electrodes as well as the potential modulation of the nonmagnetic semiconductor GaAs channel layer. Our findings provide important progress towards high-performance vertical spin MOSFETs.

Similar content being viewed by others

Introduction

Reducing the power consumption in integrated circuits is an important issue that we have to tackle in the 21st century. Making volatile components non-volatile is one of the most promising approaches to this issue; various non-volatile technologies, such as reconfigurable logic circuits1, non-volatile power gating2 and magnetic random access memory, are applicable to low-power-consumption electronics. A spin metal-oxide-semiconductor field-effect transistor (spin MOSFET)3,4, in which source and drain electrodes are ferromagnetic materials, is a key component for realizing those applications because of the several advantages inherent in spin MOSFETs: The most important advantage of spin MOSFETs over other spintronics devices such as all-spin-logic devices5,6 is the high amplification capability, which is crucially important for restoring propagating signals between transistors, and thus indispensable for the application to large scale integrated circuits. Also, spin MOSFETs are compatible with existing well-matured semiconductor technologies, which makes integration with semiconductor devices very easy. Spin MOSFETs can have the same advantages of scaling circuits as those of general transistors, which is very important for miniaturization of the device from the view point of energy consumption. For practical operation of spin MOSFETs, both large current modulation by applying a gate electric field and large magnetoresistance (MR) by magnetization reversal are required. At present, lateral and vertical types of spin MOSFETs have been proposed. The lateral spin MOSFETs, in which a current flows parallel to the substrate plane and is controlled by a gate electric field applied from the top of the channel, have a large current modulation capability (5 × 106%7, 400%8 and 107%9); however, the problem is the small MR ratio (0.1%7, 0.005%8 and 0.027%9). Meanwhile, epitaxial magnetic heterostructures were grown using various ferromagnets and semiconductors and some magnetotransport properties were studied10,11,12,13,14,15. Thus, a vertical spin field-effect transistor (FET), in which a current flows perpendicular to the film plane and is controlled by a gate voltage applied from the side surface of the channel, is promising for large MR. Previously, we reported ferromagnetic-semiconductor GaMnAs-based vertical spin FETs that exhibit large MR ratios (60%16 and 5%17). A GaMnAs-based heterostructure is one of the most ideal material systems, because we can obtain high-quality single-crystalline GaMnAs/nonmagnetic semiconductor (GaAs)/GaMnAs trilayers and thus can suppress spin relaxation at the interfaces18,19,20,21. However, in those vertical spin FETs, the current modulation ratio by the gate voltage was small (0.5%16 and 20%17). Thus, vertical spin FETs with a large current modulation are strongly required. In addition, to further improve the performance of the vertical spin FETs, we need more profound understanding of the gate electric field effect on the spin-dependent transport.

In vertical spin FETs, as shown by our electric field simulations later, the gate electric field influences the electric potential profile only within 10 nm from the side surfaces of the intermediate channel layer, which limits the current modulation. Thus, the lateral size of vertical FETs should be decreased as much as possible for obtaining high-performance vertical spin FETs. In this study, to enhance the current modulation and to understand the electric field effect on the spin-dependent transport, we reduced the lateral size (=width of the mesas as explained later) of the GaMnAs-based vertical spin MOSFET to ~500 nm. We have successfully obtained a large current modulation by the gate electric field with a modulation ratio up to 130%, which is the largest value that has been ever reported for vertical spin FETs16,17. Furthermore, using the electric field simulations, we find that indirect tunneling mainly contributes to the observed large current modulation. These new findings are important steps to further improve the performance of the vertical spin FETs.

Results

Samples

Our vertical spin MOSFET has a thin GaAs channel (9 nm) and ferromagnetic-semiconductor GaMnAs source and drain electrodes [Fig. 1(a)] (See the Methods section). To increase the current modulation, we reduced the width of the mesas down to ~500 nm. As a gate insulator, a 40-nm-thick HfO2 film was used since it has a large relative permittivity, which also contributes to the increase of the current modulation. In this device, tunneling of holes occurs between the source and drain, because GaAs is a potential barrier with a height of ~100 meV for holes in the GaMnAs layers22,23, as shown in Fig. 1(b). When the gate-source voltage VGS < 0 V (VGS ≥ 0 V), the tunneling current flowing at the side surfaces of the mesas is increased (decreased), as shown in Fig. 1(c).

(a) Schematic illustration of the vertical spin MOSFET investigated in this study. The backside of the substrate is the source electrode, the comb shaped Au/Cr layer is the drain electrode and the Au/Cr layer above the HfO2 layer is the gate electrode. (b,c) Schematic device operation of our vertical spin MOSFET when a gate voltage VGS is not applied (b) and when a negative gate voltage is applied (c). The orange arrows represent a drain-source current IDS.

MOSFET operation and its analyses

To investigate the MOSFET characteristics of this device, we measured the drain-source current IDS as a function of the drain-source voltage VDS for various VGS [Fig. 2(a)]. Nonlinear IDS–VDS characteristics were observed for each VGS (black curves), indicating that tunneling transport is dominant. Furthermore, IDS was largely controlled by VGS. We note that the gate leakage current and electric field effect on parasitic resistances (the resistances of the top/bottom GaMnAs layers, GaAs:Be layer and Au/Cr electrodes), which may induce unintended modulation of IDS, were negligibly small (see Supplementary Note 1). When VGS = 20 V, the IDS modulation ratio by VGS, which is defined by [IDS(VGS) – IDS(VGS = 0 V)]/IDS(VGS = 0 V) × 100 (%), is around −20% [see the blue points in Fig. 2(b)]. On the other hand, when VGS = −20 V, it reached ~130% [see the red points in Fig. 2(b)]. This IDS modulation ratio (~130%) is the largest among the values reported for vertical spin FETs thus far16,17.

(a) Drain-source current IDS as a function of the drain-source voltage VDS with the gate-source voltage VGS ranging from −20 V to 20 V with a step of 5 V at 3.8 K. (b) IDS modulation ratio as a function of VDS with various VGS at 3.8 K. (c) Drain-source current (−IDS) (left axis) and the IDS value normalized at VGS = 0 V (γ) (right axis) as a function of VGS with VDS = −10 mV at 3.8 K. (d) Calculated IDS normalized by the one at VGS = 0 V (γcalc) as a function of EV(S). (e,h) Calculated valence band top energy EV with respect to the Fermi level when EV(S) = 0.75 eV (e) and EV(S) = 0.15 eV (h). Here, the Fermi level corresponds to 0 eV. The vertical axis expresses the hole energy. The inset in (e) and (h) shows the structure used in our calculation. Here, the x axis represents the distance from the side surface of the mesa and the y axis denotes the distance from the interface between the bottom GaMnAs layer and the intermediate GaAs layer. The calculation was performed in the region surrounded by the dashed line. In (e,h), only the region of 0 nm ≤ x ≤ 15 nm is shown because it is sufficient to see how the gate electric field influences the valence band maximum energy in the GaAs layer. (f,g) EV vs. y at x = 1 nm (f) and 15 nm (g) when EV(S) = 0.75 eV. (i,j) EV vs. y at x = 1 nm (i) and 15 nm (j) when EV(S) = 0.15 eV.

To understand the modulation of the band alignment in detail, we measured IDS as a function of VGS at VDS = −10 mV [Fig. 2(c)]. IDS normalized at VGS = 0 V (γ) was changed from 1 to 1.28 when VGS was changed from 0 V to −3 V [see the right axis in Fig. 2(c)], meaning that IDS was increased by 28% when VGS was changed from 0 V to −3 V. As shown below, this large modulation of IDS cannot be understood by the electric field effect on direct tunneling. To obtain the potential distribution and to calculate IDS normalized at VGS = 0 V (γcalc), we performed electric field simulation varying the electric potential at the side surface of the mesa and investigated the effect of the side-gate electric field [Fig. 2(e,h)] (see Supplementary Note 2). Here, we define EV(S) as the valence band top energy EV at the side surface (interface between the side-gate electrode and the GaAs channel) with respect to the Fermi level EF in terms of hole energy. The potential profile of EV when EV(S) = 0.75 eV is shown in Fig. 2(e), which corresponds to the case of VGS = 0 V, because EF at the side surface of the GaAs channel is pinned at the middle of the band gap24. With decreasing EV(S) from 0.75 eV, the electric potential near the side surface of the mesa is decreased [Fig. 2(f,i)], whereas the electric potential in the inner region of the mesa (10 nm ≤ x) is not influenced [Fig. 2(g,j)]. As shown in Fig. 2(d), γcalc remains almost unchanged between Fig. 2(e) (γcalc = 1 when EV(S) = 0.75 eV) and (h) (γcalc = 1.028 when EV(S) = 0.15 eV) because GaAs is a potential barrier for holes in both cases. On the other hand, when EV(S) < 0.15 eV, because EV of the GaAs channel at the side surface becomes lower than EV inside the mesa, γcalc starts to increase with decreasing EV(S) [Fig. 2(d)]. This feature is different from the experimental data shown in Fig. 2(c); when VGS is changed from 0 V to −10 V, γ starts to increase at VGS = 0 V. We can see the significant difference in the curve shapes of Fig. 2(c) and Fig. 2(d). This analysis indicates that the electric field effect on the direct tunneling current cannot reproduce the experimental IDS–VGS characteristic. Instead, the main origin of the large modulation ratio observed in our device is the electric field effect on the indirect tunneling current25.

The indirect tunneling current is probably caused by a large amount of Mn atoms (~1018 cm−3), which are diffused to the intermediate GaAs layer from the top and bottom GaMnAs layers and form defect states in the band gap of GaAs. Furthermore, GaAs grown at low temperature (200 °C) is known to have a large amount of arsenic antisite defects (1018–1019 cm−3)26,27. In fact, the IDS–VDS characteristics of our device show a strong temperature dependence (see Supplementary Note 3), which indicates that indirect tunneling via defect states takes place. (If IDS were dominated only by the direct tunneling current, no temperature dependence would be observed.) Therefore, the electric field effect on indirect tunneling via defect states is the most probable origin for the large IDS modulation ratio. To enhance the IDS modulation ratio, we have to solve the Fermi level pinning problem at the surface of GaAs, i.e., because the Fermi level is severely pinned at the middle of the band gap at the surface of GaAs, it is very difficult to move the valence band maximum toward the Fermi level of the GaMnAs layers by the application of VGS. The Fermi level pinning in GaAs is thought to originate from defect states formed at the interface between GaAs and gate insulators. Thus, reducing the interface state density between GaAs and gate insulators is a key to enhancing the current modulation ratio by VGS.

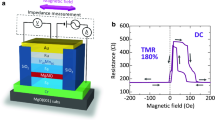

Tunneling magnetoresistance and its change by V GS

To investigate the spin-dependent transport of our device, we measured the drain-source resistance RDS as a function of μ0H applied along the [\(\bar{1}\)10] direction in the film plane with VDS = −5 mV and VGS = 0 V [Fig. 3(a)]. Here, RDS is defined by VDS/IDS, μ0 is the permeability of a vacuum and H is an in-plane external magnetic field. In the major loop (black circles), clear tunnel magnetoresistance (TMR) was observed, indicating that IDS can be controlled by the magnetization configuration. The TMR ratio, which is defined by [RDS(μ0H) – RDS(μ0H = 0 mT)]/RDS(μ0H = 0 mT) × 100 (%), reached ~7% at μ0H = 20 mT, where RDS(μ0H) is the drain-source resistance at H in the major loop. This value is more than 70 times larger than the MR ratios obtained in the lateral spin MOSFETs7,8,9. In the major loop, the negative MR was observed at μ0H < 0 mT (μ0H > 0 mT) when μ0H was swept from positive to negative (negative to positive) probably because of a multi-domain structure in the top and bottom GaMnAs layers. We also observed a clear minor loop (red circles), indicating that the antiparallel magnetization configuration is stable even at μ0H = 0 mT. (In the minor loop, RDS increases with increasing μ0H from −20 mT to 10 mT, probably because the magnetizations of the top and bottom GaMnAs layers are not completely antiparallel at the peak of RDS (at μ0H = −20 mT in the major loop) and they become close to the perfect antiparallel configuration with increasing μ0H to 10 mT in the minor loop.)

(a) Drain-source resistance RDS as a function of the in-plane external magnetic field μ0H applied along the [\(\bar{1}\)10] direction at 3.8 K. Here, the drain-source voltage VDS was −5 mV and the gate-source voltage VGS was 0 V. The black circles correspond to the major loop and the red circles correspond to the minor loop. The black (red) arrows are the sweep directions in the major (minor) loop. The magnetization states in the major loop are indicated by the white arrows above the graph. (b) TMR ratio as a function of the gate-source voltage VGS at 3.8 K. Here, the drain-source voltage VDS was fixed at −5 mV and the external magnetic field H was applied along the [\(\bar{1}\)10] direction. The TMR ratio is the maximum value obtained in the major loop at each VGS. (c–e) Magnetic-field-direction dependences of the TMR ratios at VDS = −10 mV with VGS = 0 V (c), -5 V (d) and −10 V (e).

To investigate the influence of VGS on the spin-dependent transport, we measured the VGS dependence of the TMR ratio [Fig. 3(b)]. Here, the TMR ratio corresponds to the maximum value obtained in the major loop at each VGS. The TMR ratio tends to increase as VGS is changed from 0 V to −10 V. In our device, the gate electric field can modulate the electronic states of the top/bottom GaMnAs layers as well as those of the intermediate GaAs layer, both of which can modulate TMR. Applying VGS causes the change in the hole density of the GaMnAs layers near the side surfaces of the mesas, which can change the spin polarization and magnetic anisotropy17. To understand the modulation of the magnetic anisotropy by VGS in our device, we measured TMR applying H in various in-plane directions with an angle θ with respect to the [100] axis in the counterclockwise rotation when VGS = 0, −5 and −10 V [Fig. 3(c–e)] (see Measurements section). The observed TMR ratios showed dominant uniaxial anisotropy along the [\(\bar{1}\)10] direction in addition to biaxial anisotropy along the <100> directions for any VGS [see the four red peaks in Fig. 3(c–e)]. With changing VGS from 0 V to −10 V, the easy axes of our device were slightly rotated toward the [010] direction (the red-colored region is extended toward the [010] direction). In spintronics devices, changing the magnetization directions is necessary to write information, which accompanies the power consumption. The controllability of the magnetic anisotropy by the gate voltage is more advantageous in spintronics devices than other methods such as optical control of the magnetic properties28 because we can expect the reduction of the power consumption required for writing information, since the application of the gate voltage does not accompany joule heating. Furthermore, the coercive force of the top GaMnAs layer, which has a larger coercivity than the bottom GaMnAs layer, increases as VGS is changed from 0 V to −10 V (the red-colored region slightly expands outward). These results indicate that the magnetic anisotropy constants are modulated by applying negative VGS, which can also contribute to the modulation of the TMR ratio. In addition, VGS modifies the valence band maximum energy in the GaAs layer. As we discussed in the previous section, the modulation of the indirect tunneling current via defect states is the most probable mechanism for the obtained large modulation of IDS. The TMR induced by indirect tunneling via defect states depends on many factors such as energy levels of defect states, band width of defect states, life time of carries and so on. The modulation of the electric potential can influence the indirect tunneling and thus TMR. Therefore, the electric field effect both on the top/bottom GaMnAs layers and on the intermediate GaAs layer contributes to the modulation of the observed TMR ratio. Although only the side surfaces of the mesas are influenced by VGS, the MR and the magnetic anisotropy of our device are clearly modulated. This phenomenon can be understood as follows. When negative VGS is applied, the current flowing at the side surface of the mesas is increased and becomes dominant in IDS. When negative VGS is applied, the magnetic properties of the side surface of the top and bottom GaMnAs layers are also modulated. These facts indicate that the modulation of the magnetic properties of the top and bottom GaMnAs layers, which takes place only at the edge regions of the mesas, is preferentially reflected to the measured spin-dependent transport properties in our device. Therefore, the MR and the magnetic anisotropy of our device are modulated although only the edge regions of the mesas are influenced by VGS.

Surprisingly, the VGS dependence of the TMR ratio shown in Fig. 3(b) is completely opposite to the one obtained in our previous study, i.e. the TMR ratio decreased as negative VGS is applied in our previous study16. This may be caused by the difference of the easy axes between the present device and the previous one (the biaxial anisotropy was dominant in our previous work) or by the different direction of an external magnetic field (along the direction with an angle 10-degree from the [100] direction toward the [1 \(\bar{1}\) 0] in our previous work).

Summary

In summary, we have investigated the electric field effect on the spin-dependent transport properties in a GaMnAs-based vertical spin MOSFET. We obtained a large current modulation ratio up to 130%, which is the largest value that has ever been reported thus far for the vertical spin FETs16,17. By comparing the experimental data with the calculated results, we concluded that this large IDS modulation does not originate from the modulation of direct tunneling between the source and the drain but from the modulation of the indirect tunneling current via defect states in the intermediate GaAs layer. The TMR ratio tends to increase as negative VGS is applied, which is attributed to the electric field effect both on the top/bottom GaMnAs layers and on the intermediate GaAs layer. These results provide an important insight into the device physics for realizing high-performance vertical spin MOSFETs.

Methods

Growth

The heterostructure composed of, from the top to the bottom, Ga0.94Mn0.06As (10 nm)/GaAs (9 nm)/Ga0.94Mn0.06As (3.2 nm)/GaAs:Be (50 nm, hole concentration p = 5 × 1018 cm−3) on a p+-GaAs (001) substrate by low-temperature molecular beam epitaxy. The growth temperatures of the top Ga0.94Mn0.06As, GaAs, bottom Ga0.94Mn0.06As and GaAs:Be layers were 195 °C, 180 °C, 200 °C and 520 °C, respectively. The Curie temperatures of the top and bottom GaMnAs layers were estimated to be ~53 K and 20–30 K, respectively. (For the details, see the Supplementary Note 4). Post-growth annealing was not carried out.

Process

After the growth, we partially etched the grown films and buried the etched area with a 100-nm-thick SiO2 layer for the separation of the drain electrode and the substrate. Then, a comb-shaped Au (40 nm)/Cr (5 nm) layer, whose width of the comb teeth is ~500 nm and length of them is 50 μm, was formed by electron-beam lithography and a lift-off technique. We chemically etched the area that is not covered by the Au/Cr layer and then the magnetic tunnel junctions only beneath the comb teeth area of the Au/Cr drain electrode remained after the etching. Since the narrow-line-shaped mesas are formed by chemical wet etching, the influence of defects at the side surfaces of the GaAs layer induced by the nanofabrication of the mesas can be neglected. We formed a 40-nm-thick HfO2 film as a gate insulator using atomic layer deposition at a substrate temperature of 150 °C and deposited a gate electrode composed of Au (50 nm)/Cr (5 nm) by electron-beam deposition.

Measurements

After the device was bonded with Au wires and indium solder, we measured the spin-dependent transport properties of our spin MOSFET with varying VGS and H at 3.8 K. Here, the experimental data of our vertical spin MOSFET are collected from 20 mesas that are connected by the drain electrode in the comb-shaped chip. To measure the θ dependence of TMR, we applied a strong magnetic field of 1 T in the opposite direction of θ to align the magnetization directions and we decreased H to zero. Then, we started to measure RDS while increasing H from zero in the direction of θ. The measurements were performed at every 10° step of θ. We note that our experimental data are reproducible.

References

Matsuno, T., Sugahara, S. & Tanaka, M. Novel Reconfigurable Logic Gates Using Spin Metal–Oxide–Semiconductor Field-Effect Transistors. Jpn. J. Appl. Phys. 43, 6032–6037 (2004).

Sugahara, S. & Nitta, J. Spin-Transistor Electronics: An Overview and Outlook. Proc. IEEE 98, 2124–2154 (2010).

Sugahara, S. & Tanaka, M. A spin metal–oxide–semiconductor field-effect transistor using half-metallic-ferromagnet contacts for the source and drain. Appl. Phys. Lett. 84, 2307–2309 (2004).

Tanaka, M. & Sugahara, S. MOS-Based Spin Devices for Reconfigurable Logic. IEEE Trans. Electron Devices 54, 961–976 (2007).

Lin, X. et al. Gate-Driven Pure Spin Current in Graphene. Phys. Rev. Appl. 8, 34006 (2017).

Cho, S., Chen, Y.-F. & Fuhrer, M. S. Gate-tunable graphene spin valve. Appl. Phys. Lett. 91, 123105 (2007).

Nakane, R., Harada, T., Sugiura, K. & Tanaka, M. Magnetoresistance of a Spin Metal–Oxide–Semiconductor Field-Effect Transistor with Ferromagnetic MnAs Source and Drain Contacts. Jpn. J. Appl. Phys. 49, 113001 (2010).

Sasaki, T. et al. Spin Transport in Nondegenerate Si with a Spin MOSFET Structure at Room Temperature. Phys. Rev. Appl. 2, 34005 (2014).

Tahara, T. et al. Room-temperature operation of Si spin MOSFET with high on/off spin signal ratio. Appl. Phys. Express 8, 113004 (2015).

Yamada, S., Tanikawa, K., Miyao, M. & Hamaya, K. Atomically Controlled Epitaxial Growth of Single-Crystalline Germanium Films on a Metallic Silicide. Cryst. Growth Des. 12, 4703–4707 (2012).

Jenichen, B., Herfort, J., Jahn, U., Trampert, A. & Riechert, H. Epitaxial Fe3Si/Ge/Fe3Si thin film multilayers grown on GaAs(001). Thin Solid Films 556, 120–124 (2014).

Wong, P. K. J. et al. Spin-Dependent Transport in Fe/GaAs(100)/Fe Vertical Spin-Valves. Sci. Rep. 6, 29845 (2016).

Matsuo, N., Doko, N., Takada, T., Saito, H. & Yuasa, S. High Magnetoresistance in Fully Epitaxial Magnetic Tunnel Junctions with a Semiconducting GaO x Tunnel Barrier. Phys. Rev. Appl. 6, 34011 (2016).

Sakai, S. et al. Low-temperature growth of fully epitaxial CoFe/Ge/Fe3Si layers on Si for vertical-type semiconductor spintronic devices. Semicond. Sci. Technol. 32, 94005 (2017).

Kawano, M. et al. Electrical detection of spin accumulation and relaxation in p -type germanium. Phys. Rev. Mater. 1, 34604 (2017).

Kanaki, T., Asahara, H., Ohya, S. & Tanaka, M. Spin-dependent transport properties of a GaMnAs-based vertical spin metal-oxide- semiconductor field-effect transistor structure. Appl. Phys. Lett. 107, 242401 (2015).

Terada, H., Ohya, S., Anh, L. D., Iwasa, Y. & Tanaka, M. Magnetic anisotropy control by applying an electric field to the side surface of ferromagnetic films. Sci. Rep. 7, 5618 (2017).

Tanaka, M. & Higo, Y. Large Tunneling Magnetoresistance in GaMnAs/AlAs/GaMnAs Ferromagnetic Semiconductor Tunnel Junctions. Phys. Rev. Lett. 87, 26602 (2001).

Chiba, D., Matsukura, F. & Ohno, H. Tunneling magnetoresistance in (Ga,Mn)As-based heterostructures with a GaAs barrier. Phys. E Low-dimensional Syst. Nanostructures 21, 966–969 (2004).

Saito, H., Yuasa, S. & Ando, K. Origin of the Tunnel Anisotropic Magnetoresistance in Ga1-xMn x As/ZnSe/Ga1-xMn x As Magnetic Tunnel Junctions of II-VI/III-V Heterostructures. Phys. Rev. Lett. 95, 86604 (2005).

Elsen, M. et al. Spin transfer experiments on (Ga,Mn)As/(In,Ga)As/(Ga,Mn)As tunnel junctions. Phys. Rev. B 73, 35303 (2006).

Ohno, Y., Arata, I., Matsukura, F. & Ohno, H. Valence band barrier at (Ga,Mn)As/GaAs interfaces. Phys. E Low-Dimensional Syst. Nanostructures 13, 521–524 (2002).

Ohya, S., Muneta, I., Hai, P. N. & Tanaka, M. GaMnAs-based magnetic tunnel junctions with an AlMnAs barrier. Appl. Phys. Lett. 95, 242503 (2009).

Shen, H. et al. Fermi level pinning in low‐temperature molecular beam epitaxial GaAs. Appl. Phys. Lett. 61, 1585–1587 (1992).

Vandooren, A. et al. Analysis of trap-assisted tunneling in vertical Si homo-junction and SiGe hetero-junction Tunnel-FETs. Solid. State. Electron. 83, 50–55 (2013).

Kaminska, M. et al. Structural properties of As‐rich GaAs grown by molecular beam epitaxy at low temperatures. Appl. Phys. Lett. 54, 1881–1883 (1989).

Look, D. C. et al. Anomalous Hall-effect results in low-temperature molecular-beam-epitaxial GaAs: Hopping in a dense EL2-like band. Phys. Rev. B 42, 3578–3581 (1990).

Liu, P. et al. Optically tunable magnetoresistance effect: From mechanism to novel device application. Materials (Basel). 11, 47 (2017).

Acknowledgements

This work was partly supported by Grants-in-Aid for Scientific Research (No. 26249039, No. 16H02095), CREST program of Japan Science and Technology Agency, and Spintronics Research Network of Japan (Spin-RNJ). We would like to thank Prof. S. Takagi for fruitful discussion. We also would like to thank Mr. H. Asahara for estimating the TC of the top GaMnAs layer. T. Kanaki was supported by JSPS through the program for leading graduate schools (MERIT). T. Kanaki thanks the JSPS Research Fellowship Program for Young Scientists.

Author information

Authors and Affiliations

Contributions

Sample preparation: T. Kanaki, H.Y., T. Koyama., and D.C.; measurements: T. Kanaki and H.Y.; data analysis: T. Kanaki and H.Y.; writing and project planning: T. Kanaki, S.O., and M.T.

Corresponding authors

Ethics declarations

Competing Interests

The authors declare no competing interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Kanaki, T., Yamasaki, H., Koyama, T. et al. Large current modulation and tunneling magnetoresistance change by a side-gate electric field in a GaMnAs-based vertical spin metal-oxide-semiconductor field-effect transistor. Sci Rep 8, 7195 (2018). https://doi.org/10.1038/s41598-018-24958-z

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-018-24958-z

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.