Abstract

In this paper, we investigate the synthesis of WSe2 by chemical vapor deposition and study the current transport and device scaling of monolayer WSe2. We found that the device characteristics of the back-gated WSe2 transistors with thick oxides are very sensitive to the applied drain bias, especially for transistors in the sub-micrometer regime. The threshold voltage, subthreshold swing, and extracted field-effect mobility vary with the applied drain bias. The output characteristics in the long-channel transistors show ohmic-like behavior, while that in the short-channel transistors show Schottky-like behavior. Our investigation reveals that these phenomena are caused by the drain-induced barrier lowering (short-channel effect). For back-gated WSe2 transistors with 280 nm oxide, the short-channel effect appears when the channel length is shorter than 0.4 µm. This extremely long electrostatic scaling length is due to the thick back-gate oxides. In addition, we also found that the hydrogen flow rate and the amount of WO3 precursor play an important role in the morphology of the WSe2. The hole mobility of the monolayer WSe2 is limited by Columbic scattering below 250 K, while it is limited by phonon scattering above 250 K. These findings are very important for the synthesis of WSe2 and accurate characterization of the electronic devices based on 2D materials.

Similar content being viewed by others

Introduction

WSe2 is an important member of the transition metal dichalcogenide (TMDC) family due to its smaller effective electron and hole masses compared to most of the other TMDCs1, and more importantly due to its ambipolar characteristics2. The small effective mass implies high carrier mobilities. The hole mobility of WSe2 is reported to reach 500 cm2/V-s at room temperature and 2.1 × 103 cm2/V-s at 5 K3,4. The ambipolar conduction is essential for complementary metal-oxide semiconductor (CMOS) circuits such as inverters, since most of the TMDCs (such as MoS2, MoSe2, and WS2), are naturally n-type doped. Although MoTe2 and black phosphorus have also been reported to show p-type conduction5,6,7,8, these materials are less stable in ambient conditions. Electrical properties of WSe2 including quantum oscillations, carrier mobilities, contacts, and polarity controls, have been studied and various electronic devices based on WSe2, including metal-oxide field-effect transistors (MOSFETs), tunneling devices, bipolar transistors, and integrated circuits, have been demonstrated2,3,9,10,11,12,13,14,15,16,17,18,19,20,21,22. However, most of these studies focus on exfoliated WSe2 flakes. For practical applications, synthesis of large area WSe2 with controllable layer thickness and quality is essential. There are several recent reports on the growth of thin WSe2 using chemical vapor deposition (CVD)23,24,25,26, and metal-organic CVD (MOCVD)27,28. However, study of the electrical transport of CVD grown WSe2 is still lacking. In this paper, we systematically investigate the growth of monolayer WSe2 by CVD and study the current transport of CVD WSe2, including short-channel effect, temperature dependence of carrier mobility, subthreshold swing, and interface states.

Results and Discussion

Synthesis of CVD WSe2

Solid precursor WO3 and Se power were used to synthesize WSe2 on Si/SiO2 substrate in a CVD chamber. Various growth conditions have been investigated, including hydrogen flow rate, WO3 precursor amount, growth temperature, and argon flow rate. We found that these growth parameters can significantly influence the morphology of the WSe2. Figure 1a–e show the optical images of the synthesized WSe2 with various hydrogen flow rates and WO3 precursor amounts. For a given flow rate of argon carrier gas [60 standard cubic centimeters per minute (sccm)], when the hydrogen flow rate increases from 15 sccm to 20 sccm, the grain size of WSe2 increases dramatically. However, when the hydrogen flow rate further increases to 25 sccm, the grain size decreases and multilayer stacks start to form. This is because selenium has very low chemical reactivity. A strong reducer such as hydrogen is needed in the selenization reduction of WO3. However, if the hydrogen flow rate is too high, the reduction of WO3 to W happens very quickly and the WO3 powder only lasts for a very short time, which results in small grains of thick WSe2. The amount of the precursors loaded in the chamber also plays an important role. For a given amount of Se precursor [(300 milligram (mg)], increasing the quantity of WO3 precursor from 100 mg to 150 mg can effectively increase the grain size. However, further increase of WO3 to 200 mg will result in the growth of multi-layer WSe2.

Optical image of CVD WSe2 grown at various hydrogen flow rates and WO3 precursor amounts: (a) H2 flow rate 15 sccm, WO3 quantity 150 mg; (b) H2 flow rate 20 sccm, WO3 quantity 100 mg; (c) H2 flow rate 20 sccm, WO3 quantity 150 mg; (d) H2 flow rate 20 sccm, WO3 quantity 200 mg; (e) H2 flow rate 25 sccm, WO3 quantity 150 mg. The scale bars in the images are 10 µm.

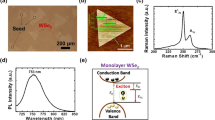

The optimized growth condition for WSe2 using this CVD system is 150 mg of WO3 and 300 mg of Se powder, ambient pressure, 875 °C growth temperature, 70/20 sccm flow of Ar/H2, and 10~15 minutes growth duration. Perylene-3,4,9,10-tetracarboxylic acid tetra potassium (PTAS) was used as the seeding promoter. With the optimized growth condition, high-quality monolayer WSe2 was obtained. Figure 2a–d shows the typical optical image, photoluminescence (PL) spectrum, Raman spectrum, and atomic force microscopy (AFM) phase image of the synthesized WSe2. Bright light emission at ∼1.60 eV and symmetric single PL peak suggest the direct band gap nature of monolayer WSe2, showing good agreement with other recent reports about PL of monolayer WSe224,25,26,29,30,31,32. The E2g and A1g modes in the Raman spectrum are at 253.5 cm−1 and 264.2 cm−1, respectively. Comparing the peak position with the spectrum obtained from the exfoliated monolayer WSe233, we verify that the WSe2 film is monolayer. The AFM phase image shows a clear triangle pattern. From the AFM step height profile, the thickness of the WSe2 is measured as ~0.54 nm, confirming its monolayer character.

Device scaling of the back-gated WSe2 transistors

WSe2 transistors with various gate lengths (from 0.1 µm to 5 µm) are fabricated using Pd as metal contacts. Figure 3 illustrated the process flow of the WSe2 devices. The alignment marks with Ti/Au metals were formed by ebeam lithography, metal deposition and lift-off. Hall-bars and transistors were designed for individual WSe2 triangles. The source/drain electrodes (40 nm Pd) were formed by ebeam lithography, metal evaporation and lift-off. The WSe2 channel is defined by ebeam lithography and oxygen plasma etching. The electrical characteristics were measured in vacuum at various temperatures.

Illustration of the fabrication of the WSe2 devices. (a) Synthesize WSe2 on SiO2/Si substrate using CVD. (b) Form alignment marks using ebeam lithography, metal deposition and lift-off. (c) Form source/drain electrodes using ebeam lithography, metal deposition and lift-off. (d) Define channel by ebeam lithography and oxygen plasma etching.

Surprisingly, in long-channel transitions (L = 5 µm), the output characteristics (ID~VD curves) are linear, indicating ohmic contacts, shown in Fig. 4a, while in short-channel transistors (L = 0.1 µm), the ID~VD curves are non-linear, shown in Fig. 4b, resembling Schottky contact characteristics. Since both the long- and short-channel transistors are fabricated on the same wafer with nearly identical WSe2 and Pd metals. It is very unlikely that they formed different types of contacts. Our further investigation reveals that these non-linear output characteristics in the WSe2 transistors are not related to the metal contacts, but due to the short-channel effect, which will be discussed below.

The transfer characteristics (ID~VG curves) were measured at various drain voltages for WSe2 transistors with various gate lengths in a transmission line micro (TLM). A typical SEM image of the TLM structure is shown in Fig. 5a. (Note, in order to avoid the SEM damage on the monolayer WSe2 in the electronic device, the SEM is taken on a neighboring device with same layout on the same wafer as the device tested electrically). The channel conductances at various drain voltages for a long-channel (L = 5 µm) and a short-channel (L = 0.1 µm) transistor, are shown in Fig. 5b and c. For the long-channel transistor, the conductance is nearly independent of the drain voltages. For the short-channel transistor, however, there is a large dispersion of the conductance, especially at the subthreshold regime. Figure 5d plots the threshold voltage as a function of drain voltage for transistors with channel lengths of L = 0.1 μm, 0.2 μm, and 5 μm. We can see that the threshold voltage increases dramatically as the amplitude of the drain voltage, |VD|, increases for the short channels (L = 0.1 μm and 0.2 μm), while it is nearly constant for the long channel (L = 5 μm). This positive shift of the threshold voltage at high drain bias in these short-channel p-type transistors is a result of the fact that the energy barrier between the source and drain is lowered by the high drain voltage and thus the transistors are much easier to turn on. The drain-induced barrier lowering (DIBL) can be estimated using the equation \({\rm{DIBL}}=\frac{{V}_{t}^{DD}-{V}_{t}^{Low}}{{V}_{DD}-{V}_{D}^{Low}}\), where \({V}_{t}^{DD}\,\)is the threshold voltage measured at a supply voltage (high drain voltage), \({V}_{t}^{Low}\,\)is the threshold voltage measured at a very low drain voltage, V DD is the supply voltage (high drain voltage), \({V}_{D}^{Low}\) is the low drain voltage. Here we use drain biases of 0.1 V and 1.1 V to extract the DIBL. Figure 5e shows the DIBL of the back-gated WSe2 transistor as a function of the channel length. The upturn of the DIBL does not show up until the channel length is shorter than 0.4 µm. Since the back-gate oxide is very thick (280 nm in this case), the electrostatic scaling length is very long. The electrostatic scaling length can be estimated by the equation \(\lambda =\sqrt{{t}_{ox}{t}_{s}{\varepsilon }_{s}/{\varepsilon }_{ox}}\), where t ox is the oxide thickness, t s is the semiconductor thickness, ε s is the semiconductor dielectric constant, and ε ox is the oxide dielectric constant34,35. For the back-gated WSe2 transistors, assuming t ox = 280 nm, t s ≈ 0.54 nm, ϵ s ≈ 7, and ϵ ox ≈ 3.9, respectively, the electrostatic scaling length is estimated as λ ≈ 0.064 μm. For a planar device, the minimum channel length needed to preserve the long-channel behavior is typically 4–5 times the electrostatic scaling length, which corresponds to L = 0.26~0.32 μm in this case. This is consistent with our DIBL results, which reveal that the short-channel effect starts to show up when the channel is shorter than 0.4 μm. As the energy barrier between source and drain reduces, the drain current will increase exponentially. This explains the dramatic increase of the drain current at high drain voltages in the ID~VD plots for the short-channel transistors, shown in Fig. 4b.

Short-channel effect in WSe2 transistors. (a) SEM image of a WSe2 TLM structure consisting of five transistors with various channel lengths. (b) Conductance as a function of gate voltage in a long-channel transistor (L = 5 µm) measured at various drain voltages. (c) Conductance as a function of gate voltage in a short-channel transistor (L = 0.1 µm) measured at various drain voltages. (d) Threshold voltage as a function of drain voltage for WSe2 transistors with various channel lengths from 0.1 µm to 5 µm. (e) Drain-induced barrier lowering (DIBL) of the WSe2 transistors as a function of channel length.

Carrier mobility in CVD WSe2

The carrier mobility is an important indicator of the quality of the semiconductor. The carrier mobility of the CVD WSe2 is studied in the long-channel transistors to eliminate the possible short-channel effects, and the conductances were measured using the four-point method to minimize the impact of the contact resistances. Figure 6a shows the SEM image of a typical Hall-bar device. The four-point conductance as a function of gate voltage measured of a WSe2 Hall-bar device at various temperatures is shown in Fig. 6b. Note the SEM and conductance are taken on two separate devices with the same layout on the same wafer to avoid the impact of SEM scan on the electrical performance of the device. The field-effect mobility is extracted from the four-point conductance, using the equation \(\mu =\frac{1}{(W/L){C}_{ox}}\frac{\partial \sigma }{\partial {V}_{G}}\), where σ is the four-point conductance, V G is the gate voltage, W is channel width, L is the channel length, and C ox is the oxide capacitance36. The extracted field effect mobility as a function of gate voltage is shown in Fig. 6c. As the transistor is biased further into the inversion, the mobility increases because of the screening effect due to the inversion charge, which reduces the Coulomb scattering. The temperature dependence of the mobility shows a turn-around behavior at 250 K, shown in Fig. 6d. At low temperatures, the mobility increases with increasing temperature, and at temperatures above 250 K, the mobility decreases with increasing temperature. At low temperatures, Coulomb scattering dominates. When the temperature increases, the carrier velocity increases, which can reduce the influence of the Coulomb scattering from the charged impurities. At high temperatures, phonon scattering dominates. Increasing temperature will increase the lattice vibration and reduce the mobility. Seven Hall-bar devices were measured to determine the mobility and carrier density. At V G − V T = −30 V, i.e. carrier density of ~2.3 × 1012 cm−2, the average mobility is ~24.8 cm2/V-s, the maximum mobility is 46.1 cm2/V-s, and the minimum mobility is 7.9 cm2/V-s. Note, these electrical characteristics were measured after source/drain formation and before the channel is etched into rectangular shape. After the sample experienced additional process steps, including lithography, oxygen plasma etching and resist strip, and additional characterizations such as SEM, the measured mobilities of the Hall-bar devices are significantly lower, as shown in Fig. S1 in the supplementary information. One possible cause of this mobility degradation is that the additional process steps and the high-energy electron beam in SEM degraded the monolayer WSe2 channel. The other possible reason for the lower extracted mobility after channel-cut is that there are parasitic current path in the triangular-shaped channel before the channel-cut, which may cause overestimation of the channel mobility. The gate voltage and temperature dependence of the channel mobilities in a WSe2 Hall-bar devices after channel-cut and SEM scan are shown in Fig. S2. The mobilities of the WSe2 device after channel-cut show similar temperature and gate voltage dependence as the one before the channel-cut.

Carrier mobility of CVD WSe2. (a) SEM image of a WSe2 Hall-bar device. (b) Four-point conductance as a function of gate voltage measured at various temperatures. (c) Extracted field-effect mobility as a function of gate overdrive, V G − V T , at various temperatures. (d) Temperature dependence of the field-effect mobility at various gate overdrives.

Interface states of the WSe2 transistors

The interface trap density is another key parameter for semiconductors, which directly impacts the performance of metal-oxide field-effect transistors (MOSFETs), tunneling field-effect transistors (TFETs), and tunneling diodes. The interface trap density of the CVD WSe2 is evaluated by measuring the subthreshold swing at various temperatures on the long-channel transistors. Figure 7a shows the ID~VD curves measured at various temperatures for a transistor with gate length L = 5 μm. The subthreshold swing is defined as the gate voltage required to vary the subthreshold current by one decade: \(SS=\partial {V}_{G}/\partial log({I}_{D})\), where I D is the drain current at the subthreshold regime. Figure 7b shows the measured subthreshold swing as a function of gate voltage. The subthreshold swing is typically a function of depletion capacitance, C D , and temperature. If there are interface states, an interface-state capacitance, C it , will be in parallel with the C D . Then the subthreshold swing can be modeled as \(SS=\frac{kT}{q}ln(10)(1+\frac{{C}_{D}+{C}_{it}}{{C}_{ox}})\)36. For transistors with atomically thin channel (monolayer WSe2), it is assumed that the device is fully depleted and C D ≈ 0. Then the interface capacitance, C it , can be extracted. The interface trap density is related to C it by the equation \({D}_{it}=\frac{{C}_{it}}{q}\), where q is the elementary charge. Figure 7c shows the extracted interface trap density, D it , as a function of gate overdrive, V G − V T , at various temperatures. As the gate overdrive, V G − V T , decreases, i.e. as the Fermi level at the WSe2/oxide interface approaches the valence band edge, the interface trap density increases, which is similar to the energy distribution of the interface traps in silicon.

Interface states in back-gated WSe2 transistors. (a) Two-point conductance as a function of gate voltage measured at various temperatures. (b) Subthreshold swing as a function of gate overdrive, V G − V T , at various temperatures. (c) Extracted interface trap density as a function of gate overdrive. (d) Temperature dependence of the threshold voltage. The inset illustrates the positive interface trapped charges located at the WSe2/oxide interface when the gate is biased at the threshold voltage.

The threshold voltages of these back-gated WSe2 transistors are also strongly dependent on the temperatures. Figure 7d shows the threshold voltage as a function of temperature. The threshold voltage increases monotonically as the temperature increases from 35 K to 300 K. This can be explained by the temperature dependence of the interface trapped charges. The interface state typically has two types: the donor-like and the acceptor-like interface states. The donor-like interface states are neutral when filled with electrons and positive when empty, whereas the acceptor-like interface states are negative when filled and neutral when empty. Assuming that the interface states below the midgap E i are donor-like, while those above E i are acceptor-like, similar to silicon, the interface states will be positively charged at threshold voltage in p-type transistors, where the Fermi level is below the midgap. This will result in a negative shift in the threshold voltage as compared to the one without interface states. As the temperature increases, the Fermi level is closer to the mid-gap at the threshold voltage, and the total amount of the positive trapped charges reduces, resulting in positive shift of the threshold voltages. The desorption of the moisture from the WSe2 surface as the samples warm up could also cause a threshold voltage shift in these back-gated transistors.

Conclusion

In summary, we have systematically investigated the synthesis of monolayer WSe2 using CVD and studied the electric transport of CVD WSe2. We found that short-channel effect plays an important role in the back-gated WSe2 transistors when the channel length is in the sub-micrometer regime. The drain-induced barrier lowering can result in variations of the threshold voltages and over- or under-estimation of the carrier mobilities. This short-channel effect can also lead to misjudgment of the metal contacts, as the output characteristics of a transistor with ohmic contacts can show Schottky-like behavior. For back-gated WSe2 transistors with 280 nm gate oxide, the DIBL starts to show an upturn when the channel length is shorter than 0.4 µm. This extremely long electrostatic scaling length is due to the thick oxide. These findings will be very important for accurate and unified characterization and analysis of 2D electronic devices with back-gate structures. In addition, we also found that the hydrogen flow rate and the amount of WO3 precursor can significantly influence the morphology of the WSe2. Large work function metal Pd forms ohmic contact to the monolayer WSe2. The interface trap density of WSe2 was extracted from the subthreshold swings. The interface trap density of CVD WSe2 increases as the energy level approaches the valence band edge. These findings will enrich the knowledge of electric transport in CVD WSe2 and the scaled electronic devices based on monolayer TMDCs.

References

Jin, Z. H., Li, X. D., Mullen, J. T. & Kim, K. W. Intrinsic transport properties of electrons and holes in monolayer transition-metal dichalcogenides. Physical Review B 90 (2014).

Das, S. & Appenzeller, J. WSe2 field effect transistors with enhanced ambipolar characteristics. Appl Phys Lett 103 (2013).

Chuang, H. J. et al. Low-Resistance 2D/2D Ohmic Contacts: A Universal Approach to High-Performance WSe2, MoS2, and MoSe2 Transistors. Nano Letters 16, 1896–1902 (2016).

Podzorov, V., Gershenson, M. E., Kloc, C., Zeis, R. & Bucher, E. High-mobility field-effect transistors based on transition metal dichalcogenides. Appl Phys Lett 84, 3301–3303 (2004).

Pradhan, N. R. et al. Field-Effect Transistors Based on Few-Layered alpha-MoTe2. Acs Nano 8, 5911–5920 (2014).

Li, L. K. et al. Black phosphorus field-effect transistors. Nature Nanotechnology 9, 372–377 (2014).

Xia, F. N., Wang, H. & Jia, Y. C. Rediscovering black phosphorus as an anisotropic layered material for optoelectronics and electronics. Nature Communications 5 (2014).

Deng, Y. X. et al. Black Phosphorus-Monolayer MoS2 van der Waals Heterojunction p-n Diode. Acs Nano 8, 8292–8299 (2014).

Prakash, A. & Appenzeller, J. Bandgap Extraction and Device Analysis of Ionic Liquid Gated WSe2 Schottky Barrier Transistors. Acs Nano 11, 1626–1632 (2017).

Agnihotri, P., Dhakras, P. & Lee, J. U. Bipolar Junction Transistors in Two-Dimensional WSe2 with Large Current and Photocurrent Gains. Nano Letters 16, 4355–4360 (2016).

Burg, G. W. et al. Coherent Interlayer Tunneling and Negative Differential Resistance with High Current Density in Double Bilayer Graphene–WSe2 Heterostructures. Nano Letters 17, 3919–3925 (2017).

Wang, J. J. et al. Gate-modulated conductance of few-layer WSe2 field-effect transistors in the subgap regime: Schottky barrier transistor and subgap impurity states. Appl Phys Lett 106 (2015).

Pradhan, N. R. et al. Hall and field-effect mobilities in few layered p-WSe2 field-effect transistors. Sci Rep-Uk 5 (2015).

Das, S., Dubey, M. & Roelofs, A. High gain, low noise, fully complementary logic inverter based on bi-layer WSe2 field effect transistors. Appl Phys Lett 105 (2014).

Chuang, H.-J. et al. High Mobility WSe2 p- and n-Type Field-Effect Transistors Contacted by Highly Doped Graphene for Low-Resistance Contacts. Nano Letters 14, 3594–3601 (2014).

Tosun, M. et al. High-Gain Inverters Based on WSe2 Complementary Field-Effect Transistors. Acs Nano 8, 4948–4953 (2014).

Movva, H. C. P. et al. High-Mobility Holes in Dual-Gated WSe2 Field-Effect Transistors. Acs Nano 9, 10402–10410 (2015).

Yu, L. et al. High-Performance WSe2 Complementary Metal Oxide Semiconductor Technology and Integrated Circuits. Nano Letters 15, 4928–4934 (2015).

Kim, H. J., Kim, D. H., Jeong, C. Y., Lee, J. H. & Kwon, H. I. Determination of Interface and Bulk Trap Densities in High-Mobility p-type WSe2 Thin-Film Transistors. Ieee Electron Device Letters 38, 481–484 (2017).

Resta, G. V. et al. Polarity control in WSe2 double-gate transistors. Sci Rep-Uk 6 (2016).

Liu, W. et al. Role of Metal Contacts in Designing High-Performance Monolayer n-Type WSe2 Field Effect Transistors. Nano Letters 13, 1983–1990 (2013).

Xu, S. G. et al. Universal low-temperature Ohmic contacts for quantum transport in transition metal dichalcogenides. 2d Materials 3 (2016).

Liu, B. L. et al. Chemical Vapor Deposition Growth of Monolayer WSe2 with Tunable Device Characteristics and Growth Mechanism Study. Acs Nano 9, 6119–6127 (2015).

Zhou, H. L. et al. Large Area Growth and Electrical Properties of p-Type WSe2 Atomic Layers. Nano Letters 15, 709–713 (2015).

Huang, J.-K. et al. Large-Area Synthesis of Highly Crystalline WSe2 Monolayers and Device Applications. Acs Nano 8, 923–930 (2014).

Clark, G. et al. Vapor-transport growth of high optical quality WSe2 monolayers. Apl Materials 2 (2014).

Eichfeld, S. M., Colon, V. O., Nie, Y. F., Cho, K. & Robinson, J. A. Controlling nucleation of monolayer WSe2 during metal-organic chemical vapor deposition growth. 2d Materials 3 (2016).

Eichfeld, S. M. et al. Highly Scalable, Atomically Thin WSe2 Grown via Metal-Organic Chemical Vapor Deposition. Acs Nano 9, 2080–2087 (2015).

Wang, Q. H., Kalantar-Zadeh, K., Kis, A., Coleman, J. N. & Strano, M. S. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. Nature Nanotechnology 7, 699–712 (2012).

Ross, J. S. et al. Electrically tunable excitonic light-emitting diodes based on monolayer WSe2 p-n junctions. Nature Nanotechnology 9, 268–272 (2014).

Baugher, B. W. H., Churchill, H. O. H., Yang, Y. F. & Jarillo-Herrero, P. Optoelectronic devices based on electrically tunable p-n diodes in a monolayer dichalcogenide. Nature Nanotechnology 9, 262–267 (2014).

Pospischil, A., Furchi, M. M. & Mueller, T. Solar-energy conversion and light emission in an atomic monolayer p-n diode. Nature Nanotechnology 9, 257–261 (2014).

Zeng, H. L. et al. Optical signature of symmetry variations and spin-valley coupling in atomically thin tungsten dichalcogenides. Sci Rep-Uk 3 (2013).

Yan, R. H., Ourmazd, A. & Lee, K. F. Scaling the Si Mosfet - from Bulk to Soi to Bulk. IEEE Transactions on Electron Devices 39, 1704–1710 (1992).

Majumdar, A., Ren, Z. B., Koester, S. J. & Haensch, W. Undoped-Body Extremely Thin SOI MOSFETs With Back Gates. IEEE Transactions on Electron Devices 56, 2270–2276 (2009).

Hori, T. Gate dielectrics and MOS ULSIs: principles, technologies, and applications. (Springer, 1997).

Acknowledgements

The authors would like to acknowledge the support from NSF ECCS 16-53241 CAR.

Author information

Authors and Affiliations

Contributions

Z.Y. synthesized the WSe2 film by CVD, designed, fabricated and measured the devices. J.L. carried out the AFM measurement and participated the device fabrication. K.X. did the metal evaporation, lift-off, SEM and part of electrical characterization. E.C. carried out the ebeam lithography and metal deposition. W.Z. initiated the project, performed electrical characterization and wrote the manuscript with input from Z.Y.

Corresponding author

Ethics declarations

Competing Interests

The authors declare no competing interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Yao, Z., Liu, J., Xu, K. et al. Material Synthesis and Device Aspects of Monolayer Tungsten Diselenide. Sci Rep 8, 5221 (2018). https://doi.org/10.1038/s41598-018-23501-4

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-018-23501-4

This article is cited by

-

Improved growth control of atomically thin WSe2 flakes using pre-deposited W source

Journal of Materials Science: Materials in Electronics (2021)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.