Abstract

The three dimensional inverters were fabricated using novel complementary structure of stacked bottom n-type aluminum-doped zinc oxide (Al:ZnO) thin-film transistor and top p-type nickel oxide (NiO) thin-film transistor. When the inverter operated at the direct voltage (VDD) of 10 V and the input voltage from 0 V to 10 V, the obtained high performances included the output swing of 9.9 V, the high noise margin of 2.7 V, and the low noise margin of 2.2 V. Furthermore, the high performances of unskenwed inverter were demonstrated by using the novel complementary structure of the stacked n-type Al:ZnO thin-film transistor and p-type nickel oxide (NiO) thin-film transistor.

Similar content being viewed by others

Introduction

Recently, in view of the inherent advantages of the direct wide bandgap energy and the high radiation hardness, the transparent metal oxide materials were widely used in electronic devices1,2, optoelectronic devices3,4, and sensors5,6. To prevent the influence of the generated current induced by the visible light, the transparent metal oxide materials were used for fabricating thin-film transistors (TFTs) and applying in display systems7,8,9,10,11. In the past decades, the transparent p-type and n-type thin-film transistors were respectively demonstrated and applied in various systems12,13,14. To simplify integrated circuit design and reduce power consumption, the complementary electronic devices become the basic structure in practical circuits. In the recent years, the complementary thin-film electronic devices and the hybrid complementary metal-oxide-semiconductor thin-film devices were reported, previously15,16. Furthermore, the three-dimensionally stacked n-type a-In-Ga-Zn-O and p-type poly-(9,9-dioctylfluorene-co-bithiophene) complementary thin-film transistor was reported17. Since the nickel oxide (NiO) thin films exhibit transparent p-type properties and have high bandgap energy from 3.6 eV to 4.0 eV, they have been used in organic and dye-sensitized solar cells18, organic light-emitting diodes19, and electrochemical devices20. Furthermore, because the aluminum-doped zinc oxide (Al:ZnO) thin films exhibit transparent n-type properties and have high bandgap energy from 3.2 eV to 3.6 eV, they have been used in transparent electrodes21, electrooptical devices22, and electronic devices23. In this work, the complementary thin-film transistors (CTFTs) were constructed by p-type TFTs and n-type TFTs fabricated using the NiO channel layer and the Al:ZnO channel layer, respectively. Moreover, to minimize the device area, the three-dimensional stacked structure of the CTFTs was proposed and applied as inverters.

Results

Characteristics of n-type Al:ZnO TFTs and p-type NiO TFTs

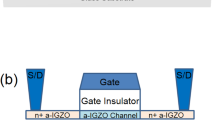

In the three dimensional-stacked CTFT inverter, the top p-type NiO TFT was stacked on the bottom n-type Al:ZnO TFT as shown in Fig. 1(a). The schematic diagram of the three dimensional-stacked complementary thin-film transistor inverter circuit was shown in Fig. 1(b). To study the characteristics, the bottom n-type Al:ZnO TFTs and the top p-type NiO TFTs were respectively measured using an Agilent 4156 C semiconductor parameter analyzer at a room temperature. Figure 2(a) shows the dependence of the drain-source current (IDSn) on the drain-source voltages (VDSn) of the bottom n-type Al:ZnO TFTs operated at various gate-source voltages (VGSn). It was found that the associated saturation drain-source current (IDSSn) at a VDSn of 10 V and a VGSn of 10 V was 77 μA. In general, the drain-source current (IDS) as a function of the gate-source voltage (VGS) of TFTs operated at the saturation region can be expressed as:

where μFE is the effective field-effect mobility, Cox is the capacitance per unit gate insulator area, VTH is the threshold voltage, W and L are the channel width and the channel length, respectively. According to the measured IDSn-VDSn characteristics, the (IDSn)½ and the IGSn as a function of the VGSn of the bottom n-type Al:ZnO TFTs operated at VDSn = 10 V were shown in Fig. 2(b). By plotting the (IDSn)½ versus VGSn and extrapolating the linear line to the VGSn axis, the intercept value is the associated threshold voltage. It could be found that the threshold voltage of the bottom n-type Al:ZnO TFTs was 3.4 V. When the TFTs operated at VDSn of 10 V and VGSn of 10 V, the associated gate leakage current and the on-to-off current ratio were 2.7 pA and 2.9 × 106, respectively. By defining the subthreshold swing (S) as S = dVGS/d (log IDS), the S value of the bottom n-type Al:ZnO TFTs was 0.78 V/decade.

The measured IDSp-VDSp characteristics of the top p-type NiO TFTs operated at various VGSp were shown in Fig. 3(a). Furthermore, the associated (IDSp)½ and IGSp as a function of the VGSp were shown in Fig. 3(b). It was found that the saturation drain-source current (IDSSp) and the gate leakage current were −77 μA and −8.9 pA, respectively, when the top p-type Ni TFTs operated at a VDSp of −10 V and a VGSp of −10 V. The associated on-to-off current ratio was 1.5 × 106. The associated threshold voltage and subthreshold swing were −3.7 V and 0.56 V/decade, respectively. Table 1 listed the performance summary of the n-type Al:ZnO TFTs and the p-type NiO TFTs.

Three dimensional stacked inverters of complementary thin-film transistors

Using the above-mentioned inverter of the stacked bottom n-type Al:ZnO TFT and top p-type NiO TFT shown in Fig. 1(a) and (b), Fig. 4 shows the load line characteristics of the inverters operated at a VDD of 10 V and an input voltage from 0 V to 10 V. The quiescent point of the inverter located at the intersection point of the load line characteristics of the n-type TFT and the p-type TFT. As shown in Fig. 1(b), when the input voltage of the inverter was 0 V, the bottom n-type Al:ZnO TFT (driver) operated at the cutoff region due to the VGSn = 0 V. Consequently, the highest output voltage (VOH) of the inverter was eventually equal to 10 V. When the input voltage increased, the VGSn increased and the |VGSp| = |VGSn − VDD| decreased. Consequently, the IDSn increased and the |IDSp| deceased. As shown in Fig. 4, since the IDSn was equal to the |IDSp|, it was worth to note that the output voltage was forced to be decreased. When the input voltage Vin = VGSn was 10 V (i.e VGSp = 0 V), the lowest output voltage (VOL) was 0.1 V. Since the VOH and VOL of the inverter was 10 V and 0.1 V, the corresponded output swing (VOH − VOL) was 9.9 V. Figure 5 shows static Vout − Vin transfer characteristics of the inverter operated at the VDD of 10 V and the input voltage from 0 V to 10 V. The input high voltage (VIH) and the input low voltage (VIL) were defined as at the point with the slope of −1 in Fig. 5. When the high noise margin (NMH) was defined as VOH − VIH, and the low noise margin (NML) was defined as VIL − VOL, the NMH and NML of the inverter were 2.7 V and 2.2 V, respectively. As shown in Fig. 5, when the output voltage Vout = VDD/2, the operated input voltage Vin was 4.9 V, which very closed to the Vout = VDD/2 = 5 V. This experimental result indicated that the three dimensional stacked complementary thin-film transistors could work as an unskewed inverter.

When an input pulse voltage from 0 V to 10 V was applied to the inverter operated at VDD = 10, the output voltage was shown in Fig. 6. It was found that the output voltage could quite response with the input pulse voltage. The response time of the output voltage was about 2 μs. It was expected that the inverter could be operated at 500 kHz.

Discussion

In this work, the inverter was constructed using the three dimensional stacked bottom n-type Al:ZnO TFTs and top p-type NiO TFTs. In the inverter, the n-type TFTs and the p-type TFTs worked as the driver and the load, respectively. When the inverter operated at the VDD of 10 V and the input voltage from 0 V to 10 V, the performances of unskewed inverter were resulted. Furthermore, the output swing voltage of 9.9 V, the high noise margin of 2.7 V and the low noise margin of 2.2 V in the inverter were obtained. Since the three dimensional stacked structure could minimize the area of the complementary thin-film transistors, it would be the promising candidate structure in systems. As our best knowledge, the three dimensional stacked structure is the first reported three dimensional complementary thin-film transistors.

When the SiO2 insulator and the Ni, Au and Al metals used in the inverters were replaced using transparent metal oxide insulator and the transparent conducting metal oxide electrode, the transparent n-type and p-type TFTs could be obtained. Consequently, the transmittance of the resulting TFTs could be improved. Since the p-type ZnO TFTs were previously demonstrated12, the total ZnO-based CTFTs could be achieved by replacing the p-type NiO TFTs using the p-type ZnO TFTs. Furthermore, in view of the high performance and the high stability TFTs using ZnO-based materials, such as quaternary indium gallium zinc oxide24 and quinary indium gallium zinc aluminum oxide25, the performances of the CTFTs could be further improved by using those materials as the channel layer of TFTs. Because the flexible devices became prevalent candidate in application of systems, the CTFTs were fabricated on flexible substrates would be a promising study topic. In the display system, the transparent TFTs can replace the conventional shadowy TFTs to improve the transparency and aspect of pixel. Furthermore, if the complementary thin-film transistors were used to replace the convention TFTs, the switch performance and the power consumption of pixel were improved. To reduce the occupied area of TFTs in pixel, the stacked complementary thin-film transistors could reduce the occupied area compared with that of the planar-structured complementary thin-film transistors. The complementary device was the basic structure of integrated circuits. Therefore, the proposed stacked complementary thin-film transistors studied in this work can be expected to be used in three dimensional integrated circuits and reduced the occupied area of the complementary thin-film transistors.

Method

Preparation of inverter using stacked n-type Al:ZnO TFTs and p-type NiO TFT

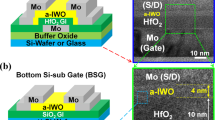

To fabricate the bottom n-type Al:ZnO TFT on glass substrate, an AZ6112 photoresist was spread on glass substrates. The gate window (gate length = 30 μm and gate width = 200 μm) was opened by a standard photolithography technique. The gate metals of Ni/Au (20 nm/70 nm) were deposited using an electron beam evaporator and formed using a lift off process. After depositing a 140-nm-thick SiO2 insulator layer using a radio frequency (RF) magnetron cosputter, a 30-nm-thick Al:ZnO channel layer of the bottom n-type TFTs was deposited using the RF magnetron cosputter system with dual targets of Al target and ZnO target. The Al:ZnO channel layer was deposited with the sputtered RF power of 100 W applied to the ZnO target and the sputtered RF power of 30 W applied to the Al target under an argon flow rate of 30 sccm and a working pressure of 75 mtorr. Using the Hall measurement at room temperature, the electron concentration and the electron mobility of the Al:ZnO layer were 8.3×1016 cm−3 and 12.2 cm2/V-s, respectively. When the AZ6112 photoresist was spread on the sample, the source window and the drain window were opened by the standard photolithography technique. The distance between the source window and the drain window was 10 μm. The width of both the windows was 100 μm. The source metals and the drain metals of Ni/Au (20 nm/70 nm) were deposited using the electron beam evaporator and formed using the lift off process. To form ohmic contact, the sample was annealed in a pure nitrogen ambient furnace at 200 °C for 3 minutes. Furthermore, the RF magnetron cosputter was used to deposit a 250-nm-thick SiO2 insulator layer to separate the bottom TFT and the followed top TFT in the three-dimensional stacked CTFT inverter.

The fabrication process and the dimension of the stacked top p-type NiO TFTs were the same as the above-mentioned bottom n-type Al:ZnO TFTs. However, in the top p-type NiO TFTs, the 130-nm-thick Al metal and the 30-nm-thick NiO layer were used as the gate electrode and the channel layer, respectively. The 160-nm-thick SiO2 insulator layer was deposited between the Al gate electrode and the NiO channel layer using RF magnetron cosputter. The NiO layer was deposited by the RF magnetron sputter with sputtered RF power of 125 W applied to the Ni target under working pressure of 10 mtorr and N2/O2 flow rate of 10 sccm/40 sccm. Using the Hall measurement at room temperature, the hole concentration and the hole mobility of the p-type NiO layer were 1.81×1016 cm−3 and 2.22 cm2/V-s, respectively. To form the source and drain electrodes of the p-type NiO TFTs, the Ni/Au (20 nm/ 120 nm) metals were deposited using an electron beam evaporator and patterned using a lift-off process. After fabricating the top p-type NiO TFT stacked on the bottom n-type Al:ZnO TFT worked as an inverter, the input port was formed by interconnecting the gate electrode of the p-type NiO TFT with the gate electrode of the n-type Al:ZnO TFT. Moreover, the output port of the inverter was formed by interconnecting the drain electrode of the p-type NiO TFT with the drain electrode of the p-type Al:ZnO TFT. After spreading AZ6112 photoresist on the front side of the top p-type NiO TFTs, the windows of the surrounding region of the drain electrode and the gate electrode were opened using the standard photolithography technique. After the materials under windows were etched, a thick Al metal was deposited as the interconnection metal by an electron beam evaporator. Figure 7 shows the transmission electron microscope image of the extended cross-sectional view of the inverter.

References

Lin, T. S. & Lee, C. T. Homostructured ZnO-based metal-oxide-semiconductor field-effect transistors deposited at low temperature by vapor cooling condensation system. Appl. Surf. Sci. 354, 71–73 (2015).

Kazuto, K. et al. Characteristics of Zn0.7Mg0.3O/ZnO heterostructure field-effect transistors grown on sapphire by molecular-beam epitaxy. Appl. Phys. Lett. 87, 112106-1–112106-3 (2005).

Lee, C. T. Fabrication methods and luminescent properties of ZnO materials for light-emitting diodes. Materials 3, 2218–2259 (2010).

Soci, C. et al. ZnO nanowire UV photodetectors with high internal gain. Nano Lett. 7, 1003–1009 (2007).

Lee, C. T. & Chiu, Y. S. Piezoelectric ZnO-nanorod-structured pressure sensors using GaN-based field-effect-transistor. Appl. Phys. Lett. 106, 073502-1–073502-3 (2015).

Zhao, Y. et al. Biomolecule-adsorption-dependent piezoelectric output of ZnO nanowire nanogenerator and its application as self-powered active biosensor. Biosens. Bioelectron. 57, 269–275 (2014).

Hoffman, R. L., Norris, B. J. & Wager, J. F. ZnO-based transparent thin-film transistors. Appl. Phys. Lett. 82, 733–735 (2003).

Nomura, K. et al. Thin-film transistor fabricated in single-crystalline transparent oxide semiconductor. Science 300, 1269–1272 (2003).

Nomura, K., Ohta, H., Takagi, A. & Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors. Nature 432, 488–492 (2004).

Lee, C. T., Lin, Y. H. & Lin, J. H. High stability mechanisms of quinary indium gallium zinc aluminum oxide multicomponent oxide films and thin film transistors. J. Appl. Phys. 117, 045309-1–045309-7 (2015).

Ofuji, M. et al. Fast thin transistor circuits based on amorphous oxide semiconductor. IEEE Electron Device Lett. 28, 273–275 (2007).

Lee, C. T. & Lin, Y. H. P-type ZnO thin-film transistors and passivation using photoelectrochemical oxidation method. Appl. Phys. Express 7, 076502-1–076502-3 (2014).

Yabuta, H. et al. Sputtering formation of p-type SnO thin film transistors on glass toward oxide complementary circuits. Appl. Phys. Lett 97, 072111-1–072111-3 (2010).

Lin, Y. H. & Lee, C. T. High stability performance of quinary indium gallium zinc aluminum oxide films and thin-film transistors deposited using vapor cooling condensation method. J. Electron. Mater. 46, 5209–5214 (2017).

Bowen, W. E., Wang, W. & Phillips, J. D. Complementary thin-film electronics based on n-channel ZnO and p-channel ZnTe. IEEE Electron Device Lett. 30, 1314–1316 (2009).

Perez, M. R. et al. Hybrid CMOS thin-film devices based on solution-processed CdS n-TFTs and TIPS-pentacene p-TFTs. Org. Electron. 13, 3045–3049 (2012).

Nomura, K. et al. Three-dimensionally stacked flexible integrated circuit: Amorphous oxide/polymer hybrid complementary inverter using n-type a-In–Ga–Zn–O and p-type poly-(9,9-dioctylfluorene-co-bithiophene) thin-film transistors. Appl. Phys. Lett. 96, 263509-1–263509-3 (2010).

Qin, P. et al. High incident photon-to-current conversion efficiency of p-type-dye-sensitized solar cells based on NiO and organic chromophores. Adv. Mater. 21, 2993–2996 (2009).

Im, H. C. et al. Highly efficient organic light-emitting diodes fabricated utilizing nickel-oxide buffer layers between the anodes and the hole transport layers. Thin Solid Films 515, 5099–5102 (2007).

Lou, X. C., Zhao, X. J., Xiong, Y. L. & Sui, X. T. The influence of annealing on electrochemic properties of Al-B-NiO thin films prepared by sol-gel. J. Sol-Gel Sci. Technol. 54, 43–48 (2010).

Lee, H. Y., Chou, Y. H., Lee, C. T., Yeh, W. Y. & Chu, M. T. Mechanisms of lighting enhancement of Al nanoclusters-embedded Al-doped ZnO film in GaN-based light-emitting diodes. J. Appl. Phys. 107, 014503-1–014503-5 (2010).

Singh, S. & Park, S. H. Fabrication and characterization of Al:ZnO based MSM ultraviolet photodetectors. Superlattices Microstruct. 86, 412–417 (2015).

Lee, W. H., Kim, E. J. & Yoon, S. M. Multilevel resistive-change memory operation of Al-doped ZnO thin-film transistor. IEEE Electron Device Lett. 37, 1014–1017 (2016).

Lee, H. Y., Ye, W. Y., Lin, Y. H., Lou, L. R. & Lee, C. T. High performance bottom-gate type amorphous InGaZnO flexible transparent thin-film transistors deposited on PET substrates at low temperature. J. Electron. Mater. 43, 780–785 (2014).

Lin, Y. H. & Lee, C. T. High stability performances of quinary indium gallium zinc aluminum oxide films and thin-film transistors deposited using vapor cooling condensation method. J. Electron. Mater. 46, 5209–5214 (2017).

Acknowledgements

This work was supported by the Ministry of Science and Technology of the Republic of China under contract no. MOST-105-2221-E-006-199-MY3.

Author information

Authors and Affiliations

Contributions

C. T. Lee conceived the study and participated in design and coordination. H. Y. Lee and C. C. Chen carried out experiments. All authors drafted read and approved the final manuscript.

Corresponding author

Ethics declarations

Competing Interests

The authors declare no competing interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Lee, CT., Chen, CC. & Lee, HY. Three dimensional-stacked complementary thin-film transistors using n-type Al:ZnO and p-type NiO thin-film transistors. Sci Rep 8, 3968 (2018). https://doi.org/10.1038/s41598-018-22430-6

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-018-22430-6

This article is cited by

-

High performance perovskite solar cells using multiple hole transport layer and modulated FAxMA1−xPbI3 active layer

Journal of Materials Science: Materials in Electronics (2020)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.