Abstract

Emerging nanoionic memristive devices are considered as the memory technology of the future and have been winning a great deal of attention due to their ability to perform fast and at the expense of low-power and -space requirements. Their full potential is envisioned that can be fulfilled through their capacity to store multiple memory states per cell, which however has been constrained so far by issues affecting the long-term stability of independent states. Here, we introduce and evaluate a multitude of metal-oxide bi-layers and demonstrate the benefits from increased memory stability via multibit memory operation. We propose a programming methodology that allows for operating metal-oxide memristive devices as multibit memory elements with highly packed yet clearly discernible memory states. These states were found to correlate with the transport properties of the introduced barrier layers. We are demonstrating memory cells with up to 6.5 bits of information storage as well as excellent retention and power consumption performance. This paves the way for neuromorphic and non-volatile memory applications.

Similar content being viewed by others

Introduction

Resistive memory devices, also known as memristors1, are nowadays attracting considerable attention due to the breadth of potential applications ranging from non-volatile memory2 to neuromorphic systems3,4 and reconfigurable circuits5. Their competitive advantage over established complementary metal-oxide-semiconductor (CMOS)-based memory stems from their capability to support a multitude of states, long retention characteristics, fast switching and ultra-low power consumption6. Many technologies have been put forward as potential winners of the non-volatile memory race7, namely phase-change (PCRAM)8, magnetic (MRAM)9 and resistive random access memory (ReRAM)10. Although MRAM and PCRAM are considered more reliable, they are constraint by power and/or scalability issues11,12. In contrast, ReRAM has shown capacity of operating in the femtojoule regime13, with functional devices reported at feature sizes that outperform CMOS14,15. However, even though the realisation of bistable memory devices (1-bit) is apparent from the very nature of the memristor to variate between two resistive states16 the implementation of a device that can reliably be programmed at a multitude of distinct resistive states still poses a significant challenge. Although there are some recent reports of multibit capable metal-oxide memory cells17, most works in literature are limited to no more than 3 bits18,19,20,21,22.

Resistive switching has been observed in many metal-oxide systems23, with Ta2O5 24,25, HfO2 26 and TiO2 27,28 being among the most popular. In all cases, the origin of switching has been attributed to either the drift of oxygen vacancies28 and/or interstitials29 or the formation of conductive filaments30 within an active metal-oxide core under the influence of an applied electrical field. Within that context several studies have reported on the importance of interface interactions and properties31, showing that the introduction of a thin interfacial barrier layer between the active layer and one of the electrodes can influence the electrochemical processes, the devices’ stability32,33, improve its switching characteristics and reduce the overall power consumption34,35,36,37.

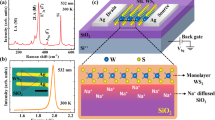

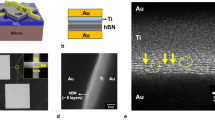

Taking into advantage these observations, we developed a series of 2-terminal prototype metal-insulator-metal (MIM) ReRAM cells, as depicted in Fig. 1a–c, with bilayer structure using TiO2 as solid electrolyte and seven different interface barrier layer configurations; all employing Pt top and bottom electrodes. The active layers studied were: 1) TiO2-only, 2) AlxOy/TiO2, 3) TaxOy/TiO2, 4) SiO2/TiO2, 5) ZnO/TiO2, 6) HfOx/TiO2 and 7) WOx/TiO2. For all fabricated devices the thickness was maintained to 4 nm and 40 nm for the barrier and TiO2 layer respectively. The size of the devices used in this paper is 20 × 20 μm2. The TiO2 layer is amorphous and stoichiometric as more details can be found in our previous38,39. Smaller and larger area devices, namely 10 × 10 μm2 and 20 × 20 μm2, were considered but no apparent impact on the multibit performance was observed. All prototypes were electroformed with 1 μs pulses of negative polarity ranging from −3 to −12 V in steps of 100 mV, to an operational resistive state range, typically between 20–150 kΩ, depending on the stack configuration (see Supplementary Fig. S1). Figure 1d,e illustrate the difference in resistive programming stability between the TiO2-only and AlxOy/TiO2 ReRAM cells. In both cases, 100 ns pulse ramps of alternating polarity from 1 to 2 V with 200 mV step are used as input stimulus. Considerable drift in programming can be observed in Fig. 1d for the TiO2-only devices, which practically results into non-discernible memory states even after 20 switching cycles. Although the stability of TiO2-only devices can be further optimised at the expense of programing energy (see Supplementary Fig. S2), the comparable AlxOy/TiO2 cells indicate a more stable behaviour, as observed in Fig. 1e, overall maintaining a constant OFF/ON resistive ratio throughout the experiment. The more clear definition of low and high resistive states is similar to what Yu et al. have reported for the HfOx/AlOx system34 in comparison to the respective single layer cell.

Comparison between TiO2-only devices and AlxOy/TiO2 bilayer devices. (a) SEM micrograph of a memristor device; (b) Schematic representation of a single layer TiO2-based device with platinum top and bottom electrodes; (c) Schematic representation of a bilayer AlxOy/TiO2-based device with platinum top and bottom electrodes; (d) Typical bipolar switching of a device based on the stack pictured in (b) using 100 ns pulses of alternating polarity voltage ramps ranging from 1 to 2 V, with voltage steps of 200 mV; (e) Typical bipolar switching of a device based on the stack pictured in (c) using 100 ns pulses of alternating polarity voltage ramps ranging from 1 to 2 V with voltage steps of 200 mV. The coloured horizontal lines in fig. (d) and (e) denote the average low (LRS) and high resistive state (HRS).

The need for stable and reliable switching at minute resistive increments becomes increasingly important if one wishes to exploit such cells as truly analogue memories. To that end, we evaluated all prototyped devices for their multistate capacity via biasing them with 100 ns pulses ranging from 1 to 2 V, at 50 mV steps. In every programming cycle, a new state is assumed to have been reached if two conditions are met. First, the resistive state is sufficiently stable over time, as evaluated by retention testing. Second, the lower bound of the standard deviation of a series of 50 × 0.5 V read pulses is at least 2σ higher than the upper bound of the previous state (see Methods and Supplementary Figs S3–S5 for more detail). Using this evaluation routine, we observed a significant increase in the number of attainable resistive states for the bilayer devices in contrast to the single-layer cells. While in the case of TiO2-only devices a maximum of 10 states on average was identified, the introduction of a barrier layer resulted into both increasing the number of resistive states significantly but also improving the dynamic response of the devices. Figure 2 summarises the switching performance of all developed bi-layer ReRAM cells both in terms of the number of attainable memory states and the resistive state dynamic range. All device prototypes that encompass an active bi-layer show improvements in both performance metrics.

Multibit evaluation of devices based on different barrier layer combinations. Number of attainable resistive states (left axis) and ratio of the final state resistance over the baseline resistance (right axis) for typical bilayer devices. Confidence interval for the state assessment is 2σ following the routine described in Supplementary Figs S4 and S5. A chart containing each individual state assessed for every bilayer combination can be found in Supplementary Figs S6 and S7.

The performance of the AlxOy/TiO2 devices is exemplified in Fig. 3a where a record number of 92 states is reported, which corresponds to a single cell with 6.5 bits memory capacity. This cumulative probability distribution function graph clearly illustrates the overall discernibility of the resistive states. Retention characteristics of a selection of states of a typical AlxOy/TiO2 device are shown in Fig. 3c,d over a period of 8 hours at room temperature and at 85 °C. It can be observed that the stored memory states are stable and remain clearly distinguishable even in the 30–40 kΩ range where the states are closely packed.

Multibit operation of a device using the AlxOy/TiO2 RRAM stack. (a) Cumulative probability distribution function plot of a device with a record of 92 distinct resistive states. All states are read at 0.5 V, are closely packed and individually discernible; (b) switching energy required to switch a typical AlxOy/TiO2 device. Only the energy expended during programming is regarded for this graph; (c) 8 hours retention measurements for select resistive states at room temperature. (d) 8 hours retention measurements for select resistive states at 85 °C. Resistance can be retained even at elevated temperatures.

The AlxOy/TiO2 combination proved to yield the best analogue performance given the “state expanse” figure of merit: (max{R/R o} × (# of states), where R o is the baseline resistance. The improved stability allows us the programming of such elements in an arbitrary manner, as shown in Fig. 4. More specifically, single 100 ns wide pulses at 2 V allow us to sequentially set the resistive state of the device gradually. Selection of a different memory state can be done by first “flushing” the device back to its baseline resistance (27.5 kΩ) via a train of 100 ns wide RESET pulses at −2 V and then applying a corresponding number of SET pulses to reach the desired memory state. The resistive state of the device can also be selected by modulating not only the number of pulses but the duration or the amplitude of the programming pulse. As Fig. 4 shows by modifying the duration of the pulse or the amplitude similar high resistive state to the sequential pulsing can be exhibited clearly illustrating the time-voltage dilemma. However the resolution of the device suffers as several resistance levels are suppressed. It is apparent that using smaller, more incremental and precise pulsing steps makes extracting more usable resistive states from the memory cell possible.

Programming the AlxOy/TiO2 device. Modes of selecting specific resistive states. Starting from a baseline resistance of ~27.5 kΩ a specific resistive state can be attained with different modes of programming, by modulating (i) the number of pulses, (ii) the duration of the pulses or (iii) the amplitude of the pulse. Using multiple pulses of lower amplitude and pulse width can help in pinpointing resistive states that otherwise could not have been discerned. In between the state selection the device is flushed with a series of 100 RESET pulses of 100 ns in duration.

The remarkable analogue memory performance and stability of states can be attributed to the specific ratio of the ionic transference numbers of the second oxide layer. By observation of the data shown in Fig. 2, a clear trend can be identified for the number of available states, whereas no particular trend on particular dependence can be observed. The highest number of stable non-volatile resistive states is achieved with the introduction of Al2O3, followed by Ta2O5, WO3, HfO2, ZnO and SiO2. It has been recently shown that many oxide thin films used for ReRAMs have mobile host cations29 and that as expected the oxidation state and stoichiometry of the matrix is also playing a significant role40. Mobility of cations and anions during high field oxide formation on metals using liquid electrolytes is well known from classical electrochemistry. In high voltages and low film thickness conditions, the transport is field-accelerated and the particular ionic transference numbers depend on the field. Al2O3 is identified as having the highest cation transference number, followed by Ta2O5, WO3 and HfO2 41,42,43. The identified trend in the data of Fig. 2 strictly correlates with the higher mobility of cations or lower mobility of oxygen ions, respectively. Similar effect of the oxygen mobility on the device stability has been reported for STO using barrier layers of Al2O3 (low O2− mobility) and yttria-stabilized ZrO2 (high O2− mobility)44. We can therefore conclude that the main factor influencing the observed device performance is attributed to the transport properties of the interfacial film added to the TiO2 layer.

It is important to mention that our characterisation routine foregoes the use of compliance current limiting, while toggling between resistive states. Current compliance limiting is a common practice that is used to control the size of the conductive filament and consequently the overall resistance of the device45,46. Instead, we have opted for a more direct approach by sequentially pulsing the device until its state stabilises. As the energy budget is increased incrementally until the resistance exceeds a predefined tolerance, we ensure that the minimum amount of required switching energy is expended. Figure 3b depicts the calculated programming energy requirements of a typical AlxOy/TiO2 device with 47 distinct states. An upper bound of the energy consumption per state during programming can be estimated as \({\sum }^{}\{{V}^{2}/{R}_{min,max}{\rm{\Delta }}t\}\), where V is the programming pulse voltage amplitude and ∆t the pulse width. As biasing typically occurs between 1 and 2 V, R min,max represent the resistance in these two voltages as calculated from the I–V characteristic in the low resistive state (see also Fig. S8). For all the states of the AlxOy/TiO2 device the switching energy remains in the pJ–nJ range. Even though the overall OFF/ON ratio of the devices among the resistive states is small in comparison to previous publications47,48 the incremental biasing steps used in this paper allow for further exploitation of the resistive values of the device that would otherwise not be possible with larger ratios. In addition our approach alleviates issues of poor retention performance mentioned in these works47,48.

As far as the statistical distribution of the resistive states for different bilayers is concerned we can observe in Fig. 5a that AlxOy/TiO2 bilayer clearly outperforms the other combinations with a median of 47 states (5.5 bits), followed by WOx/TiO2 and TaxOy/TiO2 with a median in the 4-bit range and finally by ZnOx/TiO2 and SiOx/TiO2 in the 3-bit range. Even in the worst case the AlxOy/TiO2 devices consistently exhibit at least 4-bit of information with half of the devices surpassing 5-bits and 1/3 the 6-bit mark (Fig. 5b).

Bilayer device statistics. (a) Number of resistive states ranges for different bilayer combinations. AlxOy/TiO2 devices clearly outperform all other combinations with ZnOx/TiO2 and SiOx/TiO2 exhibiting the lower amount of resistive states; (b) Attainable states distribution for 32 AlxOy/TiO2 based devices. Nearly all the devices tested exhibit at least 4 bits of information whereas 1/3 of them surpasses the 6-bit mark.

In this paper, we demonstrated that the incorporation of different metal-oxide barrier layers in ReRAM improves the overall programming stability. This is enabled via the improved transport properties of the device depending on the increasingly higher mobility of cations and subsequent lower mobility of oxygen ions, in accordance to the employed barrier layer. Through this study, we were able to demonstrate for the first-time solid-state ReRAM operating as analogue memory cells with up to 5.5-bits capacity. While ReRAM technologies have been mainly promoted for high-spatial density storage and corollary applications, our work demonstrates the new prospects arising from high-capacity memory.

Methods

Device fabrication

All devices have been fabricated on 6-inch oxidised silicon wafers (200 nm of thermal SiO2). Initially the bottom electrodes were fabricated using photolithography and electron beam evaporation of titanium (5 nm) and platinum (10 nm) followed by lift-off process in N-Methyl-2-pyrrolidone (NMP). Then, 40 nm of TiO2 were deposited using magnetron sputtering. The Al2O3, Ta2O5, and SiO2 layers (4 nm) were also deposited using magnetron sputtering after negative tone photolithography. The active layer is formed after lift-off in NMP. The 4 nm layers of ZnO, HfO2 and WO3 were synthesised using atomic layer deposition (ALD). After that a positive tone photolithography and ion beam milling processes were used to pattern and etch the active layers. The top electrode was fabricated using photolithography, electron beam evaporation of platinum (10 nm) and lift-off in NMP.

Electrical characterisation

Characterisation of the memristors has been done with our in-house memristor characterisation platform49. All read pulses are set at 50 ms in duration and 0.5 V in amplitude. Nominal line resistance for all devices evaluated is estimated to be about 150 Ω per platinum electrode. Devices are initially electroformed to a usable resistance range (25 to 200 kΩ, depending on the stack) using consecutive 1 μs pulses of negative polarity ranging from −8 to −12 V in amplitude. A series resistor of 1 kΩ was used as a current-limiting mechanism for all devices. Resistance initially drops to the 106 Ω range and then to a more stable 104–105 Ω range. Multi-bit capability of the devices has been evaluated with a custom algorithm (see following section). In order to extract the retention curve a sequence of 100 ns 2 V pulses is used to program the device to a specified resistance and then a read pulse is applied every 5 minutes for 8 hours. For temperature dependent retention measurements resistive level was selected after 85 °C have been stabilised in the probe station chuck.

Resistive state evaluation algorithm

State assessment occurs over three phases. During the first phase a series of programming pulses of a predefined duration (100 ns), increasing amplitudes and alternating polarities is applied to the device under test and the resistive state of the device is evaluated between every pair of programming trains. This is to determine the polarity that induces a switch in the resistance of the device. After the switching polarity has been determined the second phase, using fixed amplitude, 100 ns pulses of the opposite polarity in respect to the one determined in the first phase, drives the resistance to a stable low value. Stability is assumed when the fitted slope is lower that a predefined threshold. The third phase applies an increasing number of 100 ns programming pulsing using the polarity determined from the first phase followed by two read trains separated by a 100 ms retention interval. If the lower bound of the standard deviation of the resistance measured between these trains is at least 2σ higher than the upper bound of the previous state a new resistive state is established. The algorithm terminates if the voltage limit is reached or if the trend of the resistive states become non-monotonic. The granularity on the standard deviation directly impacts the number of assessed states (see Supplementary Fig. S3). 2σ was used throughout the electrical characterisation as it provides a large enough confidence interval (at least 95%) while allowing the exploitation of a high amount of resistive states. A flowchart detailing the steps of the algorithm described here can be found in Supplementary Fig. S4.

Data Availability

The data that support the findings of this study are available from the University of Southampton institutional repository at https://doi.org/10.5258/SOTON/D0329.

References

Chua, L. Memristor-The missing circuit element. IEEE Transactions on Circuit Theory 18, 507–519 (1971).

Yoshida, C., Tsunoda, K., Noshiro, H. & Sugiyama, Y. High speed resistive switching in Pt/TiO2/TiN film for nonvolatile memory application. Appl. Phys. Lett. 91, 223510 (2007).

Prezioso, M. et al. Training and operation of an integrated neuromorphic network based on metal-oxide memristors. Nature 521, 61–64 (2015).

Serb, A. et al. Unsupervised learning in probabilistic neural networks with multi-state metal-oxide memristive synapses. Nature Communications 7, ncomms12611 (2016).

Borghetti, J. et al. ‘Memristive’ switches enable ‘stateful’ logic operations via material implication. Nature 464, 873–876 (2010).

Yang, J. J., Strukov, D. B. & Stewart, D. R. Memristive devices for computing. Nat Nano 8, 13–24 (2013).

Meijer, G. I. Who Wins the Nonvolatile Memory Race? Science 319, 1625–1626 (2008).

Tyson, S., Wicker, G., Lowrey, T., Hudgens, S. & Hunt, K. Nonvolatile, high density, high performance phase-change memory. in 2000 IEEE Aerospace Conference. Proceedings (Cat. No.00TH8484) 5, 385–390 (2000).

Scott, J. F. & Araujo, C. A. P. de. Ferroelectric Memories. Science 246, 1400–1405 (1989).

Waser, R. & Aono, M. Nanoionics-based resistive switching memories. Nat Mater 6, 833–840 (2007).

Setter, N. et al. Ferroelectric thin films: Review of materials, properties, and applications. Journal of Applied Physics 100, 051606 (2006).

Hamann, H. F., O’Boyle, M., Martin, Y. C., Rooks, M. & Wickramasinghe, H. K. Ultra-high-density phase-change storage and memory. Nat Mater 5, 383–387 (2006).

Strachan, J. P., Torrezan, A. C., Medeiros-Ribeiro, G. & Williams, R. S. Measuring the switching dynamics and energy efficiency of tantalum oxide memristors. Nanotechnology 22, 505402 (2011).

Pi, S., Lin, P. & Xia, Q. Cross point arrays of 8 nm × 8 nm memristive devices fabricated with nanoimprint lithography. Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena 31, 06FA02 (2013).

Khiat, A., Ayliffe, P. & Prodromakis, T. High Density Crossbar Arrays with Sub- 15 nm Single Cells via Liftoff Process Only. Scientific Reports 6, srep32614 (2016).

Baek, I. G. et al. Highly scalable nonvolatile resistive memory using simple binary oxide driven by asymmetric unipolar voltage pulses. IEDM Technical Digest. IEEE International Electron Devices Meeting 2004, 587–590, https://doi.org/10.1109/IEDM.2004.1419228 (2004).

Merced-Grafals, E. J., Dávila, N., Ge, N., Williams, R. S. & Strachan, J. P. Repeatable, accurate, and high speed multi-level programming of memristor 1T1R arrays for power efficient analog computing applications. Nanotechnology 27, 365202 (2016).

Prakash, A., Deleruyelle, D., Song, J., Bocquet, M. & Hwang, H. Resistance controllability and variability improvement in a TaOx-based resistive memory for multilevel storage application. Appl. Phys. Lett. 106, 233104 (2015).

Zhao, L. et al. Multi-level control of conductive nano-filament evolution in HfO2 ReRAM by pulse-train operations. Nanoscale 6, 5698–5702 (2014).

Lee, S. R. et al. Multi-level switching of triple-layered TaOx RRAM with excellent reliability for storage class memory. In 2012 Symposium on VLSI Technology (VLSIT) 71–72, https://doi.org/10.1109/VLSIT.2012.6242466 (2012).

Park, J. et al. Multibit Operation of TiOx-based ReRAM by Schottky Barrier Height Engineering. IEEE Electron Device Letters 32, 476–478 (2011).

Kim, W. et al. Multistate Memristive Tantalum Oxide Devices for Ternary Arithmetic. Scientific Reports 6, srep36652 (2016).

Wong, H. S. P. et al. Metal–Oxide RRAM. Proceedings of the IEEE 100, 1951–1970 (2012).

Lee, M.-J. et al. A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta2O5−x/TaO2−x bilayer structures. Nat Mater 10, 625–630 (2011).

Torrezan, A. C., Strachan, J. P., Medeiros-Ribeiro, G. & Williams, R. S. Sub-nanosecond switching of a tantalum oxide memristor. Nanotechnology 22, 485203 (2011).

Murdoch, B. J. et al. Memristor and selector devices fabricated from HfO2−x N x. Applied Physics Letters 108, 143504 (2016).

Strukov, D. B., Snider, G. S., Stewart, D. R. & Williams, R. S. The missing memristor found. Nature 453, 80–83 (2008).

Yang, J. J. et al. Memristive switching mechanism for metal/oxide/metal nanodevices. Nat Nano 3, 429–433 (2008).

Wedig, A. et al. Nanoscale cation motion in TaOx, HfOx and TiOx memristive systems. Nat Nano 11, 67–74 (2016).

Kwon, D.-H. et al. Atomic structure of conducting nanofilaments in TiO2 resistive switching memory. Nat Nano 5, 148–153 (2010).

Cho, D.-Y., Luebben, M., Wiefels, S., Lee, K.-S. & Valov, I. Interfacial Metal–Oxide Interactions in Resistive Switching Memories. Applied Materials and Interfaces 9, 19287–19295 (2017).

Alekseeva, L., Nabatame, T., Chikyow, T. & Petrov, A. Resistive switching characteristics in memristors with Al2O3/TiO2 and TiO2/Al2O3 bilayers. Jpn. J. Appl. Phys. 55, 08PB02 (2016).

Improvement of resistive switching performances via an amorphous ZrO2 layer formation in TiO2-based forming-free resistive random access memory. Journal of Applied Physics 116, 124514 (2014).

Yu, S., Wu, Y., Chai, Y., Provine, J. & Wong, H. S. P. Characterization of switching parameters and multilevel capability in HfOx/AlOx bi-layer RRAM devices. in Proceedings of 2011 International Symposium on VLSI Technology, Systems and Applications 1–2, https://doi.org/10.1109/VTSA.2011.5872251 (2011).

Hudec, B. et al. Resistive switching in TiO2-based metal–insulator–metal structures with Al2O3 barrier layer at the metal/dielectric interface. Thin Solid Films 563, 10–14 (2014).

Yoon, J. H. et al. Current Limit and Self-Rectification Functionalities in the TiO2/HfO2 Resistive Switching Material System. Nanoscale https://doi.org/10.1039/C7NR02215H (2017).

Valov, I. Interfacial interactions and their impact on redox-based resistive switching memories (ReRAMs). Semicond. Sci. Technol. 32, 093006 (2017).

Carta, D. et al. Investigation of the Switching Mechanism in TiO2-Based RRAM: A Two-Dimensional EDX Approach. ACS Appl. Mater. Interfaces 8, 19605–19611 (2016).

Carta, D. et al. X-ray spectromicroscopy investigation of soft and hard breakdown in RRAM devices. Nanotechnology 27, 345705 (2016).

Moors, M. et al. Resistive Switching Mechanisms on TaOx and SrRuO3 Thin-Film Surfaces Probed by Scanning Tunneling Microscopy. ACS Nano 10, 1481–1492 (2016).

Davies, J. A., Domeij, B., Pringle, J. P. S. & Brown, F. The Migration of Metal and Oxygen during Anodic Film Formation. J. Electrochem. Soc. 112, 675–680 (1965).

Brown, F. & Mackintosh, W. D. The Use of Rutherford Backscattering to Study the Behavior of Ion‐Implanted Atoms During Anodic Oxidation of Aluminum: Ar, Kr, Xe, K, Rb, Cs, Cl, Br, and l. J. Electrochem. Soc. 120, 1096–1102 (1973).

Verkerk, B., Winkel, P. & de Groot, D. G. On the mechanism of anodic oxidation of Tantalum. Philips Res. Repts 13, 506–508 (1958).

Whitton, J. L. The Measurement of Ionic Mobilities in the Anodic Oxides of Tantalum and Zirconium by a Precision Sectioning Technique. J. Electrochem. Soc. 115, 58–61 (1968).

Baeumer, C. et al. Spectromicroscopic insights for rational design of redox-based memristive devices. Nature Communications 6, ncomms9610 (2015).

Jo, S. H. & Lu, W. CMOS Compatible Nanoscale Nonvolatile Resistance Switching Memory. Nano Lett. 8, 392–397 (2008).

Wang, Y.-F., Lin, Y.-C., Wang, I.-T., Lin, T.-P. & Hou, T.-H. Characterization and Modeling of Nonfilamentary Ta/TaOx/TiO2/Ti Analog Synaptic Device. Scientific Reports 5, srep10150 (2015).

Govoreanu, B. et al. Vacancy-modulated conductive oxide resistive RAM (VMCO-RRAM): An area-scalable switching current, self-compliant, highly nonlinear and wide on/off-window resistive switching cell. In 2013 IEEE International Electron Devices Meeting 10.2.1-10.2.4 https://doi.org/10.1109/IEDM.2013.6724599 (2013).

Berdan, R. et al. A -Controller-Based System for Interfacing Selectorless RRAM Crossbar Arrays. IEEE Transactions on Electron Devices 62, 2190–2196 (2015).

Acknowledgements

We acknowledge the financial support of FP7 RAMP and EPSRC EP/K017829/1. The authors would like to acknowledge Dr Ioannis Zeimpekis-Karakonstantinos for his help in Ta2O5 deposition.

Author information

Authors and Affiliations

Contributions

S.S. and A.K. contributed equally to this work. T.P., A.K. and S.S. conceived the experiments. A.K. and M.T. optimized the fabrication process flowchart and fabricated the device prototypes. S.C. performed the preliminary measurements. S.S. and A.S. developed the algorithm. S.S., A.K. and T.P. performed and optimized the electrical characterisations. I.V. contributed on discussions about underlying switching mechanisms. S.S., A.K. and T.P. wrote the manuscript and all authors contributed in the writing through providing feedback.

Corresponding author

Ethics declarations

Competing Interests

The authors declare that they have no competing interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Stathopoulos, S., Khiat, A., Trapatseli, M. et al. Multibit memory operation of metal-oxide bi-layer memristors. Sci Rep 7, 17532 (2017). https://doi.org/10.1038/s41598-017-17785-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-017-17785-1

This article is cited by

-

Combinational logic circuits based on a power- and area-efficient memristor with low variability

Journal of Computational Electronics (2024)

-

Forming-Free and Non-linear Resistive Switching in Bilayer \(\hbox {HfO}_{\textrm{x}}\)/\(\hbox {TaO}_{\textrm{x}}\) Memory Devices by Interface-Induced Internal Resistance

Electronic Materials Letters (2024)

-

Hardware implementation of memristor-based artificial neural networks

Nature Communications (2024)

-

Improving the robustness of analog deep neural networks through a Bayes-optimized noise injection approach

Communications Engineering (2023)

-

Thousands of conductance levels in memristors integrated on CMOS

Nature (2023)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.