Abstract

We studied intrinsic resistance switching behaviour in sputter-deposited amorphous silicon suboxide (a-SiO x ) films with varying degrees of roughness at the oxide-electrode interface. By combining electrical probing measurements, atomic force microscopy (AFM), and scanning transmission electron microscopy (STEM), we observe that devices with rougher oxide-electrode interfaces exhibit lower electroforming voltages and more reliable switching behaviour. We show that rougher interfaces are consistent with enhanced columnar microstructure in the oxide layer. Our results suggest that columnar microstructure in the oxide will be a key factor to consider for the optimization of future SiOx-based resistance random access memory.

Similar content being viewed by others

Introduction

Amorphous silicon suboxides (a-SiOx) are promising candidates as switching layers in resistance random access memories (RRAM)1,2,3,4,5,6,7,8,9,10, with additional applications in logic devices11 and neuromorphic engineering12, 13. a-SiOx has key advantages over other oxide materials since it is cheaply produced from abundant resources and readily integrable into current complementary-metal-oxide-semiconductor (CMOS) technology. The optimization of an a-SiOx-based RRAM device would therefore be highly desirable.

Previous studies on a-SiOx have reported extrinsic resistance switching from metallic filamentation as a result of ion migration from the electrode material1,2,3, 14, or intrinsic conductive path formation as a result of oxygen vacancy accumulation4, 5, 15,16,17,18. In the latter case, switching behaviour varies greatly between devices. For example, the devices in refs 4, 6, 15, and 19 required vacuum conditions or hermetic sealing to function, with switching only observed at an exposed oxide surface. In the remaining cases, including the present study, switching occurs in the oxide bulk in ambient conditions. Previously, the oxide layer has been fabricated using a number of different techniques, including sputtering5, 6, 8,9,10, 18, 20, plasma-enhanced chemical vapour deposition (PECVD)7, and thermal oxidation4, 15. Prior studies suggest that the oxide fabrication technique strongly influences the microstructure of a-SiOx. Two structural models have most commonly been proposed: the ‘random bonding model’21,22,23 and the ‘random mixture model’24,25,26,27,28. Differences in microstructure are clearly likely to affect the nature of the resistance switching behaviour; however, relatively few studies29, 30 have been carried out on this topic in the context of RRAM and we are not aware of such investigations for an a-SiOx oxide layer.

In the present study we concentrate on sputtering deposition. At low substrate temperatures, it has been noted that sputtered films exhibit columnar growth31, 32, resulting in columnar grain structures separated by intercolumnar boundary regions, which are less densely packed with atoms. This columnar microstructure is more well-defined if the substrate surface has a greater roughness, since particles arriving at the surface tend to aggregate at high points as a result of atomic shadowing effects31, with intercolumnar boundaries aligned with low points on the surface.

We combine electrical probing measurements with atomic force microscopy (AFM) and scanning transmission electron microscopy (STEM), to study resistance switching behaviour in a series of devices with varying degrees of roughness at their oxide-electrode interfaces. AFM and STEM imaging indicates that rougher oxide-electrode interfaces are associated with lower electroforming voltages and more reliable switching behaviour, and are consistent with well-defined columnar microstructure in the oxide. Our results suggest that columnar microstructure is a key factor to consider for the optimization of a-SiOx-based RRAM technology.

Results

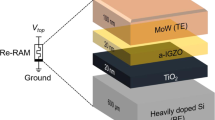

Initially, three different metal-insulator-metal (MIM) devices were studied, which will be referred to as type 1, type 2, and type 3, respectively. The structures of these devices are summarized in Fig. 1. In all three devices, columnar microstructure is visible in the electrode layers as indicated by the red arrows, with increasing roughness at the bottom electrode in the order 1 < 2 (RMS roughness = 0.55 nm) < 3 (RMS roughness = 1.10 nm). In the type 3 device, columnar growth appears to be continuous through the thickness of the bottom electrode. In comparison, the top electrode appears to consist of grains stacked above one another to form relatively wider columns. It is well known that the physical properties of the deposited material greatly influence the resulting film microstructure33, 34. Increasingly rough bottom electrode surfaces would suggest enhanced atomic shadowing during sputter-deposition of the oxide, and more pronounced columnar microstructure within the oxide layer. A closer inspection of the type 3 device reveals columnar growth within the oxide layer as shown in Fig. 2. Figure 2(a) shows a bright field (BF) STEM image, where columnar boundaries between grains in the bottom Mo layer at features A and B appear to extend into the oxide layer in the form of bright vertical streaks. These streaks are visible across the oxide layer with a spacing of approximately 20 nm and correspond to regions of low intensity in the high-angle annular dark field (HAADF) image in Fig. 2(b). This indicates that they are regions of low average atomic number35 and suggests the presence of intercolumnar boundaries in the oxide layer31, which are less densely packed with atoms. The occurence of atomic shadowing across the whole oxide layer is indicated by the roughness at the top oxide-electrode interface, which mirrors changes at the bottom oxide-electrode interface. Such regions are not visible in type 1 and type 2 devices; however, the less rough interfaces could suggest the presence of a less well-defined columnar microstructure, which is not easily observed through the thickness of the TEM sample. We note that although a different choice of electrodes is used in type 3 devices, our previous studies have indicated that switching is still intrinsic to the oxide layer in all three devices5, 9, 10. We hypothesise that the following differences in switching behaviour will therefore be strongly be influenced by the differences in the degree of columnar microstructure in the oxide, which is a product of bottom electrode roughness.

Bright field STEM images of cross-sections from type 1, type 2, and type 3 devices, with red arrows pointing out columnar grains visible in the electrode layers. The top Pt layer seen in type 1 devices is needed for focused ion beam (FIB) sample preparation. (a) Type 1 devices consist of TiN top and bottom electrodes, which are approximately 10 and 15 nm thick, respectively. The oxide layer is approximately 35 nm thick. A sub-5 nm mixing layer is visible at the bottom electrode. Its characteristics were determined using EELS. (b) Type 2 devices consist of TiN top and bottom electrodes, which are approximately 85 and 80 nm thick, respectively. The oxide layer is approximately 35 nm thick. (c) Type 3 devices consist of Au and Mo top and bottom electrodes, which are approximately 115 and 280 nm thick, respectively. The oxide layer is approximately 35 nm thick. A thin Ti wetting layer is present between the Au electrode and oxide layer. Its presence and approximate thickness of 5 nm was confirmed using EELS. (c)(ii) is a contrast-enhanced copy of (c)(i) and indicates columnar growth in the electrode layers.

Bright and dark field STEM images of a cross-section of a type 3 device. This figure is a slightly modified version of Fig. 4 from ref. 10. (a) Bright field image showing that at features A and B, columnar boundaries in the Mo layer appear to extend into the oxide layer in the form of bright vertical streaks. These streaks are visible across the oxide layer with a spacing of approximately 20 nm. (b) Contrast-enhanced high-angle annular dark field (HAADF) image corresponding to (a). The bright vertical streaks in (a) can be seen to correspond to regions of low intensity in (b). This indicates regions of low average atomic number35 and suggests the presence of intercolumnar boundaries in the oxide layer, which are less densely packed with atoms.

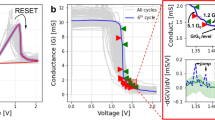

Figure 3 shows typical I-V curves obtained from the three devices. More detailed studies of the electrical characteristics of type 2 and type 3 devices are provided in refs 9 and 10. Firstly, we sweep the voltage bias to electroform (transition from the pristine state to the low resistance state) and then proceed to cyclically reset (transition from the low resistance state to the high resistance state), and set (transition from the high resistance state to the low resistance state) the device. Type 1 devices do not electroform and consistently exhibit hard breakdown (transition to a permanent low resistance state) at comparatively high voltages (≈25 V in Fig. 3(a)). Type 2 devices electroform at around 6 V and switch in a unipolar manner, with the set at around 4 V, and the reset at around 2 V (Fig. 3(b)). Despite an identical choice of electrodes and oxide layer thickness and stoichiometry in type 1 and type 2 devices, only type 2 devices electroform at a comparatively low voltage. We attribute this to the change in bottom electrode roughness, which will influence the degree of columnar microstructure in the oxide during sputtering deposition31. The best switching properties are obtained from type 3 devices, which have the roughest oxide-electrode interfaces. Such devices electroform at around −4 V and exhibit bipolar switching with low switching voltages, typically lower than −1 V to set, and up to 1.5 V to reset (Fig. 3(c)). In addition to having lower switching voltages than type 2 devices, type 3 devices also exhibit greater device endurance on the order of 107 switching cycles10 as compared to 102 for type 2 devices9. However, it should be noted that a difference in switching mechanism for unipolar and bipolar devices may greatly impact switching voltages and device endurance.

Typical I-V curves for type 1, type 2, and type 3 RRAM devices. (a) Type 1 devices do not electroform and only exhibit hard breakdown at around 25 V. (b) Type 2 devices exhibit unipolar switching behaviour, with electroforming at around 6 V, and setting and resetting at approximately 4 V and 2 V, respectively. (c) Type 3 devices exhibit bipolar switching behaviour, with electroforming at around −4 V, and setting and resetting at approximately −1 V and 1.5 V, respectively.

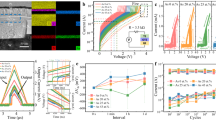

In order to isolate the effects of columnar microstructure and ensure the differences in choice of electrode layer, switching mechanism, and stoichiometry do not affect the observed changes, three type 3 devices with roughness varied at the bottom Mo electrode were fabricated. AFM topography maps for these devices are shown in Fig. 4. Type 3a, 3b, and 3c devices have an RMS roughness of 1.50 nm, 1.10 nm, and 0.90 nm, respectively, with corresponding median values for electroforming voltage around 4 V, 5 V, and 6.5 V. In addition, type 3c devices were found to be unreliable, with around half of the devices failing to reset after electroforming (see Fig. S1). As in the comparison between type 1 and type 2 devices, we again attribute this behaviour to the difference in bottom electrode roughness and the resulting columnar microstructure in the oxide. As can be observed from the reset curve in Fig. 4(c)(ii), for type 3c devices the current in the low resistance state is greater relative to the rougher devices. We suggest that this is the result of increased degradation of the oxide layer due to higher electroforming voltages, resulting in a more prominent conductive path in the low resistance state. We also note that higher electroforming voltages in type 3c devices tended to be followed by a failed reset. These results suggest that increasingly rougher oxide-electrode interfaces result in lower electroforming voltages and more reliable devices. The rougher bottom electrode would promote a greater degree of atomic shadowing during oxide deposition, and a more well-defined columnar microstructure.

(i) AFM surface roughness characterization and (ii) Typical I-V curves for type 3 RRAM devices with varying bottom Mo electrode roughness. The insets of the I-V curves show distributions of the electroforming voltages from a sample of 5 devices for each roughness value respectively. The line inside the box is the median value, the top and bottom of the box represent the 25th and 75th percentiles, and the two whiskers represent maximum and the minimum values. (a) Type 3a devices electroform around a median value of 4 V, with a range between 3.3 V and 4.7 V. (b) Type 3b devices electroform around a median value of 5 V, with a range between 4.1 V and 5.4 V (c) Type 3c devices electroform around a median value 6.5 V, with a range between 6.2 V and 9.0 V. Such devices are typically less reliable, with around half of the devices failing to reset after electroforming. The reset curve (red) reveals a higher current in the low resistance state when compared to the rougher devices.

Discussion

In previous work, we measured circular dome features approximately 10 nm in diameter using an atomic force microscope (AFM)5, 20. Scanning tunneling microscopy (STM) revealed that these structures have increased conductivity at their edges. It was suggested that these dome structures may reflect columnar microstructure within the oxide layer, and that column boundaries may act as centers for oxygen vacancy accumulation. Analogies with this model can be drawn with resistance switching in HfO2 layers, where conductive paths have been shown to preferentially form at grain boundaries36,37,38,39. Column boundaries could be defect-rich and promote the formation of interstitial O anions18, 40, 41 through mechanisms such as electron injection, as suggested by Gao et al.41, 42. In this mechanism, double electron trapping at intrinsic precursor sites facilitates the formation of an oxygen vacancy and O2− ion43, 44. More well-defined columnar boundaries, which extend across the oxide layer from the bottom electrode to the top electrode, may act as pre-defined regions for conductive path formation. This could explain the lower electroforming voltages and increased reliability recorded for rougher oxide-electrode interfaces. We hypothesise that less densely packed intercolumnar boundaries could act as low energy pathways for the transport of large quanitities of oxygen, resulting in electrode deformation and oxygen gas emission during electrical stressing as observed in previous work7, 18, 45.

In summary, our measurements suggest that the sputtering of a-SiO x onto rough electrode surfaces results in lower electroforming voltages and greater device reliability for resistance switching applications. This is consistent with enhanced columnar microstructure in the oxide layer. These observations will be important to consider for the optimization of future a-SiO x -based RRAM devices.

Methods

Three different MIM stacks were initially studied, and are referred to as type 1, type 2, and type 3. For all device types, the metal and oxide layers were deposited by sputtering onto SiO2 substrates, except in type 3 devices where the top electrode layers were deposited using electron beam evaporation. Type 1 and type 2 devices were symmetrical TiN/SiO x /TiN stacks with fabrication aiming for a stoichiometry of x ≈ 1.3, whereas type 3 devices were non-symmetrical Au/SiO x /Mo stacks with a Ti wetting layer approximately 5 nm thick between the Au and SiO x layers. The oxide layer in type 3 devices was comparatively oxygen-rich with fabrication aiming to achieve a stoichiometry with x ≈ 2. These differences in stoichiometry were confirmed from the corresponding ELNES fingerprints of the oxide46.

In order to isolate the effect of bottom electrode roughness (and therefore columnar microstructure) on switching behaviour, three variants of type 3 devices (type 3a, 3b, and 3c) were prepared, with different roughnesses for the bottom Mo electrode. The variation in roughness was achieved by adjusting the Mo sputtering parameters such as substrate temperature, deposition pressure, and power as described in the following: type 3a: power = 200 W, deposition pressure = 10 mTorr, substrate temperature = 25 C; type 3b: power = 300 W, deposition pressure = 5 mTorr, substrate temperature = 25 C; type 3c: power = 300 W, deposition pressure = 3 mTorr, substrate temperature = 150 C. The 35 nm a-SiO x layer was deposited by reactive sputtering using a silicon target in an oxygen-rich environment. The Ti/Au top contact was deposited by electron beam evaporation with individual device size defined using a shadow mask.

Roughness values for the SiO x layers were calculated from atomic force microscopy measurements. These measurements were made using a Bruker Icon microscope with a Nanoscope V controller running Nanoscope v9.1. Root mean square roughness values were calculated using Nanoscope Analysis v1.50.

All devices types were electrically stressed using a Keithley 4200 semiconductor characterization system with a Signatone probe station. All electrically stressed devices were approximately 400 μm × 400 μm in area.

An FEI Helios focused ion beam (FIB) was used to prepare TEM cross-sections of unstressed and stressed devices. STEM imaging was carried out at 80 KeV using an FEI Titan (S)TEM.

References

Schindler, C., Thermadam, S. C. P., Waser, R. & Kozicki, M. N. Bipolar and Unipolar Resistive Switching in Cu-Doped SiO2. Electron Devices, IEEE Trans. 54, 2762–2768 (2007).

Wu, X. et al. Intrinsic nanofilamentation in resistive switching. J. App. Phys. 113, 114503 (2013).

Wang, G. et al. Nanoporous Silicon Oxide Memory. Nano lett. 14, 4694–4609 (2014).

Yao, J., Sun, Z., Zhong, L., Natelson, D. & Tour, J.-M. Resistive switches and memories from silicon oxide. Nano lett. 10, 4105–4110 (2010).

Mehonic, A. et al. Resistive switching in silicon suboxide films. J. Appl. Phys. 111, 074507 (2012).

Chang, Y. et al. Understanding the resistive switching characteristics and mechanism in active SiO x -based resistive switching memory. J. Appl. Phys. 112, 123702 (2012).

Wang, Y. et al. Resistive switching mechanism in silicon highly rich SiO x (x < 0.75) films based on silicon dangling bonds percolation model. App. Phys. Lett. 102, 042103 (2013).

Mikhaylov, A. N. et al. Bipolar resistive switching and charge transport in silicon oxide memristor. Material Science and Engineering B 194, 48–54 (2015).

Mehonic, A. et al. Structural changes and conductance thresholds in metal-free intrinsic SiOx resistive random access memory. J. App. Phys. 117, 124505 (2015).

Mehonic, A. et al. Intrinsic resistance switching in amorphous silicon oxide for high performance SiO x reram devices. Microelectron. Eng. 178, 98–103 (2017).

Borghetti, J. et al. ‘Memristive’ switches enable ‘stateful’ logic operations via material implication. Nature 464, 873–876 (2010).

Serb, A. et al. Unsupervised learning in probabilistic neural networks with multi-state metal-oxide memristive synapses. Nature Comms. 7, 12611 (2016).

Mehonic, A. & Kenyon, A. J. Emulating the electrical activity of the neuron using a silicon oxide rram cell. Frontiers in Neuroscience 10, 57 (2016).

Onfrio, N., Guzman, D. & Strachan, A. Atomic origin of ultrafast resistance switching in nanoscale electrometallization cells. Nature Materials 14, 440–446 (2015).

Yao, J., Zhong, L., Natelson, D. & Tour, J.-M. In situ imaging of the conducting filament in a silicon oxide resistive switch. Sci. Rep. 2, 242 (2012).

Buckwell, M., Montesi, L., Mehonic, A., Hudziak, S. & Kenyon, A. J. Conductance tomography of conductive filaments in intrinsic silicon-rich silica rram. Nanoscale 7, 18030–18035 (2015).

Montesi, L. et al. Nanosecond analog programming of substoichiometric silicon oxide resistive ram. Nanotechnology, IEEE Trans. 15, 428–434 (2016).

Mehonic, A. et al. Nanoscale transformations in metastable, amorphous, silicon-rich silica. Adv. Mat. 28, 7486–7493 (2016).

Zhou, F. et al. Discussion on device structures and hermetic encapsulation for sio x random access memory operation in air. Appl. Phys. Lett. 105, 163506 (2014).

Mehonic, A., Wojdak, M., Hudziak, S., Rizk, R. & Kenyon, A. J. Electrically tailored resistance switching in silicon oxide. Nanotechnology 23, 455201 (2012).

Philipp, H. R. Optical and bonding model for non-crystalline SiOx and SiOxNy materials. J. Non-Crystalline Solids 8, 627–632 (1972).

Greaves, G. N., Jiang, X. L., Jenkins, R. N., Holzenkampfer, E. & Kalbitzer, S. The Local Structure of A-SiOx: H Films. Le Journal de Physique Colloques 47, 853 (1986).

Sasaki, M. & Ehara, T. Silicon oxide thin films prepared by vacuum evaporation and sputtering using silicon monoxide. J. Phys:. Conference Series 417, 012028 (2013).

Coleman, M. V. & Thomas, D. J. D. The Structure of Silicon Oxide Films. physica status solidi (b) 22, 593–602 (1967).

Temkin, R. J. An analysis of the radial distribution function of SiO x . J. Non-Crystalline Solids 17, 215–230 (1975).

Johanessen, J. S., Spicer, W. E. & Strausser, Y. E. Phase separation in silicon oxides as seen by Auger electron spectroscopy. Appl. Phys. Lett. 27, 452–454 (1975).

Forty, A. J., Kerkar, M., Robinson, J., El-Mashri, S. M. & Farrabaugh, E. N. A Structural Investigation of Some Evaporated SiOx Films. Le Journal de Physique Colloques 47, 857 (1986).

Schulmeister, K. & Mader, W. TEM investigation on the structure of amorphous silicon monoxide. J. Non-Crystalline Solids 320, 143–150 (2003).

Goux, L. et al. Influence of the Cu-Te composition and microstructure on the resistive switching of Cu-Te/Al2O3/Si cells. Appl. Phys. Lett. 99, 053502 (2011).

Clarke, H. et al. Microstructure dependent filament forming kinetics in HfO2 programmable metallization cells. Nanotechnology 27, 425709 (2016).

Thornton, J. A. The microstructure of sputter-deposited coatings. J. Vac. Sci. Tech. A 4, 3059–3065 (1986).

McCann, M. T. P., Mooney, D. A., Rahman, M., Dowling, D. P. & MacElroy, J. M. D. Novel, nanoporous silica and titania layers fabricated by magnetron sputtering. ACS Applied Materials Interfaces 3, 252–260 (2011).

Movchan, B. A. & Demchishin, A. V. Structure and Properties of Thick Condensates of Nickel, Titanium, Tungsten, Aluminum Oxides, and Zirconium Dioxide in Vacuum. Fiz. Metal. Metalloved. 29, 653–660 (1969).

Thornton, J. A. Influence of apparatus geometry and deposition conditions on the structure and topography of thick sputtered coatings. J. Vac. Sci. Tech. 11, 666–670 (1974).

Pennycook, S. J. & Jesson, D. E. High-resolution Z-contrast imaging of crystals. Ultramicroscopy 37, 14–38 (1991).

Bersuker, G. et al. Metal oxide resistive memory switching mechanism based on conductive filament properties. J. Appl. Phys. 110, 124518 (2011).

Lanza, M. et al. Grain boundaries as preferential sites for resistive switching in the HfO2 resistive random access memory structures. Appl. Phys. Lett. 100, 123508 (2012).

Lanza, M. et al. Resistive switching in hafnium dioxide layers: local phenomenon at grain boundaries. Appl. Phys. Lett. 101, 193502 (2012).

Shubhakar, K. et al. Study of preferential localized degradation and breakdown of HfO2/SiO x dielectric stacks at grain boundary sites of polycrystalline HfO2 dielectrics. Microelectron. Eng. 109, 364–369 (2013).

Jin, Y. & Chang, K. J. Mechanism for the enhanced diffusion of charged oxygen ions in SiO2. Phys. Rev. Lett. 86, 1973–1976 (2001).

Gao, D., El-Sayed, A. & Shluger, A. L. A mechanism for frenkel defect creation in amorphous SiO2 facilitated by electron injection. Nanotechnology 27, 505207 (2016).

Munde, M. S., Gao, D. Z. & Shluger, A. L. Diffusion and aggregation of oxygen vacancies in amorphous silica. JOP: Condens. Mat. 29, 245701 (2017).

El-Sayed, A.-M., Watkins, M. B., Shluger, A. L. & Afanas’ev, V. V. Identification of intrinsic electron trapping sites in bulk amorphous silica from ab initio calculations. Microelectron. Eng. 109, 68–71 (2013).

El-Sayed, A.-M., Watkins, M. B., Afanas’ev, V. V. & Shluger, A. L. Nature of intrinsic and extrinsic electron trapping in SiO2. Phys. Rev. B 89, 125201 (2014).

Jeong, D. S., Schroeder, H., Breuer, U. & Waser, R. Characteristic electroforming behavior in Pt/TiO2/Pt resistive switching cells depending on atmosphere. J. Appl. Phys. 104, 3716 (2008).

Muller, D. A. et al. The electronic structure at the atomic scale of ultrathin gate oxides. Nature 399, 758–761 (1999).

Acknowledgements

We gratefully acknowledge funding provided by EPSRC under grant EP/K01739X/1 “Resistive switches (RRAM) and memristive behaviour in silicon-rich silicon oxides”, and A*STAR through the Institute of Materials Research and Engineering under the ARAP scheme. The authors would also like to thank Kin Leong Pey and his research group at the Singapore University of Technology in Design (SUTD) for many helpful discussions and access to the electrical probe station.

Author information

Authors and Affiliations

Contributions

M.S.M. wrote the manuscript and prepared Figures 1–4. M.S.M. carried out the TEM experiments under guidance of M.Bosman, and electrical probing measurements were carried out by A.M., M.Buckwell, and L.M. Device fabrication was carried out by A.M. and W.H.N. A.J.K. and A.L.S. oversaw the project. All authors revised the manuscript.

Corresponding author

Ethics declarations

Competing Interests

The authors declare that they have no competing interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Munde, M.S., Mehonic, A., Ng, W.H. et al. Intrinsic Resistance Switching in Amorphous Silicon Suboxides: The Role of Columnar Microstructure. Sci Rep 7, 9274 (2017). https://doi.org/10.1038/s41598-017-09565-8

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-017-09565-8

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.