Abstract

We experimentally demonstrate a reconfigurable electro-optic directed logic circuit which can perform any combinatorial logic operation using cascaded carrier-injection micro-ring resonators (MRRs), and the logic circuit is fabricated on the silicon-on-insulator (SOI) substrate with the standard commercial Complementary Metal-Oxide-Semiconductor (CMOS) fabrication process. PIN diodes embedded around MRRs are employed to achieve the carrier injection modulation. The operands are represented by electrical signals, which are applied to the corresponding MRRs to control their switching states. The operation result is directed to the output port in the form of light. For proof of principle, several logic operations of three-operand with the operation speed of 100 Mbps are demonstrated successfully.

Similar content being viewed by others

Introduction

Silicon photonics has attracted more and more attention in scientific community due to its natural advantages such as complementary metal-oxide-semiconductor-compatible (CMOS) fabrication process, high transmission speed, low latency, and parallel processing, etc1,2,3,4,5,6. Currently, silicon photonics has achieved great development in many fields, and various silicon-based optical devices have been demonstrated successfully such as filters7,8,9, routers10,11,12, lasers13,14,15,16,17, multiplexers18,19,20,21,22, sensors23,24,25,26,27, electro-optic modulators28,29,30,31,32,33,34,35,36,37,38 and optical logic devices39,40,41,42,43,44,45, etc. Being a kind of basic devices in the area of silicon photonics, micro-ring resonator (MRR) is widely used in high-performance computing and optical information processing due to its unique advantages such as sharp resonances for wavelength selectivity, compact size, low consumption, and large-scale integration.

Electro-optic directed logic is a novel paradigm which employs the optical switch networks to carry out Boolean logic operations, and the electrical signals regarded as logic operands are applied to the optical switches to control their switching states46,47,48. The operands of the Boolean logic operations determines the state of each optical switch whose operation is independent to the others in the optical switch network, and all optical switches can perform their operations almost simultaneously. Since the delay time of each switch will not accumulate, and the final operation result is directed to the output port in the form of light, the overall latency of the logic circuit is very low. In addition, as it is known to all, the advantage of electrical signal lies in its convenience of control, and that of the light signal is its adaptability to operation derived from the high propagation speed. The electro-optic directed logic combines the advantages of both electrical and light signals since its control signal is electron and operation signal is photon. Therefore, electro-optic directed logic is a highly appealing candidate for future high speed, bit-rate optical computing, networking system and highly integrated on-chip photonic system. Note that for the directed logic scheme, the logic operands are electrical signals, and the operation results are output in the form of light. The output signals (light signals) must be converted into electrical signals to drive the next level. Therefore, the integrated photo-detector is needed for the scalability. However, the most desired application occasion of directed logic is in on-chip optical network, in where the operation results can be applied in next level directly rather than needed to be converted into electrical signals, and in this case, directed logic can provide ultrafast network routing functions that enable highly efficient packet-switched interconnections for high-performance computing. In a word, for some special application occasion where the operation results in the form of light can be directly applied in the next level, directed logic has more advantages over electrical logic by taking advantage of fast and low-loss propagation of light in a highly integrated on-chip photonic system.

Reconfigurable electro-optic directed logic plays a key role in optical information processing. Compared to most of electro-optic directed logic circuits, reconfigurable electro-optic directed logic circuit can perform any combinatorial logic operation, which can be applied in many occasions such as optical computing, packet routing, etc. For proof of concept, we have successfully demonstrated a reconfigurable electro-optic directed logic circuit which can perform any combinatorial logic operation with four-operand at the operation speed of 10 kbps based on the silicon thermo-optic effect in our previous work42. However, with the growing demand of high speed optical computing, the drawback of the device in ref. 42 has appeared. In this paper, we report a higher speed reconfigurable logic circuit using cascaded carrier-injection MRRs. Although relatively faster response time of reconfigurable electro-optic directed logic circuits has been reported43, 44, the Multiplexer (MUX)/Demultiplexer (DEMUX) and computing functions are achieved simultaneously by the proposed logic circuit, where the MUX/DEMUX are integrated with computing elements. Table 1 summarizes the comparison of various reconfigurable electro-optic directed logic circuits. In comparison, our logic circuit does not need additional MRRs to achieve MUX/DEMUX functions. Therefore, it is more compact than refs 43 and 44. We design and fabricate the logic circuit on Silicon-Oxide-Insulator (SOI) substrate using the standard complementary metal-oxide-semiconductor (CMOS) process, and several logic operations with the operation speed of 100 Mbps are finally demonstrated successfully.

Results

Device working principle, design and fabrication

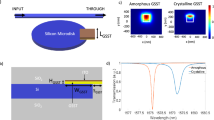

It is well known that any logic function can be expressed in the form of sum-of-product. For example, an arbitrary logic function Y can be expressed as \(Y={X}_{1}+{X}_{2}+{X}_{3}\ldots \ldots {X}_{n}\), and X n denotes the product of a number of variables, such as \({X}_{n}={a}_{1}{\bar{a}}_{2}{a}_{3}\ldots \ldots {a}_{n}\)(\({\bar{a}}_{n}\) represents the opposite logic value of a n ). According to the logic expression, we propose a reconfigurable electro-optic directed logic circuit which can perform any combinatorial logic operation based on cascaded carrier-injection MRRs. As we know, MRR can be employed to construct the optical switch (Fig. 1(a)). In order to control the working state of the optical switch, we fabricate a PIN junction embedded around the ring (Fig. 1(b)), and thus the electrical signal can be applied to MRR through the PIN diodes to achieve a high speed modulation.

(a) Single MRR with one waveguide (inset: the cross-section of the device including the quasi-TE fundamental mode and dimensions of waveguide), (b) a tunable MRR-based optical switch with a PIN junction embedded in the ring, (c) the transmission spectra of the optical switch in block/pass mode (the status of the optical switch is from OFF to ON) for light with the working wavelength, black line is the spectra when the logic signal is ‘0’, blue line is the spectra when the logic signal is ‘1’, λ 0 marks the resonant wavelength without modulation, λ 1 marks the resonant wavelength after modulation, (d) the transmission spectra of the switch in pass/block mode (the status of the optical switch is from ON to OFF).

Generally speaking, there are two different operation modes for the optical switch. One is the block/pass mode, and the other is the pass/block mode. Figure 1(c,d) show the mechanisms to realize the two different operation modes of optical switch, respectively. The resonant wavelength without modulation and the resonant wavelength after modulation are represented by λ 0 and λ 1, respectively. When the working wavelength aligns with λ 0 (see Fig. 1(c)), the switch works in the block/pass mode; while the working wavelength aligns with λ 1 (see Fig. 1(d)), the switch works in the pass/block mode.

The structure of the proposed logic circuit is composed of N MRRs and one waveguide, which is illustrated in Fig. 2(d). In fact, the essence of the proposed logic circuit is an optical switch array consisting of N MRR-based optical switches. Monochromatic continuous light with the working wavelength of λ is coupled into the input ports of logic circuits (Fig. 2(a–c)), and then the light is modulated by the electrical pulse sequences (EPS) applied to MRR1, MRR2, MRR3, …, MRR n , respectively. The low and high levels of EPS represent logic ‘0’ and ‘1’ in electrical domain, respectively; the low and high levels of the optical power at the output port represent logic ‘0’ and ‘1’ in optical domain, respectively. As mentioned in our previous work42, the logic circuit of Fig. 2(a) can perform the AND operation of N operands when all MRRs work in the block/pass mode. The operation result X can be expressed as \(X={a}_{1}{a}_{2}{a}_{3}\ldots \ldots {a}_{n}\). Similarly, the logic circuit can also perform the AND operation of N inverse operands when all MRRs work in the pass/block mode. The operation result can be expressed as \(X={\bar{a}}_{1}{\bar{a}}_{2}{\bar{a}}_{3}\ldots {\bar{a}}_{n}\) (Fig. 2(b)). The logic circuit can also perform the AND operation of N operands when some MRRs work in the pass/block mode and others work in the block/pass mode. For instance, we define MRR2 working in pass/block mode and the other MRRs working in block/pass mode in Fig. 2(c). The operation result X can be expressed as \(X={a}_{1}{\bar{a}}_{2}{a}_{3}\ldots \ldots {a}_{n}\). In brief, if the continuous wave coupled into the logic circuit is monochromatic, the product of any N variables can be obtained at the output port in the form of light according to the definitions of MRR operation modes. As the circuit diagrams show in Fig. 2(d), MRRs in the logic circuit can be divided into several operation groups, where MRRs in one group work at the same wavelength. Multi-wavelength signal lights with the wavelength of λ 1, λ 2, \({\lambda }_{3}\ldots {\lambda }_{n}\) are coupled into the input port simultaneously, and are separated and directed into different operation groups with the Wavelength Division Multiplexing (WDM) technology. Based on the above discussions, every operation group can perform the product of any variables. The operation results of all operation groups are finally multiplexed together. Therefore, the final operation result Y can be expressed as \(Y={X}_{1}+{X}_{2}+{X}_{3}\ldots \ldots {X}_{n}\) (X n denotes the product of any variables). Note that the amount of operation groups is equal to the amount of the working wavelengths, and the amount of operands in each term is equal to the amount of MRRs in the corresponding operation group. The proposed logic circuit is similar with the Field Programmable Gate Array (FPGA), and the resonant wavelengths of unused MRRs can be shifted far from the working wavelengths of the circuit through thermal tuning.

The logic circuit with (a) one working wavelength and all MRRs work in the block/pass mode, (b) one working wavelength and all MRRs work in the pass/block mode, (c) one working wavelength and MRRs work in the pass/block or block/pass mode, and (d) the proposed reconfigurable logic circuit (the solid line ring denotes MRR working in the block/pass mode, the dot line ring denotes MRR working in the pass/block mode, MRRs with the same color work at the same working wavelength, EPS: electrical pulse sequences).

For a proof of principle, a reconfigurable electro-optic directed logic circuit consisting of three electro-optic tunable MRRs is fabricated on 8 in. (20.3 cm) silicon-on-insulator (SOI) wafer with 2-μm-buried SiO 2 layer and 220-nm-top silicon layer. The microscope image of the fabricated device is shown in Fig. 3, and the efficient footprint of the fabricated device is about 400 × 1100 μm 2. The carrier-injection-based PIN modulation structure is used to achieve relatively high speed and high-efficiency modulation of the device. As we known, when the PIN junction is forward-biased, the carriers are injected into the core of the waveguide through the diffusion motion of the carriers, and then the refractive index of the waveguide is modulated. Generally, the carrier’s diffusion speed is far lower than its drift speed; therefore, the operation speed of the device based on the carrier-injection modulation scheme is lower than that’s the carrier-depletion modulation scheme. However, the number of the carrier injected into the core of the waveguide can be very large when a small forward voltage is applied to the PIN junction; therefore, the forward-biased PIN modulation scheme has higher modulation efficiency compared to the reverse-biased PN modulation scheme. For some specific application occasion in which the modulation efficiency is more desired than the operation speed, the forward-biased PIN modulation scheme is a better choice. In fact, these two modulation schemes (forward-biased PIN junction and reverse-biased PN junction) are both based on the free carrier dispersion effect, and in here, we choose the PIN modulation scheme with the simple fabrication process to verify that the free carrier dispersion effect can also be employed in our proposed device. The device is fabricated in Institute of Microelectronics (IME), Singapore using the standard commercial Complementary Metal-Oxide-Semiconductor (CMOS) process, and the fabrication process is similar to our previous works40, 41. See Methods for full fabrication process.

Static Response Test

In order to determine the working wavelengths of the device, an amplified spontaneous emission (ASE) source and an optical spectrum analyzer (OSA) are employed to measure the static response spectra of the device. The measured static response spectra with no voltage applied to the device is shown in Fig. 4. The insertion loss is about 5.3 dB which includes 5 dB coupling loss (about 2.5 dB for each end face) and 0.3 dB transmission loss; the resonant wavelengths of three cascaded MRRs are 1545.18 nm, 1548.10 nm, 1550.73 nm, respectively. The extinction ratio of each MRR is nearly equal (18 dB), and the quality factor (Q factor) of each MRR is approximately 5,000. For carrier-injection modulation, high Q factors are desirable for low-voltage and low-power operation. High Q factor means small 3-dB bandwidth to some extent; therefore, small carrier concentration change can result in enough extinction ratios. However, the trade-off of Q factor should be taken into account since the higher the Q factor is, the more sensitive the MRR will be to the change of environmental temperature. In addition, a high Q factor means long photon lifetime, which will further limits the working speed of the MRR. Therefore, a moderate Q factor of 5,000 is suitable for the device demonstrated in this paper. Consequently, we use three electro-optic tunable MRR with suitable parameters to demonstrate the reconfigurable logic operations. Note that the Ω-shape heaters are integrated on the top of MRRs in order to control their resonant wavelength accurately, and the thermal tuning response spectral is shown in Fig. 5(a), from which we can see that the MRR’s resonant wavelength occurs red-shift with the increasing of applied voltage. The thermal tuning efficiency is about 8.353 mW/nm (as shown in Fig. 5(b)), which can be greatly improved by introducing air trench around MRR49. In addition, air trench can also decrease the crosstalk between adjacent MRRs and improve the thermal stabilization of MRR. Therefore, air trench issue is a main consideration for the optimization design of the device in future.

Dynamic Response Test

As we all know, there are many different logic operations for the three-operand. However, for the purpose of proving the principle, only a few typical logic operations of them are demonstrated here. Firstly, three MMRs are divided into two operation groups, and the first group has one MRR while the second group has two MRRs (Fig. 6). The first group is composed of MRR1, and the working wavelength is chosen as λ 1. The second group is composed of MRR2 and MRR3, and the working wavelength is chosen as λ 2. The different operation modes for MRR are defined to perform different logic operations. For example, two lasers with the wavelengths of λ 1 and λ 2 are coupled into the input port of the device simultaneously, if the MRR1 is controlled by operand A in the pass/block mode, the MRR2 is controlled by operand B in the pass/block mode and the MRR3 is controlled by operand C in the block/pass mode, and thus the device can perform the logic operation of \(\bar{A}+\bar{B}C\) (Fig. 6(c)). Analogously, other logic operations can also be achieved through the definitions of different operation modes of MRR, and several typical examples are shown in Fig. 6.

The measured dynamic response results of the device are shown in Fig. 7. A two-channel tunable laser (TL), three arbitrary function generators (AFGs), an oscilloscope (OSC), an erbium doped fiber amplifier (EDFA), an optical filter, and a photo-detector (PD) are employed to characterize the dynamic response of the device. (Note that those facilities were only used to characterize the device in our experiment, while in practical application, they are no needed and the logical function of the device can be used just like traditional electric transistors.) Three MRRs are firstly divided into two groups. The first group is only composed of MRR1, and its working wavelength is λ 1. The second group includes MRR2 and MRR3, and its working wavelength is λ 2. Continuous monochromatic lights with the wavelengths of λ 1 and λ 2 from a two-channel tunable laser are simultaneously coupled into polarization controllers and then the monochromatic light with TE polarization is coupled into the device through a 2 × 1 combiner. Three pseudo-random binary sequence (PRBS) non-return-to-zero signals with the speed of 100 Mbps generated by the AFGs are applied to MRRs through the PIN diodes embedded around MRRs, respectively. The voltage swing of the PRBS is 1.50 V. The DC bias voltages are −0.06 V in block/pass mode and −0.20 V in pass/block mode for MRR1, and the DC bias voltages for MRR2 and MRR3 are the same, which are −0.19 V in block/pass mode and −0.26 V in pass/block mode, respectively. Therefore, the operating voltages are different in different operation mode for the same MRR, and the operating voltages are 0.69 V in logic ‘1’ state and −0.81 V in logic ‘0’ state for MRR1 in block/pass mode, which means the operating voltage change from 0.69 V to −0.81 V when the logic signal change from logic ‘1’ to ‘0’, vice-versa; The operating voltages are 0.55 V in logic ‘0’ state and −0.95 V in logic ‘1’ state for MRR1 in pass/block mode, which means the operating voltage change from 0.55 V to −0.95 V when the logic signal change from logic ‘0’ to ‘1’, vice-versa. The voltage swings and DC bias voltages are the same for MRR2 and MRR3, therefore, the operating voltages change from 0.56 V to −0.94 V for MRR2 and MRR3 in block/pass mode when the logic signals change from logic ‘1’ to ‘0’, vice-versa, and the operating voltages change from 0.49 V to −1.01 V for MRR2 and MRR3 in pass/block mode when the logic signals change from logic ‘0’ to ‘1’, vice-versa.

Finally, the output optical signal is coupled into a photo-detector, and the electrical signal transformed by the PD is fed into the OSC for observation. As proof of principle, several logic operations of three-operand with the operation speed of 100 Mbps are demonstrated successfully (Fig. 7). In fact, any logic operation of three-operand can be achieved by the proposed device through the alteration of the working wavelength numbers and the operation modes of optical switch. Definitely, we can increase the numbers of MRR in the logic circuit in order to achieve more complex logic operations. In a word, the proposed logic circuit can perform reconfigurable logic operations by using WDM technology. Note that although the high levels of the results are different attributed to the WDM technology, it does not affect the performance of the device since we can define the secondary high level as logic1 (Fig. 7(d)). In addition, some undesired small peaks and dips can be found in Fig. 7 resulting from the alteration of working status for the device, which has been discussed in detail in ref. 40. Note that the device can perform higher operation speed when the pre-emphasis electrical signals (logic operands) are used to reduce MRRs’ response time30. In fact, the modulation of the proposed device is to change the MRR’s resonant wavelength, in other word, all modulation schemes which can change the refractive index of the waveguide can be employed in the design of the device. Therefore, other advanced modulating schemes such as the carrier-depletion modulation and the electric field effects can also be employed to modulate the MRRs to achieve a higher speed operation of the device. However, the modulation efficiency for the carrier-depletion modulation and the electric field effects is relatively low. In order to obtain the faster operation speed as well as higher modulation efficiency, the optimization of the device will be a potential challenge in future. The power consumption of the device is related to the specific logic operation, which means the power consumptions are different if the device performs different logic operations. The specific power consumptions of several logic operations demonstrated in the paper are given in Table 2. In fact, the supplied DC power consumption can be greatly decreased by fabricating air trench around MRR. Therefore, the total power consumption can be further decreased, which has been left for our future works.

Conclusion

We report a reconfigurable electro-optic directed circuit which can implement any logic operation using cascaded MRRs, and in order to realize a high operation speed, the carrier injection scheme is employed to modulate the MRRs. As a proof of principle, a three-input reconfigurable logic circuit based on three cascaded carrier-injection MRRs is designed and fabricated, and several typical logic operations of three-operand with an operation speed of 100 Mbps are finally demonstrated successfully.

Methods

Device fabrication

248-nm deep ultraviolet (UV) lithography is employed to define the waveguide patterns, and Inductively Coupled Plasma (ICP) is employed to etch the top silicon layer (Fig. 8(a,b)). The bus and ring waveguides are formed by a submicron rib waveguide with a height of 220 nm, a width of 400 nm, and a slab thickness of 70 nm, which only supports quasi-TE fundamental mode (the quasi-TE fundamental mode of the waveguide is shown in inset in Fig. 1(a)). The radii of MRRs are designed to be 10.00 μm, 10.03 μm and 10.06 μm in order to induce slightly different initial resonant wavelengths to the three MRRs. The gaps between the ring and straight waveguides are chosen to be 260 nm to achieve high extinction ratios. In order to enhance the coupling efficiency between the waveguide and the lensed fiber, the 200-μm-long linearly inversed nanotapers with 180-nm-wide tip are fabricated on the input and output terminals. Following the silicon waveguides are formed, the p- and n-doping regions with phosphorus and boron concentrations of 5.5 × 1020 cm −3 are formed around ring waveguides to form PIN modulation structure which are employed to modulate MRRs. In order to achieve high modulation efficiency and low optical absorption loss, the edge-to-edge distance from the doped regions to the ring waveguides is designed about 500 nm (Fig. 8(c,d)). A 1.5-μm-thick SiO 2 layer is deposited as the upper cladding layer using plasma-enhanced chemical vapor deposition (PECVD). After that, the 150-nm-thick TiN microheaters are fabricated on the top of MRRs using deep UV photolithography and dry etching (Fig. 8(e)) in order to control the resonant wavelengths of MRRs accurately. Via holes to PIN diodes and microheaters are formed through two step etching processes (Fig. 8(f,g)), and then a 1-μm-thick Al layer is sputtered and patterned to form printed tracks and pads to connect the PIN diodes and microheaters (Fig. 8(h)). Finally, the end-face of the SSC (spot size converter) is exposed by a 110-μm-deep etching process as the world-to-chip interface in order to improve the coupling efficiency between the SSC and lensed fiber (Fig. 8(i)).

Processing flows of the device: (a,b) etching of the top Si layer by 150 nm and 70 nm, respectively, (c,d) p- and n- doping and through boron and phosphorus implantation, (e) deposition and etching of the TiN layer to form the microheater, (f,g) etching of the SiO 2 layer to form the via holes to the PIN diodes and microheaters, (h) deposition and etching of the Al layer to form the wires and pads, (i) deep etching to form the end-face of the SSCs.

References

Soref, R. The past, present, and future of silicon photonics. IEEE J. Sel. Topics Quantum Electron. 12, 1678–1687 (2006).

Fuchs, E. R. H., Kirchain, R. E. & Liu, S. The future of silicon photonics: not so fast? Insights from 100 g ethernet lan transceivers. IEEE J. Sel. Topics Quantum Electron. 29, 2319–2326 (2011).

Xu, Q., Dong, P. & Lipson, M. Breaking the delay-bandwidth limit in a photonic structure. Nature Phys. 3, 406–410 (2007).

Yang, L., Ji, R., Zhang, L., Ding, J. & Xu, Q. On-chip CMOS-compatible optical signal processor. Opt. Express 20, 13560–13565 (2012).

Caulfield, H. J. & Dolev, S. Why future supercomputing requires optics. Nature Photon. 4, 261–263 (2010).

Vukovic, N. et al. Ultrafast optical control using the Kerr nonlinearity in hydrogenated amorphous silicon microcylindrical resonators. Sci. Rep. 3, 2885 (2013).

Xia, F., Rooks, M., Sekaric, L. & Vlasov, Y. Ultra-compact high order ring resonator filters using submicron silicon photonic wires for on-chip optical interconnects. Opt. Express 15, 11934–11941 (2007).

Bogaerts, W. et al. Silicon-on-insulator spectral filters fabricated with CMOS technology. IEEE J. Sel. Topics Quantum Electron. 16, 33–44 (2010).

Long, Y., Xia, J., Zhang, Y., Dong, J. & Wang, J. Photonic crystal nanocavity assisted rejection ratio tunable notch microwave photonic filter. Sci. Rep. 7, 40223 (2017).

Ji, R. Q. et al. Five-port optical router for photonic networks-on-chip. Opt. Express 19, 20258–20268 (2011).

Sherwood-Droz, N. et al. Optical 4 × 4 hitless slicon router for optical networks-on-chip (noc). Opt. Express 16, 15915–15922 (2008).

Yang, L. et al. Reconfigurable nonblocking 4-port silicon thermo-optic optical router based on Mach–Zehnder optical switches. Opt. Lett. 40, 1402–1405 (2015).

Rong, H. et al. A continuous-wave raman silicon laser. Nature 433, 725–728 (2005).

Rong, H. et al. A cascaded silicon raman laser. Nature Photon. 2, 170–174 (2008).

Rong, H. et al. Low-threshold continuous-wave Raman silicon laser. Nature Photon. 1, 232–237 (2007).

Boyraz, O. & Jalali, B. Demonstration of a silicon Raman laser. Opt. Express 12, 5269–5273 (2004).

Takahashi, Y. et al. A micrometre-scale Raman silicon laser with a microwatt threshold. Nature 498, 470–474 (2013).

Zheng, X. et al. A tunable 1 × 4 silicon CMOS photonic wavelength multiplexer/demultiplexer for dense optical interconnects. Opt. Express 18, 5151–5160 (2010).

Dong, P. et al. Low power and compact reconfigurable multiplexing devices based on silicon microring resonators. Opt. Express 18, 9852–9858 (2010).

Tibuleac, S. & Filer, M. Transmission impairments in DWDM networks with reconfigurable optical add-drop multiplexers. J. Lightwave Technol. 28, 557–568 (2010).

Liu, A. et al. Wavelength Division Multiplexing Based Photonic Integrated Circuits on Silicon-on-Insulator Platform. IEEE J. Sel. Topics Quantum Electron. 16, 23–32 (2010).

Geng, M. et al. Four-channel reconfigurable optical add-drop multiplexer based on photonic wire waveguide. Opt. Express 17, 5502–5516 (2009).

Vos, K. D., Bartolozzi, I., Schacht, E., Bienstman, P. & Baets, R. Silicon-on-insulator microring resonator for sensitive and label-free biosensing. Opt. Express 15, 7610–7615 (2007).

Passaro, V. M. N. & Leonardis, F. D. Modeling and design of a novel high-sensitivity electric field silicon-on-insulator sensor based on a whispering-gallery-mode resonator. IEEE J. Sel. Topics Quantum Electron. 12, 124–133 (2006).

Yi, H. X., Citrin, D. S. & Zhou, Z. P. Highly sensitive silicon microring sensor with sharp asymmetrical resonance. Opt. Express 18, 2967–2972 (2010).

Sun, H., Chen, A. & Dalton, L. R. A reflective microring notch filter and sensor. Opt. Express 17, 10731–10737 (2009).

Klimov, N. N., Mittal, S., Berger, M. & Ahmed, Z. On-chip silicon waveguide Bragg grating photonic temperature sensor. Opt. Lett. 40, 3934–3936 (2015).

Liu, A. et al. A high-speed silicon optical modulator based on a metal-oxide-semiconductor capacitor. Nature 427, 615–618 (2004).

Xu, Q., Schmidt, B., Pradhan, S. & Lipson, M. Micrometre-scale silicon electro-optic modulator. Nature 435, 325–327 (2005).

Xu, Q., Manipatruni, S., Schmidt, B., Shakya, J. & Lipson, M. 12.5 Gbit/s carrier-injection-based silicon micro-ring silicon modulators. Opt. Express 15, 430–436 (2007).

Liu, A. et al. High-speed optical modulation based on carrier depletion in a silicon waveguide. Opt. Express 15, 660–668 (2007).

Alloatti, L. et al. 42.7 Gbit/s electro-optic modulator in silicon technology. Opt. Express 19, 11841–11851 (2011).

Yang, L. & Ding, J. F. High-speed silicon Mach-Zehnder optical modulator with large optical bandwidth. J. Lightwave Technol. 32, 966–970 (2014).

Zhou, L. & Poon, A. W. Silicon electro-optic modulators using p-i-n diodes embedded 10-micron-diameter microdisk resonators. Opt. Express 14, 6851–6857 (2006).

Xiao, X. et al. 25 Gbit/s silicon microring modulator based on misalignment-tolerant interleaved PN junctions. Opt. Express 20, 2507–2515 (2012).

Xiao, X. et al. 44-Gb/s Silicon Microring Modulators Based on Zigzag PN Junctions. Photon. Technol. Lett. 24, 1712–1714 (2012).

Tu, X. G., Liow, T. Y., Song, J. F., Yu, M. B. & Lo, G. Q. Fabrication of low loss and high speed silicon optical modulator using doping compensation method. Opt. Express 19, 18029–18035 (2011).

Ding, Y. H. et al. Effective electro-optical modulation with high extinction ratio by a graphene–silicon microring resonator. Nano Letters 15, 4393–4400 (2015).

Zhang, L. et al. Demonstration of directed XOR/XNOR logic gates using two cascaded microring resonators. Opt. Lett. 35, 1620–1622 (2010).

Tian, Y., Zhang, L. & Yang, L. Electro-optic directed AND/NAND logic circuit based on two parallel microring resonators. Opt. Express 20, 16794–16800 (2012).

Zhang, L. et al. Electro-optic directed logic circuit based on microring resonators for XOR/XNOR operations. Opt. Express 20, 11605–11614 (2012).

Tian, Y. et al. Reconfigurable electro-optic logic circuits using microring resonator-based optical switch array. IEEE Photon. J. 8, 7801908 (2016).

Qiu, C., Ye, X., Soref, R., Yang, L. & Xu, Q. Demonstration of reconfigurable electro-optical logic with silicon photonic integrated circuits. Opt. Lett. 37, 3942–3944 (2012).

Qiu, C., Gao, W., Soref, R., Robinon, J. T. & Xu, Q. Reconfigurable electro-optical directed-logic circuit using carrier-depletion micro-ring resonators. Opt. Lett. 39, 6767–6770 (2014).

Yang, L., Zhang, L., Guo, C. & Ding, J. XOR and XNOR operations at 12.5 Gb/s using cascaded carrier-depletion microring resonators. Opt. Express 22, 2996–3012 (2014).

Hardy, J. & Shamir, J. Optics inspired logic architecture. Opt. Express 15, 150–165 (2007).

Caulfield, H. J., Soref, R. A. & Vikram, C. S. Universal reconfigurable optical logic with silicon-on-insulator resonant structures. Photon. Nanostruct. Fundam. Appl. 5, 14–20 (2007).

Xu, Q. F. & Soref, R. A. Reconfigurable optical directed-logic circuits using microresonator-based optical switches. Opt. Express 19, 5244–5259 (2011).

Dong, P. et al. Thermally tunable silicon racetrack resonators with ultralow tuning power. Opt. Express 18, 20298–20304 (2010).

Acknowledgements

This work was supported by the National Science Foundation of China (NSFC) (61405082); The Natural Science Foundation of Gansu Province (145RJZA110); The Fundamental Research Funds for the Central Universities under Grant (lzujbky-2016-k05).

Author information

Authors and Affiliations

Contributions

Y.H.T. designed and supervised the research. Z.L.L., H.F.X. and G.L.Z. carry out the experiments. Z.L.L. and G.P.L. analyzed the experimental data. Y.H.T., Z.L.L. and J.H.Y. designed experiments. Z.L.L., J.F.D., L.Z. and L.Y. worked on the interpretation of results and wrote the manuscript.

Corresponding author

Ethics declarations

Competing Interests

The authors declare that they have no competing interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Tian, Y., Liu, Z., Xiao, H. et al. Experimental demonstration of a reconfigurable electro-optic directed logic circuit using cascaded carrier-injection micro-ring resonators. Sci Rep 7, 6410 (2017). https://doi.org/10.1038/s41598-017-06736-5

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-017-06736-5

This article is cited by

-

Reconfigurable optical logic in silicon platform

Scientific Reports (2024)

-

Wafer-scale nanofabrication of telecom single-photon emitters in silicon

Nature Communications (2022)

-

Recent advances in integrated optical directed logic operations for high performance optical computing: a review

Frontiers of Optoelectronics (2022)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.