Abstract

Complementary organic electronics is a key enabling technology for the development of new applications including smart ubiquitous sensors, wearable electronics, and healthcare devices. High-performance, high-functionality and reliable complementary circuits require n- and p-type thin-film transistors with balanced characteristics. Recent advancements in ambipolar organic transistors in terms of semiconductor and device engineering demonstrate the great potential of this route but, unfortunately, the actual development of ambipolar organic complementary electronics is currently hampered by the uneven electron (n-type) and hole (p-type) conduction in ambipolar organic transistors. Here we show ambipolar organic thin-film transistors with balanced n-type and p-type operation. By manipulating air exposure and vacuum annealing conditions, we show that well-balanced electron and hole transport properties can be easily obtained. The method is used to control hole and electron conductions in split-gate transistors based on a solution-processed donor-acceptor semiconducting polymer. Complementary logic inverters with balanced charging and discharging characteristics are demonstrated. These findings may open up new opportunities for the rational design of complementary electronics based on ambipolar organic transistors.

Similar content being viewed by others

Introduction

Organic electronics have been extensively investigated over the last decade1,2,3 for a wide range of new applications including healthcare4, 5, smart sensors6,7,8, wearable devices9, 10, etc. The aforementioned applications urgently require complementary technologies where both electron (n-type) and hole (p-type) conducting organic thin-film transistors (OTFTs) are available. In conventional complementary OTFT technologies, the fabrication of p- and n-type transistors requires the separate deposition, patterning and optimization of two different semiconducting materials11,12,13,14,15,16, one for each transistor type17, 18. While this may seem to be a simple approach, in practice, the n-type and p-type organic semiconductors need to exhibit comparable electronic properties, requiring ad-hoc process conditions and optimizations19, 20. These may result in complex fabrication procedures, which are not desirable for low-cost and mass production.

Ambipolar organic semiconductors, in which both holes and electrons can be injected and transported in a single semiconducting layer, significantly reduce the complexity of the fabrication processes. Depending on the applied voltage, ambipolar OTFTs can operate as a p-n junction, or p-type and n-type transistors21, 22. Therefore, ambipolar OTFTs have attracted considerable attention for their application in complementary metal–oxide semiconductor (CMOS) digital integrated circuits23, 24 and light-emitting field-effect transistors25, 26.

Continuous transitions from the hole-conduction state to the electron-conduction state are typically observed in ambipolar OTFTs. In other words, these transistors do not have large on-off current ratios as they do not have a well-defined off-state region. As a result, ambipolar conduction results in large power consumption in electronic circuits. One of the approaches to overcome this fundamental limitation is to modify the gate dielectric and/or the charge injecting contacts, so that the polarity of the transistor is permanently set22, 27. Another approach is to control the polarity of the transistor by using multiple gate electrodes. Recently, multi-gate techniques such as split-gate and tri-gate architectures have been demonstrated as viable and effective approaches to electrostatically select the polarity of ambipolar OTFTs28,29,30,31,32. Depending on the voltage bias of the secondary-gate, an ambipolar OTFT can operate as either a unipolar p-type or n-type transistor. However, the balance between hole and electron conduction in ambipolar semiconductors still remains a key requirement for achieving high-performance complementary electronics. The imbalance between hole and electron transport reduces the noise immunity and the DC gain in a logic inverter. Despite recent improvement in terms of charge transport (mobility > 1 cm2 V−1 s−1)33, 34, 35 most organic ambipolar semiconductors exhibit a significantly larger hole mobility than electron mobility36, 37 or vice versa34, 35. In addition, the turn-on voltages of p-type and n-type are typically different in ambipolar OTFTs38, 39. Previous research for balancing electron and hole current has focused on designing new materials40,41,42,43 or devising a new approach to blend44, 45 or stack46, 47 two materials. While such approaches are very promising, the balance between hole and electron currents may vary depending on the device structure40, 43 or manufacturing process42. Therefore, there is a great need to more clearly understand and control the p-type and n-type charge transport properties through a comprehensive physical analysis.

Electrical characteristics of OTFTs depend on the environmental conditions (ambient, vacuum or nitrogen atmosphere)48, 49. In particular, air exposure has a significant effect on charge transport properties. For example, it has been reported that degradation of electron transport occurs in n-type semiconductors due to interaction with oxygen and/or water50, 51. In addition, enhancing p-type hole transport by intentionally allowing interaction with diluted air has been also reported52. The degree of interaction with air is even more important in ambipolar OTFTs since both holes and electron transports need to be considered simultaneously. It has been reported that benzodifurandione-based oligo (p-phenylene vinylene) (BDOPV) exhibited ambipolar characteristics when fabricated under ambient condition while the same polymer showed unipolar n-type transport under nitrogen atmosphere34. This indicates that the amount of air exposure can be a key design parameter to control electron and hole current in an ambipolar OTFT with a careful study of atmospheric effect.

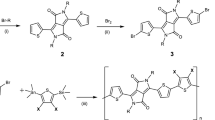

In this work, we show that hole and electron transport can be balanced by controlling the air exposure time and the temperature of the thermal treatment in poly-(diketopyrrolopyrrole-terthiophene) (PDPP3T) ambipolar semiconducting polymer. The analysis is based on electrical measurements, ultraviolet photoelectron spectroscopy (UPS), X-ray photoelectron spectroscopy (XPS), and two-dimensional (2D) numerical simulations. Based on this comprehensive analysis we demonstrate split-gate ambipolar OTFTs with balanced hole and electron characteristics. When the devices are connected in a complementary inverter configuration, larger gain and output swing were achieved compared to the values from inverters with unbalanced n/p characteristics.

Results

Experimental observation of impact of the air-exposure on the transistor properties

First, we fabricate conventional ambipolar OTFTs using PDPP3T, a recently developed DPP based donor-acceptor ambipolar copolymer23, 53, as active layer in a bottom-gate bottom-contact geometry. The cross-section of a transistor is shown in Fig. 1a. The channel length and width are L = 6 µm and W = 810 µm, respectively. The details of the fabrication method are given in the Methods section. As shown in Fig. 1b, the PDPP3T OTFTs operated in air exhibit unipolar p-type only characteristics (blue circles) and the electron transport is completely suppressed. In contrast, the same OTFTs show ambipolar transfer characteristics (red circles) when measured in vacuum after thermal treatment. The transfer characteristics of vacuum annealed PDPP3T OTFTs as a function of air exposure time are shown in Fig. 1c. As the exposure time is increased, the transfer characteristics shift towards positive gate voltages and the electron conduction is progressively suppressed (Fig. 1c). The transition voltage from p-type to n-type operation, namely the turn-on voltage, is monitored over the exposure time. Fig. 1d shows that the turn-on voltage (VTO) shifts from about 0 V to 24 V after 5 minutes of air exposure, and VTO = 38 V after 3 hours. In order to further investigate the effect of air exposure on the hole transport in PDPP3T OTFTs, we extracted the width-normalized contact resistances (RP) as a function of the exposure time from the OTFTs electrical characteristics54. Fig. 1e shows that the contact resistance decreases from about 5 kΩ·cm to 2 kΩ·cm, which suggests that the hole injection is enhanced.

PDPP3T ambipolar transistor architecture and characteristics as a function of air exposure time. (a) PDPP3T molecular structure, its schematic and the energy band level. (b) Measured (symbols) transfer characteristics of PDPP3T ambipolar transistor at VD = −30 V in ambient atmosphere (blue) and in vacuum after annealing (red). Lines indicate results from 2D numerical simulations. Blue (green) line: simulation of air exposed PDPP3T OTFTs with (without) trap states. Red line: simulation of vacuum annealed PDPP3T OTFTs. (c) Measured transfer characteristics at VD = −50 V and VD = −30 V as a function of the air exposure time. (d) Turn-on voltage (VTO) of PDPP3T transistor as a function of the air exposure time. (e) Extracted contact resistance value of PDPP3T transistor as a function of the air exposure time.

Photoelectron spectroscopy

To investigate the effects of air exposure and thermal treatment, the electronic and physical structures of the PDPP3T films are studied by means of UPS and XPS in an ultra-high vacuum chamber. We measured UPS of PDPP3T films as-received (without annealing), and with in-situ thermal treatments, namely annealed at TA = 100 °C and TA = 140 °C. The changes in the electronic properties of PDPP3T film are probed by UPS with He I resonance line (photon energy 21.2 eV). Details on the extraction of the molecular orbital levels from UPS spectra are reported in the Methods section. The Fermi energy level EF = −4.6 eV is obtained by the secondary edge cutoff. The change in EF at various temperatures is very small (ΔEF = 0.05–0.06 eV, Fig. 2a). However, Fig. 2b shows that the leading edge of the HOMO with respect to EF gradually moves down from −1.04 eV to −1.47 eV (0.43 eV down-shift) as the temperature is increased by in-situ vacuum annealing. The UPS measurements reveal that the HOMO and LUMO levels are down-shifted by in-situ vacuum annealing while EF is almost pinned. According with previous works51, 55,56,57, the energy level shift can be attributed to atmospheric dipoles located at the surface of the PDPP3T.

In order to further investigate the effect of vacuum annealing, we perform XPS measurements with in-situ thermal treatments and after air exposure. Fig. 3a–c shows XPS spectra for C 1s, S 2p, and O 1s of PDPP3T films. The O 1s spectra are greatly reduced with in-situ annealing while C 1s and S 2p spectra do not change. Furthermore, we calculated XPS relative atomic ratios of C 1s, S 2p, and O 1s by integrating peak area values of all species. Fig. 3d shows that the relative concentration of O 1s increases when the PDPP3T is exposed to air and decreases when it is annealed in vacuum. This suggests that the atmospheric oxygen derivatives such as molecule oxygen and water present on the PDPP3T films exposed to air (with the diffusion of the species) are eliminated by the thermal treatment. In addition, we found that the diffused oxygen-related gas molecules existed in the bulk not the surface of film. We conducted XPS with both lower-energy (650 eV) and higher-energy photon source (1486.6 eV) to measure surface region and bulk region, respectively. With 650 eV photon energy, the intensity of O 1s was not changed by the in-situ annealing. With 1486.6 eV, on the other hand, we found the intensity of O 1s was reduced after the in-situ annealing as shown in Supplementary Fig. 10. This result indicates that annealing is necessary to eliminate the diffused gas molecules in the film. Our bottom-gate bottom-contact device is affected by the diffused oxygen-related gas molecules in the bulk since the charge transport channel is located at the bottom of the film.

XPS analysis of the PDPP3T. (a) C 1s core level spectra. (b) S 2p core level spectra. (c) O 1s core level spectra. Blue circle: as-received. Red circle: vacuum annealing at 100 °C. (d) XPS atomic ratio variations for C 1s, S 2p, and O 1s when the PDPP3T film was measured after the air exposure and the vacuum annealing.

2D numerical simulations

To gain more insight, we reproduced the measurements of vacuum annealed and air exposed PDPP3T OTFTs by means of 2D numerical simulations (Fig. 1b, full lines). The continuity, Poisson, and drift-diffusion transport equations are solved on a 2D grid. The charge flow at the metal–semiconductor interface is calculated by means of the thermionic field-emission theory, accounting for the actual 2D energy barriers, energy disorder, and the electric field distribution at the contacts31, 58. The simulation details are given in the Method section and input parameters are given in Supplementary Tables 1 and 2. For 2D numerical simulations, we used the gold work function to be −4.7 eV based on the UPS measurement (Supplementary Fig. 9), which is in good agreement with the −4.5–−5.5 eV energy range59, 60. Based on the molecular energy levels from CV measurement (Supplementary Fig. 7) and the results reported by Janssen et al.53, we used −3.61/−5.17 eV for the LUMO/HOMO level of the PDPP3T device before annealing. For the same device annealed at 140 °C, we used −4.04/−5.60 eV for the LUMO/HOMO level by adding the 0.43 eV down-shift based on the UPS results. Consequently, the charge injection barriers of electrons and holes are estimated to be approximately ΦBe = 0.66 eV and ΦBh = 0.90 eV. Dipoles due to the ODPA treatment used for reducing the gate leakage current61,62,63, are included by means of surface charges at the insulator-semiconductor interface Nis = 2.5 × 1012 cm−2, which is in agreement with our previous report32. The interface charges are readily estimated from the transition voltage, VTS = −5 V of the ambipolar characteristics shown in Fig. 1b (red circles).

Fig. 4 shows the electron and hole density of states (DOS) obtained from the 2D numerical simulations. In both cases the DOS (dashed black line) can be well approximated by the sum of two Gaussian functions, one for the tail states (full red line) and one for the deep states (full green line). We found that the electron and hole DOS are similar. More in detail, the total number of LUMO and HOMO states are the same (Nte = Nth = 2 × 1021 cm−3), while the electron energy disorder (σe = 80 meV) is slightly larger than the hole energy disorder (σh = 60 meV). Fig. 5a and b show the calculated hole and electron concentrations inside the vacuum annealed PDPP3T OTFTs. In Fig. 5a VG = −40 V, holes are injected from the source electrode (biased at VS = 0 V) while in Fig. 5b VG = 40 V electrons are injected from the drain electrode (biased at VD = −30 V). In both cases the injected charge carriers are accumulated at the insulator-semiconductor interface, forming the channel. The hole concentration is of about 8 × 1018 cm−3 and the electron concentration is of about 2 × 1018 cm−3. The slightly larger hole concentration can be attributed to the larger electron disorder (σe > σh).

Electron and hole density of states. The dashed line is the overall DOS approximated by the sum of two Gaussian functions. The tail (red line) and deep (green line) states are also shown. The electron DOS parameters are the following. Total density of LUMO tail and deep states are Nte = 2 × 1021 cm−3 and Nde = 1 × 1020 cm−3, respectively. The energy width of the LUMO tail and deep states are σte = 80 meV and σde = 120 meV, respectively. The hole DOS parameters are the following. Total density of HOMO tail and deep states are Nth = 2 × 1021 cm−3 and Ndh = 1 × 1020 cm−3, respectively. The energy width of the HOMO tail and deep states are σth = 60 meV and σdh = 120 meV, respectively. An additional Gaussian distribution of trap states (full blue line) describes the oxygen-induced. The Gaussian distribution is located at 0.35 eV below the LUMO level, with a total density of states NtO2 = 2 × 1020 cm−3 and a disorder energy width σtO2 = 50 meV. The other simulation parameters are provided in the Methods section.

Carrier distribution in PDPP3T ambipolar transistors. 2D numerical simulations. The applied voltages are VD = −30 V, and VS = 0 V. (a) P-type operation (VG = −40 V) and (b) N-type operation (VG = 40 V) without the atmospheric effects. (c) P-type operation (VG = −40 V) and (d) N-type operation (VG = 40 V) with the atmospheric effects.

Analysis of atmospheric effects on PDPP3T semiconductor

Using the UPS and XPS characterization of the PDPP3T semiconductor in combination with the 2D numerical simulations and the electrical characterization, we investigate the effect of air exposure on PDPP3T OTFTs. The UPS characterization reveals that after air exposure the LUMO and HOMO levels of PDPP3T are up-shifted by about 0.43 eV and become −3.61 and −5.17 eV, respectively. Therefore, the charge injection barriers to electrons and holes are estimated to be approximately ΦBe = 1.09 eV and ΦBh = 0.47 eV. The up-shift of HOMO level enhanced the hole injection because the reduction of ΦBh in air (=0.47 eV) compared to ΦBh in vacuum (=0.90 eV) resulted in thinner width of Schottky barrier (SB) at the HOMO-Au junction (Fig. 1e). Moreover, the XPS characterization suggests that the air exposure causes an increase of the oxygen and the water level in the polymer. These two molecules show different nature of interaction. In the presence of both water and oxygen, the PDPP3T polymer anion can be oxidized according to the following chemical equation51, 64:

This, in turn, causes the transfer of electrons from the polymer chain to the OH− groups, where mobile electrons are removed and cannot contribute to transport48. In a transistor, this leads to the formation of a matrix of fixed OH− ions in the channel, which causes a positive shift of the turn on voltage, without any polymer degradation (so that the vacuum annealing can recover n-type charge properties). The oxidation potential of the polymer anion can be considered equal to its electron affinity (the lowest unoccupied molecular orbital (LUMO) energy level). As a rule of thumb, it is generally assumed that the higher is the electron affinity of the polymer, the higher is the stability of the polymer anion in air. According to the previous work51, a LUMO level deeper than −3.7 eV should be sufficient to guarantee the stability of the polymer in the presence of water, while a LUMO level deeper than −4.9 eV is needed to avoid polymer anion oxidation in the presence of both water and oxygen. In our case the LUMO energy level of the neutral PDPP3T polymer is located at −3.61 eV and hence the effect of both water and oxygen molecules should be accounted for. This is further confirmed by the measured transfer characteristics as a function of the exposure time shown in Fig. 1c. When the exposure time is increased, the amount of oxygen and water in the PDPP3T film increases, and, consequently, the turn on voltage (Fig. 1d) shifts towards positive voltages. Therefore, we included the effect of the fixed OH− ions in our numerical simulations as surface charges located at the insulator-semiconductor interface. We estimated that the surface charges increased by 6 × 1012 cm−2 after 3 hours of exposure, thus resulting in an overall surface charges Nis = 8.5 × 1012 cm−2.

Fig. 1b shows the current calculated by accounting for the up-shift of the LUMO and HOMO levels by atmospheric effects. It is worthwhile noting the increased Nis (dashed green line) does not explain the measured transfer characteristic of air exposed PDPP3T OTFTs. In fact, the calculated current exceeds the measured current by orders of magnitude when VG > 20 V, while they are in good agreement when VG < 20 V. This can be explained as follows. When VG > 20 V, electron becomes the major carrier for the current transport. The electron current decreases significantly because the electronic coupling between the polymer π electrons and the oxygen molecules results in an increase of the electron trapping rate. In contrast, hole current is dominant when VG < 20 V so that increased electron trap density does not affect current level. Similar to what was previously reported for n-type polymer semiconductors51, 65 the electronic coupling eventually gives rise to an intra-gap electron trap level, typically located at 0.3–0.5 eV below the LUMO level. For short exposure time the concentration of traps is not sufficient to reduce the electron current (viz. Fig. 1c, t = 5 min), while for longer exposure time the density of trap sites becomes comparable to the charge density in the accumulation layer, and the electron current drops by orders of magnitude (viz. Fig. 1c, t = 180 min). By reproducing the measurements of air exposed PDPP3T OTFTs over the whole range of applied voltages (Fig. 1b, red full line), we found that the density of trap sites can be approximated with a Gaussian distribution located at 0.35 eV below the LUMO level, with a total density of states NtO2 = 2 × 1020 cm−3 and a disorder energy width σtO2 = 50 meV. The calculated trap states is shown in Fig. 4 (full blue line). Fig. 5c and d show the holes and electrons concentration within the air exposed PDPP3T semiconductor, respectively. We found that the hole concentration in the channel exceeds 5 × 1018 cm−3 (Fig. 5c), while the electron concentration is lower than 5 × 1015 cm−3 (Fig. 5d) because of the traps. According to several studies50, 51, 66, we found that the polymer interaction with water results in an electrochemical oxidation of the polymer, while the interaction with the molecular oxygen gives rise to a formation of localized electron traps below the LUMO energy level. These findings extend to the case of ambipolar semiconductors34, 67 and air-induced electron trapping in n-type polymer semiconductors51 as reported in previous works, thus revealing that vacuum annealing is crucial to obtain ambipolar charge transport in PDPP3T.

Control of hole and electron properties in split-gate ambipolar TFTs

In order to investigate the effect of different annealing temperatures on the hole and electron transport in the PDPP3T, we fabricated split-gate OTFTs. It is worth noting that split-gate transistors enable to electrically select the transistor polarity, and, in turn, to easily disentangle and quantify electron and hole conduction. A simplified cross-section and a top view optical image of the split-gate OTFT are shown in Fig. 6a and b, respectively. In a split-gate transistor the gate electrode is divided into two parts, namely the main gate and the side gate. The side gate is used to inhibit the unwanted charge injection at the drain electrode31, 32. Four annealing temperatures are applied, thus setting four different conditions: TI = 100 °C (condition I), TII = 140 °C (condition II), TIII = 180 °C (condition III), and TIV = 200 °C (condition IV). Thermal treatments are performed in ultra-high vacuum (<10−6 torr). Note that all electrical measurements were carried out in room temperature after each annealing treatment. Further details on the thermal treatment conditions and the split-gate ambipolar OTFTs fabrication are given in the Method section.

PDPP3T split-gate ambipolar TFTs and their output characteristics as a function of vacuum annealing condition. (a) Schematic of device structure. (b) Top view optical image. The length of the scale bar is 200 μm (black). Measured output characteristics at (c) TI = 100 °C. (d) TII = 140 °C. (e) TIII = 180 °C. (f) TIV = 200 °C. Unipolar p-type operation at VSIDE = −60 V. Unipolar n-type operation at VSIDE = 60 V.

Fig. 6c–f show the measured output characteristics of split-gate PDPP3T OTFTs operating as unipolar p-type (VSIDE = −60 V) or n-type (VSIDE = 60 V) transistors. As the annealing temperature is increased from TI = 100 °C to TIII = 180 °C, the hole current decreases while electron current increases. At the optimal annealing condition TIII, symmetric and balanced p- and n-type output characteristics with almost same drain current (about 8 µA) are obtained. With further increase of the annealing temperature (condition IV, TIV = 200 °C) both electron and hole current were decreased. To investigate the electrical degradation at higher temperature annealing, we conducted further experiments such as atomic force microscopy (AFM), grazing-incidence wide-angle X-ray scattering (GIWAXS), near edge X-ray absorption fine structure (NEXAFS), differential scanning calorimeter (DSC), and thermal gravimetric analysis (TGA). The measurement results revealed that the electrical degradation above 200 °C was not induced by chemical decomposition but by formation of voids inside the semiconductor (Supplementary Figs 1–6 and Table 3).

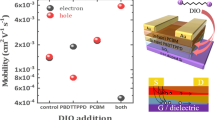

Next, we measured the transfer characteristics of split-gate PDPP3T OTFTs operated as p-type or n-type transistors as a function of the annealing temperature (Fig. 7a–d). We found that at the optimal annealing condition the transfer characteristics are well balanced, with comparable maximum current and turn-on voltage. More in detail, Fig. 8a shows the saturation mobilities in the case of p-type and n-type operations. The mobility for p-type (µh) decreases with the increase of the temperature while the mobility for the n-type (µe) increases until TIII = 180 °C and decreases at TIV = 200 °C. At the optimal annealing condition TIII, we observed similar mobility for both hole and electron conductions, which amounted to µh = 0.026 cm2 V−1 s−1 and µe = 0.012 cm2 V−1 s−1, respectively. Fig. 8b shows the turn-on voltage (Vto,p, Vto,n) as a function of the annealing temperature obtained when the split-gate PDPP3T OTFT is operated as p-type or n-type transistor. Both Vto,p and Vto,n are reduced by increasing the temperature and they are comparable at the optimal annealing condition TIII. Furthermore, we quantified the balancing between hole and electron conduction as the ratio between the corresponding on-currents (In/Ip) at |VD| = 40 V, |VG| = 80 V, and |VSIDE| = 60 V. As shown in Fig. 8c, the polarity balance are 0.01, 0.12, 1.1 and 2.24 in the cases TI = 100 °C, TII = 140 °C, TIII = 180 °C, and TIV = 200 °C, respectively. This confirms that the annealing condition III results in the optimal condition. We further investigate the effect of the annealing temperature by calculating the hole and electron channel resistances (viz. RhCh, ReCh) from the measured output characteristics54. Fig. 8d shows that RhCh increases by raising the annealing temperature while ReCh decreases by increasing the annealing temperature from TI to TIII. At the optimal annealing temperature TIII = 180 °C, RhCh(III) ≈ ReCh(III) in the whole range of gate voltages, thus confirming that balanced hole and electron transport is achieved.

Electrical transfer characteristics of PDPP3T split-gate ambipolar TFTs depending on vacuum annealing condition. (a) Measured transfer characteristics at (a) TI = 100 °C. (b) TII = 140 °C. (c) TIII = 180 °C. (d) TIV = 200 °C. Unipolar p-type operation at VD, VSIDE = −60 V. Unipolar n-type operation at VD, VSIDE = 60 V.

Impact of the vacuum annealing on the transistor electrical properties. (a) Extracted saturation mobilities as a function of vacuum annealing condition and (b) Turn-on voltage. (c) Polarity balance: defined as electron/hole current ratio at |VG| = 80 V. |VD| = 40 V, and |VSIDE| = 60 V. (d) Extracted channel resistance of the PDPP3T split-gate ambipolar TFTs. Orange diamond: TI = 100 °C. Red circle: TII = 140 °C. Blue triangle: TIII = 180 °C. Green square TIV = 200 °C.

Complementary inverters

As a relevant application example, we fabricated complementary inverters with PDPP3T split-gate OTFTs operated as p-/n-type unipolar transistors. The simplified cross-section of the split-gate complementary inverter is shown in Fig. 9a. In order to evaluate the impact of the annealing temperature on the inverter performance, we measured PDPP3T split-gate inverters at various annealing temperatures (namely TII, TIII, and TIV). The ratio between the maximum hole and electron current (IONh/IONe) depends on the thermal treatment and results 1/0.12 (TII), 1/1.1 (TIII), and 1/2.5 (TIV). The corresponding inverter transfer characteristics (VO-VI) are measured and the output swing together with the gain G = dVO/dVI are displayed in Fig. 9b. The transfer characteristic obtained at the optimal annealing temperature TIII is shown in Fig. 9c and the calculated gain is displayed in Fig. 9d. The maximum gain is larger than 14 (when VDD = 50 V) and 120 (when VDD = 100 V, Supplementary Fig. 14). The output swing is 75% of VDD, thus showing superior performances with respect to state-of-art split-gate inverters31. In contrast, the inverter performances are seriously degraded when the hole and electron conduction are not well balanced. Indeed, in inverters fabricated with non-balanced ambipolar OTFTs the gain is lower than 5 and the output swing is reduced to 57% of VDD.

Impact of the polarity balance on the inverter performance. (a) Schematic of complementary split-gate PDPP3T inverter structure. (b) Output swing and gain as a function of the polarity balance. (c) Measured inverter characteristics (VOUT vs. VIN) at the optimal condition of TIII = 180 °C. (d) Gain (=dVOUT/dVIN) at TIII = 180 °C.

In summary, we studied the impact of the air exposure and vacuum annealing in the ambipolar PDPP3T OTFTs on balancing the hole and electron conduction. Both conventional coplanar transistors and split-gate transistor architectures have been considered.

Analysis based on UPS, XPS, and 2D numerical simulations reveals that vacuum annealing decreases the hole current while increasing electron current. The combination of the molecular orbitals reorganization and the electron charge trapping by the polymer anion oxidation effect enables to explain the change of hole and electron current characteristics. We observed that hole and electron current of PDPP3T OTFTs were balanced at 180 °C annealing temperature. Furthermore, split-gate transistors showed the symmetric unipolar n- and p-type characteristics with comparable turn-on voltage as well as maximum currents. The detailed study of the effect of air-exposure on electron and hole current in ambipolar OTFTs provides fundamental guidelines for the efficient design of ambipolar polymeric materials and transistors.

We also demonstrated a complementary inverters based on split-gate devices with balanced n- and p-type characteristics. The inverters show the larger gain and output swing than the counterparts with unbalanced n/p characteristics. Therefore, we believe that this work is a step forward towards the development of high-performance complementary ambipolar electronics for low-cost, mass production organic applications.

Methods

Photoelectron spectroscopy

Ultraviolet photoelectron spectroscopy (UPS) measurements were performed using He I (hv = 21.2 eV) source from a gas discharge lamp. The energy resolution was better than around 30 meV at room temperature. X-ray photoelectron spectroscopy (XPS) equipped with a photon source (Al-Ka(1486.6 eV) and He I (21.2 eV)) was employed. XPS was conducted at the Korea Basic Science Institute (KBSI).

The cyclic voltammetry (CV) measured value for HOMO level (−5.17 eV) was the same as that in the literature53 (Supplementary Fig. 7). Hence, we adopted the HOMO/LUMO level of PDPP3T from the literature for the numerical simulation. The value we took from the UPS measurement of PDPP3T film was the HOMO level down-shift (−0.43 eV) due to vacuum annealing.

Devices fabrication

Bottom gate/bottom contact conventional and split-gate ambipolar TFTs were fabricated on having SiO2/Si substrate. Bottom gate electrodes (aluminum, 200 nm) were deposited using an e-beam evaporator and were patterned using the dry metal etching method. Gate dielectric layers, aluminum oxide (200 nm), were deposited using the atomic layer deposition method. The source/drain electrodes (Au, 100 nm) were deposited on top of the aluminum oxide using e-beam evaporation and lift-off lithography. Inductively Coupled Plasma (ICP) etching was used for oxide etching to form via-holes from bottom electrodes to source/drain electrodes. The samples were dipped in a solution of 10 mM of octadecylphosphonic acid (ODPA) in Isopropyl alcohol (IPA) for 3–5 days after being exposed to UV-ozone for 15 min. Then, PDPP3T, from Solarmer, was dissolved in 1, 2-dichlorobenzene (ODCB) to obtain 13 mg mL−1 and spin-coated. The samples were vacuum-annealed at thermal conditions in ultra-high vacuum (<10−6 torr) as follows. TI = 100 °C. TII = 140 °C. TIII = 180 °C. TIV = 200 °C.

The bottom gate/bottom contact conventional ambipolar TFTs have the channel length and width equal to L = 6 μm and W = 848 μm. The split-gate ambipolar TFTs have the channel length, width, and the gate-gap equal to L = 6 μm, W = 810 μm, and Gap = 1 μm, respectively. All split-gate inverter circuits have a channel length (L) = 12 μm and width (W) = 800 μm for n-type transistor and L = 6 μm and W = 800 μm for p-type transistor.

Electrical characterizations

All devices were measured in a vacuum probe station (Keithley 4200-SCS) and LCR meter (E4980A). The electrical characterizations of the conventional ambipolar TFTs and the split-gate ambipolar TFTs as a function of the annealing condition were conducted by measuring the same devices, respectively. The saturation mobility was extracted using the following equation (2):

The measured Ci = 40 nF cm−2, which is in agreement with a relative permittivity of the Al2O3 equal to 9. The voltage transfer characteristics (VTC) of the split-gate inverters were measured at VDD = 50 V.

Two-dimensional numerical simulations

The coupled drift-diffusion, Poisson, and current continuity equations are solved together30, 32, 58. The electron and hole DOS are approximated by the sum of two Gaussian functions. An additional Gaussian DOS describes the oxygen-induced trap sites when the OSC is exposed to air. The DOS is shown in Fig. 4 and the DOS parameters are listed in the Supplementary Tables 1 and 2. The simulation parameters are the following: relative permittivity of semiconductor εrs = 3, relative permittivity of insulator εri = 9, hole mobility μh = 0.1 cm2 V−1 s−1, electron mobility μe = 0.1 cm2 V−1 s−1, gold electrodes work function ΦAu = −4.7 eV, Schottky barrier lowering ∆ΦB = e [e E/(4 π ε0 εrs)]1/2, where e is the elementary charge, E is the electric field, and ε0 is the vacuum permittivity. The highest occupied molecular orbital (HOMO) energy level of vacuum annealed PDPP3T is EHOMO = −5.60 eV, and the lowest unoccupied molecular orbital (LUMO) energy level is ELUMO = −4.04 eV. After PDPP3T air exposure, EHOMO = −5.17 eV and ELUMO = −3.61 eV.

References

Crone, B. et al. Large-scale complementary integrated circuits based on organic transistors. Nature 403, 521–523 (2000).

Gelinck, G. H. et al. Flexible active-matrix displays and shift registers based on solution-processed organic transistors. Nat. Mater. 3, 106–110 (2004).

Smits, E. C. P. et al. Bottom-up organic integrated circuits. Nature 455, 956–959 (2008).

Schwartz, G. et al. Flexible polymer transistors with high pressure sensitivity for application in electronic skin and health monitoring. Nat. Commun. 4, 1859 (2013).

Khan, Y., Ostfeld, A. E., Lochner, C. M., Pierre, A. & Arias, A. C. Monitoring of Vital Signs with Flexible and Wearable Medical Devices. Adv. Mater. 28, 4373–4395 (2016).

Crone, B. et al. Electronic sensing of vapors with organic transistors. Appl. Phys. Lett. 78, 2229 (2001).

Torsi, L. et al. A sensitivity-enhanced field-effect chiral sensor. Nat. Mater. 7, 412–417 (2008).

Torsi, L., Magliulo, M., Manoli, K. & Palazzo, G. Organic field-effect transistor sensors: a tutorial review. Chem. Soc. Rev. 42, 8612–8628 (2013).

Sekitani, T. et al. Stretchable active-matrix organic light-emitting diode display using printable elastic conductors. Nat. Mater. 8, 494–499 (2009).

Matsuhisa, N. et al. Printable elastic conductors with a high conductivity for electronic textile applications. Nat. Commun. 6, 7461 (2015).

Li, Y. V. et al. Hybrid Inorganic/organic complementary circuits using PEALD ZnO and ink-jet printed diF-TESADT TFTs. Org. Electron. physics, Mater. Appl 14, 2411–2417 (2013).

Guerin, M. et al. High-gain fully printed organic complementary circuits on flexible plastic foils. IEEE Trans. Electron Devices 58, 3587–3593 (2011).

Daami, A. et al. Fully printed organic CMOS technology on plastic substrates for digital and analog applications. 2011 IEEE Int. Solid-State Circuits Conf. 328–330 (2011).

Smaal, W. et al. Complementary integrated circuits on plastic foil using inkjet printed n- and p-type organic semiconductors: Fabrication, characterization, and circuit analysis. Org. Electron. 13, 1686–1692 (2012).

Kwon, J., Kyung, S., Yoon, S., Kim, J.-J. & Jung, S. Solution-Processed Vertically Stacked Complementary Organic Circuits with Inkjet-Printed Routing. Adv. Sci 3, 1500439 (2016).

Seong, H., Choi, J., Jang, B. C., Kim, M. & Yoo, S. A Low-Voltage Organic Complementary Inverter with High Operation Stability and Flexibility Using an Ultrathin iCVD Polymer Dielectric and a Hybrid Encapsulation Layer. Adv. Electron. Mater 2, 1500385 (2016).

Nakayama, K. et al. High-Mobility Organic Transistors with Wet-Etch-Patterned Top Electrodes: A Novel Patterning Method for Fine-Pitch Integration of Organic Devices. Adv. Mater. Interfaces 1, 1300124 (2014).

Min, S.-Y. et al. Large-scale organic nanowire lithography and electronics. Nat. Commun. 4, 1773 (2013).

Kang, B. et al. Enhancing 2D growth of organic semiconductor thin films with macroporous structures via a small-molecule heterointerface. Nat. Commun. 5, 4752 (2014).

Yoo, H. et al. Self-assembled, millimeter-sized TIPS-pentacene spherulites grown on partially crosslinked polymer gate dielectric. Adv. Funct. Mater. 25, 3658–3665 (2015).

Bisri, S. Z., Piliego, C., Gao, J. & Loi, M. A. Outlook and emerging semiconducting materials for ambipolar transistors. Adv. Mater. 26, 1176–1199 (2014).

Nakano, M., Osaka, I. & Takimiya, K. Control of Major Carriers in an Ambipolar Polymer Semiconductor by Self-Assembled Monolayers. Adv. Mater. 29, 1602893 (2016).

Roelofs, W. S. C. et al. Fast ambipolar integrated circuits with poly(diketopyrrolopyrrole- terthiophene). Appl. Phys. Lett. 98, 96–98 (2011).

Zhu, W. et al. Flexible black phosphorus ambipolar transistors, circuits and AM demodulator. Nano Lett. 15, 1883–1890 (2015).

Zaumseil, J., Friend, R. H. & Sirringhaus, H. Spatial control of the recombination zone in an ambipolar light-emitting organic transistor. Nat. Mater. 5, 69–74 (2006).

Bürgi, L. et al. High-mobility ambipolar near-infrared light-emitting polymer field-effect transistors. Adv. Mater. 20, 2217–2224 (2008).

Khim, D. et al. Control of ambipolar and unipolar transport in organic transistors by selective inkjet-printed chemical doping for high performance complementary circuits. Adv. Funct. Mater. 24, 6252–6261 (2014).

Hsu, B. B. Y. et al. Split-gate organic field effect transistors: Control over charge injection and transport. Adv. Mater. 22, 4649–4653 (2010).

Hsu, B. B. Y. et al. Control of efficiency, brightness, and recombination zone in light-emitting field effect transistors. Adv. Mater. 24, 1171–1175 (2012).

Torricelli, F. et al. Ambipolar Organic Tri-Gate Transistor for Low-Power Complementary Electronics. Adv. Mater. 28, 284–290 (2016).

Yoo, H. et al. Asymmetric Split-Gate Ambipolar Transistor and Its Circuit Application to Complementary Inverter. Adv. Mater. Technol. 1, 1600044 (2016).

Yoo, H. et al. Reconfigurable Complementary Logic Circuits with Ambipolar Organic Transistors. Sci. Rep. 6, 35585 (2016).

Gao, Y. et al. High Mobility Ambipolar Diketopyrrolopyrrole-Based Conjugated Polymer Synthesized Via Direct Arylation Polycondensation. Adv. Mater. 27, 6753–6759 (2015).

Lei, T., Dou, J. H., Cao, X. Y., Wang, J. Y. & Pei, J. A BDOPV-based donor-acceptor polymer for high-performance n-type and oxygen-doped ambipolar field-effect transistors. Adv. Mater. 25, 6589–6593 (2013).

Sun, B., Hong, W., Yan, Z., Aziz, H. & Li, Y. Record high electron mobility of 6.3 cm2V-1s−1 achieved for polymer semiconductors using a new building block. Adv. Mater. 27, 2636–2642 (2014).

Lin, H.-W., Lee, W.-Y. & Chen, W.-C. Selenophene-DPP donor–acceptor conjugated polymer for high performance ambipolar field effect transistor and nonvolatile memory applications. J. Mater. Chem. 22, 2120 (2012).

Usta, H., Newman, C., Chen, Z. & Facchetti, A. Dithienocoronenediimide-based copolymers as novel ambipolar semiconductors for organic thin-film transistors. Adv. Mater. 24, 3678–3684 (2012).

Deng, Y. et al. (3E,8E)-3,8-Bis(2-oxoindolin-3-ylidene)naphtho-[1,2-b:5,6-b′]difuran-2,7(3H,8H)-dione (INDF) based polymers for organic thin-film transistors with highly balanced ambipolar charge transport characteristics. Chem. Commun. 51, 13515–13518 (2015).

Kim, F. S., Guo, X., Watson, M. D. & Jenekhe, S. A. High-mobility ambipolar transistors and high-gain inverters from a donor-acceptor copolymer semiconductor. Adv. Mater 22, 478–482 (2010).

James, D. I. et al. High-Performance Hole Transport and Quasi-Balanced Ambipolar OFETs Based on D-A-A Thieno-benzo-isoindigo Polymers. Adv. Electron. Mater 2, 1500313 (2016).

Gu, C., Hu, W., Yao, J. & Fu, H. Naphthalenediimide-benzothiadiazole copolymer semiconductors: Rational molecular design for air-stable ambipolar charge transport. Chem. Mater. 25, 2178–2183 (2013).

Mohebbi, A. R. et al. Emeraldicene as an acceptor moiety: balanced-mobility, ambipolar, organic thin-film transistors. Adv. Mater. 23, 4644–4648 (2011).

Jiang, T. et al. An ultra-low bandgap diketopyrrolopyrrole (DPP)-based polymer with balanced ambipolar charge transport for organic field-effect transistors. RSC Adv 6, 78720–78726 (2016).

Cho, J. et al. Facile and Fine Polarity-Tuning of Polymeric Semiconductors: The Effects of Nitrile Groups on Polymer-Polymer Blend Systems. Adv. Electron. Mater 2, 1600015 (2016).

Schwartz, G., Ke, T. H., Wu, C. C., Walzer, K. & Leo, K. Balanced ambipolar charge carrier mobility in mixed layers for application in hybrid white organic light-emitting diodes. Appl. Phys. Lett. 93, 073304 (2008).

Wang, H. et al. Ambipolar organic field-effect transistors with air stability, high mobility, and balanced transport. Appl. Phys. Lett. 88, 1–4 (2006).

Guan, Y.-S. et al. Donor-acceptor co-assembled supramolecular nanofibers with high and well-balanced ambipolar charge transport properties under ambient conditions. Chem. Commun 52, 4648–4651 (2016).

Shijeesh, M. R., Vikas, L. S., Jayaraj, M. K. & Puigdollers, J. Degradation study and calculation of density-of-states in PTCDI-C8 channel layer from the electrical characteristics of thin-film transistors. J. Appl. Phys. 116, 024507 (2014).

Soeda, J. et al. High electron mobility in air for N,N′-1H,1H-perfluorobutyldicyanoperylene carboxydi-imide solution-crystallized thin-film transistors on hydrophobic surfaces. Adv. Mater. 23, 3681–3685 (2011).

Di Pietro, R. & Sirringhaus, H. High resolution optical spectroscopy of air-induced electrical instabilities in n-type polymer semiconductors. Adv. Mater. 24, 3367–3372 (2012).

Di Pietro, R., Fazzi, D., Kehoe, T. B. & Sirringhaus, H. Spectroscopic investigation of oxygen- and water-induced electron trapping and charge transport instabilities in n-type polymer semiconductors. J. Am. Chem. Soc. 134, 14877–14889 (2012).

Lu, G. et al. Moderate doping leads to high performance of semiconductor/insulator polymer blend transistors. Nat. Commun. 4, 1588 (2013).

Bijleveld, J. C. et al. Poly(diketopyrrolopyrrole−terthiophene) for Ambipolar Logic and Photovoltaics. J. Am. Chem. Soc. 131, 16616–16617 (2009).

Torricelli, F., Ghittorelli, M., Colalongo, L. & Kovacs-Vajna, Z. M. Single-transistor method for the extraction of the contact and channel resistances in organic field-effect transistors. Appl. Phys. Lett. 104, 1–5 (2014).

Nishi, T., Kanai, K., Ouchi, Y., Willis, M. R. & Seki, K. Evidence for the atmospheric p-type doping of titanyl phthalocyanine thin film by oxygen observed as the change of interfacial electronic structure. Chem. Phys. Lett. 414, 479–482 (2005).

Tanaka, Y., Kanai, K., Ouchi, Y. & Seki, K. Oxygen effect on the interfacial electronic structure of C60 film studied by ultraviolet photoelectron spectroscopy. Chem. Phys. Lett. 441, 63–67 (2007).

Nishi, T., Kanai, K., Ouchi, Y., Willis, M. R. & Seki, K. Oxygen effects on the interfacial electronic structure of titanyl phthalocyanine film: p-Type doping, band bending and Fermi level alignment. Chem. Phys. 325, 121–128 (2006).

Torricelli, F., Colalongo, L., Raiteri, D., Kovács-Vajna, Z. M. & Cantatore, E. Ultra-high gain diffusion-driven organic transistor. Nat. Commun. 7, 10550 (2016).

Chen, Z. et al. High-Performance Ambipolar Diketopyrrolopyrrole- Thieno [3, 2- b] thiophene Copolymer Field-Effect Transistors with Balanced Hole and Electron Mobilities. Adv. Mater. 24, 647–652 (2012).

Braun, S., Salaneck, W. R. & Fahlman, M. Energy-level alignment at organic/metal and organic/organic interfaces. Adv. Mater. 21, 1450–1472 (2009).

Lv, Y. et al. Electroactive self-assembled monolayers for enhanced efficiency and stability of electropolymerized luminescent films and devices. Adv. Funct. Mater. 21, 2896–2900 (2011).

Kobayashi, S. et al. Control of carrier density by self-assembled monolayers in organic field-effect transistors. Nat. Mater. 3, 317–322 (2004).

Pernstich, K. P. et al. Threshold Voltage Shift in Organic Field Effect Transistors by Dipole-Monolayers on the Gate Insulator. J. Appl. Phys. 96, 1–9 (2008).

de Leeuw, D. M., Simenon, M. M. J., Brown, A. R. & Einerhand, R. E. F. Stability of n-type doped conducting polymers and consequences for polymeric microelectronic devices. Synth. Met 87, 53–59 (1997).

Zhan, X. et al. Rylene and related diimides for organic electronics. Adv. Mater. 23, 268–284 (2011).

Nikolka, M. et al. High operational and environmental stability of high-mobility conjugated polymer field-effect transistors achieved through the use of molecular additives. Nat. Mater. 16, 356–362 (2017).

Tada, H., Touda, H., Takada, M. & Matsushige, K. Quasi-intrinsic semiconducting state of titanyl-phthalocyanine films obtained under ultrahigh vacuum conditions. Appl. Phys. Lett. 76, 873 (2000).

Acknowledgements

This research was supported by the MSIP (Ministry of Science, ICT and Future Planning), Korea, under the “ICT Consilience Creative Program” (IITP-R0346-16-1007) supervised by the IITP(Institute for Information & communications Technology Promotion).

Author information

Authors and Affiliations

Contributions

H.Y. and J.K designed the study. H.Y. fabricated the transistor devices and circuits. H.Y. and D.L. collected data. F.T. and M.G. performed the 2D numerical simulations. H.L. performed UPS and XPS experiments. H.A. performed and analyzed GIWAXS experiment. H.Y., J.K., H.L., F.T., and M.G. analyzed data. G.G. and E.S. contributed to the performance analysis. All authors wrote the manuscript.

Corresponding authors

Ethics declarations

Competing Interests

The authors declare that they have no competing interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Yoo, H., Ghittorelli, M., Lee, DK. et al. Balancing Hole and Electron Conduction in Ambipolar Split-Gate Thin-Film Transistors. Sci Rep 7, 5015 (2017). https://doi.org/10.1038/s41598-017-04933-w

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-017-04933-w

This article is cited by

-

Polymer field-effect transistors with inkjet-printed silver electrodes: from device fabrication to circuit simulation

Journal of Materials Science: Materials in Electronics (2024)

-

Vertically Integrated Electronics: New Opportunities from Emerging Materials and Devices

Nano-Micro Letters (2022)

-

Highly stacked 3D organic integrated circuits with via-hole-less multilevel metal interconnects

Nature Communications (2019)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.