Abstract

Recently, liquid phase crystallization of thin silicon films has emerged as a candidate for thin-film photovoltaics. On 10 μm thin absorbers, wafer-equivalent morphologies and open-circuit voltages were reached, leading to 13.2% record efficiency. However, short-circuit current densities are still limited, mainly due to optical losses at the glass-silicon interface. While nano-structures at this interface have been shown to efficiently reduce reflection, up to now these textures caused a deterioration of electronic silicon material quality. Therefore, optical gains were mitigated due to recombination losses. Here, the SMooth Anti-Reflective Three-dimensional (SMART) texture is introduced to overcome this trade-off. By smoothing nanoimprinted SiO x nano-pillar arrays with spin-coated TiO x layers, light in-coupling into laser-crystallized silicon solar cells is significantly improved as successfully demonstrated in three-dimensional simulations and in experiment. At the same time, electronic silicon material quality is equivalent to that of planar references, allowing to reach V oc values above 630 mV. Furthermore, the short-circuit current density could be increased from 21.0 mA cm−2 for planar reference cells to 24.5 mA cm−2 on SMART textures, a relative increase of 18%. External quantum efficiency measurements yield an increase for wavelengths up to 700 nm compared to a state-of-the-art solar cell with 11.9% efficiency, corresponding to a j sc, EQE gain of 2.8 mA cm−2.

Similar content being viewed by others

Introduction

Liquid phase crystallization (LPC) of 5–40 μm thin silicon (Si) films directly on a glass substrate is a promising technology endorsing the general trend towards reduced absorber thicknesses in silicon photovoltaics. This technique allows avoiding current challenges of silicon wafers, namely high material losses and handling issues particularly arising at very low wafer thicknesses. By scanning a line-shaped energy source, e.g. a laser beam, across silicon films on glass large-grained polycrystalline material is formed1,2,3,4. It has been shown that an excellent material quality equivalent to that of multi-crystalline silicon wafers can be obtained using this technology, leading to record open-circuit voltages (V oc ) of 656 mV5 and 13.2% solar cell efficiency6. However, the short-circuit current density (j sc ) of state-of-the-art LPC solar cells is limited by reflection losses, mainly at the planar glass-silicon interface7. One possibility to reduce these losses is nano- or micro-structuring of the glass-silicon interface, either by directly texturing the glass8, 9, or by nanoimprint lithography using high-temperature stable sol-gel films10, 11. While these measures efficiently enhance light in-coupling into the silicon absorber in superstrate devices, the textured interfaces cause lower material quality and higher surface recombination velocities12.

Similar challenges are known for other silicon thin-film technologies, e.g. nano-crystalline silicon (nc-Si) thin-film solar cells13,14,15,16. One successful approach for nc-Si solar cells in substrate configuration is the implementation of flat light scattering substrates (FLiSS) as light-trapping structures17,18,19,20. In the FLiSS approach, a periodically patterned17 or randomly textured18, 19, ZnO layer is covered by an amorphous silicon layer and subsequently polished until the tips of the ZnO pattern are bared. Using the FLiSS substrate in nc-Si solar cells lead to an equivalent material quality of the absorber compared to planar devices, and a relative increase in efficiency of 10% was observed19. Another technique, which was developed for amorphous silicon thin-film solar cells in superstrate configuration, uses imprinting of random nano- and micro-pyramids in a hydrogen silsesquioxane layer21. These pyramids are planarized by spin-coating a ZnO nanoparticle solution, thereby enabling a silicon material quality equivalent to that of planar devices while increasing the short-circuit current density, leading to an 18% relative efficiency increase.

In this contribution, we present a method for producing high-quality LPC silicon solar cells on nanostructured substrates, the SMooth Anti-Reflective Three-dimensional (SMART) texture. The SMART texture is produced by combining nanoimprint lithography of hexagonal nano-pillar arrays with spin-coating of titanium oxide layers. The spin-coating leads to a preferential filling of the voids between the hexagonal nano-pillars, resulting in a smooth surface morphology without edges and steep flanks. The refractive index contrast in the two used materials leads to an optically rough, morphologically flat texture. We present the compatibility of the SMART texture with the silicon laser crystallization and solar cell preparation process. Optical, electronic material quality and optoelectronic characterization of silicon thin-film solar cell devices on SMART textures reveal that these solar cells outperform reference cells on optimized planar interlayer systems and demonstrate how the SMART texture may improve state-of-the-art LPC silicon thin-film solar cells in combination with additional light management measures.

Results

Fabrication of SMART textures

As superstrates 1.1 mm thick Corning Eagle XG glasses with a size of 5 × 5 cm2 are used. 250 nm thick silicon oxide (SiO x ) is sputtered onto these superstrates, serving as a diffusion barrier to glass impurities during liquid phase crystallization. Figure 1 illustrates the production process for SMART textures: Hexagonal pillar arrays with a period p of 750 nm and pillar heights h of 50 nm are replicated in a high-temperature stable, UV curable sol-gel resist based on silicon alcoxides22 (step 1) using nanoimprint lithography23. Further details about the used nanoimprint process can be found in ref. 24.

In order to smooth the surface of these superstrates, a titanium oxide precursor solution consisting of a mildly acidic solution of titanium isopropoxide in anhydrous ethanol is cast on the superstrate and spun with 2000 rpm for 30 s25. The spin-coating results in a preferential filling of the voids between the silicon oxide pillars, thus reducing the surface roughness significantly (step 2). By thermal curing for 30 minutes at 150 °C and 30 minutes at 500 °C, the solvents evaporate and a compact titanium oxide layer is formed25. Finally, a 10 nm thin silicon oxide layer is sputtered onto the stack, serving as a passivation layer at the interface with the silicon absorber (step 3).

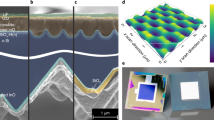

Figure 2(a) shows atomic force microscope images of the hexagonal nano-pillar array (step 1) and the SMART texture after spin-coating (step 3). For comparison, the height scaling was set constant in the AFM measurements. It is clearly seen that the height of the surface protrusions from the nano-pillars is greatly reduced by spin-coating the titanium oxide. This is also observed in the scanning electron microscope image of a SMART texture cross section in Fig. 2(b). The titanium oxide (TiO x ) layer (colored in green) preferably fills the voids between the SiO x nano-pillars (colored in blue). Specifically, edges and steep flanks of the texture – which are detrimental to silicon material quality after liquid phase crystallization11, 12, – are flattened out to a very smooth surface morphology at the interface to the crystalline silicon (c-Si, grey).

(a) Exemplary atomic force microscope images showing the hexagonal SiO x nano-pillar array (cf. step 1 in Fig. 1) and the surface of the SMART texture (cf. step 3 in Fig. 1) with the same height scaling. The characteristic texture parameters are outlined. (b) Exemplary scanning electron microscope image of a SMART texture with a silicon absorber on top. For clarification, the SiO x (blue) and TiO x (green) layers have been colored. The thin SiO x passivation layer is not visible.

Simulation results

In order to identify a suitable experimental structure for the SMART texture, optical simulations of hexagonal nano-pillar arrays, as sketched in Fig. 3(a), were performed with varying periods (p), heights (h) and filling fractions (ff). The period p was varied between 350 nm and 750 nm and the pillar height h between 20 nm and 150 nm. The filling fraction ff was set to 0.25, 0.5 and 0.75 by choosing the appropriate diameter d of the pillar following Eq. (2) (see methods section). Figure 3(b) shows the fraction of light coupled into the silicon absorber (1−R) in the wavelength range 400 nm–600 nm for three different filling fractions ff as a function of nanostructure height h, for a fixed period p of 750 nm. Smaller SiO x nano-pillars diameters, i.e. a lower filling fraction ff, lead to decreased reflectance. This can be explained by interpreting the SMART texture as a single mixed medium consisting of SiO x (n = 1.5) and TiO x (n = 2.1). Within this representation, a smaller filling fraction of SiO x nano-pillars corresponds to a higher effective refractive index. As the optimal refractive index between glass and silicon, given by the geometrical mean value, is around 2.4, higher effective refractive indices improve the anti-reflective properties at the interface. Filling fractions lower than 0.25 were not considered in simulations due to difficulties in the experimental production of very narrow pillars.

(a) Unit cell of the SMART texture used for 3-dimensional optical simulations, consisting of a hexagonal array of SiO x nano-pillars and the smoothing TiO x layer. The parameters varied in the simulations are denoted, namely the period (p), the height (h) and the diameter (d). On bottom and top, infinite halfspaces of glass and silicon layers are assumed, which is realized with perfectly matched layers (PML). Mean 1−R (reflectance) between 400 nm and 600 nm, calculated with 3-dimensional FEM simulations for (b) different filling fractions ff with a fixed period of 750 nm, and (c) various periods p of the nanostructure with a fixed filling fraction of 0.25.

Therefore, ff was set to 0.25 during simulations of various periods (Fig. 3(c)). The simulations predict an optimal height of the SMART texture between 40 and 60 nm, which is nearly independent of the period. Comparing different periods of the nanostructure, it is seen that mean reflectance generally decreases with the period of the SMART texture. However, the reflectance difference in the optimal thickness range between the smallest (blue) and largest (gold) period is only 3%. As it has been shown that the LPC process yields better material quality for larger nanostructure periods11, the structure used in experiment was chosen to have a period of 750 nm, height of 45 nm and a ff of 0.3.

Optoelectronic properties

Optical characteristics of the prepared solar cells were measured in order to confirm their anti-reflective behavior at the glass-silicon interface. The anti-reflective properties of the SMART texture are compared to a nano-pillar array (data from ref. 11) with the same period as the SMART texture, but a higher height-to-period ratio of 0.2. The higher height-to-period ratio of the nano-pillar array is required to enable optical properties that are comparable to the SMART texture. Figure 4 shows the reflectance spectra, which are plotted as 1−R (dashed curves in Fig. 4). 1−R represents the fraction of light coupled into the absorber, where it is either absorbed or transmitted. It can be seen that both the SMART texture (green) and nano-pillar array (red) significantly reduce reflection at the glass-silicon interface in comparison to the optimized planar reference (black). These optimized planar devices exhibit an interlayer stack of 250 nm SiO x , 70 nm silicon nitride (SiN x ) and 10 nm SiO x , which was previously found to have optimal broadband anti-reflective properties2, 4, and were processed in parallel to the SMART superstrates. Particularly, the minimum reflectance for the SMART texture is only about 5% at a wavelength of 560 nm, of which 4% (absolute) are already reflected at the sun-facing planar air-glass interface. The mean reflectance in the wavelength regime 400 nm–600 nm, where the influence of the rear side of the 8 μm thick silicon absorber can be excluded, amounts to 16% (absolute) in the planar reference stack with optimized anti-reflective SiN x layer, and 9% (absolute) for both the nano-pillar array and the SMART texture. For longer wavelengths, the rear-side texture of the nano-pillar array leads to increased scattering at the silicon backside and higher light in-coupling.

Optoelectronic characterization of solar cells with a SMART texture (green), planar reference (black) and nano-pillar array from ref. 11 (red), as measured by external quantum efficiency (EQE, solid) and 1-reflectance (1−R, dashed). The dotted curve shows the parasitic absorption in the SMART texture (A, dotted).

Compared to the planar reference, light in-coupling in the long wavelength regime is enhanced for the SMART textured solar cell. As the roughness of the back silicon surface in both cases is similar as confirmed by atomic force microscope images (not shown), the increased light in-coupling is attributed to scattering of light at the SMART texture. The contrast between the refractive indices of the mixed SiO x /TiO x layer makes it optically rough, leading to diffraction and therefore a longer light path through the absorber. Because extraction of electron-hole pairs is critical for solar cell performance, a high current density can only be reached if absorption is enhanced and at the same time, recombination remains at a low level, both in the bulk and at interfaces. Measurements of the external quantum efficiency (solid lines in Fig. 4) provide insight into carrier extraction depending on the wavelength of the incident light. It is seen that the solar cell on the nano-pillar array has a low EQE, indicating texture-induced defects at the glass-silicon interface and the bulk. This is not the case for the SMART texture (green), as its EQE is even higher compared to the parallel processed planar reference (black) for the whole wavelength range from 400 nm to 1100 nm. We attribute this to the smooth surface of the SMART texture compared to the nano-pillar array. Thus, it is confirmed that the increased light absorption in the laser-crystallized silicon absorber is not mitigated by an increased number of bulk material or interface defects. The reduced EQE in the short wavelength regime can be explained by parasitic absorption in the TiO x layer, cf. the absorption curve (dotted) for the superstrate with a SMART texture in Fig. 4. However, solar radiation is not very strong in this wavelength regime and maximum current loss compared to a planar interlayer stack is only 0.04 mA cm−2. The difference between EQE and 1−R arises mainly due to parasitic absorption in the contact layers and recombination of carriers at interfaces and in the poly-crystalline silicon absorber. A detailed analysis of loss contributions in planar LPC silicon thin-film solar cells on glass can be found in ref. 7. In summary, the SMART texture not only enhances absorption in the 8 μm thin silicon absorber, but also preserves material quality which is vital to carrier extraction. Hence, short-circuit current density j sc, EQE (cf. Eq. (1) in the methods section) could be increased from 21.0 mA cm−2 for the planar reference cell to 24.5 mA cm−2 for the solar cell with a SMART texture.

Material quality

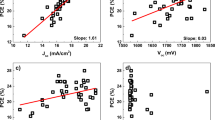

Electronic material quality of the bulk LPC silicon absorbers on SMART textures and planar reference samples was evaluated by means of Suns-V oc measurements. Figure 5 shows the open-circuit voltage of the four best cells (solid squares) of the planar reference, the SMART texture and the nano-pillar array from ref. 11. As for the external quantum efficiency, the bulk electronic material quality of the nano-pillar is greatly reduced. V oc values for both the planar reference stack and the SMART texture samples are very high, with mean V oc values of 629 mV and 636 mV for the planar reference sample and the SMART texture cells, respectively. Maximum V oc values of 636 mV and 649 mV were measured. Therefore, the material quality of the bulk silicon absorber crystallized on SMART textures is at least equivalent to the planar reference stack. The increase of V oc values on SMART textures cannot solely be explained by the increased current, which we estimate from a one-diode model to about ΔV oc,current ≈ 3 mV. Therefore, the increased V oc of silicon thin-film solar cells on SMART superstrates might be attributed to passivation properties of the TiO x layer, which are already known from literature26,27,28,29. However, further investigations are needed in order to elucidate this hypothesis, e.g. using current-voltage measurements30.

Open-circuit voltage V oc of liquid phase crystallized silicon thin-film solar cell devices (see inset) obtained from Suns-V oc measurements illuminated from the glass side for the planar reference sample, the SMART texture and the hexagonal nano-pillar array published in ref. 11. Open squares represent the mean value of the best four cells (solid squares), boxes the standard error, and whiskers the standard deviation. The highest measured value is indicated by a star.

Solar cell characteristics

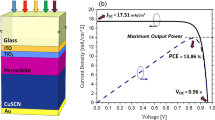

As discussed in previous sections, implementing the SMART texture at the glass-silicon interface leads to improved optical properties of the LPC silicon solar cells while preserving material quality. Figure 6 shows the current-voltage characteristics of the best measured solar cells with a nano-pillar array (red), SMART texture (green) and planar reference (black), as measured with a solar simulator (solid lines) and calculated using Suns-V oc data under the assumption of zero series resistance (dashed). While both j sc and V oc are strongly decreased for the nano-pillar array, the improved light in-coupling and preserved material quality of the solar cell with a SMART texture leads to a significant increase in short-circuit current density from 19.0 mA cm−2 in the planar reference cell to 23.2 mA cm−2 and equivalent open-circuit voltages of 627 mV and 633 mV, corresponding to solar cell efficiencies of 6.8% and 9.1% on the planar reference and SMART textured cells, respectively. Pronounced differences between the measured jV characteristics and the calculated jV curves from Suns-V oc measurements arise from the high series resistance of the utilized solar cell processing as discussed in the methods section. Assuming zero series resistance, a pseudo power conversion efficiency of 9.7% and 11.6% can be calculated for the planar reference and SMART textures devices, respectively. Please note that neither the planar nor the SMART textured devices shown here exhibit rear side textures which would further enhance light trapping for long-wavelength light. All solar cell parameters are summarized in Table 1.

Current-voltage curves of the nano-pillar array from ref. 11 (red), the SMART texture (green) and planar reference (black), as measured with a solar simulator (solid, jV) and by Suns-V oc (dashed).

Comparison to state-of-the-art solar cell device

For further analysis of the potential of the SMART texture in high-efficiency devices, the external quantum efficiency of the best solar cell exhibiting a SMART texture is compared to a state-of-the-art LPC-Si solar cell with an interdigitated back contact (IBC) system6. The state-of-the-art cell exhibits a 13 μm-thick silicon absorber with n-type dopant concentration of around 1 × 1017 cm−3 and random pyramid back texture, and provides a power conversion efficiency of 11.9%6. If additional light-management measures at the air-glass interface are employed, a record power conversion efficiency of 13.2% was reached with this cell. In order to investigate the anti-reflective properties at the glass-silicon interface independent of other light-management techniques, the SMART texture is compared to this record cell without anti-reflective texture at the air-glass interface. Figure 7 shows the external quantum efficiency in superstrate configuration (EQE, solid lines) and reflectance (1−R, dashed lines) of the solar cell with a SMART texture (green) and the back textured IBC cell (black). The solar cell with a SMART texture was measured with a white-paint back reflector, while back reflection in the IBC cell is provided by the ITO/Ag contact fingers. For the IBC cell, a correction for dead areas based on a laser-beam induced current measurement (cf. supplementary material) of 8% was accounted for in order to compare the IBC cell to the full emitter cell design described in the methods section.

Comparing the reflectance (measured as 1−R, dashed lines) of the SMART texture (green) to the back textured IBC (black), one sees that the SMART texture efficiently reduces the reflection at the glass-silicon interface leading to increased light in-coupling up to around 700 nm (shaded in grey). For longer wavelengths, absorption in silicon is low and the optical properties are dominated by scattering at the silicon back side. Therefore, the back textured IBC cell shows improved light absorption in this wavelength regime. Considering EQE (solid lines in Fig. 7), it is seen that the improved anti-reflective properties of the SMART texture (green) at the glass-silicon interface lead to an increase in EQE compared to the IBC back textured cell (black) in the wavelength regime up to about 700 nm, corresponding to the gain in 1−R (shaded in red). For longer wavelengths, the EQE of the back textured IBC cell is higher due to its light-trapping texture at the silicon rear-side. From the corresponding trends in EQE and 1−R, it can be concluded that the internal quantum efficiency (not shown) of both, the back textured IBC cell and the solar cell on SMART texture, are equivalent, indicating excellent electronic material quality and low defect densities at the glass-silicon interface in the device exhibiting the SMART texture. Overall, j sc,EQE amounts to 24.5 mA cm−2 and 26.0 mA cm−2 for the SMART texture and back textured IBC cell, respectively. If only contributions from the wavelength regime between 300 nm and 700 nm are considered, the current density amounts to 15.0 mA cm−2 and 12.2 mA cm−2, a 22% (relative) increase due to the SMART texture.

Solar cell parameters as obtained from current-voltage and Suns-V oc measurements are summarized in Table 1. Compared to the parallel processed planar reference cell, the short-circuit current density of the solar cell on the SMART texture was increased from 19.0 mA cm−2 to 23.2 mA cm−2, corresponding to a relative increase of 18%. The open-circuit voltage is slightly higher for solar cells on SMART superstrates, which might be explained by an improved interface passivation. Both the SMART textured and planar interlayer solar cells have a FF of around 60% owing to the high series resistance of the contacting scheme used. From Suns-V oc measurements, the pseudo–FF neglecting the influence of series resistance can be calculated, giving values close to 80%. The back textured IBC cell, in contrast, exhibits a FF of 74.7%. Due to its thicker absorber layer and pyramidal back texture, the short-circuit current density of the IBC cell is higher than that of the SMART textured cell (cf. Fig. 7). This leads to an overall efficiency of 11.9%.

In order to further increase the short-circuit current density and thus power conversion efficiency in liquid phase crystallized silicon thin-film solar cells, the SMART texture can be combined with additional light-management measures at the air-glass interface and silicon rear-side, as has been successfully demonstrated for planar devices6, 7.

For SMART textured LPC silicon absorber layers with a film thickness of 15 μm combined with a KOH random pyramid texture and a white paint back reflector at the silicon back side, analysis of the optical properties yield a maximum current density of 36.4 mA cm−2, indicating the potential to realize an increased short-circuit current density in LPC silicon thin-film solar cell devices31. Thus, an efficiency of 36.4 mA cm−2 × 650 mV × 0.75 = 18% could potentially be reached for liquid-phase crystallized thin-film silicon solar cells exhibiting a SMART texture and additional light-management techniques at other interface in the device.

Discussion and Conclusion

We presented a novel nanostructure for increased light in-coupling in liquid phase crystallized silicon thin-film solar cells: the SMooth Anti-Reflective Three-dimensional (SMART) texture. Nanoimprinted, high-temperature stable SiO x sol-gel nano-pillars were smoothed by spin-coating of TiO x . Thereby, an optically rough nanostructure with a smooth surface could successfully be prepared and integrated in the liquid phase crystallization solar cell preparation process. Three-dimensional optical simulations allowed to obtain suitable nanostructure parameters for experiment. Anti-reflective properties and process compatibility of the nanostructure was found to be optimal at a period p = 750 nm, a filling fraction ff = 0.25 and nanostructure height h = 40–50 nm. Solar cells with a SMART texture were prepared using the parameters obtained from simulations. Despite its much smoother surface morphology, anti-reflective properties of the SMART texture were found to be equivalent to the more pronounced hexagonal nano-pillar array. The pronounced texture of the nano-pillar array was previously found to cause poor material quality of LPC silicon solar cells, limiting the external quantum efficiency and the open-circuit voltage due to an increased number of interface defects and extended bulk defects. In contrast, implementing the SMART texture had no detrimental effects on material quality of the silicon absorber, leading to V oc values up to 649 mV and an increase in j sc,EQE from 21.0 mA cm−2 to 24.5 mA cm−2 compared to a planar reference cell. Furthermore, the SMART texture was compared to a state-of-the-art solar cell with an interdigitated back contact system exhibiting a textured back side. Measurements of optical properties and external quantum efficiency yielded that increased light in-coupling for wavelengths up to 700 nm in the solar cell with a SMART texture was not mitigated by an increased number of defects at the glass-silicon interface. Consequently, a higher EQE on the SMART textured cell than on the state-of-the-art device that provides a power conversion efficiency of 11.9% was measured up to 700 nm, corresponding to a current gain of 2.8 mA cm−2 in the wavelength regime between 300 nm and 700 nm. Hence, the SMART texture allows overcoming the trade-off between optical and electronic performance in nano-structured liquid phase crystallized silicon thin-film solar cells by decoupling the anti-reflective properties from absorber structuring, potentially leading to more efficient liquid phase crystallized silicon thin-film solar cells on glass in combination with anti-reflective measures at other interfaces in future devices.

Methods

Solar cell preparation

The silicon absorber is deposited onto the SMART superstrates and on planar reference superstrates. The reference sample has an interlayer stack of 250 nm SiO x , 70 nm silicon nitride (SiN x ) and 10 nm SiO x , which was previously found to have optimal broadband anti-reflective properties2, 4, and is processed in parallel to the SMART superstrates. The 8 μm thick silicon absorbers are deposited by electron beam evaporation at a heater temperature of T = 600 °C32. Liquid phase crystallization of the silicon is performed using a line-shaped laser with a 1/e 2 size of 30 × 0.3 mm2 and a wavelength of 808 nm. The laser beam is scanned across the samples with a scanning speed of 3 mm/s, and melts the nano-crystalline silicon layer. Upon solidifying, large grains of up to centimeters in length and millimeters in width are formed1, 5. Solar cells with n-type dopant concentration of about 1 × 1017 cm−3 are prepared on both substrate types as described in refs 4 and 5, therein denoted as test structure and test cells, respectively. In this solar cell design, the LPC silicon absorber surface is cleaned using a standard RCA cleaning. Subsequently, a heterojunction is formed by depositing 5 nm intrinsic and 10 nm p-type amorphous silicon on the n-type LPC silicon absorber using low-temperature PECVD, followed by a 80 nm thick ITO layer deposited by room-temperature sputtering. Polyimide tape circles with a diameter of 8 mm are attached to the ITO, serving as etching mask in the subsequent removal of ITO and a-Si:H by wet-chemical etching. After removing native SiO x in 1% HF solution for 30 s, 30 nm Ti and 1 μm Al is thermally evaporated on the samples. Underetching of the tape leads to separation of electron and hole contacts. Prior to measurements, the samples were annealed for 5 min at 200 °C in order to increase the mobility in the ITO layer.

Due to this quick and simple processing without lithographic techniques, these solar cell devices typically exhibit high series resistances and, consequently, have only low fill factors. Nevertheless, all vital solar cell parameters for the characterization of devices exhibiting a SMART texture at the glass-silicon interface can be measured with this contacting scheme5.

Characterization

Optical characterization is conducted with a Perkin Elmer Lambda 1050 spectrophotometer equipped with an integrating sphere.

External quantum efficiency (EQE) is measured on a custom-made setup featuring a probe beam of 3 × 2 mm2 using lock-in technique. While no bias voltage is applied during measurements, bias light from a halogen lamp is used, imitating the AM1.5 G spectrum. Short-circuit current densities are also calculated from the EQE according to

where e is the elementary charge and Φ(λ) the spectral photon flux corresponding to the AM1.5 G solar radiation spectrum.

Atomic force microscope (AFM) images were measured using a Park Systems XE-70.

Electron microscopy was performed with a Hitachi cold field emitter scanning electron microscope.

Current-Voltage characteristics are measured using a dual-source solar simulator with xenon and tungsten lamp with class AAA characteristics (WXS-155 S-L2 by Wacom Electric Co, Japan), from which open-circuit voltage and short-circuit current density can be extracted.

Alternatively, open-circuit voltages (V oc ) are also determined using a Suns-V oc unit of a WCT-100 photo conductance lifetime tool by Sinton Instruments. The setup additionally allows to calculate the so-called pseudo fill factor pseudo–FF, assuming no series resistance in the device.

Three-dimensional optical simulations

Optical simulations are performed with the 3-dimensional finite-element method (FEM) solver JCMsuite33, which provides rigorous solutions to Maxwell’s equations. Sufficient numerical accuracy is achieved by constraining the side lengths of the elements to the light wavelength in the corresponding material and adapting the polynomial degree during simulations. Top and bottom of the computational domain are considered as infinite halfspaces, which is realized by using so-called perfectly matched layers (PML). By doing this, the computational cost of the simulations can be kept low34. On the boundaries of the computational domain periodic boundary conditions are applied. Due to the periodic structure of the SMART texture, light reflected at the glass-silicon interface can be refracted into higher orders. In order to take into account light that reaches the silicon absorber after a second light path through the glass, an a posteriori first order correction is applied to the reflected light as described in ref. 35. The simulated structures consist of hexagonal nano-pillar arrays, as illustrated in the meshed unit cell in Fig. 3(a). The parameters characterizing the nanostructure are the period p, the height h and the diameter d of the nano-pillar, as indicated in Fig. 3(a). The area filling fraction ff of SiO x nano-pillars in the SMART texture is connected to p and d via

Light absorbed in the silicon layer or reaching the perfectly matched layer is interpreted as 1−R (reflectance), because the (parasitic) absorption in the interlayers can be neglected. For light that does not reach the back-side of the absorber layer due to a sufficiently short penetration depth in silicon, 1−R represents a measurable parameter for the characterization of the anti-reflective properties of the front interface of the device. For our devices this holds for wavelengths shorter than about 600 nm.

References

Dore, J. et al. Thin-film polycrystalline silicon solar cells formed by diode laser crystallisation. Prog. Photovoltaics 21, 1377–1383 (2013).

Dore, J., Ong, D., Varlamov, S., Egan, R. & Green, M. A. Progress in Laser-Crystallized Thin-Film Polycrystalline Silicon Solar Cells: Intermediate Layers, Light Trapping, and Metallization. IEEE J. Photovolt. 4, 33–39 (2014).

Gabriel, O. et al. Crystalline silicon on glass - interface passivation and absorber material quality. Prog. Photovoltaics 15, 659–676 (2015).

Amkreutz, D. et al. Liquid-Phase Crystallized Silicon Solar Cells on Glass: Increasing the Open-Circuit Voltage by Optimized Interlayers for n- and p-Type Absorbers. IEEE J. Photovolt. 5, 1757–1761 (2015).

Haschke, J., Amkreutz, D., Korte, L., Ruske, F. & Rech, B. Towards wafer quality crystalline silicon thin-film solar cells on glass. Sol. Energ. Mat. Sol. C. 128, 190–197 (2014).

Sonntag, P. et al. Silicon Solar Cells on Glass with Power Conversion Efficiency above 13% and thickness below 15 μm. Sci. Rep. 7, 873 (2017).

Frijnts, T. et al. Analysis of photo-current potentials and losses in thin film crystalline silicon solar cells. Sol. Energ. Mat. Sol. C. 143, 457–466 (2015).

Pakhuruddin, M. Z., Dore, J., Huang, J. & Varlamov, S. Effects of front and rear texturing on absorption enhancement in laser-crystallized silicon thin-films on glass. Jpn. J. Appl. Phys. 54, 08KB04 (2015).

Pakhuruddin, M. Z., Huang, J., Dore, J. & Varlamov, S. Light Absorption Enhancement in Laser-Crystallized Silicon Thin Films on Textured Glass. IEEE J. Photovolt 60, 159–165 (2016).

Becker, C., Preidel, V., Amkreutz, D., Haschke, J. & Rech, B. Double-side textured liquid phase crystallized silicon thin-film solar cells on imprinted glass. Sol. Energ. Mat. Sol. C. 135, 2–7 (2015).

Köppel, G., Rech, B. & Becker, C. Sinusoidal nanotextures for light management in silicon thin-film solar cells. Nanoscale 8, 8722–8728 (2016).

Preidel, V. et al. Balance of optical, structural, and electrical properties of textured liquid phase crystallized Si solar cells. J. Appl. Phys. 117, 225306 (2015).

Python, M. et al. Influence of the substrate geometrical parameters on microcrystalline silicon growth for thin-film solar cells. Sol. Energ. Mat. Sol. C. 93, 1714–1720 (2009).

Kim, D. et al. Effect of substrate morphology slope distributions on light scattering, nc-Si:H film growth, and solar cell performance. ACS Appl. Mater. Inter. 6, 22061–22068 (2014).

Sever, M., Krč, J. & Topič, M. Prediction of defective regions in optimisation of surface textures in thin-film silicon solar cells using combined model of layer growth. Thin Solid Films 573, 176–184 (2014).

Tamang, A. et al. On the interplay of interface morphology and microstructure of high-efficiency microcrystalline silicon solar cells. Sol. Energ. Mat. Sol. C. 151, 81–88 (2016).

Sai, H., Kanamori, Y. & Kondo, M. Flattened light-scattering substrate in thin film silicon solar cells for improved infrared response. Appl. Phys. Lett. 98, 113502 (2011).

Söderström, K. et al. Thin-film silicon triple-junction solar cell with 12.5% stable efficiency on innovative flat light-scattering substrate. J. Appl. Phys. 112, 114503 (2012).

Söderström, K., Bugnon, G., Haug, F.-J., Nicolay, S. & Ballif, C. Experimental study of flat light-scattering substrates in thin-film silicon solar cells. Sol. Energ. Mat. Sol. C. 101, 193–199 (2012).

Isabella, O., Sai, H., Kondo, M. & Zeman, M. Full-wave optoelectrical modeling of optimized flattened light-scattering substrate for high efficiency thin-film silicon solar cells. Prog. Photovoltaics 22, 671–689 (2014).

Kim, Y. D. et al. Novel patterned layer to enhance conversion efficiency of amorphous silicon thin-film solar cells. Phys. Status Solidi A 211, 1493–1498 (2014).

Verschuuren, M. & Van Sprang, H. 3D Photonic Structures by Sol-Gel Imprint Lithography. In MRS Spring Meet. 1002 (2007).

Guo, L. J. Nanoimprint lithography: Methods and material requirements. Adv. Mat 19, 495–513 (2007).

Becker, C. et al. 5 × 5 cm2 Silicon Photonic Crystal Slabs on Glass and Plastic Foil Exhibiting Broadband Absorption and High-Intensity Near-Fields. Sci. Rep 4, 5886 (2014).

Eperon, G. E., Burlakov, V. M., Goriely, A. & Snaith, H. J. Neutral Color Semitransparent Microstructured Perovskite Solar Cells. ACS Nano 8, 591–598 (2014).

Thomson, A. F. & McIntosh, K. R. Light-enhanced surface passivation of TiO2-coated silicon. Prog. Photovoltaics 20, 343–349 (2012).

Barbé, J., Thomson, A. F., Wang, E.-C., McIntosh, K. & Catchpole, K. Nanoimprinted TiO2 sol-gel passivating diffraction gratings for solar cell applications. Prog. Photovoltaics 20, 143–148 (2012).

Liao, B., Hoex, B., Aberle, A. G., Chi, D. & Bhatia, C. S. Excellent c-Si surface passivation by low-temperature atomic layer deposited titanium oxide. Appl. Phys. Lett. 104, 253903 (2014).

Liao, B., Hoex, B., Shetty, K. D., Basu, P. K. & Bhatia, C. S. Passivation of Boron-Doped Industrial Silicon Emitters by Thermal Atomic Layer Deposited Titanium Oxide. IEEE J. Photovolt. 5, 1062–1066 (2015).

Preissler, N. et al. Interface passivation of liquid-phase crystallized silicon on glass studied with high-frequency capacitance-voltage measurements. Phys. Status Solidi A 213, 1697–1704 (2016).

Köppel, G., Eisenhauer, D., Rech, B. & Becker, C. Combining tailor-made textures for light in-coupling and light trapping in liquid phase crystallized silicon thin-film solar cells. Opt. Exp. 25, A467–A472 (2017).

Becker, C. et al. Polycrystalline silicon thin-film solar cells: Status and perspectives. Sol. Energ. Mat. Sol. C. 119, 112–123 (2013).

Pomplun, J., Burger, S., Zschiedrich, L. & Schmidt, F. Adaptive finite element method for simulation of optical nano structures. Phys. Status Solidi B 244, 3419–3434 (2007).

Lavrinenko, A. V., Laegsgaard, J., Gregersen, N., Schmidt, F. & Sondergaard, T. Numerical Methods in Photonics (CRC Press, 2014).

Jäger, K., Hammerschmidt, M., Köppel, G., Burger, S. & Becker, C. On Accurate Simulations of Thin-Film Solar Cells With a Thick Glass Superstrate. Light, Energy and the Environment Congress paper PM3B. 5 (2016).

Acknowledgements

The authors gratefully acknowledge the support of M. Krüger, H. Rhein, E. Conrad, and C. Klimm, Helmholtz-Zentrum Berlin für Materialien und Energie GmbH (HZB), for their help with solar cell preparation and SEM imaging. Simulation results were obtained at the Berlin Joint Lab for Optical Simulations for Energy Research (BerOSE) of HZB, Zuse Institute Berlin and Freie Universität Berlin. The German Ministry of Education and Research (BMBF) is acknowledged for funding the research activities of the Young Investigator Group Nano-SIPPE at HZB in the program NanoMatFutur (no. 03X5520). This project has received funding from the European Union’s Seventh Programme for research, technological development and demonstration under grant agreement no. 609788.

Author information

Authors and Affiliations

Contributions

D.E. conceived the experiments for the SMART texture, D.E. and G.K. conducted these experiments. P.S. and D.A. produced and measured the back-textured IBC cell. K.J. and D.C. designed and conducted the three-dimensional simulations. O.S. synthesized the TiO x sol-gel. D.E. wrote the manuscript text. C.B. and B.R. managed the project and edited the manuscript. All authors reviewed the manuscript.

Corresponding author

Ethics declarations

Competing Interests

The authors declare that they have no competing interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Eisenhauer, D., Köppel, G., Jäger, K. et al. Smooth anti-reflective three-dimensional textures for liquid phase crystallized silicon thin-film solar cells on glass. Sci Rep 7, 2658 (2017). https://doi.org/10.1038/s41598-017-02874-y

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41598-017-02874-y

This article is cited by

-

A template-free, more environmentally friendly approach for glass micro-texturing

Scientific Reports (2022)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.