Abstract

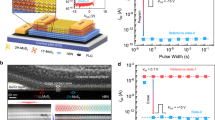

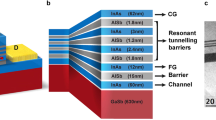

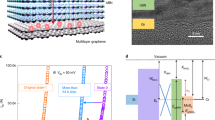

The development of high-performance memory devices has played a key role in the innovation of modern electronics. Non-volatile memory devices have manifested high capacity and mechanical reliability as a mainstream technology; however, their performance has been hampered by low extinction ratio and slow operational speed. Despite substantial efforts to improve these characteristics, typical write times of hundreds of micro- or milliseconds remain a few orders of magnitude longer than that of their volatile counterparts. Here we demonstrate non-volatile, floating-gate memory devices based on van der Waals heterostructures with atomically sharp interfaces between different functional elements, achieving ultrahigh-speed programming/erasing operations in the range of nanoseconds with extinction ratio up to 1010. This enhanced performance enables new device capabilities such as multi-bit storage, thus opening up applications in the realm of modern nanoelectronics and offering future fabrication guidelines for device scale up.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 print issues and online access

$259.00 per year

only $21.58 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

Source data are provided with this paper. All relevant data are available from the corresponding authors upon reasonable request.

References

International Roadmap for Devices and Systems (IRDS) https://irds.ieee.org/ (2017).

Hwang, C. S. Prospective of semiconductor memory devices: from memory system to materials. Adv. Electron. Mater. 1, 1400056 (2015).

Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors. Nat. Rev. Mater. 1, 16052 (2016).

Novoselov, K. S. et al. Electric field effect in atomically thin carbon films. Science 306, 666–669 (2004).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Li, L. et al. Black phosphorus field-effect transistors. Nat. Nanotechnol. 9, 372–377 (2014).

Feng, W., Zheng, W., Cao, W. & Hu, P. Back gated multilayer InSe transistors with enhanced carrier mobilities via the suppression of carrier scattering from a dielectric interface. Adv. Mater. 26, 6587–6593 (2014).

Wu, L. et al. InSe/hBN/graphite heterostructure for high-performance 2D electronics and flexible electronics. Nano Res. 13, 1127–1132 (2020).

Geim, A. K. & Grigorieva, I. V. Van der Waals heterostructures. Nature 499, 419–425 (2013).

Liu, Y. et al. Van der Waals heterostructures and devices. Nat. Rev. Mater. 1, 16042 (2016).

Novoselov, K. S., Mishchenko, A., Carvalho, A. & Castro Neto, A. H. 2D materials and van der Waals heterostructures. Science 353, aac9439 (2016).

Haigh, S. J. et al. Cross-sectional imaging of individual layers and buried interfaces of graphene-based heterostructures and superlattices. Nat. Mater. 11, 764–767 (2012).

Kretinin, A. V. et al. Electronic properties of graphene encapsulated with different two-dimensional atomic crystals. Nano Lett. 14, 3270–3276 (2014).

Fiori, G. et al. Electronics based on two-dimensional materials. Nat. Nanotechnol. 9, 768–779 (2014).

Bertolazzi, S., Krasnozhon, D. & Kis, A. Nonvolatile memory cells based on MoS2/graphene heterostructures. ACS Nano 7, 3246–3252 (2013).

Choi, M. S. et al. Controlled charge trapping by molybdenum disulphide and graphene in ultrathin heterostructured memory devices. Nat. Commun. 4, 1624 (2013).

Li, D. et al. Nonvolatile floating-gate memories based on stacked black phosphorus–boron nitride–MoS2 heterostructures. Adv. Funct. Mater. 25, 7360–7365 (2015).

Wang, S. et al. New floating gate memory with excellent retention characteristics. Adv. Electron. Mater. 5, 1800726 (2019).

Hong, A. J. et al. Graphene flash memory. ACS Nano 5, 7812–7817 (2011).

Lee, S. et al. Impact of gate work-function on memory characteristics in Al2O3/HfOx/Al2O3/graphene charge-trap memory devices. Appl. Phys. Lett. 100, 023109 (2012).

Chen, M. et al. Multibit data storage states formed in plasma-treated MoS2 transistors. ACS Nano 8, 4023–4032 (2014).

Wang, J. et al. Floating gate memory‐based monolayer MoS2 transistor with metal nanocrystals embedded in the gate dielectrics. Small 11, 208–213 (2015).

Zhang, E. et al. Tunable charge-trap memory based on few-layer MoS2. ACS Nano 9, 612–619 (2015).

Feng, Q., Yan, F., Luo, W. & Wang, K. Charge trap memory based on few-layer black phosphorus. Nanoscale 8, 2686–2692 (2016).

Lee, D. et al. Black phosphorus nonvolatile transistor memory. Nanoscale 8, 9107–9112 (2016).

Liu, C. et al. Eliminating overerase behavior by designing energy band in high‐speed charge‐trap memory based on WSe2. Small 13, 1604128 (2017).

Wang, P. F. et al. A semi-floating gate transistor for low-voltage ultrafast memory and sensing operation. Science 341, 640–643 (2013).

Liu, C. et al. A semi-floating gate memory based on van der Waals heterostructures for quasi-non-volatile applications. Nat. Nanotechnol. 13, 404–410 (2018).

Kahng, D. & Sze, S. M. A floating gate and its application to memory devices. Bell Syst. Tech. J. 46, 1288–1295 (1967).

Lee, J.-D., Hur, S.-H. & Choi, J.-D. Effects of floating-gate interference on NAND flash memory cell operation. IEEE Electron Device Lett. 23, 264–266 (2002).

Misra, A. et al. Multilayer graphene as charge storage layer in floating gate flash memory. In 2012 4th IEEE International Memory Workshop 1–4 (2012).

Vu, Q. A. et al. Two-terminal floating-gate memory with van der Waals heterostructures for ultrahigh on/off ratio. Nat. Commun. 7, 12725 (2016).

Yang, J. J., Strukov, D. B. & Stewart, D. R. Memristive devices for computing. Nat. Nanotechnol. 8, 13–24 (2013).

Cho, T. et al. A dual-mode NAND flash memory: 1-Gb multilevel and high-performance 512-Mb single-level modes. IEEE J. Solid-State Circuits 36, 1700–1706 (2001).

Xiang, D. et al. Two-dimensional multibit optoelectronic memory with broadband spectrum distinction. Nat. Commun. 9, 2966 (2018).

Tran, M. D. et al. Two-terminal multibit optical memory via van der Waals heterostructure. Adv. Mater. 31, 1807075 (2019).

Kang, K. et al. Layer-by-layer assembly of two-dimensional materials into wafer-scale heterostructures. Nature 550, 229–233 (2017).

Li, X. et al. Large-area synthesis of high-quality and uniform graphene films on copper foils. Science 324, 1312–1314 (2009).

Pan, Y. et al. Highly ordered, millimeter-scale, continuous, single-crystalline graphene monolayer formed on Ru (0001). Adv. Mater. 21, 2777–2780 (2009).

Shi, Z. et al. Vapor–liquid–solid growth of large-area multilayer hexagonal boron nitride on dielectric substrates. Nat. Commun. 11, 849 (2020).

Kang, K. et al. High-mobility three-atom-thick semiconducting films with wafer-scale homogeneity. Nature 520, 656–660 (2015).

Liu, L., Ding, Y., Li, J., Liu, C. & Zhou, P. Ultrafast non-volatile flash memory based on van der Waals heterostructures. Preprint at https://arxiv.org/abs/2009.01581 (2020).

Lee, G.-H. et al. Flexible and transparent MoS2 field-effect transistors on hexagonal boron nitride-graphene heterostructures. ACS Nano 7, 7931–7936 (2013).

Castellanos-Gomez, A. et al. Deterministic transfer of two-dimensional materials by all-dry viscoelastic stamping. 2D Mater. 1, 011002 (2014).

Wang, G. et al. Introduction of interfacial charges to black phosphorus for a family of planar devices. Nano Lett. 16, 6870–6878 (2016).

Acknowledgements

We thank Y.-Y. Zhang, S. Du, G. Qian and Z. Zhu for helpful discussions, and H. Yang, J. Li, C. Gu and Q. Huan for assistance in device fabrication and measurement. This work was supported by the National Key Research & Development Projects of China (grant nos. 2016YFA0202300 and 2018FYA0305800), National Natural Science Foundation of China (grant no. 61888102), Strategic Priority Research Program of Chinese Academy of Sciences (CAS; grant nos. XDB30000000 and XDB28000000), Youth Innovation Promotion Association of CAS (Y201902) and Beijing Outstanding Young Scientist Program (BJJWZYJH01201914430039). M.O. acknowledges support from ONR (N000141712885) and NSF (DMR1608720). S.J.P. acknowledges support from the Ministry of Education, Singapore, under a Tier 2 grant (no. MOE2017-T2-2-139). A portion of the research was performed in the CAS Key Laboratory of Vacuum Physics.

Author information

Authors and Affiliations

Contributions

H.-J.G. supervised the overall research. L.B., M.O. and H.-J.G. designed the experiments. L.W., A.W., J.Y. and L.B. fabricated the devices and carried out the electrical measurements. J.S., S.J.P. and W.Z. performed the STEM measurements. A.W. constructed the home-made electric circuit with ultrashort voltage pulse signals with FWHM of 21 ns. L.W., L.B., A.W., J.S., J.Y., W.Z., M.O., S.T.P. and H.-J.G. analysed the data. L.W., L.B., J.S., W.Z., S.J.P., S.T.P., M.O. and H.-J.G. wrote the paper. All the authors contributed to the preparation of the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Peer review information Nature Nanotechnology thanks the anonymous reviewers for their contribution to the peer review of this work.

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Extended data

Extended Data Fig. 1

Floating-gate memory devices based on 2D materials.

Supplementary information

Supplementary Information

Supplementary Figs. 1–15, Notes 1–5 and refs. 1–7.

Source data

Source Data Fig. 2

Contains bare data for images.

Source Data Fig. 3

Contains bare data for images.

Source Data Fig. 4

Contains bare data for images.

Rights and permissions

About this article

Cite this article

Wu, L., Wang, A., Shi, J. et al. Atomically sharp interface enabled ultrahigh-speed non-volatile memory devices. Nat. Nanotechnol. 16, 882–887 (2021). https://doi.org/10.1038/s41565-021-00904-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41565-021-00904-5

This article is cited by

-

Steep-slope vertical-transport transistors built from sub-5 nm Thin van der Waals heterostructures

Nature Communications (2024)

-

An ultrafast bipolar flash memory for self-activated in-memory computing

Nature Nanotechnology (2023)

-

Simultaneously ultrafast and robust two-dimensional flash memory devices based on phase-engineered edge contacts

Nature Communications (2023)

-

Retina-inspired organic neuromorphic vision sensor with polarity modulation for decoding light information

Light: Science & Applications (2023)

-

Extending in-sensor computing from static images to dynamic motions

Nature Electronics (2023)