Abstract

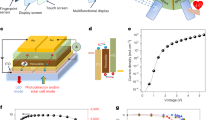

The need for continuous size downscaling of silicon transistors is driving the industrial development of strategies to enable further footprint reduction1,2. The atomic thickness of two-dimensional materials allows the potential realization of high-area-efficiency transistor architectures. However, until now, the design of devices composed of two-dimensional materials has mimicked the basic architecture of silicon circuits3,4,5,6. Here, we report a transistor based on a two-dimensional material that can realize photoswitching logic (OR, AND) computing in a single cell. Unlike the conventional transistor working mechanism, the two-dimensional material logic transistor has two surface channels. Furthermore, the material thickness can change the logic behaviour—the architecture can be flexibly expanded to achieve in situ memory such as logic computing and data storage convergence in the same device. These devices are potentially promising candidates for the construction of new chips that can perform computing and storage with high area-efficiency and unique functions.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 print issues and online access

$259.00 per year

only $21.58 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the plots in this paper and other findings of this study are available from the corresponding authors on reasonable request.

References

Seabaugh, A. C. & Zhang, Q. Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 98, 2095–2110 (2010).

Ionescu, A. M. & Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479, 329–337 (2011).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Fang, H. et al. High-performance single layered WSe2 p-FETs with chemically doped contacts. Nano Lett. 12, 3788–3792 (2012).

Desai, S. B. et al. MoS2 transistors with 1-nanometer gate lengths. Science 354, 99–102 (2016).

Si, M. et al. Steep-slope hysteresis-free negative capacitance MoS2 transistors. Nat. Nanotechnol. 13, 24–28 (2018).

Li, L. et al. Black phosphorus field-effect transistors. Nat. Nanotechnol. 9, 372–377 (2014).

Liu, C. et al. A semi-floating gate memory based on van der Waals heterostructures for quasi-non-volatile applications. Nat. Nanotechnol. 13, 404–410 (2018).

Liu, C. et al. Eliminating overerase behavior by designing energy band in high-speed charge-trap memory based on WSe2. Small 13, 1604128 (2017).

Vu, Q. A. et al. Two-terminal floating-gate memory with van der Waals heterostructures for ultrahigh on/off ratio. Nat. Commun. 7, 12725 (2016).

Huang, M. et al. Multifunctional high-performance van der Waals heterostructures. Nat. Nanotechnol. 12, 1148–1154 (2017).

Shim, J. et al. Phosphorene/rhenium disulfide heterojunction-based negative differential resistance device for multi-valued logic. Nat. Commun. 7, 13413 (2016).

Wachter, S., Polyushkin, D. K., Bethge, O. & Mueller, T. A microprocessor based on a two-dimensional semiconductor. Nat. Commun. 8, 14948 (2017).

Britnell, L. et al. Electron tunneling through ultrathin boron nitride crystalline barriers. Nano Lett. 12, 1707–1710 (2012).

Mak, K. F., Lee, C., Hone, J., Shan, J. & Heinz, T. F. Atomically thin MoS2: a new direct-gap semiconductor. Phys. Rev. Lett. 105, 474–479 (2010).

Zhao, W. et al. Evolution of electronic structure in atomically thin sheets of WS2 and WSe2. ACS Nano 7, 791–797 (2012).

Yu, L. et al. Design, modeling and fabrication of CVD grown MoS2 circuits with E-Mode FETs for large-area electronics. Nano Lett. 16, 6349–6356 (2016).

Lopezsanchez, O., Lembke, D., Kayci, M., Radenovic, A. & Kis, A. Ultrasensitive photodetectors based on monolayer MoS2. Nat. Nanotechnol. 8, 497–501 (2013).

Ohta, T. et al. Interlayer interaction and electronic screening in multilayer graphene investigated with angle-resolved photoemission spectroscopy. Phys. Rev. Lett. 98, 206802 (2007).

Borghetti, J. et al. ‘Memristive’ switches enable ‘stateful’ logic operations via material implication. Nature 464, 873–876 (2010).

Shulaker, M. M. et al. Three-dimensional integration of nanotechnologies for computing and data storage on a single chip. Nature 547, 74–78 (2017).

Acknowledgements

This work was supported by the National Key Research and Development Program (2017YFB0405600), National Natural Science Foundation of China (61622401, 61851402 and 61734003), Shanghai Education Development Foundation and Shanghai Municipal Education Commission Shuguang Program (18SG01). P.Z. acknowledges support from Shanghai Municipal Science and Technology Commission (18JC1410300). P.Z. thanks D. Sandubashao’s group for encouragement and help, and H. Zhou from Giantec Semiconductor for assistance during device fabrication and for discussions.

Author information

Authors and Affiliations

Contributions

P.Z. conceived the idea and supervised the experiments. C.L. performed the device fabrication and carried out the electrical characteristics measurements. H.C., X.H., H.Z., J.H., Y.-G.J. and X.Z. provided valuable input to the overall experiments. D.W.Z. provided input regarding the experiment conditions. C.L. and P.Z. wrote the paper, with help from all authors.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Journal peer review information: Nature Nanotechnology thanks Wei Chen and other anonymous reviewer(s) for their contribution to the peer review of this work.

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Supplementary Sections 1–8, Supplementary Figs. 1–8, Supplementary references 1–7

Rights and permissions

About this article

Cite this article

Liu, C., Chen, H., Hou, X. et al. Small footprint transistor architecture for photoswitching logic and in situ memory. Nat. Nanotechnol. 14, 662–667 (2019). https://doi.org/10.1038/s41565-019-0462-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41565-019-0462-6

This article is cited by

-

On-chip optoelectronic logic gates operating in the telecom band

Nature Photonics (2024)

-

Wearable in-sensor reservoir computing using optoelectronic polymers with through-space charge-transport characteristics for multi-task learning

Nature Communications (2023)

-

A reconfigurable binary/ternary logic conversion-in-memory based on drain-aligned floating-gate heterojunction transistors

Nature Communications (2023)

-

Ferroelectric gating of two-dimensional semiconductors for the integration of steep-slope logic and neuromorphic devices

Nature Electronics (2023)

-

Programmable graded doping for reconfigurable molybdenum ditelluride devices

Nature Electronics (2023)