Abstract

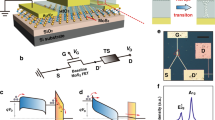

The so-called Boltzmann tyranny defines the fundamental thermionic limit of the subthreshold slope of a metal–oxide–semiconductor field-effect transistor (MOSFET) at 60 mV dec−1 at room temperature and therefore precludes lowering of the supply voltage and overall power consumption1,2. Adding a ferroelectric negative capacitor to the gate stack of a MOSFET may offer a promising solution to bypassing this fundamental barrier3. Meanwhile, two-dimensional semiconductors such as atomically thin transition-metal dichalcogenides, due to their low dielectric constant and ease of integration into a junctionless transistor topology, offer enhanced electrostatic control of the channel4,5,6,7,8,9,10,11,12. Here, we combine these two advantages and demonstrate a molybdenum disulfide (MoS2) two-dimensional steep-slope transistor with a ferroelectric hafnium zirconium oxide layer in the gate dielectric stack. This device exhibits excellent performance in both on and off states, with a maximum drain current of 510 μA μm−1 and a sub-thermionic subthreshold slope, and is essentially hysteresis-free. Negative differential resistance was observed at room temperature in the MoS2 negative-capacitance FETs as the result of negative capacitance due to the negative drain-induced barrier lowering. A high on-current-induced self-heating effect was also observed and studied.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 12 print issues and online access

$259.00 per year

only $21.58 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

References

Ionescu, A. M. & Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479, 329–337 (2011).

Sze, S. M. & Ng, K. Physics of Semiconductor Devices 3rd edn (Wiley, Hoboken, New Jersey, 2008).

Salahuddin, S. & Datta, S. Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett. 8, 405–410 (2008).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nature Nanotech. 6, 147–150 (2011).

Liu, H., Neal, A. T. & Ye, P. D. Channel length scaling of MoS2 MOSFETs. ACS Nano 6, 8563–8569 (2012).

Das, S., Chen, H.-Y., Penumatcha, A. V. & Appenzeller, J. High performance multilayer MoS2 transistors with scandium contacts. Nano Lett. 13, 100–105 (2013).

Wang, H. et al. Integrated circuits based on bilayer MoS2 transistors. Nano Lett. 12, 4674–4680 (2012).

Desai, S. B. et al. MoS2 transistors with 1-nanometer gate lengths. Science 354, 99–102 (2016).

English, C. D., Shine, G., Dorgan, V. E., Saraswat, K. C. & Pop, E. Improved contacts to MoS2 transistors by ultra-high vacuum metal deposition. Nano Lett. 16, 3824–3830 (2016).

Liu, Y. et al. Pushing the performance limit of sub-100 nm molybdenum disulfide transistors. Nano Lett. 16, 6337–6342 (2016).

Yang, L. et al. Chloride molecular doping technique on 2D materials: WS2 and MoS2. Nano Lett. 14, 6275–6280 (2014).

Liu, L., Lu, Y. & Guo, J. On monolayer MoS2 field-effect transistors at the scaling limit. IEEE Trans. Electron. Dev. 60, 4133–4139 (2013).

Gopalakrishnan, K., Griffin, P. B. & Plummer, J. D. I-MOS: a novel semiconductor device with a subthreshold slope lower than kT/q. Proc. IEEE Int. Electron. Dev. Meet. 289–292 (2002).

Appenzeller, J., Lin, Y.-M., Knoch, J. & Avouris, P. Band-to-band tunneling in carbon nanotube field-effect transistors. Phys. Rev. Lett. 93, 196805 (2004).

Sarkar, D. et al. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature 526, 91–95 (2015).

Abele, N. et al. Suspended-gate MOSFET: bringing new MEMS functionality into solid-state MOS transistor. Proc. IEEE Int. Electron. Dev. Meet. 479–481 (2005).

Dubourdieu, C. et al. Switching of ferroelectric polarization in epitaxial BaTiO3 films on silicon without a conducting bottom electrode. Nature Nanotech. 8, 748–754 (2013).

Jain, A. & Alam, M. A. Stability constraints define the minimum subthreshold swing of a negative capacitance field-effect transistor. IEEE Trans. Electron. Dev. 61, 2235–2242 (2014).

Khan, A. I. et al. Negative capacitance in a ferroelectric capacitor. Nat. Mater. 14, 182–186 (2015).

Zubko, P. et al. Negative capacitance in multidomain ferroelectric superlattices. Nature 534, 524–528 (2016).

McGuire, F. A., Cheng, Z., Price, K. & Franklin, A. D. Sub-60 mV/decade switching in 2D negative capacitance field-effect transistors with integrated ferroelectric polymer. Appl. Phys. Lett. 109, 093101 (2016).

Wang, X. et al. Ultrasensitive and broadband MoS2 photodetector driven by ferroelectrics. Adv. Mater. 27, 6575–6581 (2015).

Salvatore, G. A., Bouvet, D. & Ionescu, A. M. Demonstration of subthreshold swing smaller than 60 mV/decade in Fe-FET with P(VDF-TrFE)/SiO2 gate stack. Proc. IEEE Int. Electron. Dev. Meet. 167–170 (2008).

Muller, J. et al. Ferroelectricity in simple binary ZrO2 and HfO2. Nano Lett. 12, 4318–4323 (2012).

Cheng, C. H. & Chin, A. Low-voltage steep turn-on pMOSFET using ferroelectric high-κ gate dielectric. IEEE Electron. Dev. Lett. 35, 274–276 (2014).

Lee, M. H. et al. Prospects for ferroelectric HfZrO x FETs with experimentally CET = 0.98 nm, SSfor = 42 mV/dec, SSrev = 28 mV/dec, switch-off <0.2V, and hysteresis-free strategies. Proc. IEEE Int. Electron. Dev. Meet. 616–619 (2015).

Zhou, J. et al. Ferroelectric HfZrO x Ge and GeSn PMOSFETs with sub-60 mV/decade subthreshold swing, negligible hysteresis, and improved IDS. Proc. IEEE Int. Electron. Dev. Meet. 310–313 (2016).

Li, K. S. et al. Sub-60mV-swing negative-capacitance FinFET without hysteresis. Proc. IEEE Int. Electron. Dev. Meet. 620–623 (2015).

Ota, H. et al. Fully coupled 3-D device simulation of negative capacitance FinFETs for sub 10 nm integration. Proc. IEEE Int. Electron. Dev. Meet. 318–321 (2016).

McGuire, F. A. et al. Sustained sub-60 mV/decade switching via the negative capacitance effect in MoS transistors. Nano Lett. 17, 4801–4806 (2017).

Acknowledgements

This material is based upon work partly supported by the Air Force Office of Scientific Research (AFOSR)/National Science Foundation (NSF) Two-Dimensional Atomic-layer Research and Engineering (2DARE) programme, Army Research Office (ARO) and Semiconductor Research Corporation (SRC).

Author information

Authors and Affiliations

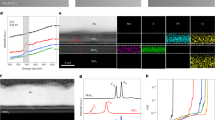

Contributions

P.D.Y. conceived the idea and supervised the experiments. C.J.S. performed the ALD of HZO and Al2O3 and dielectric physical analysis. M.S. performed the device fabrication, d.c. and C–V measurements, and data analysis. M.S. and N.J.C. carried out the fast I–V measurement. M.S. and G.Q. performed the AFM measurement. H.Z., K.D.M. and A.S. did the thermo-reflectance imaging. G.Q. performed the Raman and photoluminescence experiment. C.T.W. conducted TEM and EDS analyses. C.J. and A.M.A. conducted the theoretical calculations and analysis. M.S., A.M.A. and P.D.Y. summarized the manuscript and all authors commented on it.

Corresponding author

Ethics declarations

Competing financial interests

The authors declare no competing financial interests.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Supplementary Information

Steep Slope Hysteresis-free Negative Capacitance MoS2 Transistors.

Rights and permissions

About this article

Cite this article

Si, M., Su, CJ., Jiang, C. et al. Steep-slope hysteresis-free negative capacitance MoS2 transistors. Nature Nanotech 13, 24–28 (2018). https://doi.org/10.1038/s41565-017-0010-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41565-017-0010-1

This article is cited by

-

Steep-slope vertical-transport transistors built from sub-5 nm Thin van der Waals heterostructures

Nature Communications (2024)

-

Process implications on the stability and reliability of 300 mm FAB MoS2 field-effect transistors

npj 2D Materials and Applications (2024)

-

The future transistors

Nature (2023)

-

Ferroelectric gating of two-dimensional semiconductors for the integration of steep-slope logic and neuromorphic devices

Nature Electronics (2023)

-

A reconfigurable transistor and memory based on a two-dimensional heterostructure and photoinduced trapping

Nature Electronics (2023)