Abstract

Silicon-based implantable neural devices have great translational potential as a means to deliver various treatments for neurological disorders. However, they are currently held back by uncertain longevity following chronic exposure to body fluids. Conventional deposition techniques cover only the horizontal surfaces which contain active electronics, electrode sites, and conducting traces. As a result, a vast majority of today’s silicon devices leave their vertical sidewalls exposed without protection. In this work, we investigated two batch-process silicon dioxide deposition methods separately and in combination: atomic layer deposition and inductively-coupled plasma chemical vapor deposition. We then utilized a rapid soak test involving potassium hydroxide to evaluate the coverage quality of each protection strategy. Focused ion beam cross sectioning, scanning electron microscopy, and 3D extrapolation enabled us to characterize and quantify the effectiveness of the deposition methods. Results showed that bare silicon sidewalls suffered the most dissolution whereas ALD silicon dioxide provided the best protection, demonstrating its effectiveness as a promising batch process technique to mitigate silicon sidewall corrosion in chronic applications.

Similar content being viewed by others

Introduction

A wide variety of implantable neural devices have been developed using microfabrication as a reliable and reproducible method for producing large batches of electrical1,2, chemical3, optical4, multimodal5, and microfluidic devices6. These devices have expanded our knowledge about the nervous systems and may soon have clinical applications in treating neurological disorders7. In particular, an early example of a device with significant impact was the Michigan probe1. Other groups have since innovated on this design style8,9, adding features such silicon-on-insulator (SOI) shank shaping10,11,12,13, high channel counts14,15,16, and CMOS-based microelectrodes17,18,19. The logical next step is to translate these technologies to clinical applications. While there have been successful long-term chronic studies in animals12,13,20, to date, there has been no U.S. Food and Drug Administration (FDA) clinical approval for “multisite” (multiple microelectrodes per shank) silicon-based microelectrodes. This stands in contrast to the Utah Electrode Array or Blackrock Array, which has been approved for human implantation for up to one month but is limited to only one electrode site at the tip of each shank21. For penetrating multisite microelectrodes and other silicon-based devices of various modalities to be approved for human use, long-term reliability and biostability must be demonstrated.

Microelectronics implanted in vivo are typically protected by layers of chemically inert, electrically insulating materials such as silicon dioxide (SiO2)4,22, silicon nitride (SiNx)11, multilayer stacks of SiO2 and SiNx13, or polymers such as Parylene C13,16, polyimide23, or SU-824. These materials prevent exposure of conducting elements to the body environment, which can compromise device performance by creating short circuits and allowing corrosion to occur22,25. Although the top surfaces are protected, almost all penetrating multisite silicon-based devices leave the sidewalls of the silicon shanks exposed to body fluids without protection. This is generally considered acceptable as the sidewalls do not have conducting elements on them. However, silicon corrodes in saline environments at a rate depending on the temperature, chemistry of the solution, and silicon doping level. In a study by Hwang et al., their most physiologically relevant measurement was 36.8 µm per year for undoped silicon in 37 °C bovine serum26. In another study, they showed that heavily doping the silicon slowed dissolution by about an order of magnitude27. Unfortunately, for microscale devices intended to be implanted for decades, even a few microns of dissolution per year can contribute to device failure22,25. Therefore, unprotected silicon sidewalls may present a barrier to clinical approval for permanent implantation and neural stimulation applications.

With the exceptions of single-tip devices such as microwires and Blackrock array, only one study, to our knowledge, attempted to protect the sidewalls. In this previous study, Parylene C was deposited as a conformal coating after releasing the silicon probes13. However, this method required serial laser ablation to expose the electrode sites, with a narrow parameter space between successful removal of Parylene and damage to the underlying electrode material. An ideal sidewall protection technique would be batch process-compatible and utilize a low-temperature process that does not preclude the use of commonly used metals (e.g., gold, titanium) and photoresist.

In this work, we explored two deposition techniques that met these constraints: atomic layer deposition (ALD) and inductively-coupled plasma chemical vapor deposition (ICPCVD). Both these processes are compatible with batch processing and are performed at photoresist friendly temperatures (≤130 °C), which allows us to use photoresist to protect top device features. For the material, we chose SiO2 due to its biocompatibility and biostability28,29,30. In order to assess the sidewall coverage, we utilized wet etching using potassium hydroxide (KOH) as a silicon etchant. KOH has high etch selectivity for silicon over SiO231,32, so any pinholes or defects in the sidewall protection will allow rapid etching of the underlying silicon, making this a straightforward, rapid, and simple method to evaluate the coverage quality. Although concentrated KOH is not present in the physiological environment, identifying pinholes and defects is useful, since these spots are likely to be weak points for degradation of silicon in vivo. We fabricated test devices with the same shape and material composition as our previously-validated neural microelectrodes12,13,20, and coated the sidewalls of the shanks with ALD SiO2, ICPCVD SiO2, both, or neither (control). To compare the success of each technique, we used focused ion beam (FIB) cross sectioning, scanning electron microscopy (SEM), and 3D extrapolations of etched silicon volumes.

Results

Qualitative observation of exposed silicon surface over time

As shown in Fig. 1, the front views of the device tips revealed the etched profiles of the sidewalls before and after KOH wet etching. The first row (Fig. 1a–c) shows a control device (bare silicon). After 30 min in KOH, silicon was extensively etched, as expected. The second row (Fig. 1d–f) shows that ALD SiO2 was intact after 5 min, and even after 30 min, with only a thin band of exposed silicon visible near the top edge. The third row (Fig. 1g–i) shows ICPCVD sidewall protection which, after 5 min of etching, kept the silicon mostly intact (Fig. 1h). However, after 30 min, roughly half of the silicon wall was exposed (Fig. 1i). The fourth row (Fig. 1j–l) shows the dual ALD and ICPCVD SiO2 films. After 5 min of etching, the sidewall protection films were partially collapsed near the top surface (Fig. 1k), and after 30 min, more silicon was exposed (Fig. 1l), but still less severe than ICPCVD alone (Fig. 1i). The spatial pattern of the insulation breakdown was more irregular than the other groups.

The columns correspond to etch durations of 0 min, 5 min, and 30 min, while the rows represent deposition methods. False coloring indicates different materials. The less exposed silicon (blue) on the sidewalls, the better the protection. The scale bars are 50 µm. The control group (top row, a–c) suffered the most etching whereas the ALD film (second row, d–f) provided the best protection. The ICPCVD (third row, g–i) and ALD/ICPCVD (fourth row, j–l) films showed obvious etching over time. Partial exposure of silicon through SiO2 is visible in (f), (i), (k), and (l).

Quantification of etched silicon volume and overall assessment

Quantification of the etched silicon volume was performed based on the side view SEM images, as shown in Fig. 2a. Extrapolated 3D volumes were quantified and plotted in Fig. 2b, enabling comparison among the four sample groups. Control devices were heavily etched along the entire sidewall surface by an average volume of 952,381 ± 52,662 μm3. ALD-protected devices, meanwhile, had the least amount of silicon etched: 33,682 ± 2925 μm3. Average etched volume for ICPCVD and ALD/ICPCVD were 477,898 ± 23,383 μm3 and 322,052 ± 18,510 μm3, respectively. One-way ANOVA showed there was a significant difference among the means of etched volumes (p < 0.01) and Tukey pairwise comparisons confirmed significant differences for all combinations with 95% confidence. Overall, ALD resulted in the least etched volume and was, therefore, the best protection, followed by ALD/ICPCVD, then ICPCVD. Surprisingly, this means that ALD outperformed ALD/ICPCVD, suggesting that ICPCVD after ALD actually reduced the performance of the ALD layer. In contrast, ALD did not reduce the performance of ICPCVD, because ALD/ICPCVD outperformed ICPCVD. In this study, the residual stress for ICPCVD film was measured at 32.88 ± 1.58 MPa, compressive.

a Side view SEM images, as noted in Fig. 6a, from each group after 30 min KOH etching. False coloring is identical to Fig. 1. Bright purple areas on ICPCVD panel are charged up photoresist during imaging. The scale bars are 10 µm. b Comparison of etched silicon volume for each group using 3D extrapolated models. ALD-protected devices showed the least loss of silicon sidewalls whereas bare silicon was etched the most. The error bars are standard deviation of the mean for each group (N = 3). Tukey pairwise comparisons confirmed significant differences for all combinations after one-way ANOVA (p < 0.01 and 95% confidence level).

High-resolution SEM analysis of ALD/ICPCVD failure mode

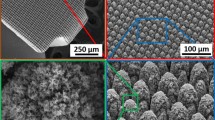

We investigated the ALD/ICPCVD dual-coating using SEM to determine why it performed only moderately well despite its higher overall film thickness and underlying ALD layer. Figure 3a shows the sidewalls after 5 min KOH etching which revealed strips of SiO2 corresponding to the periodic, scalloped morphology formed by the DRIE Bosch process on silicon. A higher magnification image (Fig. 3b) also supports the idea that SiO2 detached from the silicon surface in strips as opposed to being etched through. The detachment appears to start near the top, which was also seen at the tip of the device (Fig. 3c). A high magnification view of a fallen piece of ALD/ICPCVD SiO2 lying on its side (Fig. 3d) revealed the columnar growth structure of the film.

a The protection layer collapsed in “strips,” starting from near the top. The scale bar is 10 µm. b The boundary between exposed silicon and SiO2 protection film shows an abrupt interface. The scale bar is 3 µm. c Closer view at the front edge of the device tip. The scale bar is 5 µm. d High magnification view of a dislodged SiO2 strip. The scale bar is 500 nm.

FIB-SEM analysis of sidewall coverage

Figure 4a–c show cross-section views of the top edges of the devices before KOH etching for an ALD-protected, ICPCVD-protected, and ALD/ICPCVD-protected devices, respectively. All images show that silicon is slightly undercut laterally from the edge of the thermal oxide layer (Tox), a known effect of DRIE. ALD appears to conformally cover the sidewalls even at the hard-to-access area which is indicated by an arrow (Fig. 4a), in contrast to ICPCVD which leaves some gaps in the protection layer (Fig. 4b). These gaps become smaller further down the sidewall and the coverage eventually becomes continuous (Fig. 4d). This may explain why the sidewall protection collapsed from the top as seen in Fig. 1.

Yellow arrows indicate the protection films and gaps in coverage. a Top edge of an ALD-protected device shows conformal and uniform coverage without gaps. The top and bottom images’ scale bars are 2 µm and 500 nm, respectively, for (a–c). b Top edge of an ICPCVD-protected device, in which low conformality is noted, and, in particular, gaps in coverage. c Top edge of an ALD/ICPCVD-protected device, in which a relatively uneven (bulging) film morphology and gaps in coverage are noted. d ICPCVD-protected sidewall, at various heights, revealing a noticeable gap in coverage at the top and more uniform coverage toward the bottom. The scale bars are 200 nm. TOX = thermal oxide.

Discussion

Long-term reliability and biostability of silicon-based penetrating multisite microelectrodes and chemical, optical, or multimodal devices remains a major challenge7. An overlooked design consideration is to protect the exposed silicon sidewalls from the physiological environment. Exposed silicon sidewalls are present for the vast majority of devices reported so far1,8,9,10,11,15,16,17,18. This oversight may be a barrier to clinical approvals for human use. To the best of our knowledge, this is the first paper that systematically studied silicon sidewall dissolution in penetrating multisite microelectrodes as a potential failure source for chronic implantations. In this work, we developed batch-process-compatible sidewall protection strategies and assessed their coverage quality with a simple, rapid KOH etch.

Accelerated aging is the typical technique for evaluating neural microelectrodes’ long-term materials reliability. The elevated temperature of a phosphate-buffered saline solution exponentially accelerates aging of the device according to the Arrhenius equation33. However, the experiment may still take weeks to months depending on the desired lifetime of the implant in the human body. Assuming Arrhenius behavior, the rate of reaction approximately doubles with each 10 °C increase in temperature34. In other words, even at 87 °C, in order to study failure over an equivalent 20 years device lifetime in vivo, one would need to perform accelerated testing on the devices up to a period of 7.5 months in vitro. Reactive accelerated aging has been proposed as a more in vivo-like test by employing reactive oxygen species in addition to elevated temperatures, although it requires a specialized setup35. Our purpose in this study was to compare the quality of several SiO2 sidewall protection films. Our rapid KOH accelerated failure test reveals pinholes, defects, or unprotected areas in the SiO2 sidewall protection films due to its high etch selectivity for silicon. This rapid failure test can be used to evaluate insulation coverage faster than standard PBS-based accelerating soak testing and to comparatively screen candidate insulation films.

The 3D-extrapolated calculations of etched silicon volume in this study were made based on the assumption that the etched profile of the device’s front edge was consistent along the rest of the device’s sidewalls. It may be possible to construct more sophisticated 3D models using overlapping SEM images36,37. However, our focus was in obtaining relative performance metrics against the control.

Among the insulation materials tested, ALD performed the best in terms of surface coverage and quantified volume of etched silicon, as seen in Figs. 1 and 2, respectively. ALD’s uniform and conformal deposition property was crucial to its success. This property is due to its self-limiting surface reaction during film nucleation compared to conventional CVD techniques38. This feature enabled extremely conformal film growth which was critical for sidewall protection, particularly underneath the edge of the silicon shank (Fig. 4a). ICPCVD was too directional to cover all parts of the sidewall. We were not surprised to find that ALD/ICPCVD outperformed ICPCVD alone due to the presence of additional film thickness and the better coverage from the ALD film. However, its inferiority to ALD was intriguing. As both ALD and ICPCVD films are compressively stressed39,40,41,42, it is possible that the combined stress may have been large enough to cause the film to delaminate. It is also possible that the adhesion of ALD was stronger to ICPCVD (both are oxides) than to the silicon sidewall, contributing to delamination of the films (Fig. 3d). In both cases, deposition non-uniformity resulted in the bulging appearance near the top edge, as seen in Fig. 4c, which likely did not help sustain the sidewall structure.

In addition, we observed that failure of the sidewall protection started near the top edge (Fig. 5a) in all groups. We postulate that this is attributable to two mechanisms: (1) the protection films were less conformal near the top, exposing the silicon, and (2) better KOH diffusion access to the top areas may have caused faster etching of SiO2. FIB-SEM strongly suggests that the first mechanism played a role for ICPCVD films because there were easily-visible gaps in the protection layers near the top, but fewer near the bottom. These insulation gaps would have allowed KOH to etch silicon beneath the protection layers, causing them to detach. Meanwhile, ALD SiO2 did not show any visible gaps, but also showed a modest etching near the top after 30 min. This could be due to the second mechanism. Finally, it is possible that a combination of the two mechanisms played a role. The possibility of electrochemical corrosion as a contributing factor in this study is unlikely. These results provide an interesting contrast with a recent study that showed a bilayer of plasma-assisted-ALD Al2O3 and Parylene C failed more quickly than Parylene C alone. The suggested mechanism in this study was dissolution of the alumina film allowing undercutting and detachment of the Parylene C43. To avoid having aluminum in our ALD film, we performed a slower ALD process with trismethylaminosilane and ozone.

a The starting wafer had a 1 µm-thick layer of thermal SiO2 over a 500 µm-thick silicon wafer. b SiO2/ SiNx stack passivation layers were deposited by PECVD. Conductive traces were skipped for simplicity. c The shape of the devices was defined by photolithography. d Reactive ion etching selectively removed SiO2 and SiNx layers. e Deep reactive ion etching of silicon shaped probe shanks, at which point the silicon sidewalls are exposed. f Conformal coating of silicon sidewalls was achieved by (f-1) ALD, (f-2) ICPCVD, or (f-3) ALD and ICPCVD. The photoresist was left in place during deposition in anticipation of functional device fabrication, in which case the photoresist would be needed to protect the electrode sites until the devices are released from the wafer.

Our techniques for protecting sidewalls of a penetrating multisite microelectrode can be applied to most existing silicon-based devices. A technique for protecting functional devices is described below. Assuming the top feature plane is covered by hard-baked photoresist, which is the case after DRIE (Fig. 5e), a sidewall protection SiO2 film (e.g., ALD) can be deposited. A follow-up anisotropic dry etch can be performed to etch away the SiO2 film from the top and bottom horizontal surfaces, while leaving the vertical sidewalls mostly unchanged. In certain conditions, the thermal oxide projecting out over the sidewalls (Fig. 4a–c) would help protect the top corners of the sidewalls from the anisotropic etch. The rest of the process would be identical to what has been described in previous papers to backside etch and release probes from the wafer12,13,20,44,45.

In summary, most of the implantable silicon-based penetrating multisite neural devices leave the silicon sidewalls exposed to body fluids without protection. We investigated multiple SiO2 films as sidewall protection. We employed a KOH wet etch as a rapid evaluation of ALD and ICPCVD SiO2 film coverage quality. Among the studied groups, ALD provided the best coverage in terms of silicon etched volumes. Our results showed that ALD reduced etched silicon volume by a factor of 28.27 compared to bare silicon (control), while ALD/ICPCVD reduced it by a factor of 2.96, and ICPCVD by 1.99. We also showed that our rapid failure analysis technique is an effective engineering tool that allows expedited evaluation of film coverage. Application of this technique is not limited to microelectrodes and could be implemented in many types of silicon-based implantable devices requiring failure-free chronic implantation and FDA approval. Future work will compare these results with standard accelerating aging tests results and validate the ALD protection technique in a long-term in vivo functional study.

Methods

Fabrication process overview

Figure 5 shows an overview of the microfabrication process which was part of a previously in vivo-validated device technology12,13,44,45,46,47,48. Four groups of devices were fabricated in this study: control (no protection), ALD-SiO2, ICPCVD-SiO2, and both ALD- and ICPCVD-SiO2. Briefly, the process began with a 100 mm-diameter silicon wafer which is heavily boron-doped, with resistivity 0.005–0.02 Ω·cm, and has 1 µm-thick thermal SiO2 (Ultrasil LLC, CA, USA) (Fig. 5a). Eight passivation layers were deposited in a plasma enhanced chemical vapor deposition (PECVD) system (STS, UK), in the order of NONONONO, where N is SiNx and O is SiO2, to a total thickness of 1.85 µm (Fig. 5b). Then, to define the device shank, 9 µm-thick AZ4620 photoresist was patterned and hard baked at 100 °C for 30 min (Fig. 5c), followed by reactive ion etching (90 sccm Ar, 10 sccm C3F8) to etch through passivation layers and thermal oxide using an NLD-570 ICP RIE (ULVAC, MA, USA) (Fig. 5(d)). Deep reactive ion etching (DRIE) Bosch processing (400 sccm SF6, 1 sccm C4F8) in an Omega LPX Rapier DRIE system (SPTS, UK) was performed to etch approximately 80 µm into silicon, which exposed the sidewalls of the shanks (Fig. 5e). Then, except for the control sample, samples were coated with SiO2 using ALD and/or ICPCVD. Deposition details are provided in the following sections. Fabrication was performed at the University of Connecticut (CT, USA) and Harvard University (MA, USA).

Atomic layer deposition (ALD)

ALD is known for highly conformal and pinhole-free film deposition at relatively low temperatures38. Approximately 50 nm-thick SiO2 (1500 cycles) was deposited on the samples following DRIE (Fig. 5f-1). Trismethylaminosilane and ozone were used as precursors in an AT410 ALD system (Anric Technologies, MA, USA). The chamber temperature was 130 °C and the deposition rate was 0.02–0.035 nm per cycle. Film thickness was confirmed using ellipsometry (Film Sense LLC, NE, USA) on a witness silicon chip.

Inductively-coupled plasma chemical vapor deposition (ICPCVD)

Inductively-coupled plasma can achieve higher film quality than conventional parallel electrode PECVD, even at lower deposition temperatures, due to its high-density plasma39. Approximately 1323 nm SiO2 was deposited on samples for 90 min in an ICPCVD reactor (Oxford Instruments, UK) (Fig. 5f-2). Film thickness was measured using ellipsometry on a witness silicon chip. The chuck temperature was 80 °C. Chamber gases were silane, helium, and oxygen. The ICP power was 1322 W. Residual stress was measured using a dual laser thin film stress measurement instrument (Toho Technology Inc, IL, USA) on a 100 mm-diameter silicon wafer before and after deposition (four repetitions).

Accelerated failure test

We designed our etching experiment based on the well-established etch rate difference between silicon and SiO2 of two orders of magnitude32,49. Approximately 1.5 × 1.5 cm2 rectangular chips containing multiple dies from a 100 mm-diameter wafer were placed in 45% KOH in a beaker on a 60 °C hotplate. Three etching durations of 0 min, 5 min, and 30 min were used. Samples were placed face-up at the bottom of the beaker and there was no agitation in the solution. Three devices were available in each group for analysis.

Scanning electron microscopy

Qualitative and quantitative evaluation of silicon sidewalls was conducted by SEM on each sample, before and after 30 min of KOH etching, using a SU8230 electron microscope (Hitachi High-Tech America, Inc., IL, USA). Devices were mounted and fixed horizontally on the SEM stage using carbon tape and were tilted 40°. Examples are shown in Fig. 6b, c. Detector mode was secondary electron, the working distance was approximately 14.5 mm, and the accelerating voltage was 2 kV. False coloring of the images was done in GNU Image Manipulation Program 2.10.

a A functional probe with an arrow indicating the SEM viewing direction (“tip side view”). The scale bar is 1 mm. b On the left is data collection from an SEM side view of the probe tip with sidewall surface points before KOH etch (solid circles). The scale bar is 10 µm. On the right is the side view of the generated model in SolidWorks based on those surface points. c Data collection from an SEM image after 30 min KOH etch with surface points (hollow circles). The scale bar is 10 µm. Right is the side view of the generated model in SolidWorks. The reduction in volume after 3D extrusion defined the etched volume.

3D extrapolation and quantification

Quantification of etched silicon volume was achieved by 3D extrapolation of 2D SEM images. First, SEM images of shank tips (Fig. 6b-left) were imported into ImageJ50. Then, a series of points along the vertical edge of the shank were acquired and corrected to account for the 40° tilt as “surface points” (Fig. 6b-left). This step identified the surfaces of the silicon sidewalls. Separately, the design layout of the device (L-Edit, Tanner Research, USA) was imported into SolidWorks (Dassault Systèmes, France) and was extruded to the actual dimensions of the fabricated silicon device (Fig. 6b-right). Next, the surface points were used to define extruded cuts along all sidewalls of the model silicon shank, assuming etching was consistent along the lengths of the shank (Fig. 6b, c-right). Finally, the volumes of the etched and non-etched models were compared.

Statistical reliability was tested using one-way analysis of variance (ANOVA) with N = 3 for each group in Minitab19 (Minitab, LLC, IL, USA) followed by Tukey pairwise comparison for 95% confidence level. A p-value of 0.05 was considered statistically significant.

Focused ion beam scanning electron microscopy

To understand the interior structures of the sidewalls, FIB cross-section images were taken. A 5 nm coating of 80:20 platinum:palladium alloy was sputtered onto the FIB samples to reduce charging. FIB cross sections were then obtained using a FEI Helios 660 (Thermo Fisher Scientific Materials and Structural Analysis Division, Oregon, USA) or ZEISS Crossbeam (Carl Zeiss Microscopy, LLC, NY, USA), both with gallium ion source. The cut was done on the edge of the device shank. A platinum strap was deposited by the FIB before cutting to protect the surface morphology of the sample.

Data availability

The authors confirm that all relevant data are available with restrictions.

References

Najafi, K., Ji, J. & Wise, K. D. Scaling limitations of silicon multichannel recording probes. IEEE Trans. Biomed. Eng. 37, 111 (1990).

Nambiar, A., Nolta, N. F. & Han, M. 3D Reconstruction of the intracortical volume around a hybrid microelectrode array. Front. Neurosci. 13, 393 (2019).

Frey, O. et al. Enzyme-based choline and L-glutamate biosensor electrodes on silicon microprobe arrays. Biosens. Bioelectron. 26, 477–484 (2010).

Son, Y. et al. In vivo optical modulation of neural signals using monolithically integrated two-dimensional neural probe arrays. Sci. Rep. 5, 15466 (2015).

Song, E. et al. Flexible electronic/optoelectronic microsystems with scalable designs for chronic biointegration. Proc. Natl Acad. Sci. USA 116, 15398–15406 (2019).

Seidl, K. et al. In-plane silicon probes for simultaneous neural recording and drug delivery. J. Micromech. Microeng. 20, 105006 (2010).

Wellman, S. M. et al. A materials roadmap to functional neural interface design. Adv. Funct. Mater. 28, 1701269 (2018).

Turner, J. N. et al. Cerebral astrocyte response to micromachined silicon implants. Exp. Neurol. 156, 33–49 (1999).

Kewley, D. T. et al. Plasma-etched neural probes. Sens. Actuator A Phys. 58, 27–35 (1997).

Norlin, P., Kindlundh, M., Mouroux, A., Yoshida, K. & Hofmann, U. G. A 32-site neural recording probe fabricated by DRIE of SOI substrates. J. Micromech. Microeng. 12, 414–419 (2002).

Cheung, K. C., Djupsund, K., Dan, Y. & Lee, L. P. Implantable multichannel electrode array based on SOI technology. J. Microelectromech. Syst. 12, 179–184 (2003).

Han, M., & McCreery, D. B. A new chronic neural probe with electroplated iridium oxide microelectrodes. Ann. int. Conf. Proc. IEEE Eng. Med. Biol. Soc. 4220-4221 (2008).

Han, M., Manoonkitiwongsa, P. S., Wang, C. X. & McCreery, D. B. In vivo validation of custom-designed silicon-based microelectrode arrays for long-term neural recording and stimulation. IEEE Trans. Biomed. Eng. 59, 346–354 (2012).

Wise, K. D., Anderson, D. J., Hetke, J. F., Kipke, D. R. & Najafi, K. Wireless implantable microsystems: high-density electronic interfaces to the nervous system. Proc. IEEE 92, 76–97 (2004).

Ruther, P., Herwik, S., Kisban, S., Seidl, K. & Paul, O. Recent progress in neural probes using silicon MEMS technology. IEEJ Trans. Electr. Electron. Eng. 5, 505–515 (2010).

Du, J. G., Blanche, T. J., Harrison, R. R., Lester, H. A. & Masmanidis, S. C. Multiplexed, high density electrophysiology with nanofabricated neural probes. PLoS ONE 6, 11 (2011).

Angotzi, G. N. et al. SiNAPS: an implantable active pixel sensor CMOS-probe for simultaneous large-scale neural recordings. Biosens. Bioelectron. 126, 355–364 (2019).

Jun, J. J. et al. Fully integrated silicon probes for high-density recording of neural activity. Nature 551, 232–236 (2017).

Steinmetz, N. A., Koch, C., Harris, K. D. & Carandini, M. Challenges and opportunities for large-scale electrophysiology with Neuropixels probes. Curr. Opin. Neurobiol. 50, 92–100 (2018).

McCreery, D., Kamal, Y. & Martin, H. Responses of neurons in the feline inferior colliculus to modulated electrical stimuli applied on and within the ventral cochlear nucleus; Implications for an advanced auditory brainstem implant. Hear. Res. 363, 85–97 (2018).

Flesher, S. N. et al. Intracortical microstimulation of human somatosensory cortex. Sci. Transl. Med. 8, 361 (2016).

Hämmerle, H. et al. Biostability of micro-photodiode arrays for subretinal implantation. Biomaterials 23, 797–804 (2002).

Badia, J. et al. Biocompatibility of chronically implanted transverse intrafascicular multichannel electrode (TIME) in the rat sciatic nerve. IEEE Trans. Biomed. Eng. 58, 2324–2332 (2011).

Fu, T. M., Hong, G., Viveros, R. D., Zhou, T. & Lieber, C. M. Highly scalable multichannel mesh electronics for stable chronic brain electrophysiology. Proc. Natl Acad. Sci. USA 114, E10046–E10055 (2017).

Kozai, T. D. et al. Mechanical failure modes of chronically implanted planar silicon-based neural probes for laminar recording. Biomaterials 37, 25–39 (2015).

Hwang, S. W. et al. 25th anniversary article: materials for high‐performance biodegradable semiconductor devices. Adv. Mater. 26, 1992–2000 (2014).

Hwang, S. W. et al. Dissolution chemistry and biocompatibility of single-crystalline silicon nanomembranes and associated materials for transient electronics. ACS Nano 8, 5843–5851 (2014).

Fang, H. et al. Ultrathin, transferred layers of thermally grown silicon dioxide as biofluid barriers for biointegrated flexible electronic systems. Proc. Natl Acad. Sci. USA 113, 11682–11687 (2016).

Edell, D. J., Toi, V. V., McNeil, V. M. & Clark, L. D. Factors influencing the biocompatibility of insertable silicon microshafts in cerebral cortex. IEEE Trans. Biomed. Eng. 39, 635–643 (1992).

Maloney, J. M., Lipka, S. A., and Baldwin, S. P. In vivo biostability of CVD silicon oxide and silicon nitride films. Mater. Res. Soc. Symp. Proc., 872, https://doi.org/10.1557/PROC-872-J14.3 (2005).

Petersen, K. E. Silicon as a mechanical material. Proc. IEEE 70, 420–457 (1982).

Williams, K. R. & Muller, R. S. Etch rates for micromachining processing. J. Microelectromech. Syst. 5, 256–269 (1996).

Minnikanti, S. et al. Lifetime assessment of atomic-layer-deposited Al2O3-Parylene C bilayer coating for neural interfaces using accelerated age testing and electrochemical characterization. Acta Biomater. 10, 960–967 (2014).

Hukins, D. W. L., Mahomed, A. & Kukureka, S. N. Accelerated aging for testing polymeric biomaterials and medical devices. Med. Eng. Phys. 30, 1270–1274 (2008).

Takmakov, P. et al. Rapid evaluation of the durability of cortical neural implants using accelerated aging with reactive oxygen species. J. Neural Eng. 12, 026003 (2015).

Eulitz, M. & Reiss, G. 3D reconstruction of SEM images by use of optical photogrammetry software. J. Struct. Biol. 191, 190–196 (2015).

Dos Santos, Q. M., Dzika, E. & Avenant-Oldewage, A. Using scanning electron microscopy (SEM) to study morphology and morphometry of the isolated haptoral sclerites of three distinct diplozoid species. PloS One 14, e0211794 (2019).

Lee, J. H. et al. Investigation of silicon oxide thin films prepared by atomic layer deposition using SiH2Cl2 and O3 as the precursors. Jpn. J. Appl. Phys. 43, L328 (2004).

Mackenzie, K. D., Lee, J. W., and Johnson, D. Inductively-coupled plasma deposition of low temperature silicon dioxide and silicon nitride films for III–V applications. In Proc. 30th Symp. State-of-the-Art Progr. Comp. Semicond., 1–12 (1999).

Pfeiffer, K. et al. Comparative study of ALD SiO2 thin films for optical applications. Opt. Mater. Express 6, 660–670 (2016).

King, S. W. Plasma enhanced atomic layer deposition of SiN x: H and SiO2. J. Vac. Sci. Technol. A 29, 041501 (2011).

Lee, J. W. et al. Low temperature silicon nitride and silicon dioxide film processing by inductively coupled plasma chemical vapor deposition. J. Electrochem. Soc. 147, 1481 (2000).

Caldwell, R. et al. Analysis of Al2O3—Parylene C bilayer coatings and impact of microelectrode topography on long term stability of implantable neural arrays. J. Neural Eng. 14, 046011 (2017).

McCreery, D., Han, M., Pikov, V., Yadav, K. & Pannu, S. Encoding of the amplitude modulation of pulsatile electrical stimulation in the feline cochlear nucleus by neurons in the inferior colliculus; effects of stimulus pulse rate. J. Neural Eng. 10, 056010 (2013).

Pikov, V., McCreery, D. B. & Han, M. Intraspinal stimulation with a silicon-based 3D chronic microelectrode array for bladder voiding in cats. J. Neural Eng. 17, 065004 (2020).

Nolta, N. F., Ghelich, P., & Han, M. Recessed traces for planarized passivation of chronic neural microelectrodes. Annu. Int. Conf. Proc. IEEE Eng. Med. Biol. Soc. 5125–5128 (2019).

Nolta, N. F., Ghelich, P., Ersoz, A. & Han, M. Fabrication and modeling of recessed traces for silicon-based neural microelectrodes. J. Neural Eng. 17, 056003 (2020).

McCreery, D., Han, M. & Pikov, V. Neuronal activity evoked in the inferior colliculus of the cat by surface macroelectrodes and penetrating microelectrodes implanted in the cochlear nucleus. IEEE Trans. Biomed. Eng. 57, 1765–1773 (2010).

Williams, K. R., Gupta, K. & Wasilik, M. Etch rates for micromachining processing-Part II. J. Microelectromech. Syst. 12, 761–778 (2003).

Schneider, C. A., Rasband, W. S. & Eliceiri, K. W. NIH Image to ImageJ: 25 years of image analysis. Nat. Methods 9, 671–675 (2012).

Acknowledgements

We would like to thank Joseph Favata, Nicholas May, and Sina Shahbazmohamadi at the University of Connecticut for help with the FIB technique. This work was supported by the National Institute of Health grants R01DC014044 and R24NS086603 (MH). This work was performed in part at Harvard University’s Center for Nanoscale Systems (CNS), a member of the National Nanotechnology Coordinated Infrastructure Network (NNCI).

Author information

Authors and Affiliations

Contributions

Pejman Ghelich: methodology, validation, formal analysis, investigation, writing—original draft, visualization. Nicholas F. Nolta: methodology, validation, formal analysis, investigation, visualization, writing—review & editing. Martin Han: conceptualization, methodology, investigation, resources, writing—review & editing, supervision, project administration, funding acquisition.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Ghelich, P., Nolta, N.F. & Han, M. Unprotected sidewalls of implantable silicon-based neural probes and conformal coating as a solution. npj Mater Degrad 5, 5 (2021). https://doi.org/10.1038/s41529-021-00154-9

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41529-021-00154-9