Abstract

Transfer printing of high mobility inorganic nanostructures, using an elastomeric transfer stamp, is a potential route for high-performance printed electronics. Using this method to transfer nanostructures with high yield, uniformity and excellent registration over large area remain a challenge. Herein, we present the ‘direct roll transfer’ as a single-step process, i.e., without using any elastomeric stamp, to print nanoribbons (NRs) on different substrates with excellent registration (retaining spacing, orientation, etc.) and transfer yield (∼95%). The silicon NR based field-effect transistors printed using direct roll transfer consistently show high performance i.e., high on-state current (Ion) >1 mA, high mobility (μeff) >600 cm2/Vs, high on/off ratio (Ion/off) of around 106, and low hysteresis (<0.4 V). The developed versatile and transformative method can also print nanostructures based on other materials such as GaAs and thus could pave the way for direct printing of high-performance electronics on large-area flexible substrates.

Similar content being viewed by others

Introduction

Advances in flexible large-area electronics (LAE) have enabled novel applications across numerous areas including wearable systems, soft robotics, bendable displays, and healthcare1,2,3,4,5. This will also have an impact on the development of the Internet of Things (IoT) concept where smart objects are required to be aware of and interact with the environment6. Conformability of electronic devices to different shapes is indispensable for the above applications7,8,9,10,11,12,13. Further, fast computing and communication needed in many of these applications to enable myriad human-machine interactions with low latency also call for high performance of the devices. As a result, significant research efforts are being made to manufacture electronic devices and circuits with flexible form factors and high performance. For example, taking advantage of the high-performance Si technology, ultra-thin chips (UTCs) have been developed for system-in foil applications14,15. However, due to economic reasons and integration-related difficulties their use is limited to areas requiring compact electronics. The heterogeneous integration of advanced nanomaterials/nanostructures through printing is another manufacturing route that can bring innovations in high-performance flexible electronics7,16,17,18,19,20,21.

Among various printing technologies, transfer printing has shown good potential for realizing high-performance flexible electronic devices and circuits7,22 with silicon and compound semiconductor material-based nanostructures (NSs) such as micro-/nano-membranes (NMs), nanoribbons (NRs), nanowires (NWs), etc. as building blocks. In a conventional transfer printing process, the NSs are picked up from their growth/fabrication rigid substrates using soft polymeric stamps, usually made of Polydimethylsiloxane (PDMS), and then printed onto flexible substrates to obtain the electronic devices and circuits22,23. The controllable and reproducible transfer of NSs from the donor to the receiver substrate is critical for LAE, and hence a precise control over the interface properties (stamp/donor and stamp/receiver) is required during transfer printing. It is challenging to have complete control over printing parameters (e.g., retrieval/pick up velocity, adhesion switchability, stamp surface recovery, etc.) and interface properties and as a result, it is difficult to obtain high yield and reproducibility. This is due to the viscoelastic properties of soft stamps, which may cause unexpected tilt, orientation, and buckling of NSs under applied force during the printing process. Further, it is challenging to print sub-100 nm thick NSs using conventional transfer printing. This is because at such thicknesses the strain energy release rate at the stamp/NS interface decreases with respect to the NS/substrate interface, which leads to lower printing yield24. Few attempts have been made to address these challenges with modified transfer printing involving the surface morphology25,26, interface engineering27,28, thermal modulation and kinetically controlled velocity29,30,31, magnet-controlled32, and laser-driven method18, etc. (summarized in Table 1). These modified transfer printing methods improve the yield and reliability of the process and further extend the transfer printing capacities to: (i) selective printing33, (ii) arbitrary substrate integration34, and (iii) deterministic assembly of nano to chip-scale structures17,28,35. These modified transfer printing methods have shown good potential for flexible electronics, but they also require additional excitation equipment such as laser system, and magnet actuating system, etc. In this regard, it is highly desirable to develop a precise transfer printing process that enables higher transfer yield, excellent registration, and compatibility with R2R printing without adding complex printing equipment17,36,37.

In this work, we report a simple, cost-effective, yet robust direct roll transfer printing technique and demonstrates its efficacy for high-performance electronics by developing NR-based field-effect transistors (NRFETs). The developed technique has the following distinct advantages: (i) unlike conventional transfer printing, the presented method does not require a PDMS transfer stamp (hence, named as direct transfer printing), which means reduced number of printing steps and hence reduced printing cost and time. Further, it reduces the chance of breakage and/or wrinkling of printed nanostructures and hence helps to preserve their morphology and structure. This also offers an excellent opportunity to enhance the transfer yield and registration of printing nanostructures; (ii) The process helps to achieve high device-to-device uniformity by avoiding contamination from PDMS stamps, and (iii) the process is compatible with R2R fabrication which is advantageous for future LAE manufacturing. The semi-automated direct roll printing system has been used for printing sub-100 nm thick (≈70 nm) Si NR arrays directly on the target flexible receiver substrate using a custom roll system. Using a series of morphological characterizations such as Scanning Electron Microscopy (SEM) and Atomic Force Microscopy (AFM), we demonstrate: (a) near-perfect registration of the printed structures (<0.1 µm), (b) high yield (~95%), (c) residue-free transfer of Si NRs and (d) large area transfer (9 cm2). The direct transfer printed Si NRs were further processed to obtain NRFETs are accomplished following our recently demonstrated room temperature (RT) fabrication process including a dielectric deposition. The developed NRFETs exhibit excellent electrical properties: average device effective mobility of ~631 cm2/Vs, and high on/off current ratio (Ion/off) of around 106. The response after cyclic bending tests shows the device having excellent mechanical stability and flexibility. The obtained results are also compared with the Si NRFET devices obtained using conventional transfer printing. The presented results show the significant potential of direct transfer printing as a new route towards high-performance printed LAE.

Results and discussions

Direct roll transfer printing method

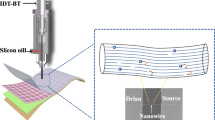

Figure 1 schematically shows the fabrication steps for NRFETs using direct roll printing technology. The printing process is displayed in the supplementary information (Supplementary video M1 and Fig. 1). The details of the processes are given in the experimental section. To draw the comparison, Fig. 1 also illustrates the processing steps for conventional transfer printing. For both printing techniques, silicon NRs are first fabricated on the rigid wafer using a conventional nanofabrication process, as described in our previous works7. Briefly, the fabrication process involves anisotropic wet etching of selected exposed regions on the top side of the Si wafer, followed by undercut etching of the buried oxide (Box) using hydrofluoric acid to eventually release Si NRs structures38,39,40. Figure 1a shows the fabrication steps to obtain Si NRs from a commercial silicon-on-insulator (SOI). The SEM image of the fabricated and released NRs is also shown in figure7. This method produces horizontal arrays of NRs over SOI source wafers, which are transfer printed onto flexible receiver substrates. The process steps for conventional transfer printing are shown in Fig. 1b. It can be seen from this figure, it is a two-step process where the transfer mechanism can be understood by studying the competing fracture between the stamp/NS interface and the NS/substrate interface41. The kinetically controlled conventional transfer printing process has shown poor yield for sub-100 nm thick NRs because of difficulties in controlling the mechanics of viscoelastic PDMS stamp. As a major advance over the traditional processes, direct roll printing addresses the above issue by avoiding the use of PDMS stamp (Fig. 1c) and thus also reducing the complexity of the fabrication process. In this process, the SOI wafer with Si NRs (donor substrate) is brought into direct physical contact with the semi-cured PI thin film over the receiver substrate. A thin layer of partially cured PI is utilized to enhance the adhesion between NRs and receiver substrate during the printing process. As an immediate benefit, the direct roll printing approach leads to lower process steps, reduced complexity, shorter printing time, and lower fabrication cost compared with conventional transfer printing. Following the direct transfer printing of NRs, low-temperature steps (e.g., dielectric and metal deposition) were carried out to realize devices on flexible receiver substrates, as shown in Fig. 1d.

a Fabrication step of Si NRs carried out on the donor substrate with n+ selective doping followed by releasing the NRs from buried oxide (Box) layer as shown in SEM cross-sectional image (scale bar, 10 μm). b Conventional transfer printing steps using an elastomeric stamp (PDMS) with an optical image of each step (scale bar, 25 μm). c Direct roll printing of NRs from donor to the semi-cured PI substrate (scale bar, 25 μm). d Conventional microfabrication processing steps toward a final NRFET device (i.e., room temperature dielectric deposition, metallization, etc (scale bar, 100 μm)).

The semi-cured PI layer allows us to perform direct roll printing of NSs with enhanced transfer yield. However, this step could potentially make the printing process slow and pose challenges in terms of printing over different substrates. This is because, after direct transfer printing, the annealing of the coated PI layer is needed. To investigate this, we have printed Si NRs over various flexible substrates such as metal foils (e.g., Al, Cu, and Mg) and polymers (e.g., Kapton sheet, PET, and PI). The data is shown in Supplementary Fig. 2. Depending on the underlying substrate and its glass transition temperature, the curing time could vary from 2 h (for PI, Kapton, and metal foils) to 4 h (PET). Indeed, 2–4 h of curing makes the printing step slower, but this drawback could be overcome by using UV-cured polymers as an adhesive layer. UV curing can speed up the process42 and reduce the time duration of the entire printing process.

For high transfer yield in LAE, it is important to have good control over the shape, and geometrical configuration of the printed structures (high registration). To obtain the statistical data on registration, yield and to evaluate the quality of direct roll printed NRs, the morphological analysis was performed using SEM, optical microscopy, and AFM. It is to be noted that this statistical data is obtained for NRs printed over PI substrate. Figure 2 shows the images of released Si NRs, before and after the direct roll printing. Figure 2a shows an optical microscopy image of selectively doped Si NR arrays over donor substrate; the inset shows the magnified SEM image of a single Si NRs array in releasable form, prepared to allow direct retrieval onto the surface of PI substrate. The inset of Fig. 2a shows the suspended NRs are anchored at both edges (5 μm width at both sides and supported by the underlying 2 µm thick of Box layer) to maintain the correct alignment. Figure 2b shows the corresponding optical image of arrays of 70 nm thick Si NRs, directly transferred onto a target PI substrate using direct roll printing. The SEM image in the inset of Fig. 2b illustrates a defect-free transfer of NRs. From fig. 2a, b and supplementary Fig. 3, it is clear that the arrays of Si NRs with perfect registration were transferred over the PI substrate (separated by 930 μm in X-direction and ~990 μm Y-direction). These registration values perfectly match with the NRs on the donor wafer. A high registration quality of printed structures is critical for the high-performance LAE as poor registration may lead to poor control over device dimensions and hence greater variation in device-to-device performance17. The use of a viscoelastic soft stamp in conventional transfer printing may degrade the registration quality of the printed NSs43,44. For instance, periodic wavy/buckled structures formed spontaneously with specific amplitudes defined by the moduli of the materials and the thicknesses of the structures. This leads to little control over the geometries or the phases of the waves45. This is because of the mechanical properties of soft stamps such as PDMS. We studied this aspect using COMSOL simulations and noted that a 2 N compressive force on the PDMS surface to retrieve the NSs could introduce a lateral displacement of more than 1 µm in PDMS due to the shear strain (Supplementary Fig. 4). This means, during the retrieval step, the release of strain energy may lead to wavy/buckled structures and hence the misalignment of at least 1 µm. This misalignment is significant when we consider printed electronics in large areas. For example, this 1 µm misalignment from on a 1 cm stamp can become 10 µm on a 10 cm long substrate, which is fatal for the realization of electronic circuits on such areas, particularly when the device’s dimensions are smaller than the misalignment. If the channel length of a FET device is 1 µm, one can expect huge variations in electrical performance from device to device. Although controlled wavy/buckled structures could be used for the development of small-scale stretchable electronics but for LAE it is likely to lead to poor uniformity in device-to-device performance.

Optical images of (a) Si NR array on the donor wafer before printing (scale bar, 500 μm) with corresponding SEM image (inset) (scale bar, 25 μm). b Transferred Si NR arrays onto flexible receiver substrate (scale bar, 500 μm) with corresponding SEM image (inset) (scale bar, 25 μm). c, d Study of the yield based on presented direct printing approach (contact area of donor/receiver during direct roll printing ~2.25 cm2). e Atomic force microscopy (AFM) image of the surface of single Si NR (scan size 25 µm × 25 µm) on PI substrate. The figure also shows a high-resolution AFM scan (2 µm × 2 µm) to monitor the roughness of Si NRs. SEM cross-sectional images of anchored Si NR array after etching the Box layer with top view image of the anchor point (inset) (scale bar, 20 μm). f Gap anchor point = 55 µm. g Gap anchor point >55 µm.

The reliability and robustness of the presented printing approach were evaluated by the transfer yield of NRs from the donor to receiver substrate. High transfer yield (~100%) is desired for any practical application. To have a uniform and high printing yield over a large area, conformal contact between the semi-cured PI layer and Si NRs is needed for a direct roll printing approach. To achieve an excellent conformal contact and thus, the printing yield, dependency of applied force on transfer yield was evaluated. The contact force is one of the critical parameters that affect the final yield of the process. The optimization study with the applied force is shown in (Supplementary Fig. 5), where each single Si NR array consists of 9 NRs, the width and spacing between them are 5 µm, the length and thickness are 50 µm and 70 nm, respectively. The transfer yield results were obtained and characterized based on different applied forces from 2 to 12 N while the printing speed was fixed to 1 mm/s. As shown in this figure, the transfer yield increases with the increase in applied force and reaches 95% for the applied contact force of 12 N (the printed area was 2.25 cm2 chip). This observation is based on the data from 11 × 12 Si NR arrays. These results can be explained as higher forces lead to more conformal contact of NRs with the semi-cured PI, which in turn enhances the adhesive strength between them. Eventually, this helps to achieve a uniform and high transfer yield. The applied 12 N is close to the max loading capacity of the present roll printing system (load cells, motors). However, with further modifications of our roll printing setup, it would be possible to apply larger forces to further enhance the transfer yield.

It is important to note that the gap between the anchor points is also critical for higher transfer yield. To optimize the gap, we have performed etching of the Box layer for various time durations. The SEM images of the NRs anchored at two ends, with different etching duration of the Box layer, are shown in Fig. 2f, g). We observed that the transfer yield is almost zero when the gap between the anchor point is >55 µm. This is because, for larger gaps between anchor points, the suspended NRs touch the base of the silicon wafer and create a bond with the bulk substrate which eventually leads to broken ribbons or the ones that cannot be retrieved from the source substrate during direct roll printing.

Following the optimization study, large-area printing was performed using SOI donor substrate having a size of 3 × 3 = 9 cm2 (close to 2-inch wafer size) with an optimized roll printing parameter (12 N force @ 1 mm/s), as illustrated in the (Supplementary Fig. 6). By carefully optimizing the process (shown above), we managed to achieve highly uniform printing with ~95% transfer yield averaged over the printed large area. It is worth mentioning here that the present printing area is restricted only by the size of the roller and not the process itself. By increasing the roller size it will be possible to increase the print area. This marks a significant advantage over the conventional two-step transfer printing process, which usually shows a low printing yield for sub-100 nm thick NSs24. This is because the adhesion forces that are considered insignificant at the macro scale become dominant at the micro/nanoscale. As a result, releasing the micro-/nano structures from stamps has been a major challenge for a ‘pick-and-place’ assembly technique. Thereby, accuracy, yield, and throughput of the printing process are majorly compromised. As shown in Fig. 2a, b, the probability for the misalignment of printed structures during the direct roll printing process is low, as viscoelastic stamps are not involved in this process. By retaining the NRs alignment, the variation in NR density across the substrate and the overlapping of adjacent NRs are reduced, and eventually, the device-to-device uniformity is improved. Further, it leads to a higher transfer yield of the NSs (Fig. 2c, d). Table 1 summarizes these results along with a comparison with the conventional transfer printing process.

Finally, we have evaluated the surface topography of the printed NRs. It is worth mentioning that the use of an intermediate stamp in conventional transfer printing may leave residues on the surface of the NSs due to high bonding strength and strong adhesion between PDMS stamp and native oxide (SiO2) layer46,47. The post-surface treatment is normally needed to remove the residues will also add few extra fabrication steps and increase the process complexity. The removal of PDMS residues typically involves plasma treatment or wet etching which could damage or introduce roughness over the NRs of sub-100 nm thickness. The elastomeric stamp residues (non-conducting material) strongly influence the electrical performance and reliability of nanostructures-based electronics since the interfacial contact between the nanostructures and deposited metal contacts are not desirable. Therefore, there is a possibility of performance degradation in the case of traditional transfer printing. Surface chemistry technique has also been demonstrated by depositing/sputtering thin SiO2 layer on the top of the target NS to enhance stamp/NS adhesion48. Such steps increase complexities in the printing process and produce surface contamination on top of printed NSs, which may subsequently lead to variation in terms of device performance. The surface quality of transferred Si NRs on receiving substrate (PI) was investigated by AFM surface morphology. Figure 2e shows an AFM image (25 µm × 25 µm) of a single Si NR array directly transferred on PI substrate. The surface topography of the printed NRs was found to be free from polymer residues/contamination. Further, the surface roughness of the printed NR was calculated using a high-resolution AFM image (2 µm × 2 µm), as shown in Fig. 2e. The calculated root means square (RMS) roughness of transferred ribbons is 0.41 nm. It can be seen from Fig. 2e that sidewalls of ultrathin NS are formed on PI substrate without any polymer residues, unlike other reported approaches such as glue-assisted transfer printing25,49,50. The presence of residues may lead to surface contamination and defects and failures in transferred NSs, eventually degrading the device performance51.

Direct roll transfer printed Si nanoribbon-based transistors

The direct roll printed Si NRs were used to fabricate the top-gated field-effect transistors (FETs) on the flexible (PI) substrate. The top-gate FET geometry is preferred here because the top-gate electrode could be wrapped around the nanostructure to effectively control the charge transport. The gate dielectric needed for the realization of top-gated FET on flexible substrates can be deposited at room temperature (RT). This gate dielectric, conformally covered over the nanostructure, should have minimal defect density at the semiconductor/dielectric interface and provide a large capacitance per unit area. In this regard, the inductively coupled plasma-chemical vapor deposition (ICP-CVD) technique offers a unique advantage as it allows high-quality dielectric (SiOx, SiNx, etc.) deposition at RT without any plasma related harmful effects7. We have used RT deposited SiNx as our top-gate dielectric material as it has been widely explored gate dielectric material for III–V devices and oxide thin-film transistors exhibiting good device performance. Figure 3a shows the schematic and optical images of fabricated top-gated Si NR-FET devices (channel length (L) and width (W) ∼5 μm and ∼45 μm (9 NRs of 5 μm), respectively) and its transfer and output scans. The cross-section and optical image of the Si-NRFET are shown in Fig. 3a. The output characteristics (VDS–IDS) of Si NR-FET in Fig. 3b show the varying gate bias (VGS) from 0 V to 4 V with the step of 1 V by sweeping drain-source bias (VDS) from –3 V to +3 V (only positive VDS voltages illustrated). As VGS increases towards positive voltage, the corresponding drain current (IDS) is also increased, confirming that the device is n-channel. Due to the n+ doping and low energetic contact barriers, the variation of IDS with VDS is linear without any inflection point at low-VDS region (VDS ≤∼0.1 V). The transfer characteristics (IDS–VGS) of Si NR-FET with VDS of 0.1 V were obtained by varying VGS from −10 to 10 V (Fig. 3c). In terms of the electrical performance of the NR-FET, the main parameters to consider are: on-state (Ion), off-state current (Ioff), current on/off ratio (Ion/Ioff), and effective mobility (\(\mu _{{\mathrm{eff}}}\)), and subthreshold slope (SS)52. The logarithmic plot of the transfer curve in Fig. 3c revealed an Ion (∼60 μA)/Ioff (<0.1 nA) current ratio of >106 suggesting an excellent gate-channel control. Figure 3d shows the transfer characteristics of Si NRFET at various values of VDS. It is worth noting from Fig. 3d that the threshold voltage (Vth) remains constant with applied voltage VDS, indicating high stability charge transport behavior under different voltages. The field-effect mobility of the device was extracted based on the conventional MOSFET model in the linear regime7 as given by:

where L and W are the gate length and width of the Si NRFET, respectively, gd is the drain conductance, Cox is the oxide capacitance, VGS is the gate-source voltage and Vth is the threshold voltage. The thickness of the gate is negligible since, the thickness of active NRs is relatively low (∼70 nm), the effective width is 45 μm (9 ribbons × 5 μm each). The threshold voltage (Vth) measured through extrapolation in the linear region of Si NRFET is ~0.4 V. The drain conductance gd is extracted using the following equation:

a Schematic cross-sectional view of the Si NRFET device (scale bar, 50 μm). b Output characteristics of Si-NRFET. c Transfer characteristics (IDS–VGS) of Si NRFET with VDS = 0.1 V in logarithmic and linear scales. d Transfer characteristics (IDS–VGS) of Si NRFET with VDS varying from 0.1 V to 1 V with the step of 0.1 V.

The drain conductance was estimated from the output characteristics, at VDS = 30 mV. The estimated drain conductance extracted by numerically differentiating the drain current with reference to the drain-source voltage under planar condition is 47 μS. Similarly, from transfer characteristics, the peak transconductance was estimated by using the following expression:

The extracted effective mobility (\(\mu _{{\mathrm{eff}}}\)) is ~631 cm2/Vs. The subthreshold slope (SS) was extracted from the logarithmic transfer characteristics by numerical differentiation based on the equation:

The extracted subthreshold slope is ~1000 mV/decade (using the semi-logarithmic plot of the transfer scan). Table 2 compares the extracted electrical parameters of Si NRFETs fabricated using NRs transferred through the direct roll printing process and those using other transfer printing techniques. It can be seen that the extracted mobility compares well with most of the state-of-the-art Si NR-based devices and is higher than nanomeshed Si nanomembrane-based FET devices53. The µeff value is marginally lower than the previously reported value (680 cm2/Vs) employing self-assembled nanodielectrics (SAND) dielectric (15 nm thick). However, the process to deposit SAND is time-consuming and requires additional efforts in terms of solution processing in controlled ambient and hence may not be suitable for scalable high throughput processing7. Instead with the deposition of a thinner SiNx dielectric, the mobility of roll printed devices could be enhanced further. The extracted subthreshold slope (SS) value is significantly higher for the roll printed devices. It may be noted that, in the absence of surface anomalies, the theoretical limit of SS is around 60 mV/dec. The calculated subthreshold swing is ~8 times higher than one of the best examples in literature (∼120 mV/dec) using SAND54, and ∼16 times larger than the theoretical limit in CMOS. As mentioned above, a thin gate dielectric could improve the gate control over the channel and thus reduce the SS values close to the state of the art.

In nanomaterial-based FETs, working in depletion/accumulation mode, the dielectric/semiconductor interface quality plays a dominant role in defining the transistor performance and electric-bias stability. To this end, we quantified the occupied trap charge density at the SiNx/Si NR interface (Dit) using the following relation55,56:

To calculate the hysteresis (i.e., ΔVth), the forward and reverse transfer scans were performed between −5 VGS to +10 VGS. As shown in Supplementary Fig. 7, negligible hysteresis (0.4 V) is observed for the NRFETs. Using the hysteresis data, the Si NRFET showed a Dit value of 1.7 × 1011/cm2 (ΔVth = 0.4 V, and Cox = 7 × 10−4 F/m2). The estimated value of Dit at the SiNx/Si NR interface is an order of magnitude less than the SiO2−semiconductor interface for nanomaterial-based FETs56,57.

Electromechanical characterizations of Si NRFETs

The mechanical robustness and device stability of the fabricated flexible Si NRFETs were evaluated under different bending conditions. The electrical characterization results under bending are shown in Fig. 4. The device was subjected to tension and compression by mounting it onto 3D printed convex and concave structures. For both bending types, the radius of bending curvature was 40 mm, as shown in the inset of Fig. 4a. The transfer and output characteristics under bending are shown in Fig. 4a, b, respectively. As can be seen, the device showed slight variation in Ion while Vth, SS, and other device parameters were largely remained unchanged. The effect of mechanical stress on Ion of NRFET under compressive and tensile bending cycle was investigated with VGS = 5 V and VDS = 3 V for five randomly chosen NRFET devices (Fig. 4c). The strain resulting from mechanical bending is known to affect the semiconducting material’s band structure and hence the effective mass and the mobility of the charge carriers14,58. The change in mobility has a direct effect on the source current of the transistor. As expected, a tensile bending strain led to a slight increase in the IDS, whereas a compressive bending led to a decrease in IDS7. To inspect the mechanical robustness the fabricated NRFETs were subjected to 100 bending cycles and corresponding drain currents are illustrated in Fig. 4d. The peak values of drain current were obtained under planar conditions after every 10 cycles of compressive and tensile bending (Rc = 40 mm). As can be seen from this set of data, the Ion showed a near stable response with repeated bending. The minor variation in the electrical properties during cyclic bending is attributed to two main factors. First, the mechanical bending, which results in the change of the effective mass and hence the mobility of the charge carrier, as mentioned above15,58. The second is the delamination of device layers including metal contacts. These can be mitigated and addressed by adding an encapsulation layer on top of the final device/circuits. Such a layout has been demonstrated in the past with a thin layer of the polymer as an encapsulant (usually the same material as substrate) on top of Si NRFET. Such a configuration enables high flexibility along with stable electrical properties by bringing the devices to the neutral mechanical plane and prevents the device from experiencing any strain-induced variations caused during cyclic bending. This could enhance the bendability, device stability and also resolve the slight variation of the electrical properties under bending conditions59.

a Measured transfer characteristic (IDS vs. VGS) of Si-NRFET under planar, tensile, and compressive bending conditions. b Output characteristics of Si-NRFET at planar, and under bending conditions (Rc = 40 mm)). c Variation of the on-state current at VGS = 5 V at compressive and tensile bending cycles. d Variation of the drain current at planar condition during compressive and tensile bending cycles at VDS = 3 V, VGS = 5 V.

In summary, we have presented a simple, efficient, and R2R compatible direct roll printing technique to transfer silicon nanoribbons (Si NRs) directly onto the flexible PI substrate. Avoiding the use of elastomeric transfer stamps, this innovative printing method minimizes the process complexity and enhances the printing yield and registration accuracy. The high transfer yield of ~95% with perfect registration has been demonstrated. The printed NRs were employed as active channel material to obtain high-performance flexible FETs and the ICP process was adapted for the deposition of high-quality dielectric (SiNx) at RT. The Si NRFETs showed excellent performance with mobility (>630 cm2/Vs) and current on/off ratio (~106) at par with devices reported previously using the traditional transfer printing process. Furthermore, excellent robustness under large bending deformation was illustrated. The excellent electrical characteristic of NRFETs after 100 cycles of bending, makes them an excellent candidate for next-generation high-performance flexible LAE electronics. The presented approach could also be used for printing ultrathin micro/nanostructures based on other high mobility materials such as GaAs, GaN, etc.

Methods

Fabrication of Si NR using SOI wafer

Si-NRs were defined on SOI wafers (donor substrate) using standard photolithography and etching process (top-down method). The commercial SOI wafer having 70 nm top Si (100) layer over 2 μm of buried oxide, supported by 600 μm bulk Si was selected as the donor substrate to fabricate NRs with same dimensions (i.e., thickness, length, and width). The SOI wafers were chemically cleaned to eliminate the surface contaminants by ultrasonication in acetone, isopropyl alcohol (IPA), and deionized (DI) water. Si NRs with a width of 5 μm and length 55 μm were defined by a mask designed with MA/BA6 mask aligner from Suss MicroTec. The sample was spin-coated S1805 photoresist (4000 rpm for 30 s), followed by soft baking at 115 °C for 60 s. At this stage, samples were exposed to UV sources, and patterns were developed by using Microposit MF-319 developer. The exposed Si was etched in a solution of nitric acid (HNO3), ammonium fluoride (NH4F), and water (H2O) in a volume ratio of 126:60:5 (HNO3: H2O: NH4F). The etchant solution has an etch rate of ∼150 nm/min. The sample was etched for 2 min to ensure that Si is completely etched away. The photoresist mask, which was used to protect the Si nanoribbons, was dissolved in acetone and isopropanol (IPA) with ultrasonic agitation, then abundantly rinsed with de-ionized (DI) water and dried using a stream of nitrogen flow to lead to Si ribbons structure with 70 nm thickness.

Doping of source and drain region of transistors

The selective doping of the NRs was carried out using spin-on dopant (SOD) through the diffusion of phosphorus (Filmtronics, P451) at 1050 °C and ohmic contacts were created by masking channel with SiO2. The SiO2 diffusion barrier mask layer (thickness ∼150 nm) was deposited on the top of the wafer by using the plasma-enhanced chemical vapor deposition (PECVD). The source and drain regions were patterned by using the designed mask and conventional photolithography. The resist served as a mask for selective dry etch process with a CH3/Ar plasma using Reactive Ion Etching (RIE) system (40 sccm CH3/Ar flow with a chamber base pressure of 30 mTorr, 200 W RF power). This process was carried out to etch the exposed areas of the oxide mask to open the active regions of the source and drain. The doping concentration, measured using 4-point-probe, was found to be higher than 1 × 10 19 cm–3. The remaining oxide mask layer was removed with a buffered oxide etch (BOE 5:1). The etching of Box was carried by hydrofluoric acid (HF) solution to obtain the suspended nanoribbons with delicate anchor points at both ends.

Direct printing of Si NR

Custom-made direct roll printing technology was used to transfer the fabricated Si NRs to the receiving flexible substrates including metal foils (e.g., Al, Cu, and Mg) and polymers (e.g., Kapton sheet, PET, and PI). In this approach, all the steps are carried out at low temperatures to complete the device fabrication. For a detailed statistical data study and device fabrication, PI foil (thickness of 25 μm) was used as a receiver substrate. The process details are as follows: an adhesion promoter was applied to the commercial PI substrate prior to printing. An ultrathin layer of PI-2545 precursor (from HD microsystems) was spun over the PI sheet at 2000 rpm for 60 s (thickness ∼1.0 µm). The adhesion between the receiver substrate and the PI layer was promoted by coating (VM652 from Microsystems). The spun PI layer (partially cured at 120 °C for 2 mins) provided an ultrathin layer of adhesive, during direct roll printing of Si NR arrays from the SOI wafer to the PI substrate. The PI substrate is subsequently cured at 250 °C for 2 h to ensure solidification through the thickness of the thin film and to enhance the adhesion of the NRs on the receiver substrate. A reliable direct roll printing depends critically on the conformal contact at the interface of the donor/interfacial adhesion of semi-cured PI on the receiver substrate.

Silicon nanoribbon field-effect transistor fabrication

The fabrication of NRFETs was completed by the room temperature deposition of high-quality gate dielectric (SiNx, 100 nm) on the printed NRs by using ICP-CVD system followed by metal deposition (Ti (10 nm)/Au (90 nm)) for gate, source, and drain using e-beam evaporation method and lift-off. A short dip in diluted HF was performed prior to metallization to remove the native oxide on the active Si regions, source, and drain (S/D).

Morphological and electrical characterizations

The structure and surface morphology of direct printed NRs were studied through Scanning electron Microscopy (SEM) of Hitachi SU824 and Atomic Force Microscope (Dimension Icon AFM from Bruker Nano). Electrical characterizations of fabricated Si NRs based field-effect-transistor (Si-NRFET) on the flexible (PI) substrate were performed in the ambient environment using Cascade Micro-tech Auto-guard probe station interfaced to a semiconductor parameter analyzer (B1500A, Agilent).

Data availability

The datasets generated and analyzed during this study are available from the corresponding author on reasonable request.

References

Song, E., Li, J., Won, S. M., Bai, W. & Rogers, J. A. Materials for flexible bioelectronic systems as chronic neural interfaces. Nat. Mater. 19, 590–603 (2020).

Ling, Y. et al. Disruptive, soft, wearable sensors. Adv. Mater. 32, 1904664 (2020).

Someya, T. & Amagai, M. Toward a new generation of smart skins. Nat. Biotechnol. 37, 382–388 (2019).

Dahiya, R. et al. Large-area soft e-skin: the challenges beyond sensor designs. Proc. IEEE 107, 2016–2033 (2019).

Dahiya, R., Akinwande, D. & Chang, J. S. Flexible electronic skin: from humanoids to humans. Proc. IEEE 107, 2011–2015 (2019).

Escobedo, P., Bhattacharjee, M., Nikbakhtnasrabadi, F. & Dahiya, R. Smart bandage with wireless strain and temperature sensors and battery-less NFC tag. IEEE Internet Things J. 8, 5093–5100 (2021).

Zumeit, A., Navaraj, W. T., Shakthivel, D. & Dahiya, R. Nanoribbon-based flexible high-performance transistors fabricated at room temperature. Adv. Electron. Mater. 6, 1901023 (2020).

Escobedo, P., N., M., Shakthivel, D., Navaraj, W. T. & Dahiya, R. Energy generating electronic skin with intrinsic touch sensing. IEEE Trans. Robot. 8, 5093–5100 (2021).

Ozioko, O., Karipoth, P., Hersh, M. & Dahiya, R. Wearable assistive tactile communication interface based on integrated touch sensors and actuators. IEEE Trans. Neural Syst. Rehab. Eng. 28, 1344–1352 (2020).

Ozioko, O. et al. SensAct: the soft and squishy tactile sensor with integrated flexible actuator. Adv. Intell. Syst. 3, 1900145 (2021).

Ray, T. R. et al. Bio-integrated wearable systems: a comprehensive review. Chem. Rev. 119, 5461–5533 (2019).

Niu, S. et al. A wireless body area sensor network based on stretchable passive tags. Nat. Electron. 2, 361–368 (2019).

Seo, J.-H., Zhang, K., Kim, M., Zhou, W. & Ma, Z. High-performance flexible BiCMOS electronics based on single-crystal Si nanomembrane. npj Flex. Electron 1, 1–7 (2017).

Navaraj, W. T., Gupta, S., Lorenzelli, L. & Dahiya, R. Wafer scale transfer of ultrathin silicon chips on flexible substrates for high performance bendable systems. Adv. Electron. Mater. 4, 1700277 (2018).

Gupta, S., Navaraj, W. T., Lorenzelli, L. & Dahiya, R. Ultra-thin chips for high-performance flexible electronics. npj Flex. Electron 2, 8 (2018).

Wang, C. et al. Programmable and scalable transfer printing with high reliability and efficiency for flexible inorganic electronics. Sci. Adv. 6, eabb2393 (2020).

Dahiya, A. S. et al. High-performance printed electronics based on inorganic semiconducting nano to chip scale structures. Nano Converg. 7, 33 (2020).

Bian, J. et al. Laser transfer, printing, and assembly techniques for flexible electronics. Adv. Electron. Mater. 5, 1800900 (2019).

Yogeswaran, N., Hosseini, E. S. & Dahiya, R. Graphene based low voltage field effect transistor coupled with biodegradable piezoelectric material based dynamic pressure sensor. ACS Appl. Mater. Interfaces 12, 54035–54040 (2020).

Liu, F., Navaraj, W. T., Yogeswaran, N., Gregory, D. H. & Dahiya, R. van der Waals contact engineering of graphene field-effect transistors for large-area flexible electronics. ACS Nano 13, 3257–3268 (2019).

Núñez, C. G. et al. Heterogeneous integration of contact-printed semiconductor nanowires for high-performance devices on large areas. Microsyst. Nanoeng. 4, 1–15 (2018).

Rogers, J., Lagally, M. & Nuzzo, R. Synthesis, assembly and applications of semiconductor nanomembranes. Nature 477, 45–53 (2011).

Yoon, J. et al. GaAs photovoltaics and optoelectronics using releasable multilayer epitaxial assemblies. Nature 465, 329–333 (2010).

Kim-Lee, H.-J., Carlson, A., Grierson, D. S., Rogers, J. A. & Turner, K. T. Interface mechanics of adhesiveless microtransfer printing processes. J. Appl. Phys. 115, 143513 (2014).

Kim, T.-i et al. Thin film receiver materials for deterministic assembly by transfer printing. Chem. Mater. 26, 3502–3507 (2014).

Jeong, J. W. et al. High-resolution nanotransfer printing applicable to diverse surfaces via interface-targeted adhesion switching. Nat. Commun. 5, 1–12 (2014).

Yoo, B., Cho, S., Seo, S. & Lee, J. Elastomeric angled microflaps with reversible adhesion for transfer-printing semiconductor membranes onto dry surfaces. ACS Appl. Mater. Interfaces 6, 19247–19253 (2014).

Kim, S. et al. Microstructured elastomeric surfaces with reversible adhesion and examples of their use in deterministic assembly by transfer printing. PNAS 107, 17095–17100 (2010).

Yan, Z. et al. Thermal release transfer printing for stretchable conformal bioelectronics. Adv. Sci. 4, 1700251 (2017).

Feng, X. et al. A finite-deformation mechanics theory for kinetically controlled transfer printing. J. Appl. Mech. 80, 061023 (2013).

Meitl, M. A. et al. Transfer printing by kinetic control of adhesion to an elastomeric stamp. Nat. Mater. 5, 33–38 (2006).

Linghu, C. et al. Rapidly tunable and highly reversible bio-inspired dry adhesion for transfer printing in air and a vacuum. Soft Matter 15, 30–37 (2019).

Huang, Y. et al. Direct laser writing-based programmable transfer printing via bioinspired shape memory reversible adhesive. ACS Appl. Mater. Inter. 8, 35628–35633 (2016).

Luo, H. et al. Laser-driven programmable non-contact transfer printing of objects onto arbitrary receivers via an active elastomeric microstructured stamp. Natl Sci. Rev. 7, 296–304 (2020).

Luo, H., Wang, S., Wang, C., Linghu, C. & Song, J. Thermal controlled tunable adhesive for deterministic assembly by transfer printing. Adv. Funct. Mater. 31, 2010297 (2021).

Liu, F. et al. A flexible chip with embedded intelligence. Nat. Electron. 3, 358–359 (2020).

Wu, W. Inorganic nanomaterials for printed electronics: a review. Nanoscale 9, 7342–7372 (2017).

Yoder, M. A., Yan, Z., Han, M., Rogers, J. A. & Nuzzo, R. G. Semiconductor nanomembrane materials for high-performance soft electronic devices. J. Am. Chem. 140, 9001–9019 (2018).

Yu, K. J., Yan, Z., Han, M. & Rogers, J. A. Inorganic semiconducting materials for flexible and stretchable electronics. npj Flex. Electron 1, 1–14 (2017).

Khan, S., Lorenzelli, L. & Dahiya, R. Flexible MISFET devices from transfer printed Si microwires and spray coating. IEEE J. Electron Dev. 4, 189–196 (2016).

Linghu, C., Zhang, S., Wang, C. & Song, J. Transfer printing techniques for flexible and stretchable inorganic electronics. npj Flex. Electron 2, 26 (2018).

Mendes‐Felipe, C., Oliveira, J., Etxebarria, I., Vilas‐Vilela, J. L. & Lanceros‐Mendez, S. State‐of‐the‐art and future challenges of UV curable polymer‐based smart materials for printing technologies. Adv. Mater. Technol. 4, 1800618 (2019).

Wu, J., Dan, Q. & Liu, S. Effect of viscoelasticity of PDMS on transfer printing. In 2015 16th International Conference on Electronic Packaging Technology (ICEPT). 759–764 (IEEE, 2015).

Cheng, H. et al. A viscoelastic model for the rate effect in transfer printing. J. Appl. Mech. 80, 041019 (2013).

Sun, Y., Choi, W. M., Jiang, H., Huang, Y. Y. & Rogers, J. A. Controlled buckling of semiconductor nanoribbons for stretchable electronics. Nat. Nanotechnol. 1, 201–207 (2006).

Baca, A. J. et al. Printable single‐crystal silicon micro/nanoscale ribbons, platelets and bars generated from bulk wafers. Adv. Funct. Mater. 17, 3051–3062 (2007).

Duffy, D. C., McDonald, J. C., Schueller, O. J. & Whitesides, G. M. Rapid prototyping of microfluidic systems in poly (dimethylsiloxane). Anal. Chem. 70, 4974–4984 (1998).

Sun, Y. et al. Photolithographic route to the fabrication of micro/nanowires of III–V semiconductors. Adv. Funct. Mater. 15, 30–40 (2005).

Lee, K. J. et al. Large‐area, selective transfer of microstructured silicon: a printing‐based approach to high‐performance thin‐film transistors supported on flexible substrates. Adv. Mater. 17, 2332–2336 (2005).

Sun, Y. & Rogers, J. A. Fabricating semiconductor nano/microwires and transfer printing ordered arrays of them onto plastic substrates. Nano Lett. 4, 1953–1959 (2004).

Dahiya, R., Gottardi, G. & Laidani, N. PDMS residues-free micro/macrostructures on flexible substrates. Microelectron. Eng. 136, 57–62 (2015).

Dahiya, A. S., Sporea, R., Poulin-Vittrant, G. & Alquier, D. Stability evaluation of ZnO nanosheet based source-gated transistors. Sci. Rep. 9, 1–11 (2019).

Han, X. et al. Nanomeshed Si nanomembranes. npj Flex. Electron 3, 1–8 (2019).

Kim, H.-S. et al. Self-assembled nanodielectrics and silicon nanomembranes for low voltage, flexible transistors, and logic gates on plastic substrates. Appl. Phys. Lett. 95, 183504 (2009).

Dahiya, A. S. et al. Flexible organic/inorganic hybrid field-effect transistors with high performance and operational stability. ACS Appl. Mater. Inter. 9, 573–584 (2017).

Choi, K. et al. Trap density probing on top-gate MoS2 nanosheet field-effect transistors by photo-excited charge collection spectroscopy. Nanoscale 7, 5617–5623 (2015).

Paska, Y. & Haick, H. Interactive effect of hysteresis and surface chemistry on gated silicon nanowire gas sensors. ACS Appl. Mater. Inter. 4, 2604–2617 (2012).

Heidari, H., Wacker, N. & Dahiya, R. Bending induced electrical response variations in ultra-thin flexible chips and device modeling. Appl. Phys. Rev. 4, 031101 (2017).

Kim, D.-H. et al. Stretchable and foldable silicon integrated circuits. Science 320, 507–511 (2008).

Cho, S., Kim, N., Song, K. & Lee, J. Adhesiveless transfer printing of ultrathin microscale semiconductor materials by controlling the bending radius of an elastomeric stamp. Langmuir 32, 7951–7957 (2016).

Eisenhaure, J. D. et al. The use of shape memory polymers for microassembly by transfer printing. J. Microelectromech. S 23, 1012–1014 (2014).

Saeidpourazar, R. et al. Laser-driven micro transfer placement of prefabricated microstructures. J. Microelectromech. Syst. 21, 1049–1058 (2012).

Menard, E., Nuzzo, R. G. & Rogers, J. A. Bendable single crystal silicon thin film transistors formed by printing on plastic substrates. Appl. Phys. Lett. 86, 093507 (2005).

Seo, J.-H. et al. Microwave flexible transistors on cellulose nanofibrillated fiber substrates. Appl. Phys. Lett. 106, 262101 (2015).

Mack, S., Meitl, M., Baca, A., Zhu, Z.-T. & Rogers, J. Mechanically flexible thin-film transistors that use ultrathin ribbons of silicon derived from bulk wafers. Appl. Phys. Lett. 88, 213101 (2006).

Acknowledgements

This work was supported in part by Engineering and Physical Sciences Research Council (EPSRC) through Engineering Fellowship for Growth (EP/R029644/1) and Heteroprint Programme Grant (EP/R03480X/1).

Author information

Authors and Affiliations

Contributions

A.Z. and R.D. conceived the idea. A.Z. performed the transistor device fabrication, characterizations and wrote the manuscript. A.S.D. assisted in device electrical characterizations and data analysis. A.C. designed and built the roll printing set-up and performed COMSOL simulations. D.S., A.S.D., and R.D. contributed to the writing of the manuscript. R.D. provided overall supervision of the work. All authors have read and approved the final manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Zumeit, A., Dahiya, A.S., Christou, A. et al. Direct roll transfer printed silicon nanoribbon arrays based high-performance flexible electronics. npj Flex Electron 5, 18 (2021). https://doi.org/10.1038/s41528-021-00116-w

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41528-021-00116-w