# nature communications

Article

https://doi.org/10.1038/s41467-023-39033-z

# Thermally stable threshold selector based on CuAg alloy for energy-efficient memory and neuromorphic computing applications

Received: 31 May 2022

Accepted: 25 May 2023

Published online: 06 June 2023

Check for updates

Xi Zhou  $\mathbb{O}^{1,2,3,7}$ , Liang Zhao  $\mathbb{O}^{2,4,7} \boxtimes$ , Chu Yan<sup>2</sup>, Weili Zhen<sup>5</sup>, Yinyue Lin<sup>1,3</sup>, Le Li<sup>1,3</sup>, Guanlin Du<sup>1,3</sup>, Linfeng Lu<sup>1,3</sup>, Shan-Ting Zhang<sup>1,3,6</sup>, Zhichao Lu<sup>4</sup> & Dongdong Li  $\mathbb{O}^{1,3,6} \boxtimes$

As a promising candidate for high-density data storage and neuromorphic computing, cross-point memory arrays provide a platform to overcome the von Neumann bottleneck and accelerate neural network computation. In order to suppress the sneak-path current problem that limits their scalability and read accuracy, a two-terminal selector can be integrated at each cross-point to form the one-selector-one-memristor (1S1R) stack. In this work, we demonstrate a CuAg alloy-based, thermally stable and electroforming-free selector device with tunable threshold voltage and over 7 orders of magnitude ON/OFF ratio. A vertically stacked  $64 \times 64$  1S1R cross-point array is further implemented by integrating the selector with SiO<sub>2</sub>-based memristors. The 1S1R devices exhibit extremely low leakage currents and proper switching characteristics, which are suitable for both storage class memory and synaptic weight storage. Finally, a selector-based leaky integrate-and-fire neuron is designed and experimentally implemented, which expands the application prospect of CuAg alloy selectors from synapses to neurons.

In the era of artificial intelligence (AI) and carbon neutrality, the demand for energy-efficient computing systems capable of solving data-intensive computing tasks is surging rapidly. For example, state-of-the-art machine-learning models such as Generative Pre-trained Transformer-3<sup>1</sup> or switch transformers<sup>2</sup> can easily incorporate multiple billions of computing parameters. Conventional computing hardware based on von Neumann architecture experiences major difficulty processing such data-centric workloads, primarily due to the bottle-neck of data transfer between the processor and the memory blocks in these systems (also called the "memory wall" problem)<sup>3</sup>.

In order to break the memory wall and achieve energy-saving green AI, the design philosophy of compute-in-memory (CIM) has attracted significant interest<sup>4–7</sup>. Such non-vonNeumann computing systems are often realized with emerging memory technologies such as memristors<sup>5,8</sup>, phase change memories<sup>9–11</sup>, ferroelectric memories<sup>12</sup> or magnetic memories<sup>13</sup>. In particular, CIM chip based on memristors (or resistive randomaccess memory, RRAM) is one of the most widely studied candidates due to its advantages of low-power operation, low-cost manufacturing and compatibility with complementary metal oxide semiconductor (CMOS) technology<sup>14–16</sup>. In order to achieve RRAM-based CIM with high storage capacity, crosspoint array is a favorable scenario in terms of unit cell area (-4 $F^2$ , where *F* is the minimum feature size)<sup>6,17</sup>. However, the cross-point arrays of 2-terminal memory devices typically suffer from the

<sup>1</sup>The Interdisciplinary Research Center, Shanghai Advanced Research Institute, Chinese Academy of Sciences, 99 Haike Road, Zhangjiang Hi-Tech Park, 201210 Pudong, Shanghai, China. <sup>2</sup>College of Information Science and Electronic Engineering, Zhejiang University, 38 Zheda Road, 310007 Hangzhou, China. <sup>3</sup>School of Microelectronics, University of Chinese Academy of Sciences, 19 Yuquan Road, 100049 Beijing, China. <sup>4</sup>Hefei Reliance Memory Ltd., Bldg. F4-11F, Innovation Industrial Park Phase II, 230088 Hefei, China. <sup>5</sup>High Magnetic Field Laboratory, Chinese Academy of Sciences, 230031 Hefei, China. <sup>6</sup>Zhangjiang Laboratory, 100 Haike Road, Zhangjiang Hi-Tech Park, 201210 Pudong, Shanghai, China. <sup>7</sup>These authors contributed equally: Xi Zhou, Liang Zhao.

sneak-path current problem, which significantly limits the feasible array size<sup>18-20</sup>.

The one-selector-one-memristor (1S1R) architecture, as a general scheme for high-density cross-point memory arrays, is able to suppress the sneak-path currents while improving the storage density<sup>6,21-25</sup>. An ideal selector for cross-point arrays features a small leakage current in the OFF state, sufficiently low resistance in the ON state, steep switching slope (SS) as well as tunable threshold voltage  $(V_{\rm th})$  that can match the memristors for joint operations<sup>26</sup>. As of today, selector devices based on insulator-metal transition (IMT)<sup>27,28</sup>, ovonic threshold switching (OTS)<sup>29,30</sup>, Cu-containing mixed-ionicelectronic conduction (MIEC)<sup>31,32</sup> and metal-filament-based threshold switching<sup>33,34</sup> have been considered for 1S1R integration. The IMT selectors with NbOx or VO2 switching layer do not require electroforming but have relatively high leakage currents and are susceptible to ambient temperature change, making it difficult to achieve large array operations<sup>27,28</sup>. OTS selectors also exhibit limited selectivity (~10<sup>3</sup>), and their high-temperature stability for backend-of-line (BEOL) integration is yet to be demonstrated<sup>29,30</sup>. MIEC-based selectors possess a high ON/OFF ratio and promising integration potential but exhibit relatively gradual SS<sup>31,32</sup>. Finally, metal-filament selectors have sufficiently small leakage currents and abrupt switching but often lack stability under high-temperature annealing<sup>35</sup>. In particular, Ag-based metal-filament selectors suffer from the self-agglomeration of Ag under BEOL thermal budget<sup>36,37</sup>, whereas Cu-based selectors typically require higher electroforming voltages before normal operations<sup>34</sup>. Therefore, new selector technology with hightemperature stability, electroforming-free feature, steep SS and suitable ON and OFF currents is highly desired.

Furthermore, selectors and 1S1R arrays have potential applications in neuromorphic computing, which adopts certain features of the biological neural systems to accelerate processing and mimic the human brain. For example, spiking neural networks (SNN)<sup>16,38</sup> and Hopfield neural networks (HNN)<sup>5,39</sup> based on memristor crossbars have been widely explored. SNN uses pulses to encode input information which mimics the working pattern of the brain, potentially offering better energy efficiency for AI computing tasks<sup>9</sup>. HNN based on memristors has been explored for applications such as associative memory<sup>39</sup>, pattern recognition<sup>40</sup> and solution of non-deterministic polynomial-time-hard problems5. However, for practical SNN/HNN applications, large cross-point arrays (e.g.,  $64 \times 64$  or larger<sup>5,41</sup>) are desired, which share the same sneak-path current problem as crosspoint memories, i.e., the initial weight data cannot be properly programmed into large arrays without selectors (See "Methods" and Supplementary Fig. 1 for array simulations)<sup>42</sup>. In this regard, thermally stable selectors with high selectivity (>106) are necessary but are rarely demonstrated in the form of large 1S1R arrays due to integration challenges<sup>43</sup>. Also, selector devices are solely utilized to implement the synaptic functions so far, while the volatile and hysteresis nature of selector switching is inherently suitable for implementing oscillatory neurons9,44.

In this work, we demonstrate for the first time that copper-silver (CuAg) alloy as an electrode material of selectors exhibits superior thermal stability (400 °C/1 h) compared to either Ag or Cu electrodes, making it compatible with CMOS BEOL processing. The high ON current, large ON/OFF ratio (>10<sup>7</sup>), electroforming-free feature and adjustable  $V_{th}$  of the proposed CuAg/SiO<sub>2</sub>/CuAg selector confirm its feasibility for large 1S1R cross-point arrays. Subsequently, a functional 64 × 64 1S1R cross-point array is experimentally demonstrated by vertically integrating the CuAg/SiO<sub>2</sub>/CuAg selector with Pt/SiO<sub>2</sub>/TiN RRAM, exhibiting significant suppression of sneak-path currents and enhanced computational accuracy as synapses. Furthermore, we demonstrate that the proposed selector can be turned into a compact leaky integrate-and-fire (LIF) neuron by simply adding one resistor and one capacitor in parallel, which is a rigorous physical analog of the LIF

neuron model. These results suggest that the CuAg alloy-based selector is a promising and reliable new candidate for cross-point memory and neuromorphic computing applications.

#### **Results and discussion**

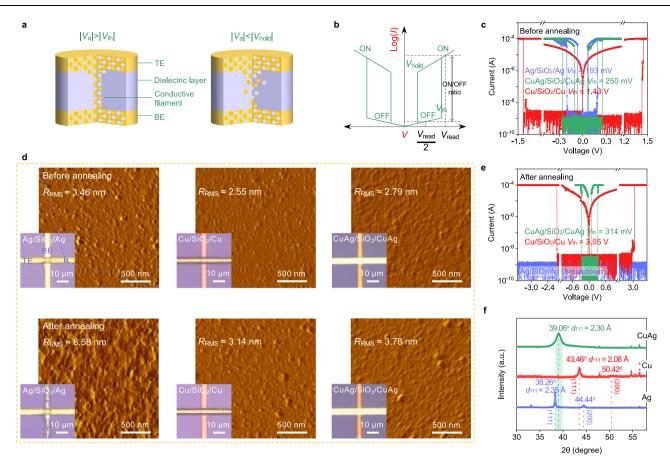

#### CuAg alloy-based selector with high-temperature stability

Figure 1a, b demonstrates the device concept and working principles of the Cu/Ag metal-filament-based selector device. These two metals can be injected into the intermediate dielectric layer and form a conductive path when applying a sufficient electric field, and the switching can be volatile due to agglomeration and surface-tension effects<sup>45,46</sup>. In this study, the CuAg alloy is adopted as the electrode material<sup>34</sup>, which is previously known for its tunable optical properties<sup>47</sup>, outstanding mechanical strength<sup>48</sup>, durability and oxidation resistance<sup>49,50</sup>. Here, the thermal stability of symmetrical Ag/dielectric/Ag, Cu/dielectric/Cu and CuAg/dielectric/CuAg cross-point selector arrays are first investigated comparatively. The Cu, Ag and CuAg are prepared as bottom electrodes (BE) and top electrodes (TE) by magnetron sputtering. The dielectric layers of SiO<sub>2</sub> (Fig. 1) prepared by electron beam evaporation and Al<sub>2</sub>O<sub>3</sub> (Supplementary Fig. 2) prepared by atomic layer deposition (ALD) are both investigated (See "Methods"). Before annealing, Ag/ SiO<sub>2</sub>/Ag, Ag/Al<sub>2</sub>O<sub>3</sub>/Ag, CuAg/SiO<sub>2</sub>/CuAg, CuAg/Al<sub>2</sub>O<sub>3</sub>/CuAg and Cu/ Al<sub>2</sub>O<sub>3</sub>/Cu selectors all exhibit steep threshold switching characteristics with various  $V_{\text{th}}$  (Fig. 1c and Supplementary Fig. 2b). For Cu/SiO<sub>2</sub>/Cu though, its selector behavior is not ideal since it has excessively strong retention (Fig. 1c).

In order to simulate the compatibility of the devices with the BEOL processes, the devices are subjected to a high-temperature annealing process (400 °C, Ar atmosphere, 3 mTorr, hold time 1h), and their root-mean-square roughness ( $R_{RMS}$ ) is determined by atomic force microscopy (AFM). As shown in Fig. 1d and Supplementary Fig. 2a, the Ag electrodes exhibit significant self-agglomeration after annealing. The  $R_{\rm RMS}$  of the annealed device increases tremendously compared to the initial  $R_{\text{RMS}}$  (from 3.46 to 8.58 nm for Ag/SiO<sub>2</sub>/Ag and from 5.03 to 8.37 nm for Ag/Al<sub>2</sub>O<sub>3</sub>/Ag). In contrast, the stacks of Cu/SiO<sub>2</sub>/Cu, Cu/ Al<sub>2</sub>O<sub>3</sub>/Cu, CuAg/SiO<sub>2</sub>/CuAg and CuAg/Al<sub>2</sub>O<sub>3</sub>/CuAg maintain similar morphology before and after annealing, in which the  $R_{\rm RMS}$  changes from 2.55, 2.61, 2.79 and 2.21 nm to 3.14, 3.13, 3.78 and 3.87 nm, respectively. In addition, the annealing process significantly degrades the threshold switching behaviors of Ag/dielectric/Ag and Cu/dielectric/Cu devices. The Ag-based devices become open due to the apparent degradation of electrodes. On the other hand, the  $V_{\rm th}$  of Cubased devices significantly increases (Fig. 1e and Supplementary Figs. 2c and 3), potentially caused by copper oxidation even though the structure seems intact. Intriguingly, the CuAg-based device still maintains the threshold switching characteristics after annealing. The crystalline structures of the Ag, Cu and CuAg thin films (~200 nm), which are deposited on Si/SiO<sub>2</sub> substrates, are subsequently characterized by X-ray diffraction (XRD, Fig. 1f). The combined results of XRD, scanning transmission electron microscope (STEM, Supplementary Fig. 4a) and corresponding energy dispersive X-ray spectroscopy (EDS) (Supplementary Fig. 4b, c) indicate that the CuAg film is an alloy with an interplanar spacing of 2.30 Å and a Cu/Ag atomic ratio of 3:5 (denoted as CuAg(3:5), if not otherwise specified, CuAg(3:5) is expressed as CuAg in simplified form in this work). In addition, we also vary the process conditions to obtain two more copper-silver alloys, with the Cu/Ag atomic ratios determined as 8:3 and 4:7, respectively (denoted as CuAg(8:3) and CuAg(4:7), see Supplementary Fig. 5a-c for details). After 400 °C annealing, these devices with alloy electrodes also maintain the threshold switching behaviors, indicating a wide process window for good thermal stability (Supplementary Fig. 5d-f).

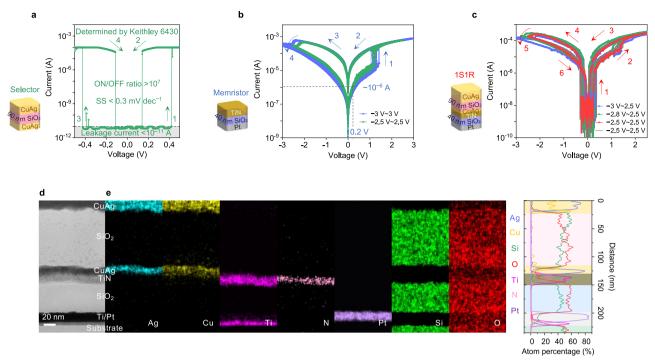

Furthermore, we explore the leakage current, voltage tunability and endurance of the CuAg-based selectors. Symmetric CuAg/SiO<sub>2</sub>/ CuAg cross-point architecture is prepared as illustrated in Fig. 2a and Supplementary Fig. 6a, d. The  $R_{\text{RMS}}$  of the SiO<sub>2</sub> interlayer (90 nm

**Fig. 1** | **Exploration of the CuAg alloy-based selector. a** Schematic illustrations of a metal-filament-based selector under different applied voltage ( $V_a$ ). **b** Representative current–voltage (I-V) characteristics of a Cu/Ag metal-filament-based selector, the ON/OFF ratio corresponds to the current variation at the read voltage ( $V_{read}$ ) and half-read voltage ( $V_{read}/2$ ). **c** I-V characteristics of Ag/SiO<sub>2</sub>/Ag,

Cu/SiO<sub>2</sub>/Cu and CuAg/SiO<sub>2</sub>/CuAg selectors before annealing. **d** Surface morphologies of Ag/SiO<sub>2</sub>/Ag, Cu/SiO<sub>2</sub>/Cu and CuAg/SiO<sub>2</sub>/CuAg devices before and after annealing in Ar atmosphere at 400 °C for 1 h. **e** *I*–*V* characteristics of annealed Ag/SiO<sub>2</sub>/Ag, Cu/SiO<sub>2</sub>/Cu and CuAg/SiO<sub>2</sub>/CuAg selectors. **f** XRD patterns of the Ag, Cu and CuAg films on SiO<sub>2</sub>/Si substrates.

thickness) is ~1.95 nm, and the valence state of Si is determined to be dominant Si<sup>4+</sup> (103.3 eV) (Supplementary Fig. 6b, c). The tunable  $V_{\text{th}}$  is achieved by varying the thickness of SiO<sub>2</sub>, where the thicknesses are determined by AFM on patterned SiO<sub>2</sub> films (Supplementary Figs. 7 and 8). In order to better evaluate the ON/OFF ratio, a Keithley 6430 source meter with higher precision is used to measure the switching characteristics of the CuAg/SiO2(90 nm)/CuAg selector. The CuAg/ SiO<sub>2</sub>(90 nm)/CuAg device demonstrates stable symmetric threshold switching characteristics with a superior SS of <0.3 mV decade<sup>-1</sup> and an average  $V_{\rm th}$  of 316 mV (Standard deviation  $\sigma \approx 55$  mV) when the compliance current (I<sub>CC</sub>) is set to 100 µA (Fig. 2a and Supplementary Fig. 8d). The device's leakage current is at least smaller than 10<sup>-11</sup> A, the ON/OFF ratio is larger than 10<sup>7</sup> (Fig. 2a), which enables large crosspoint arrays that are very difficult to achieve with other categories of selector technologies. Also, the endurance of CuAg selectors can reach over 10<sup>10</sup> (Supplementary Fig. 9). Moreover, it should be pointed out that the as-fabricated CuAg/SiO2/CuAg selectors do not require an electroforming process with a voltage higher than V<sub>th</sub>. This phenomenon can be explained by the lower migration barrier of Ag/Ag<sup>+</sup> in SiO<sub>2</sub> compared to Al<sub>2</sub>O<sub>3</sub>, which is calculated by ab initio simulations with the nudged elastic band method<sup>51</sup> (Supplementary Fig. 10). In addition, the EDS mappings (Supplementary Fig. 6d) show the diffused Cu and Ag particles, corroborating that the threshold switching of CuAg alloybased selectors originates from metallic conductive filaments<sup>15,34</sup>.

As mentioned above, high-performance selectors need to have sufficiently low leakage current in the OFF state and high drive current in the ON state so as to suppress sneak-path currents and achieve highdensity arrays on the one hand, and to allow easy memory write and read operations without significant voltage drops on the selector on the other hand. In these regards, the CuAg/SiO<sub>2</sub>(90 nm)/CuAg selector is potentially a promising candidate due to its negligible leakage current (<10 pA), high ON current (>100 µA), steep SS (<0.3 mV decade<sup>-1</sup>), sufficient endurance (>10<sup>10</sup>), electroforming-free feature and superior thermal stability.

#### 64 × 64 1S1R array for synaptic weight storage

To further explore the feasibility of applying CuAg/SiO<sub>2</sub>/CuAg selectors in ISIR arrays, we construct vertically stacked 64 × 64 ISIR array with CuAg/SiO<sub>2</sub>/CuAg selectors and Pt/SiO<sub>2</sub>/TiN memristors. Independent Pt/SiO<sub>2</sub>(40 nm)/TiN memristors are also prepared and measured for comparison (See "Methods"). TiN electrode is obtained by reactive magnetron sputtering with N<sub>2</sub>/Ar flow of 0.2/20 for optimized electrical conductivity (Supplementary Fig. 11). The device characteristics of Pt/SiO<sub>2</sub>/TiN memristor are summarized in Fig. 2b, which exhibit typical bipolar resistive switching behaviors with moderate SET and RESET voltages<sup>52–54</sup>.

For 1S1R integration, the manufacturing processes are shown in Supplementary Fig. 12. The as-fabricated CuAg/SiO<sub>2</sub>/CuAg/TiN/SiO<sub>2</sub>/Pt 1S1R device exhibits the desired DC sweep characteristics (Fig. 2c). The CuAg/SiO<sub>2</sub>/CuAg selector acts as a threshold switch with low leakage (<10<sup>-11</sup> A), significantly suppressing the sneak-path currents in the cross-point array. As the sweep voltage (from CuAg TE to Pt BE) increases, the current of the 1S1R device first sharply increases at -0.3 V (*V*<sub>th</sub>), completing the threshold switch (arrow 1, Fig. 2c). Then, a second

**Fig. 2** | **SiO<sub>2</sub>-based selector, memristor and ISIR device.** a *I*-*V* characteristics of the CuAg/SiO<sub>2</sub>(90 nm)/CuAg selector as determined by Keithley 6430. b *I*-*V* characteristics of the Pt/SiO<sub>2</sub>/TiN memristor in DC voltage sweep cycles with different stop voltages, the Pt/SiO<sub>2</sub>/TiN memristor exhibits typical SET and RESET

processes. **c** *I*–*V* characteristics of the 1S1R device in DC voltage sweep cycles with different stop voltages. **d** Cross-sectional STEM image of one 1S1R device. **e** The EDS mapping and linear sweep results with the elements Ag, Cu, Ti, N, Pt, Si and O corresponding to (**d**).

current jump occurs at -1.5 V, indicating the SET process (arrow 2). When the voltage sweeps back to -0.1 V (hold voltage,  $V_{hold}$ ), the current drops, and the selector device switches to the OFF state (arrow 3). When the voltage sweeps to negative values, the selector turns on again at ~-0.3 V (- $V_{th}$ , arrow 4), followed by a reduction in current at above -2 V, indicating the RESET process (arrow 5). Finally, after the negative voltage sweeps back to ~-0.1 V (- $V_{hold}$ ), the current drops again, and the device returns to the HRS (arrow 6). A full switching cycle is hence completed. To visualize the stacking of ISIR devices, the cross-sectional profile is extracted by focused ion beam milling in the middle of one ISIR device, where the stacking order of the electrodes and dielectric layers can be clearly observed using STEM and EDS (Fig. 2d, e).

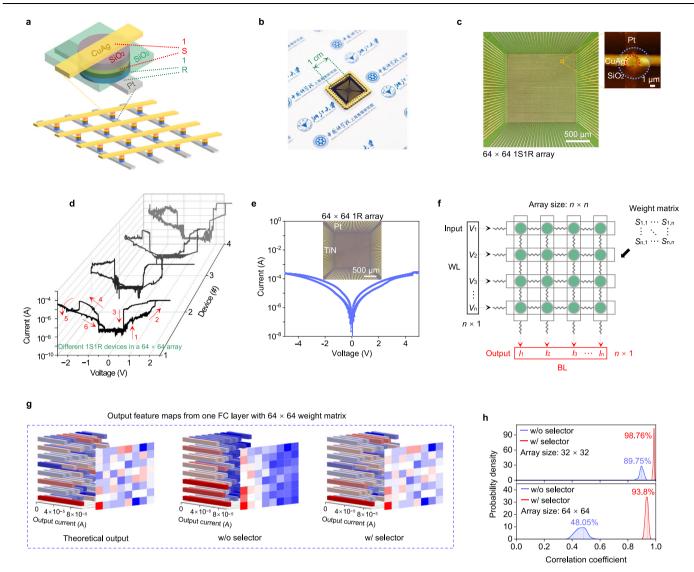

In addition, the potential of the 1S1R array for implementing nextgeneration memory and neuromorphic computing primitives is considered. The structure schematic, chip and array photos are shown in Fig. 3a-c. By optimizing the RRAM interlayer process, various devices in the as-fabricated 64 × 64 1S1R array exhibit expected electrical properties, making it a promising candidate for high-density memory applications (Fig. 3d and Supplementary Fig. 13). With the integration of the selector, the leakage current of the  $64 \times 64$  1S1R reduces from  $10^{-6}$  $(64 \times 64 \text{ 1R in Fig. 3e})$  to  $<10^{-11}$  A (Supplementary Fig. 14). The sneak-path current and parasitic capacitance are significantly suppressed (Supplementary Fig. 15), indicating that 1S1R array is a particularly useful technology for SNN applications with improved operation speed and reduced power consumption. In summary, the ON/OFF ratio of 1S1R devices achieves an improvement of 10<sup>5</sup> times relative to the Pt/SiO<sub>2</sub>/ TiN 64×64 1R array alone, reducing the power consumption and improving the feasible array size as cross-point memory.

Furthermore, we demonstrate the advantages of applying 1S1R to synaptic weight storage by performing simulations of vector matrix multiplication (VMM) using  $32 \times 32$  and  $64 \times 64$  cross-point arrays, with and without selectors (See "Methods" for array simulations). Figure 3f shows a schematic of the simulation procedure, in which the input

vector and binary weight matrices are randomly generated<sup>55-58</sup>. The weights are encoded in the form of RRAM conductance matrix (S) in which LRS corresponds to '1' and HRS corresponds to '0'. During the simulations, the LRS resistances are generated using the measured distribution, and the ON/OFF ratios of RRAM and 1S1R are assumed to be 100 and 10<sup>7</sup>, respectively. The output results in terms of BL currents are simulated with one fully connected (FC) layer of 64 × 64 or 32 × 32 weight matrices, as shown in Fig. 3g and Supplementary Fig. 16. These results indicate that the arrays with selectors are able to generate much more similar output feature maps to the theoretical values than those without selectors. In order to quantify the accuracy of VMM computation, the correlation coefficient of the simulated output vector (IR drop and sneak-path currents considered) versus the theoretical output (by floating-point calculation) is calculated. The probability density of the correlation coefficients obtained from 1000 sets of random inputs are shown in Fig. 3h. It can be concluded that cross-point arrays with selectors achieve much higher VMM accuracy compared to those without selectors (93.8% vs. 48.05% for 64 × 64 array). Subsequently, the accuracy of VMM calculations using the 1S1R and 1 R subarrays is also compared in Supplementary Fig. 17 to demonstrate the positive effect of the 1S1R on the VMM. It can be seen that the accuracy decreases significantly with increasing array size in the absence of the selector. By eliminating the sneak-path currents, the as-fabricated 1S1R device can strongly suppress the accuracy degradation and enable much larger arrays of synaptic data to be accessed simultaneously, boosting energy efficiency.

#### Selector-based LIF neuron

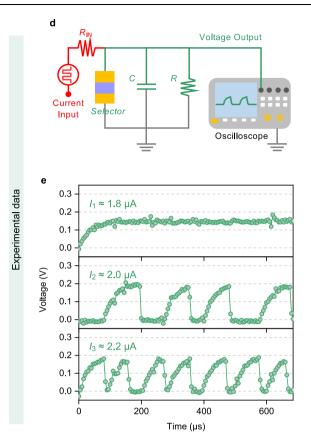

The LIF neuron is an important classical biological neuron model which has been widely studied and adopted to mimic the human brain<sup>59</sup> (Fig. 4a). The LIF model features a "leaky" resistor and a capacitor connecting in parallel with a switch, the voltage across which represents the membrane potential of the biological neuron (Fig. 4b). So far, there have been many attempts to emulate LIF model with

**Fig. 3** | **The 64 × 64 1S1R array. a** Schematic illustration of the integrated 1S1R devices. **b** Photo of the integrated 64 × 64 1S1R chip. **c** Optical micrograph of the 64 × 64 1S1R array. The inset shows an AFM image of one 1S1R device. **d** *I*–*V* characteristics of different 1S1R devices in a 64 × 64 array. **e** *I*–*V* characteristics of the Pt/ SiO<sub>2</sub>/TiN memristor measured from the 64 × 64 1R array. The inset shows the optical image of the 64 × 64 1R array. **f** Schematic diagram of VMM simulation using cross-point array, where the voltage vector input to the word line (WL) is a random

value and the current after VMM is output from the bit line (BL). **g** Output feature map obtained by VMM simulation using one FC layer with  $64 \times 64$  weight matrix for the theoretical output (left), without selector (middle), and with selector (right), respectively. **h** Probability density of the correlation coefficients between the theoretical results and the output results obtained by generating 1000 random sets of voltage vectors and weight matrices fed into the RRAM matrix with and without selector.

CMOS analog circuits<sup>60</sup> or non-volatile memories such as NOR Flash<sup>61</sup> or FeFET<sup>62</sup>. Figure 4c depicts a key feature of the LIF neuron: there is minimal input for the neuron to reach the threshold and fire, and once the threshold is reached, the firing frequency increases almost linearly with increasing input. By setting the refractory period ( $\tau_0$ ), RC time constant ( $\tau_{\rm RC}$ ) and threshold current ( $I_{\rm th}$ ), the variation curve of firing rate with input current in Fig. 4c is simulated. Compared to other selectors with higher leakage (e.g.,  $VO_2^{28}$ ,  $NbO_x^{10}$ , or OTS-based<sup>30</sup>), the extremely low leakage currents of CuAg alloy-based selectors is the key enabler for implementing a LIF neuron. This is because the equivalent leaky resistance of the LIF neuron circuits depends on both the parallel resistor and the OFF state resistance of the switch. With the connection topology of Fig. 4b, the CuAg alloy-based selector's OFF state resistance and its impact on the parameters of the LIF neuron is negligible compared to the parallel resistor, where the value of the parallel resistor can be well controlled in modern integrated circuit design.

In order to characterize the behaviors of the proposed LIF neuron, we carry out electrical measurements using the setup shown in Fig. 4d and Supplementary Fig. 18. When a constant current is input to the neuron, it will charge up the capacitor and increase the input node voltage from 0 V, which in turn will induce leakage current through the parallel resistor. If the input current is smaller than the  $I_{\rm th}$  (Fig. 4e), the input node voltage will saturate at a voltage smaller than the  $V_{\rm th}$ of the selector, and the neuron will not be fired. On the other hand, if the input current is above  $I_{\rm th}$ , the input node voltage will rise above  $V_{\rm th}$ , leading to an ON state of the selector device (i.e., the neuron is fired). The firing of the neuron manifests itself as a high transient current across the device and the discharge of the parallel capacitor. Based on the mechanism described above, the  $I_{\rm th}$  of the LIF neuron can be derived in terms of the selector  $V_{\text{th}}$ :  $I_{\text{th}} = V_{\text{th}}/R$ . The firing frequency of the selector-based LIF neuron also increases with the input current due to the less time needed to charge up the parallel capacitor again. In summary, the LIF behaviors predicted by the theoretical model have been experimentally observed from the selector-based LIF neuron. We may conclude that the proposed LIF neuron circuit based on CuAg alloy selectors is a near-perfect physical analog of the LIF model.

**Fig. 4** | **On the validation of selector-based LIF neuron. a** Schematic diagram of a biological neuron. **b** Circuit model of a LIF neuron, the relationship between the I(t) and the u(t) is described by the equation in (**b**), where  $u_{rest}$  is the resting membrane potential. **c** Simulation schematic of a LIF response function, where the relationship

In summary, we have demonstrated the CuAg alloy-based selector as a promising candidate for high-density cross-point memory and neuromorphic computing applications, which features simple preparation processes, good thermal stability, electroforming-free selector behaviors, tunable  $V_{\rm th}$  and over 7 orders of magnitude ON/OFF ratio. Based on this selector device, the proper 1S1R device characteristics in a vertically stacked 64 × 64 1S1R cross-point array are achieved, including sufficiently low sneak-path current, desirable I-V curves, stable memory window and switching endurance. Such cross-point arrays can be used to store the synaptic weights of neural networks and achieve more accurate and energy-efficient in-memory computation for AI. A selectorbased LIF neuron is also experimentally demonstrated, providing a new perspective for the application of such devices as neurons. The CuAgalloy electrode selector has good thermal stability that is compatible with the CMOS BEOL process. It can potentially realize the on-chip integration of 1S1R array and LIF neuron, which implements two different functions (synapse and neuron) on one technology platform.

# Methods

#### **Device fabrication**

(1) CuAg-based selector: The Cu, Ag and CuAg BE are deposited on polished SiO<sub>2</sub> (300 nm) on Si wafers by means of standard photolithography and magnetron sputtering (AJA, ACT Orion 8). Cu and Ag are obtained by magnetron sputtering of 50.8 mm diameter Cu target (99.99% purity) and Ag target (99.99% purity), respectively. During the co-sputtering process, the Ag target is sputtered at a radio frequency power of 60 W/120 W/240 W, and the Cu target is sputtered at a direct current power of 60 W. SiO<sub>2</sub>

between the firing rate and the input current is described by the equation in (c). **d** Circuit for implementing the selector-based LIF neuron. **e** Experimental demonstration of the LIF neuron's firing rate with various input currents ( $I_1 \approx 1.8 \,\mu$ A,  $I_2 \approx 2.0 \,\mu$ A and  $I_3 \approx 2.2 \,\mu$ A).

films with different thicknesses are obtained by electron beam evaporation with an acceleration voltage of 10 kV at room temperature (99.99% purity of SiO<sub>2</sub> particles, evaporation rate: -5 Å/s). The Al<sub>2</sub>O<sub>3</sub> layer is deposited on the BE by the ALD process (200 °C, 60 cycles). For a single cycle of ALD, trimethylaluminum (TMA) is first pulsed to 70 Pa for 0.02 s, followed by a 15 s purge. H<sub>2</sub>O is then pulsed to 90 Pa for 0.01 s, followed by a 20 s purge. After that, Cu, Ag and CuAg alloy thin films as TE are deposited by photolithography and magnetron sputtering.

- (2) Annealing process: All selectors are placed in an argon atmosphere (3 mTorr) at a heating rate of 0.3 °C per second to 400 °C and maintained for 1 h, followed by slow cooling to room temperature.

- (3) Pt/SiO<sub>2</sub>/TiN memristors: Patterned Ti/Pt (5/15 nm) as BE are deposited at room temperature by means of photolithography and electron beam evaporation (99.99% purity of Ti and Pt particles). SiO<sub>2</sub> films are obtained by electron beam evaporation with an acceleration voltage of 10 kV at room temperature (99.99% purity of SiO<sub>2</sub> particles, evaporation rate: -5 Å/s). Patterned TiN as TE is deposited at room temperature by sputtering (AJA, ACT Orion 8) Ti target (99.99% purity) in N<sub>2</sub>/Ar flow ratio of 0.2 sccm /20 sccm (3 mTorr) at room temperature.

- (4) The 1S1R array: The 64×64 1S1R array consists of CuAg/SiO<sub>2</sub>/ CuAg selectors and Pt/SiO<sub>2</sub>/TiN memristors stacked vertically, and the fabrication steps are detailed in Supplementary Fig. 12.

#### Materials characterizations

Optical microscope images are obtained by 3D laser scanning confocal microscope (Keyence VK9710K). AFM images and Raman spectra are obtained by a combined AFM/Raman (532 nm) instrument (NT-MDT

NTEGRA). The composition and structural analyses are carried out by XRD (Rigaku D/max2200) and X-ray photoelectron spectroscopy (XPS, Thermo Fisher 250 XI). STEM images and corresponding EDS are obtained by FEI Titan Themis 200.

#### **Electrical measurements**

Electrical characterizations are executed with an Agilent B1500A semiconductor device parameter analyzer, a Keithley 6430 source meter, an Agilent MSO7054A oscilloscope, a Keysight 33250A waveform generator, a Keithley 4200 SCS, a Keithley 707A switch matrix, and a self-made variable resistance box (10 k, 100 k, 1M and 10 M $\Omega$ ).

#### Array simulations

The input parameters of the  $n \times n$  cross-point array simulations include voltage vector applied to the WL  $[V_1, V_2, V_3, ..., V_n]$ , the weight data in the form of conductance matrix corresponding to all cross-points  $[S_{11}, \dots, S_{nn}]$ , and the line resistances between two adjacent junctions along WLs or BLs ( $R_{WL}$ ,  $R_{BL}$ ). The output parameters of VMM are defined as the current vector read from the BLs  $[I_1, I_2, I_3, ..., I_n]$  when the BL voltages are fixed at zero. The junction conductance is defined by the measured results of 1S1R devices, and the line resistance is defined with empirical values. The cross-point array simulations are performed as SPICE-style simulations of the equivalent circuits implemented in MATLAB. The steady-state electrical characteristics of a cross-point array can be completely described by the WL plane voltages  $[V_{WL}(i, j)]$ and BL plane voltages  $[V_{BI}(i, j)]$  at each cross-point, where  $1 \le i, j \le n$ . Based on Kirchhoff's law and the input parameters, these  $2 \times n \times n$ voltage variables can be written in matrix form and solved for the currents in an iterative manner. The accuracy of the VMM operations using the cross-point array is characterized by the statistical results of the correlation coefficient between the simulated output current vector and the theoretical output vector, obtained using multiple sets of randomly generated input parameters (See Supplementary Fig. 1 and Supplementary Table 1 for further details).

# Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

# **Code availability**

The simulation codes supporting the findings of this study are available from the corresponding authors upon reasonable request.

#### References

- Floridi, L. & Chiriatti, M. GPT-3: its nature, scope, limits, and consequences. *Minds. Mach.* **30**, 681–694 (2020).

- 2. Vaswani, A. et al. Attention is all you need. In Advances in Neural Information Processing Systems, 5998–6008 (NIPS, 2017).

- Wulf, W. A. & McKee, S. A. Hitting the memory wall: implications of the obvious. ACM SIGARCH Comput. Archit. N. 23, 20–24 (1995).

- Radway, R. M. et al. Illusion of large on-chip memory by networked computing chips for neural network inference. *Nat. Electron.* 4, 71–80 (2021).

- Cai, F. et al. Power-efficient combinatorial optimization using intrinsic noise in memristor Hopfield neural networks. *Nat. Electron.* 3, 409–418 (2020).

- Xia, Q. & Yang, J. J. Memristive crossbar arrays for brain-inspired computing. *Nat. Mater.* 18, 309–323 (2019).

- Wang, C. et al. Scalable massively parallel computing using continuous-time data representation in nanoscale crossbar array. *Nat. Nanotechnol.* 16, 1079–1085 (2021).

- Guo, X. et al. Modeling and experimental demonstration of a Hopfield network analog-to-digital converter with hybrid CMOS/memristor circuits. *Front. Neurosci.* 9, 488 (2015).

- 9. Yi, W. et al. Biological plausibility and stochasticity in scalable VO<sub>2</sub> active memristor neurons. *Nat. Commun.* **9**, 4661 (2018).

- Kumar, S., Williams, R. S. & Wang, Z. Third-order nanocircuit elements for neuromorphic engineering. *Nature* 585, 518–523 (2020).

- 11. Ding, K. et al. Phase-change heterostructure enables ultralow noise and drift for memory operation. *Science* **366**, 210–215 (2019).

- Berdan, R. et al. Low-power linear computation using nonlinear ferroelectric tunnel junction memristors. *Nat. Electron.* 3, 259–266 (2020).

- 13. Jung, S. et al. A crossbar array of magnetoresistive memory devices for in-memory computing. *Nature* **601**, 211–216 (2022).

- Dalgaty, T. et al. In situ learning using intrinsic memristor variability via Markov chain Monte Carlo sampling. *Nat. Electron.* 4, 151–161 (2021).

- Yeon, H. et al. Alloying conducting channels for reliable neuromorphic computing. *Nat. Nanotechnol.* 15, 574–579 (2020).

- Wang, Z. et al. Fully memristive neural networks for pattern classification with unsupervised learning. *Nat. Electron.* 1, 137–145 (2018).

- 17. Pi, S. et al. Memristor crossbar arrays with 6-nm half-pitch and 2-nm critical dimension. *Nat. Nanotechnol.* **14**, 35–39 (2019).

- Cassuto, Y., Kvatinsky, S. & Yaakobi, E. Sneak-path constraints in memristor crossbar arrays. In Proc. 2013 IEEE International Symposium on Information Theory, 156–160 (IEEE, 2013).

- Liang, J. & Wong, H.-S. P. Cross-point memory array without cell selectors—device characteristics and data storage pattern dependencies. *IEEE Trans. Electron Devices* 57, 2531–2538 (2010).

- Zidan, M. A., Fahmy, H. A. H., Hussain, M. M. & Salama, K. N. Memristor-based memory: the sneak paths problem and solutions. *Microelectron. J.* 44, 176–183 (2013).

- Song, J., Woo, J., Lim, S., Chekol, S. A. & Hwang, H. Self-limited CBRAM with threshold selector for 1S1R crossbar array applications. *IEEE Electron Device Lett.* 38, 1532–1535 (2017).

- 22. Midya, R. et al. Anatomy of Ag/Hafnia-based selectors with 10<sup>10</sup> nonlinearity. *Adv. Mater.* **29**, 1604457 (2017).

- 23. Hua, Q. et al. A threshold switching selector based on highly ordered Ag nanodots for X-point memory applications. *Adv. Sci.* **6**, 1900024 (2019).

- 24. Sun, Y. et al. Performance-enhancing selector via symmetrical multilayer design. *Adv. Funct. Mater.* **29**, 1808376 (2019).

- Shen, J. et al. Elemental electrical switch enabling phase segregation-free operation. Science 374, 1390–1394 (2021).

- Kim, S., Zhou, J. & Lu, W. D. Crossbar RRAM arrays: selector device requirements during write operation. *IEEE Trans. Electron Devices* 61, 2820–2826 (2014).

- Son, M. et al. Excellent selector characteristics of nanoscale VO<sub>2</sub> for high-density bipolar ReRAM applications. *IEEE Electron Device Lett.* 32, 1579–1581 (2011).

- Zhou, X. et al. Phase-transition-induced VO<sub>2</sub> thin film IR photodetector and threshold switching selector for optical neural network applications. *Adv. Electron. Mater.* 7, 2001254 (2021).

- 29. Yang, Y. et al. A new opportunity for the emerging tellurium semiconductor: making resistive switching devices. *Nat. Commun.* **12**, 6081 (2021).

- 30. Velea, A. et al. Te-based chalcogenide materials for selector applications. *Sci. Rep.* **7**, 8103 (2017).

- Gopalakrishnan, K. et al. Highly-scalable novel access device based on mixed ionic electronic conduction (MIEC) materials for high density phase change memory (PCM) arrays. In Proc. 2010 Symposium on VLSI Technology, 205–206 (IEEE, 2010).

- 32. Shenoy, R. et al. Endurance and scaling trends of novel accessdevices for multi-layer crosspoint-memory based on mixed-ionicelectronic-conduction (MIEC) materials. In *Proc. 2011 Symposium* on *VLSI Technology-Digest of Technical Papers*, 94–95 (IEEE, 2011).

### Article

- Lu, Y.-F. et al. Low-power artificial neurons based on Ag/TiN/ HfAlO<sub>x</sub>/Pt threshold switching memristor for neuromorphic computing. *IEEE Electron Device Lett.* **41**, 1245–1248 (2020).

- Zhou, X., Zhao, L., Lu, L. & Li, D. CuAg/Al<sub>2</sub>O<sub>3</sub>/CuAg threshold switching selector for RRAM applications. In Proc. 2021 Device Research Conference (DRC), 1–2 (IEEE, 2021).

- 35. Xu, X. et al. Investigation of LRS dependence on the retention of HRS in CBRAM. *Nanoscale Res. Lett.* **10**, 61 (2015).

- Park, J. H., Kim, D., Kang, D. Y., Jeon, D. S. & Kim, T. G. Nanoscale 3D stackable Ag-doped HfO<sub>x</sub>-based selector devices fabricated through low-temperature hydrogen annealing. ACS Appl. Mater. Inter. **11**, 29408–29415 (2019).

- Sharma, S. & Spitz, J. Hillock formation, hole growth and agglomeration in thin silver films. *Thin Solid Films* 65, 339–350 (1980).

- Burr, G. W. et al. Neuromorphic computing using non-volatile memory. Adv. Phys. X 2, 89–124 (2017).

- Hu, S. et al. Associative memory realized by a reconfigurable memristive Hopfield neural network. Nat. Commun. 6, 7522 (2015).

- Sun, J., Xiao, X., Yang, Q., Liu, P. & Wang, Y. Memristor-based Hopfield network circuit for recognition and sequencing application. AEU-Int. J. Electron. Commun. 134, 153698 (2021).

- Zhang, Y., Cui, M., Shen, L. & Zeng, Z. Memristive quantized neural networks: a novel approach to accelerate deep learning on-chip. *IEEE Trans. Cybern.* 51, 1875–1887 (2019).

- Woo, J. & Yu, S. Impact of selector devices in analog RRAM-based crossbar arrays for inference and training of neuromorphic system. *IEEE Trans. VLSI Syst.* 27, 2205–2212 (2019).

- Fazio, A. Advanced technology and systems of cross point memory. In Proc. 2020 IEEE International Electron Devices Meeting (IEDM), 24.1.1–24.1.4 (IEEE, 2020).

- Dutta, S., Kumar, V., Shukla, A., Mohapatra, N. R. & Ganguly, U. Leaky integrate and fire neuron by charge-discharge dynamics in floating-body MOSFET. Sci. Rep. 7, 8257 (2017).

- Wang, Z. et al. Threshold switching of Ag or Cu in dielectrics: materials, mechanism, and applications. *Adv. Funct. Mater.* 28, 1704862 (2018).

- Liu, Q. et al. Controllable growth of nanoscale conductive filaments in solid-electrolyte-based ReRAM by using a metal nanocrystal covered bottom electrode. ACS Nano 4, 6162–6168 (2010).

- Zhang, H. et al. Blue laser-induced photochemical synthesis of CuAg nanoalloys on h-BN supports with enhanced SERS activity for trace-detection of residual pesticides on tomatoes. J. Alloy. Compd. 825, 153996 (2020).

- Kushchev, S. et al. Structure and mechanical properties of Ag–Cu films prepared by vacuum codeposition of Au and Cu. *Inorg. Mater.* 51, 673–678 (2015).

- Li, W. et al. Printable and flexible copper-silver alloy electrodes with high conductivity and ultrahigh oxidation resistance. ACS Appl. Mater. Inter. 9, 24711–24721 (2017).

- Zhang, L. et al. Hydrogenation of levulinic acid into gammavalerolactone over in situ reduced CuAg bimetallic catalyst: strategy and mechanism of preventing Cu leaching. *Appl. Catal. B Environ.* 232, 1–10 (2018).

- 51. Xue, K.-H. et al. Theoretical investigation of the Ag filament morphology in conductive bridge random access memories. *J. Appl. Phys.* **124**, 152125 (2018).

- 52. Lim, D.-H. et al. Filament geometry induced bipolar, complementary and unipolar resistive switching under the same set current compliance in Pt/SiO<sub>x</sub>/TiN. *Sci. Rep.* **5**, 15374 (2015).

- Zhao, L. et al. Dynamic modeling and atomistic simulations of SET and RESET operations in TiO<sub>2</sub>-based unipolar resistive memory. *IEEE Electron Device Lett.* **32**, 677–679 (2011).

- 54. Zhao, L. et al. Multi-level control of conductive nano-filament evolution in  $HfO_2$  ReRAM by pulse-train operations. *Nanoscale* **6**, 5698–5702 (2014).

- Chen, A. A comprehensive crossbar array model with solutions for line resistance and nonlinear device characteristics. *IEEE Trans. Electron Devices* 60, 1318–1326 (2013).

- Chen, A. Memory selector devices and crossbar array design: a modeling-based assessment. J. Comput. Electron. 16, 1186–1200 (2017).

- Chen, P.-Y., Li, Z. & Yu, S. Design tradeoffs of vertical RRAM-based 3-D cross-point array. *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.* 24, 3460–3467 (2016).

- Lepri, N. et al. Modeling and compensation of IR drop in crosspoint accelerators of neural networks. *IEEE Trans. Electron Devices* 69, 1575–1581 (2022).

- Liu, Y.-H. & Wang, X.-J. Spike-frequency adaptation of a generalized leaky integrate-and-fire model neuron. J. Comput. Neurosci. 10, 25–45 (2001).

- Ebong, I. E. & Mazumder, P. CMOS and memristor-based neural network design for position detection. *Proc. IEEE* **100**, 2050–2060 (2011).

- 61. Kornijcuk, V. et al. Leaky integrate-and-fire neuron circuit based on floating-gate integrator. *Front. Neurosci.* **10**, 212 (2016).

- 62. Luo, J. et al. Capacitor-less stochastic leaky-FeFET neuron of both excitatory and inhibitory connections for SNN with reduced hard-ware cost. In *Proc. 2019 IEEE International Electron Devices Meeting (IEDM)*. 6.4.1–6.4.4 (IEEE 2019).

# Acknowledgements

This work was supported by the Natural Science Foundation of Shanghai (No. 19ZR1479100) and the Shanxi Science and Technology Department (20201101012). This work was supported in part by the Key Research and Development Program of Zhejiang Province under Grant 2021C01039.

# **Author contributions**

L.Z. conceived and designed the experiments and performed the simulation. X.Z. performed the experiments and measurements. L.Z. and X.Z. wrote this paper. C.Y. contributed to the simulation. W.Z. contributed to the experiments and measurements. Y.L., L.Li and G.D. assisted the device fabrications under the supervision of D.L., L.Lu, S.Z. and Z.L. All authors discussed and reviewed the manuscript. D.L. and L.Z. supervised the project.

# **Competing interests**

The authors declare no competing interests.

# **Additional information**

**Supplementary information** The online version contains supplementary material available at https://doi.org/10.1038/s41467-023-39033-z.

**Correspondence** and requests for materials should be addressed to Liang Zhao or Dongdong Li.

**Peer review information** *Nature Communications* thanks Martin Lueker-Boden and the other anonymous reviewers for their contribution to the peer review of this work. A peer review file is available.

**Reprints and permissions information** is available at http://www.nature.com/reprints

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/ licenses/by/4.0/.

© The Author(s) 2023