# nature communications

**Article**

https://doi.org/10.1038/s41467-023-36715-6

# Wafer-scale and universal van der Waals metal semiconductor contact

Received: 23 July 2022

Accepted: 13 February 2023

Published online: 23 February 2023

Lingan Kong<sup>1,3</sup>, Ruixia Wu<sup>1,2,3</sup>, Yang Chen<sup>1</sup>, Ying Huangfu<sup>2</sup>, Liting Liu<sup>1</sup>, Wei Li<sup>2</sup>, Donglin Lu<sup>1</sup>, Quanyang Tao<sup>1</sup>, Wenjing Song<sup>1</sup>, Wanying Li<sup>1</sup>, Zheyi Lu<sup>1</sup>, Xiao Liu<sup>1</sup>, Yunxin Li<sup>1</sup>, Zhiwei Li<sup>1</sup>, Wei Tong<sup>1</sup>, Shuimei Ding<sup>1</sup>, Songlong Liu<sup>2</sup>, Likuan Ma<sup>1</sup>, Liwang Ren<sup>1</sup>, Yiliu Wang<sup>1</sup>, Lei Liao<sup>1</sup>, Xidong Duan <sup>6</sup> & Yuan Liu <sup>6</sup> ⊠

Van der Waals (vdW) metallic contacts have been demonstrated as a promising approach to reduce the contact resistance and minimize the Fermi level pinning at the interface of two-dimensional (2D) semiconductors. However, only a limited number of metals can be mechanically peeled and laminated to fabricate vdW contacts, and the required manual transfer process is not scalable. Here, we report a wafer-scale and universal vdW metal integration strategy readily applicable to a wide range of metals and semiconductors. By utilizing a thermally decomposable polymer as the buffer layer, different metals were directly deposited without damaging the underlying 2D semiconductor channels. The polymer buffer could be dry-removed through thermal annealing. With this technique, various metals could be vdW integrated as the contact of 2D transistors, including Ag, Al, Ti, Cr, Ni, Cu, Co, Au, Pd. Finally, we demonstrate that this vdW integration strategy can be extended to bulk semiconductors with reduced Fermi level pinning effect.

Two-dimensional (2D) semiconductors have attracted considerable interest as ultrathin channel materials for transistors<sup>1-6</sup>. With atomically thin body and dangling-bond free surface, 2D semiconductor offers significant potential for ultimate body thickness scaling, which is essential for reducing short channel effect and further extending Moore's Law<sup>7-11</sup>. However, on the other hand, with ultra-thin body and delicate lattice, achieving high quality metal contact to 2D semiconductors remains a critical challenge<sup>12</sup>. Conventional metallization approaches in microelectronics research (e.g., thermal/e-beam evaporation, sputtering, chemical vapor deposition) are generally "highenergy" fabrication processes based on the vaporization of metal precursor<sup>13-15</sup>. These methods are not necessarily compatible with emerging 2D semiconductors because they usually involve hot metal atoms or clusters bombardment to the contact region, leading to substantial damage via kinetic energy transfer or chemical reaction between the metal atoms and the 2D semiconductors<sup>16-20</sup>. Therefore, strong Fermi level pinning effect is typically observed at metal-2D contact interface with uncontrollable Schottky barrier height and large contact resistance<sup>20-24</sup>, posing an important technological challenge for the investigation of novel physics within 2D semiconductors as well as the realization of high-performance 2D devices.

To avoid the damage during metallization process and to retain the intrinsic properties of 2D contact region, considerable efforts have been devoted to a "low-energy" van der Waals (vdW) integration processes  $^{25-32}$ . Within this approach, the metal and 2D semiconductor are interacted through weakest vdW force in the contact region, rather than chemical bonding (covalent or ionic), hence could retaining their isolated states without interface disorder. For example, by directly evaporating indium with low melting temperature (157 °C) on the MoS $_2$  surface, the intrinsic properties of monolayer MoS $_2$  could be well retained during the "low-energy" and gentle deposition process, forming an atomic clean contact between 2D semiconductors and 3D metals with a clear vdW gap in between  $^{25}$ . Therefore, high-performance monolayer MoS $_2$  transistors could be achieved with low contact

<sup>1</sup>Key Laboratory for Micro-Nano Optoelectronic Devices of Ministry of Education, School of Physics and Electronics, Hunan University, Changsha 410082, China. <sup>2</sup>State Key Laboratory for Chemo/Biosensing and Chemometrics, College of Chemistry and Chemical Engineering, Hunan University, Changsha 410082, China. <sup>3</sup>These authors contributed equally: Lingan Kong, Ruixia Wu. ⊠e-mail: yuanliuhnu@hnu.edu.cn

resistance ~3 k $\Omega$  µm (ref.  $^{25}$ ). Similarly, directly evaporating semimetals $^{26,33}$  (Bi, with melting temperature of 271 °C; Sn, with melting temperature of 232 °C) to monolayer MoS $_2$  could minimize the Fermi level pinning effect with negligible contact barrier and lowest contact resistance of 0.12 k $\Omega$  µm, approaching that suggested by International Roadmap for Devices and Systems (IRDS) $^{34}$ . However, these "low-energy" evaporating processes only work with specific metals (such as In or Bi) and their thermal stability may need further assessment due to low melting temperature.

Alternatively, low-energy vdW contact could be achieved through transferring the pre-fabricated metal electrodes<sup>27–32,35</sup>. By mechanically laminating the flat metal films on the surface of 2D semiconductor, the conventional "high-energy" lithography and metallization processes could be avoided. Hence, the intrinsic physical properties of 2D semiconductors could be well retained, resulting in an ideal metal-2D interfaces and highly tunable Schottky barrier (close to Schottky-Mott limit). However, this method relies on mechanically peeling metals from the pre-deposited substrate, and only a few low-adhesion metals (e.g., Ag, Au, Pt, Pd) could be successfully peeled-off and transferred. For most metals (e.g., Al, W, Ni, Co, Mo, Ti, Ta) used in industry fabrication line, they demonstrate high adhesion force to the predeposited substrate and can not be transferred to form vdW contact with 2D semiconductors. To overcome this limitation, recent work directly deposits a thin Se layer on 2D semiconductors as the buffer layer<sup>36</sup>, followed by evaporation of metals on top. By thermally removing the Se buffer, various metals could be vdW contacted with the underlying 2D materials. However, this process still involves highenergy evaporation process by directly depositing Se buffer on 2D lattice, which could impact the intrinsic lattice of 2D material, and the scalability and this method is not explored. Therefore, a damage-free and scalable vdW integration technique between different 3D metals and 2D semiconductors has yet to be demonstrated, posing a critical limitation for the practical application of vdW contact and highperformance 2D transistors.

Here, we report a wafer-scale and universal vdW metal integration strategy that can be readily applicable to different metals and semiconductors. By spin-coating a decomposable poly(propylene carbonate) (PPC) as the buffer layer between metals and 2D semiconductors. the intrinsic properties of 2D monolayers are not impacted. With further thermally annealing, the PPC layer is dry-decomposed into gases and flow away<sup>37,38</sup>, leading to vdW contact between metals and 2D semiconductors. The achieved vdW interface is atomically clean and sharp, as verified through detailed mechanical test, optical microscopy, atomic force microscopy (AFM), scanning electron microscopy (SEM) and high-resolution transmission electron microscopy (HRTEM) characterizations. With this technique, various high-adhesion and industry compatible metals (e.g., Co, Ni, Al, Ti) could be vdW integrated as the contact of 2D transistors, demonstrating highly tunable Schottky barrier and improved electrical performance. Finally, we demonstrate our vdW integration strategy is not only limited to 2D semiconductors, but could be well-extended to bulk semiconductors (such as Ge, GaAs, IGZO, perovskite) with reduced Fermi level pinning effect. Our study not only realizes high-performance 2D transistor through vdW metal contact, but also provides a wafer-scale and general vdW integration process of different metals without uncontrollable peeling and lamination processes.

### Results

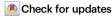

### Fabrication processes of the general vdW contact

Figure 1a-d schematically illustrates the fabrication processes of our vdW metal contact, and the corresponding device optical images are also included. To fabricate the device, WSe<sub>2</sub> is used as a representative 2D semiconductor, which is synthesized using chemical vapour deposition (CVD) method onto a silicon substrate with 300 nm silicon oxide (Fig. 1a). Next, 450 nm thick PPC polymer is spin-coated on top of WSe<sub>2</sub>. Subsequently, source-drain electrodes (60 nm thick Au) are directly evaporated on top of the PPC using standard thermal evaporation process (Fig. 1b), as detailed in Methods section. Since PPC

**Fig. 1** | **Wafer-scale van der Waals (vdW) integration processes. a–d** Schematics and optical images of vdW Au-WSe<sub>2</sub> integration with four steps: WSe<sub>2</sub> flake prepared on substrate (a), poly(propylene carbonate) (PPC) buffer spin-coating

followed by metal deposition (**b**), PPC buffer dry-decomposed through annealing (**c**), intimate contact formation between Au and WSe $_2$  (**d**). The scale bar is 50  $\mu$ m. **e**, **f** Optical images of large scale vdW contacts.

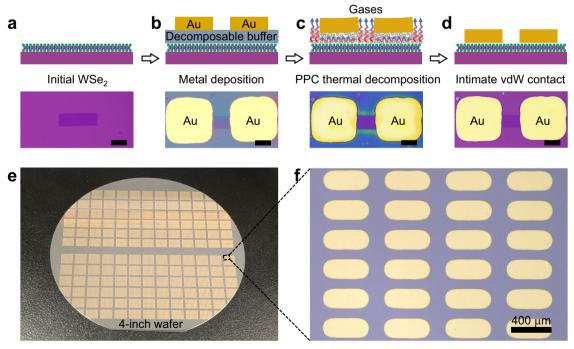

**Fig. 2** | **Characterizations of the vdW metal-semiconductor interface. a** Cross-sectional scanning electron microscopy (SEM) image of WSe<sub>2</sub>/PPC/Au tri-layer structure, purple dashed line represents WSe<sub>2</sub>. **b** Cross-sectional high-resolution transmission electron microscopy (HRTEM) image of the WSe<sub>2</sub>/Au vdW interface after PPC layer decomposed. Atomic sharp and clean metal-semiconductor interface is observed with a vdW gap of -0.3 nm. **c** The schematic of atomic force microscopy (AFM) sample preparation for characterizing the interface quality in

larger area. The as-fabricated  $Cr/WSe_2$  interface is decoupled by mechanically peeling-off the Cr electrodes, and the bottom surface of Cr electrode could be flipped for AFM measurement. **d** AFM characterization of Cr bottom surface (flipped after peeling), demonstrating a small root-mean square (RMS) of 0.16 nm. **e** AFM characterization of WSe<sub>2</sub> top surface after peeling-off the Cr electrode, with RMS of 0.39 nm.

layer is thick enough, it could work as an effective protection layer to prevent any deposition induced damages to underlayer WSe<sub>2</sub> or chemical bonding between Au and WSe<sub>2</sub>. We further note the spin-coating of buffer layer is a low-energy process, and is essential to keep the intrinsic properties of 2D monolayers. As shown in Supplementary Fig. 1, the optical and electrical properties of WSe<sub>2</sub> keeps unchanged before and after spin-coating PPC buffer. Finally, the device is heated at 250 °C for 30 mins under nitrogen environment (Fig. 1c). At this stage, the PPC layer would be totally dry-decomposed into gases and flow away, where the Au are automatically laminated onto WSe<sub>2</sub> through weak vdW interaction, as schematically illustrated in Fig. 1d. Furthermore, the demonstrated vdW integration process here is compatible with industry process and could be fabricated at wafer-scale, as demonstrated in a 4-inch wafer with over ~25,000 vdW contacts using one batch of fabrication (Fig. 1e, f).

We note the PPC polymer used here is essential for our vdW contact approach owing to its unique properties. It could be dry-decomposed into gases at evaluated temperature (250 °C) without involving solution or residues<sup>37,38</sup>, as confirmed through the XPS (X-ray photoelectron spectroscopy) measurement in Supplementary Fig. 2. Hence, the PPC decomposition process has been widely used in microelectronic applications to create various "air-gaps" structure<sup>39-43</sup>,

indicating this process is industry compatible. Since the metals are directly laminated onto the surface of 2D semiconductor, our process could avoid manual transfer process used in previous vdW approach<sup>44</sup>. In addition, the size of individual metal electrode should be <5 mm. For example, if the metal film is continuous (over 1 cm size), the decompose gases will be trapped in the metal film and can not be fully removed, leading to air bubbles or metal film crack, as shown in Supplementary Fig. 3.

To confirm the achieved metal-2D vdW interface is atomically sharp and clean, cross-sectional SEM and HRTEM characterizations are conducted. As shown in Fig. 2a, the as-deposited sample (before PPC decomposition) demonstrates a clear WSe $_2$ /PPC/Au tri-layer structure, where PPC buffer layer is uniform after metal deposition, preventing any interaction between WSe $_2$  and Au during the "high-energy" evaporation process. After the PPC is thermally decomposed, the metal demonstrates intimate contact with the underlayer WSe $_2$  without polymer residues or metal-2D chemical interaction, as confirmed in Fig. 2b using HRTEM. Particularly, the WSe $_2$  lattice structure is well retained without deposition induced damages and a vdW gap -0.3 nm is clearly observed (Fig. 2b and Supplementary Fig. 4), indicating the metal is physical laminated on WSe $_2$  during PPC decomposition.

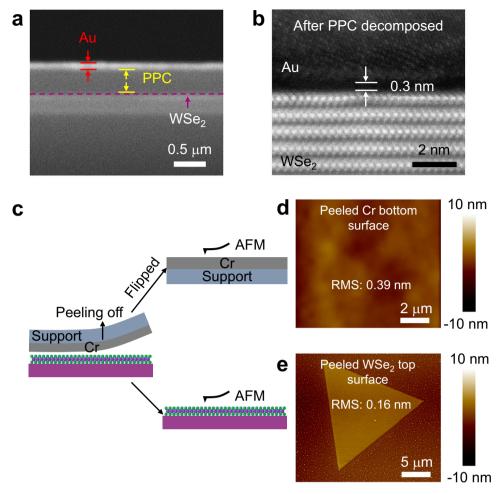

Fig. 3 | Optical images of WSe<sub>2</sub> flakes with different contact metals integrated and peeled-off. a–f The upper panels show the optical images of different metals integrated on top of WSe<sub>2</sub> flake, including Ag (a), Al (b), Cr (c), Cu (d), Co (e), Pd (f). In the meantime, the corresponding optical image after peeling-off electrodes are also demonstrated as the lower panels, where the white dash lines are used to

highlight the outlines of electrode position. The underlying WSe $_2$  nanosheets sustain their original shapes without observable cracks or wrinkles, indicating the weak vdW interaction between different metals with 2D materials. The scale bar is 40  $\mu$ m.

Since the HRTEM only characterizes the interface properties of small region (typically tens of nanometers), AFM measurement is further conducted to characterize the interface properties of the whole contact region. Thanks to the weak vdW interaction within the metal-2D contact, the as-fabricated Cr/WSe<sub>2</sub> vdW interface could be decoupled by mechanically peeling-off the integrated Cr electrodes (Method section), where the bottom surface of Cr film could be flipped for AFM measurement (schematically illustrated in Fig. 2c). As shown in the Fig. 2d, the bottom surface of peeled Cr demonstrates atomic flat surface with a root-mean square (RMS) of 0.39 nm, which replicates the flat surface of the PPC film (Supplementary Fig. 5). In the meantime, the decoupled WSe<sub>2</sub> demonstrates flat surface with small RMS roughness of 0.16 nm (Fig. 2e), consistent with the as-grown WSe<sub>2</sub> surface (Supplementary Fig. 6). The flat Cr bottom surface and WSe<sub>2</sub> top surface (after separating the fabricated interface) is strong evidence of the optimized vdW interface achieved without polymer residues. We note the AFM approach to characterize peeled junction could also be extended to examine other vdW interfaces (e.g., superconductor/insulator, semiconductor/dielectric) with atomic resolution, which could provide more information within two-dimensional area (over 20×20 µm2 in our experiment). This could be a complementary approach of commonly used focused ion beam (FIB) cutting followed by cross-sectional TEM, which only provides onedimensional line information (typically ~100 nm) of the interfacial property.

Furthermore, the intrinsic properties of WSe $_2$  are examined through optical measurement. We have compared the Raman and photoluminescence (PL) spectrums of as-grown WSe $_2$  and after vdW metal integration. As shown in Supplementary Fig. 7, the  $E^1_{ig}$  Raman peak of WSe $_2$  remains at 250.68 cm $^{-1}$  (ref. <sup>45</sup>) and the PL spectrum remains identical before and after the vdW integration process <sup>46</sup>, indicating our vdW integration process won't introduce strains or doping effect to the underlayer 2D semiconductor.

#### vdW integrating various metals on top of WSe<sub>2</sub>

Our vdW metal-2D contact geometry is realized by decomposing the buffer layer, and is not limited to any specific metal properties. Therefore, it could be theoretically applied to any choices of metals, as long as it can be evaporated on top of the PPC buffer. To demonstrate this, we have fabricated vdW metal-WSe2 contact using other metals, including Ag, Al, Ti, Cr, Ni, Cu, Co, Pd, as shown in Fig. 3 and in Supplementary Fig. 8. Importantly, after transistor electrical measurement, all these metals can be further mechanically peeled-off from the WSe2, suggesting the weakly interacted contact without chemical bonding between different vdW metals and underlayer WSe2. As shown in Fig. 3, the WSe<sub>2</sub> under contact regions still demonstrate original shape and optical contrast after the metal peeling processes, suggesting the vdW metal integration processes of these metals are damage-free and residue-free, where the 2D semiconductor could retain its intrinsic properties. This is in great contrast to directly deposition of high-adhesion metals (such as Al, Ti, Cr) on top 2D semiconductors, which could form strong chemical bonding and can not be further separated once deposited.

# Electrical performance $WSe_2$ transistors

To demonstrate the robustness of our vdW contact approach, we have measured the electrical properties of the resulting WSe $_2$  transistors, where highly doped Si substrate is used as the back gate, 300 nm thick SiO $_2$  is used as the gate dielectric, different vdW metals are used as the source drain electrodes. Also, all devices have identical channel length of 50 µm (defined by the stencil mask, see Method), channel thickness of -1.4 nm (bilayer WSe $_2$ ), and varied channel width from 90 µm to 135 µm (depending on the flake size of grown WSe $_2$ ). For comparison, WSe $_2$  transistors fabricated using conventional evaporated contacts are also measured, where identical channel material (WSe $_2$  from same batch of CVD growth) and same device structure are used for fair comparison. As shown in Fig. 4a, b, using Pd as the contact metal,

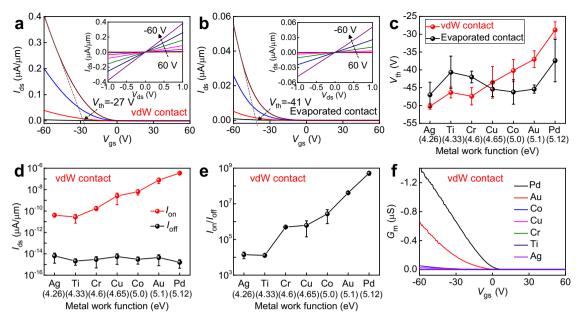

**Fig. 4** | **Electrical performance of WSe<sub>2</sub> transistors using different metal contacts. a, b** The drain source current- gate source voltage  $(I_{\rm ds} - V_{\rm gs})$  transfer curve and drain source current- drain source voltage  $(I_{\rm ds} - V_{\rm ds})$  output curve of WSe<sub>2</sub> transistors with vdW integrated Pd electrodes (a), as well as evaporated Pd

electrodes (**b**). **c**-**e** Extraction of threshold voltage ( $V_{\rm th}$ ) (**c**) on-state current densities (**d**), and current on-off ratios (**e**). Error bars in **c**-**e** are determined from the statistical standard deviations of 5 devices. **f** Transconductance ( $G_{\rm m}$ ) as a function of  $V_{\rm gs}$  with different vdW metals.

devices with both contact approaches exhibit p-type drain source current-gate source voltage ( $I_{\rm ds}$ - $V_{\rm gs}$ ) transfer characteristics with linear drain source current- drain source voltage ( $I_{\rm ds}$ - $V_{\rm ds}$ ) output curve. The major difference is their driving current, where the extracted on-state current ( $V_{\rm gs}$  of -60 V,  $V_{\rm ds}$  of 1 V) of vdW contact is 0.5  $\mu$ A  $\mu$ m<sup>-1</sup>, 7 times higher compared to control sample with deposited contacts. We note the current density (in Fig. 4a, b) is largely limited by the long channel length and small bias voltage, which could be further boosted using shorter channel, thinner gate dielectric or higher bias voltage (Supplementary Fig. 9).

Furthermore, we have systematically measured vdW integrated device as well as directly deposited device using seven different contact metals (Ag, Ti, Cr, Cu, Co, Au, Pd). As shown in Fig. 4c-f and in Supplementary Fig. 10, the electrical properties of vdW-contacted device are highly sensitive to the metal work functions, where higher work function metals lead to larger on-state current densities  $(I_{on})$ , higher on-off ratios  $(I_{on}/I_{off})$ , more positive threshold voltage  $(V_{th})$  and smaller subthreshold swing (SS), consistent with band alignment theory between metal work function and the valance band of p-type WSe<sub>2</sub>. In contrast, for devices contacted with directly evaporated metals, their electrical parameters are relatively insensitive with metals (Supplementary Fig. 10), indicating the strong Fermi level pinning effect during metal evaporation process<sup>18,22-24</sup>. In particular, the two-point transconductance G<sub>m</sub> (with different metals contact) is extracted according  $I_{ds}$ - $V_{gs}$  transfer curve, as shown in Fig. 4f. The extracted highest G<sub>m</sub> is 1.4 μS for vdW contacted (Pd) device, over 7 time higher than control device with evaporated Pd (0.18 µS). Since same channel material is used, the observed better electrical properties could be largely attributed to the optimized contact using our vdW integration with reduced Fermi level pinning effect, consistent with previous reports<sup>25-27</sup>.

To further confirm the optimized contact in our vdW geometry, we have measured the contact resistance ( $R_{\rm C}$ ) of different vdW metals using the transfer length method. As shown in Supplementary Fig. 11, low  $R_{\rm C}$  of 5.3 k $\Omega$ · $\mu$ m and 10.2 k $\Omega$ · $\mu$ m is achieved by vdW integrating high work function Pd and Au, respectively; while vdW integrating low work function metals (Ag and Ti) yields much larger  $R_{\rm C}$  of 27.5 M $\Omega$ · $\mu$ m

and 3.9 MΩ·μm, respectively. Therefore, the metal-dependent electrical properties (such as mobility or  $I_{on}$ ) could be attributed to change of R<sub>C</sub> using different metal and the switching between contact-limited and channel-limited regimes<sup>47</sup>. We also note reducing the  $R_C$  to the IRDS target<sup>34</sup> has been a major focus in 2D research community recent year, and vdW contact geometry has demonstrated promising potential for realizing this target. Currently, the  $R_{\rm C}$  achieved in our method (5.3 k $\Omega$ ·µm) is still much higher than  $R_C$  of previous vdW contact<sup>48,49</sup>, which could be largely attributed to the thick gate dielectric and inferior quality of channel material, and could further improved using thinner dielectrics, as shown in Supplementary Fig. 12. Besides  $R_C$ , the Schottky barrier height ( $\phi_{SB}$ ) could be also measured by varying the measurement temperature (from 300 K to 100 K), and the extracted  $\Phi_{\rm SB}$  are 116 meV, 103 meV, 83 meV, 53 meV, 36 meV, for Ag, Ti, Ni, Co, Pd, respectively (Supplementary Fig. 13). We note although the measured barrier height is linear related to the metal work functions, the slope ( $\phi_{SB}$  vs. metal work function) is far from unity and n-type WSe<sub>2</sub> is still not realized even using low-work function metals, which could be attributed to CVD grown WSe2 with large intrinsic defects and strong p-type doping effect.

### vdW contact for other 2D and 3D bulk semiconductors

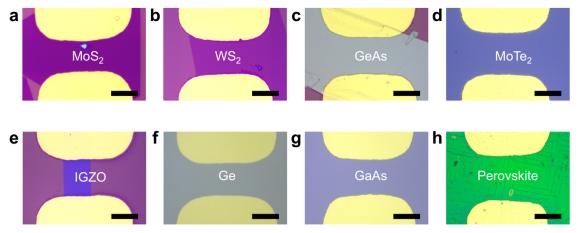

This simple vdW contact approach is not only limited to WSe<sub>2</sub>, but could be well-extended to other 2D semiconductors or 3D bulk semiconductors to achieve vdW metal-semiconductor junction, and to avoid the metal induced damages to the contact region. As shown in Fig. 5, various transistors using this vdW metal contact have been successfully achieved including 2D MoS<sub>2</sub> (Fig. 5a), WS<sub>2</sub> (Fig. 5b), GeAs (Fig. 5c), MoTe<sub>2</sub> (Fig. 5d), as well as 3D amorphous oxide IGZO (indiumgallium-zinc-oxide, Fig. 5e), group IV Ge (Fig. 5f), group Ill–V compound GaAs (Fig. 5g), perovskite microcrystal CsPbX<sub>3</sub> (Fig. 5h). In particular, the electrical properties of 2D p-type semiconductor MoTe<sub>2</sub> and 3D n-type semiconductor IGZO transistors have been systematically measured using different vdW contact metals with distinct work functions. As shown in Supplementary Fig. 14, the vdW contacted devices demonstrate tunable electrical behavior, where the on-state current and  $V_{\rm th}$  are depended on the work function of vdW metals,

**Fig. 5** | **vdW contact integration for other 2D semiconductors and 3D bulk semiconductors. a–d** Optical images of Au electrode pair integrated on top of chemical vapour deposition (CVD)-grown MoS<sub>2</sub> flake (**a**), CVD-grown WS<sub>2</sub> flake (**b**), mechanically exfoliated GeAs flake (**c**) and CVD-grown MoTe<sub>2</sub> thin-film (**d**). **e–h**

Optical images of Au electrode pair integrated on top of amorphous oxide IGZO (e), group IV Ge (f), group III–V compound GaAs (g), and perovskite microcrystal CsPbX $_3$  (h). The scale bar is 40  $\mu$ m.

suggesting the reduced Fermi level pinning effect is a general trend for different semiconductors. This is in great contrast to MoTe<sub>2</sub> and IGZO devices using directly deposited metals, where the electrical behavior is relatively insensitive to the metal work functions, demonstrating strong Fermi level pinning effect, as shown in Supplementary Fig. 14.

In addition, we note the demonstration of vdW metal integration approaches to 3D bulk semiconductor may open up a new avenue for a variety of well-studied semiconductors with delicate lattice, including compound semiconductors, ultra-thin organic thin films/crystals, and the halide perovskite materials. Such materials are usually not stable under high temperature, not compatible with traditional microfabrication processes or are highly prone to degradation during the electrode deposition process. Besides the advantages of device fabrication, vdW integration may provide reduced pinning contacts for other 3D semiconductor (similar as IGZO), which could be used to design devices that require either low contact barrier for efficient carrier injection (e.g., transistors) or high contact barrier for efficient charge separation (e.g., Schottky-based photodetectors).

# Discussion

In summary, we have demonstrated a scalable and universal vdW integration method that can be readily applicable to different metals and semiconductors. Utilizing PPC buffer layer, various metal electrodes could be physically contacted with the 2D semiconductor through a simple dry-annealing process, yield an atomic clean vdW interface. Compared to previous vdW integration (using metal transfer process), our strategy here does not rely on the metal peeling process, and thus could be used to vdW integrate different metals. More importantly, the direct evaporation process on PPC buffer could avoid the air-bubbles or wrinkles during metal transfer process with higher alignment resolutions, especially in wafer-scale. Therefore, various industry-compatible metals could be vdW integrated as the contact of 2D transistors, including Ag, Al, Ti, Cr, Ni, Cu, Co, Au, Pd, exhibiting improved electrical performance depending on the metal work functions.

Furthermore, this dry-decomposed process can be extended to other buffer layers with distinct properties (e.g., polyphthalaldehyde (PPA), polyethylene carbonate, hyperbranched polymers (HB560)), which have been demonstrated to fabricate uniform air-gaps structure in different temperature range. Finally, we have also demonstrated our vdW integration strategy could be well-extended to different 2D semiconductors as well as bulk semiconductors (Ge, GaAs, IGZO, perovskite) with weakly coupled vdW interface. These demonstrations

may intrigue implications for bulk semiconductors that are previously plagued by the high energy metallization process and ill-defined metal-semiconductor contacts, enabling new device structures or high-performance devices.

### **Methods**

# Preparation of CVD-grown 2D semiconductors, perovskite microcrystals, and IGZO thin film

For preparation of WSe<sub>2</sub>, WS<sub>2</sub>, MoS<sub>2</sub>, powder and a piece of SiO<sub>2</sub>/Si substrate (300 nm SiO<sub>2</sub>) were put into the center and downstream end of tube furnace, respectively. After purging out the air and water vapor inside the tube furnace by argon (Ar), large-scale monolayer or bilayer 2D materials were synthesized (at 1170 °C for WSe<sub>2</sub>, 1200 °C for WS<sub>2</sub>, 650 °C for MoS<sub>2</sub>) for 5 min with Ar flow rate of 80 sccm (ref.  $^{50}$ ).

For fabrication of MoTe<sub>2</sub> thin-film, about 3 nm-thick Mo films were firstly evaporated on  $SiO_2/Si$  substrates (300 nm  $SiO_2$ ) through e-beam evaporation. Subsequently, after purging out the air and water vapor inside the tube furnace by Ar, the Mo film are tellurized at the temperature of 550 °C. Finally, about 7 nm-thick MoTe<sub>2</sub> thin-film was synthesized in the downstream end of the tube furnace<sup>51</sup>. For fabrication of perovskite microcrystals, single-step CVD growth of cesium lead halide (CsPbX<sub>3</sub>) microcrystal was conducted<sup>52</sup>.

For preparation of amorphous IGZO, 10 nm-thick channel thin film was deposited on  $SiO_2/Si$  substrates (300 nm  $SiO_2$ ) by using RF magnetron sputtering method. During the sputtering process, the working power was controlled at 50 W under the vacuum pressure of 0.7 Pa with Ar flow rate of 15 sccm.

# Fabrication processes of vdW integration and electrodes peeling-off

Firstly, the poly(propylene carbonate) (PPC) precursor solution with a concentration of 10 wt% was obtained by dissolving PPC polymer into anisole at room temperature. The resulting precursor solution was spin-coated at a speed of 5000 rotations per minute (r.p.m). Then the samples were annealed on the preheated hot plate at 120 °C for 2 min to form a 450 nm-thick film. Next, 60 nm-thick electrodes were evaporated by standard thermal evaporation process under vacuum (pressure ~5 ×  $10^{-4}$  Pa), with the assistance of stencil mask. Finally, the samples were placed on a hot plate in the glove box, and annealed at 250 °C for 30 mins to entirely decompose the PPC film. To peel-off the integrated metal films, PPC precursor solution was spin-costed on top of vdW metal-2D junction at a speed of 3000 r.p.m to wrap the metal electrodes inside. Then the samples were annealed on the preheated

plate at 120 °C for 2 min. At last, PPC film is mechanically peeled-off from 2D materials by using Scotch tape, together with the metal electrodes wrapped. We note that the steel-based stencil mask is used in our process, which typically have a resolution >10  $\mu$ m. This resolution could be further improved to sub- $\mu$ m using polymer-based stencil mask<sup>53</sup>.

#### Electrical measurement and material characterization

The electrical measurements were collected in a Lakeshore PS-100 cryogenic probe station at room temperature in vacuum (pressure ~ $5\times10^{-5}\,\mathrm{mTorr}$ ), using Keysight B2900A source measurement unit (SMU). Raman and PL spectrum measurement (Renishaw invia-reflex) was conducted by using confocal microscope with 488 nm laser as the excitation source.

# Data availability

Relevant data supporting the key findings of this study are available within the article and the Supplementary Information file. All raw data generated during the current study are available from the corresponding authors upon request.

### References

- Radisavljevic, B. et al. Single-layer MoS<sub>2</sub> transistors. Nat. Nanotechnol. 6, 147–150 (2011).

- 2. Fiori, G. et al. Electronics based on two-dimensional materials. *Nat. Nanotechnol.* **9**, 768–779 (2014).

- 3. Kang, K. et al. High-mobility three-atom-thick semiconducting films with wafer-scale homogeneity. *Nature* **520**, 656–660 (2015).

- Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors. Nat. Rev. Mater. 1, 16052 (2016).

- Manzeli, S. et al. 2D transition metal dichalcogenides. Nat. Rev. Mater. 2, 17033 (2017).

- Chang, C. et al. Recent progress on two-dimensional materials. Acta Phys. Chim. Sin. 37, 2108017 (2021).

- Franklin, A. D. Nanomaterials in transistors: from high-performance to thin-film applications. Science 349, aab2750 (2015).

- 8. Waldrop, M. M. The chips are down for Moore's law. *Nature* **530**, 144–147 (2016).

- Akinwande, D. et al. Graphene and two-dimensional materials for silicon technology. *Nature* 573, 507–518 (2019).

- 10. Liu, Y. et al. Promises and prospects of two-dimensional transistors. *Nature* **591**, 43–53 (2021).

- 11. Wu, F. et al. Vertical  $MoS_2$  transistors with sub-1-nm gate lengths. Nature **603**, 259–264 (2022).

- Wang, Y. & Chhowalla, M. Making clean electrical contacts on 2D transition metal dichalcogenides. Nat. Rev. Phys. 4, 101–112 (2022).

- 13. Sequeda, F. O. Thin film deposition techniques in microelectronics. *J. Met.* **38**, 55–65 (1986).

- Lioubtchenko, D. V., Markov, I. A. & Briantseva, T. A. GaAs surface modifications under Au evaporating flux. *Appl. Surf. Sci.* 211, 335–340 (2003).

- Grodzicki, A. et al. Copper(I), silver(I) and gold(I) carboxylate complexes as precursors in chemical vapour deposition of thin metallic films. Coord. Chem. Rev. 249, 2232–2258 (2005).

- Liu, W. et al. Impact of contact on the operation and performance of back-gated monolayer MoS<sub>2</sub> field-effect-transistors. ACS Nano 9, 7904–7912 (2015).

- McDonnell, S., Smyth, C., Hinkle, C. L. & Wallace, R. M. MoS<sub>2</sub>-titanium contact interface reactions. ACS Appl. Mater. Interfaces 8, 8289–8294 (2016).

- Mleczko, M. J. et al. Contact engineering high-performance n-type MoTe<sub>2</sub> transistors. Nano Lett. 19, 6352–6362 (2019).

- Wu, R. J. et al. Visualizing the metal-MoS<sub>2</sub> contacts in twodimensional field-effect transistors with atomic resolution. *Phys. Rev. Mater.* 3, 111001 (2019).

- Smyth, C. M., Addou, R., Hinkle, C. L. & Wallace, R. M. Origins of fermi-level pinning between molybdenum dichalcogenides (MoSe<sub>2</sub>, MoTe<sub>2</sub>) and bulk metal contacts: interface chemistry and band alignment. J. Phys. Chem. C. 123, 23919–23930 (2019).

- Das, S., Chen, H. Y., Penumatcha, A. V. & Appenzeller, J. High performance multilayer MoS<sub>2</sub> transistors with scandium contacts. Nano Lett. 13, 100–105 (2013).

- Kaushik, N. et al. Schottky barrier heights for Au and Pd contacts to MoS<sub>2</sub>. Appl. Phys. Lett. 105, 113505 (2014).

- Kim, C. et al. Fermi level pinning at electrical metal contacts of monolayer molybdenum dichalcogenides. ACS Nano 11, 1588–1596 (2017).

- Kim, G. S. et al. Schottky barrier height engineering for electrical contacts of multilayered MoS<sub>2</sub> transistors with reduction of metalinduced gap states. ACS Nano 12, 6292–6300 (2018).

- Wang, Y. et al. Van der Waals contacts between three-dimensional metals and two-dimensional semiconductors. *Nature* 568, 70–74 (2019).

- Shen, P. C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. *Nature* 593, 211–217 (2021).

- Liu, Y. et al. Approaching the Schottky-Mott limit in van der Waals metal-semiconductor junctions. *Nature* 557, 696–700 (2018).

- Telford, E. J. et al. Via method for lithography free contact and preservation of 2D materials. Nano Lett. 18, 1416–1420 (2018).

- Jung, Y. et al. Transferred via contacts as a platform for ideal twodimensional transistors. Nat. Electron. 2, 187–194 (2019).

- Kong, L. et al. Doping-free complementary WSe<sub>2</sub> circuit via van der Waals metal integration. Nat. Commun. 11, 1866 (2020).

- 31. Liu, L. et al. Transferred van der Waals metal electrodes for sub-1nm MoS<sub>2</sub> vertical transistors. *Nat. Electron.* **4**, 342–347 (2021).

- 32. Li, Q. et al. Low voltage and robust InSe memristor using van der Waals electrodes integration. *Int. J. Extrem. Manuf.* **3**, 045103 (2021).

- 33. Kumar A. et al. in 2021 IEEE International Electron Devices Meeting (IEDM) 7.3.1–7.3.4 (IEEE, 2021).

- 34. IEEE. International Roadmap for Devices and Systems. https://irds.ieee.org/editions/2020 (2020)

- 35. Liu, G. et al. Graphene-assisted metal transfer printing for wafer-scale integration of metal electrodes and two-dimensional materials. *Nat. Electron.* **5**, 275–280 (2022).

- 36. Kwon, G. et al. Interaction- and defect-free van der Waals contacts between metals and two-dimensional semiconductors. *Nat. Electron.* **5**, 241–247 (2022).

- Yan, H., Cannon, W. R. & Shanefield, D. J. Thermal decomposition behaviour of poly(propylene carbonate). *Ceram. Int.* 24, 433–439 (1998).

- 38. Zhong, X. et al. Surface modification of poly(propylene carbonate) by aminolysis and layer-by-layer assembly for enhanced cyto-compatibility. *Colloids Surf.*, B **93**, 75–84 (2012).

- Metz, S., Jiguet, S., Bertsch, A. & Renaud, P. Polyimide and SU-8 microfluidic devices manufactured by heat-depolymerizable sacrificial material technique. *Lab Chip* 4, 114–120 (2004).

- 40. Dang B. et al. Wafer-level microfluidic cooling interconnects for GSI. *IEEE Int. Interconnect Technol. Conf.* 180–182 (2005).

- 41. Joseph, P. J., Monajemi, P., Ayazi, F. & Kohl, P. A. Wafer-level packaging of micromechanical resonators. *IEEE Trans. Adv. Packag.* **30**, 19–26 (2007).

- Spencer, T. J. et al. Air-gap transmission lines on organic substrates for low-loss interconnects. *IEEE Trans. Microw. Theory Techn.* 55, 1919–1925 (2007).

- 43. Lu, J. Y. et al. Terahertz air-core microstructure fiber. *Appl. Phys. Lett.* **92**, 064105 (2008).

- 44. Wang, L. et al. A general one-step plug-and-probe approach to topgated transistors for rapidly probing delicate electronic materials. *Nat. Nanotechnol.* **17**, 1206–1213 (2022).

- Corro, E. D. et al. Excited excitonic states in 1L, 2L, 3L, and bulk WSe<sub>2</sub> observed by resonant raman spectroscopy. ACS Nano 8, 9629–9635 (2014).

- 46. Zhang, Z. et al. Highly selective synthesis of monolayer or bilayer  $WSe_2$  single crystals by pre-annealing the solid precursor. *Chem. Mater.* **33**, 1307–1313 (2021).

- Smets Q. et al. in 2019 IEEE International Electron Devices Meeting (IEDM), 23.2.21–23.2.24 (IEEE, 2019).

- Leong, W. S. et al. Low resistance metal contacts to MoS<sub>2</sub> devices with nickel-etched graphene electrodes. ACS Nano 9, 2071–2079 (2015).

- Wu, R. et al. Bilayer tungsten diselenide transistors with on-state currents exceeding 1.5 milliamperes per micrometre. *Nat. Electron.* 5, 497–504 (2022).

- Zhang, Z. et al. Robust epitaxial growth of two-dimensional heterostructures, multiheterostructures, and superlattices. *Science* 357, 788–792 (2017).

- Xu, X. et al. Seeded 2D epitaxy of large-area single-crystal films of the van der Waals semiconductor 2H MoTe<sub>2</sub>. Science 372, 195–200 (2021).

- Wang, Y. et al. Chemical vapor deposition growth of singlecrystalline cesium lead halide microplatelets and heterostructures for optoelectronic applications. *Nano Res.* 10, 1223–1233 (2017).

- 53. Song, W. et al. High-resolution van der Waals stencil lithography for 2D transistors. Small 17, e2101209 (2021).

### Acknowledgements

Y.L. acknowledge the financial support from National Key R&D Program of China (No. 2021YFA1200503), from the National Natural Science Foundation of China (Grant Nos. 51991340, 51991341, 52221001, U22A2074), and from the science and technology innovation Program of Hunan Province. The authors acknowledge the analytical instrumentation center of Hunan University.

#### **Author contributions**

Y.L. conceived the research. Y.L., L.K., and R.W. designed the experiments. L.K. leads the samples fabrication and electrical characterization. R.W. leads the CVD grown of 2D materials, with the assistance of Y.H. and We.L., Y.C., D.L. contributed to the Raman and PL measurements. S.L. and Y.W. provided the perovskite crystals. Lit.L., Q.T., W.S., Wa.L., Zhe.L., X.L., Y.L. Zhi.L., W.T., S.D., L.M., L.R., Lei.L., X.D. assisted with the

fabrication of the devices and the electrical characteristic measurements. Y.L., and L.K. co-wrote the manuscript. All authors discussed the results and commented on the manuscript.

# **Competing interests**

The authors declare no competing interests.

### **Additional information**

**Supplementary information** The online version contains supplementary material available at https://doi.org/10.1038/s41467-023-36715-6.

**Correspondence** and requests for materials should be addressed to Yuan Liu.

**Peer review information** *Nature Communications* thanks Dennis Lin, Soon-Yong Kwon and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

**Reprints and permissions information** is available at http://www.nature.com/reprints

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

© The Author(s) 2023