Abstract

Recent advancements in the field of electronics have paved the way to the development of new applications, such as tattoo electronics, where the employment of ultraconformable devices is required, typically achievable with a significant reduction in their total thickness. Organic materials can be considered enablers, owing to the possibility of depositing films with thicknesses at the nanometric scale, even from solution. However, available processes do not allow obtaining devices with thicknesses below hundreds of nanometres, thus setting a limit. Here, we show an all-organic field effect transistor that is less than 150 nm thick and that is fabricated through a fully solution-based approach. Such unprecedented thickness permits the device to conformally adhere onto nonplanar surfaces, such as human skin, and to be bent to a radius lower than 1 μm, thereby overcoming another limitation for field-effect transistors and representing a fundamental advancement in the field of ultrathin and tattoo electronics.

Similar content being viewed by others

Introduction

Continuous advancements in the field of ultraflexible electronics and in reducing device thickness have boosted the development of conformable electronic components, serving various applications, spanning from wearable electronics1 to so-called “tattoo electronics” or “skin-laminated electronics”2,3,4. Conformable electronics refers to a class of devices with the ability to adhere onto complex shaped surfaces, adapting their morphology to local details of the target surface (e.g., local roughness)5. This ability strictly relies on both the intrinsic mechanical properties of the adopted materials and the device architecture.

In general, both the conformability and mechanical flexibility of a specific material are determined by its bending stiffness: on the one hand, they can be improved by reducing the Young’s modulus of the material6. On the other hand, since the bending stiffness has a cubic dependence on the material thickness7,8, another typical way to improve conformability and flexibility is to reduce the total thickness. For this reason, most of the reported approaches in the literature for the fabrication of ultraflexible and ultraconformable electronics are based on superthin (few micrometres thick) or ultrathin structures (thickness below 1 μm), according to the definition reported by Nawrocki9.

In this emerging field of conformable devices, organic electronics is one of the most exploited options thanks to the peculiar and intrinsic characteristics of the employed materials, typically hardly achievable with inorganic counterparts10,11. Indeed, organic materials permit the achievement of ultrathin functional nanosheets that are intrinsically soft, flexible and transparent. Moreover, since they can be made solution processable, they are compatible with several large areas and cost-efficient deposition techniques, such as printing12,13,14,15, and require low processing temperatures16,17,18.

Since the substrate typically represents the thickest layer in an electronic device stack, its scaling has mainly driven progress in this context. To date, Parylene C is probably the most employed material as a substrate for the fabrication of superthin and ultrathin devices due to its mechanical properties and the possibility of being deposited through chemical vapour deposition (CVD), controlling its thickness with high precision, down to a few tens of nanometres. Bonfiglio and collaborators reported the first example of organic ultrathin devices, adopting a Parylene C nanosheet as the substrate and gate dielectric to produce freestanding organic field-effect transistors (OFETs)19. Afterwards, analogue structures have been reported for a single-stage amplifier20, multimodal sensor21 and printed logic circuits22,23,24,25.

The works of Takao Someya’s group pushed even further the thickness limit for ultrathin organic transistors. They presented a 270-nm-thick OFET fabricated over Parylene diX-SR, employed as a touch sensor directly onto human skin, able to reach an impressive bending radius of 1.5 μm26.

In addition to the use of Parylene C, alternative insulators have been exploited for superthin and ultrathin organic transistors. For instance, freestanding OFETs fabricated over poly(vinyl alcohol) (PVA)27,28,29,30 and poly-acrylonitrile (PAN) nanosheets have been demonstrated31,32.

In all the reported works so far19,20,21,22,23,24,25,26,27,28,29,30,31,32, the fabrication process requires at least one step in high-vacuum conditions (such as thermal evaporation or CVD). To date, there is no demonstration of ultrathin transistors in which each part of the stack (i.e., substrate, electrodes, semiconductor, gate dielectric) is fully solution processed. The latter approach would greatly simplify fabrication process flows, enabling easier upscaling at reduced costs.

Here, we demonstrate that it is possible to fabricate an all solution-processed OFET with a total thickness <150 nm, which is the thinnest freestanding transistor ever fabricated, by adopting an approach based on solution-assisted delamination of freestanding ultrathin insulating poly(vinyl formal) (PVF) layers employed as a self-standing (or self-supporting) gate dielectric. As a consequence, we also demonstrate the smallest bending radius (0.7 µm) reported thus far for any transistor technology. Due to its ultralow thickness, the device shows high transparency, together with an extremely high level of conformability, and is able to conform on complex 3D surfaces, such as human skin. Such a result pushes even further the boundaries of ultrathin organic electronics towards solution-based and large-area produced imperceptible systems suitable for integration on top of prefabricated objects to make them “smarter” or “connected” without altering their aspect, with simple lamination processes driven by van der Waals forces. In addition to higher mechanical robustness and flexibility, a thinner device implies lower volumes of materials, especially substrates, a critical aspect for the sustainability of electronics conceived to be disposable.

Results

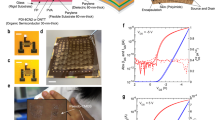

PVF nanosheet fabrication relies on the adaptation of the process originally proposed by Baxamusa’s group (see the “Methods” section for details)33. We use a functionalized silicon wafer over which an ultrathin PVF nanosheet is deposited by spin-coating. The functionalization is based on a subnanometric layer of a poly(diallyldimethylammonium chloride) (PDAC) that strongly adheres to the silicon wafer, establishing a favourable free energy condition that promotes spontaneous delamination of the PVF nanosheet once the wafer is placed in contact with water. Once delaminated, the nanosheet remains well spread out, floating on the water surface due to its strong hydrophobic behaviour. As such, it provides a very flat, homogeneous and robust freestanding dielectric layer. With respect to the dry delamination (or peeling) procedure, the liquid-mediated delamination (or wet delamination) process guarantees lower stresses in the film, and in additional layers eventually deposited on top, since, under the right conditions, it is thermodynamically favoured33. We report the device fabrication strategy in Fig. 1a and the architecture of the realized OFETs in Fig. 1b, c. The latter layout is the result of the coupling of two different ultrathin PVF nanosheets using a multistep fabrication procedure. We refer to them as layer-1 and layer-2, respectively. As the first step, we deposited layer-1 on the silicon wafer (Fig. 1a (i-ii)), and we patterned source and drain electrodes on it by ink-jet printing poly(3,4-ethylenedioxithiophene):polystyrene sulfonate (PEDOT:PSS, Fig. 1a (iii)). These electrodes show a very high level of transparency. As a consequence, connection with external probes for electrical testing results is challenging. To overcome this issue, contact pads were patterned by ink-jet printing a silver nanoparticle-based ink at the extremes of the PEDOT:PSS electrodes. Such electrodes are clearly visible and facilitate the electrical characterization of the transistors. However, they are not required for the correct operation of any transistor presented here. For the organic semiconductor (OSC), we explored different donor-acceptor copolymers, which are representative of a relevant class of solution-processable and printable semiconducting materials, which we patterned onto the electrodes by inkjet printing as well (Fig. 1a (iv)). In particular, we employed both a (poly[2,5-bis(7-decylnonadecyl)pyrrolo[3,4-c]pyrrole-1,4(2H,5H)-dione-(E)-1,2-di(2,2′-bithiophen-5-yl)ethene] (29-DPP-TVT) and 3,6-diketopyrrolopyrrole-alt-5,5-(2,5-di(thien-2-yl)thieno [3,2-b]thiophene) DPP-TTT (data reported in Supplementary Figs. 3–4). In parallel, we prepared layer 2 on another silicon wafer (Fig. 1a (v)). We then proceeded to couple the two layers. In detail, we delaminated layer-1, obtaining a floating freestanding nanosheet with ink-jet printed electrodes and a semiconductor facing upward (see Supplementary Video 1). Afterwards, we recollected floating layer-1 using a plastic ring approaching the nanosheet from the top (Fig. 1a (vi)). At this point, we delaminated the pristine PVF nanosheet (layer-2), recollecting it with the plastic ring carrying freestanding layer-1 (Fig. 1a (vii)). As a result, layer-2 is stacked on top of the dielectric side of layer-1, forming the double-layer gate dielectric of the freestanding OFET. To complete the device, we ink-jet printed the PEDOT:PSS gate electrode directly on top of the freestanding system (Fig. 1a (viii)). It is important to emphasize that we adopted a PVF bilayer as the dielectric to limit the possibility of short circuits from the top printed gate to the bottom layers since single PVF nanosheets could sporadically display microscopic pinholes. By adopting this strategy, the probability of observing a short circuit is drastically reduced, since it is very unlikely for two pinholes of different layers to overlap when two nanosheets are recollected one on top of the other34.

a Fabrication process flow for all-organic ultrathin OFETs: (i) PDAC spin-coating, (ii) layer-1 and layer-2 PVF spin-coating, (iii) ink-jet printing of PEDOT:PSS source/drain electrodes on layer-1, (iv) ink-jet printing of the organic semiconductor onto the electrodes over layer-1, (v) layer-1 and layer 2 delamination in water, (vi) layer-1 recollection on a plastic ring, (vii) recollection of layer-2 on layer-1, (viii), ink-jet printing of PEDOT:PSS gate electrodes. b Lateral view scheme and c overview of the ultrathin all-organic transistors.

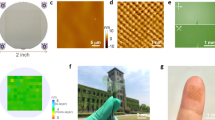

We show a photograph of the assembled freestanding OFET in Fig. 2a, while its optical microscopy picture is reported in Fig. 2b, where colorized areas highlight the different functional parts (source, drain, gate and OSC).

a Photograph of the final freestanding ultrathin OFET arrays suspended on a plastic ring. b Optical microscope image of two freestanding devices (right one colorized for clarity, scale bar 1 mm). Profilometry locations, scanning electron microscopy cross sections and optical spectral measurements (c, e, f) are highlighted by numbered arrows, diamonds and circles, respectively. c Profile measurements of the device in different locations: (I) source-drain channel and organic semiconductor; (II) gate electrode; (III) single PVF dielectric film. d Results of thickness measurement (mean and standard deviation) by profilometry of the different layers and of the overall device in a statistically significant number of samples (10 measurements for the full stack, 10 measurements for the PVF layer, 8 for the source/drain electrodes, 8 for the OSC, 6 for the gate electrode). e Scanning electron microscopy images of the cross section of the device in different positions obtained by focus ion beam etching (sample tilt 52°, scale bar 200 nm): section of the full stack (α), section of dielectric and organic semiconductor (β) and section of only dielectric (γ). f Optical transmission spectra measured in different positions (measurement spot diameter ~300 µm): (1, red line) Ag covered pad transmittance, (2, green line) dielectric layer transmittance, (3, blue line) dielectric layer over bottom gate transmittance, (4, purple line) full stack transmittance; black line is lamp reference signal.

We performed profilometry measurements of each single layer forming the structure (directly on the silicon wafer before delamination) and of the full stack device (after delamination from the wafer). The thickness of a single PVF film layer is ~25 nm, producing an ~50 nm thick dielectric bilayer. The thickness of the bottom gate is less than 70 nm and that of the top source/drain electrodes covered by the semiconductor is ~40 nm, as shown in Fig. 2c. In Fig. 2d, we compare the total thickness statistics obtained both by measuring the full stack and by summing the thickness obtained for each single layer in the stack. The two values are in very good agreement, returning a total device thickness of 143 ± 7 nm, thus qualifying the proposed OFET as the thinnest ever produced. Scanning electron microscopy (SEM) images of the device cross section obtained by means of focused ion beam (FIB) milling further support the thickness analysis (Fig. 2e). The extreme thinness of PEDOT:PSS electrodes and of the semiconductor results in a high transparency of the device, with an overall average transmittance of more than 80% in the visible range for the full stack (see Fig. 2f for the transmittance spectra of the device). The transmittance value can reach 90% considering the weighted average obtained by the transmittance spectra of the different elements of the device and their coverage area, as reported and explained in the Experimental Section. Such a level of transparency exceeds the values obtained with other approaches adopted thus far for ultrathin devices19,20,21,23,24,25,26,27,28,29,30,31,32.

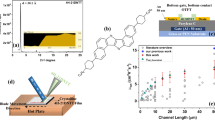

The electrical characterization of the freestanding OFETs is presented in Fig. 3, where we report the data averaged for an array of eight devices. Thanks to the scaling of the gate dielectric thickness, its areal capacitance approaches the value of 60 nF/cm2 (see Supplementary Fig. 5 for the complete impedance measurements), thus allowing the low-voltage operation of the devices in both the linear and saturation regimes, with an average threshold voltage of 0.9 ± 0.2 V in saturation. As appreciable from the average transfer curves with their standard deviation (Fig. 3a–b), the devices have very good reproducibility over the array (see Supplementary Fig. 4 for the raw data). We also verified good run-to-run reproducibility (see Supplementary Fig. 11). Despite the ultrathin dielectric layer, for all the presented transistors, the IGS gate leakage currents are significantly low, with values below 700 pA in the linear regime and below 1 nA at saturation. Furthermore, from the shape of the output characteristic curve (Fig. 3c), it is possible to appreciate the proper operation of the transistor.

Average transfer characteristic curves, with their standard deviation, obtained on eight ultrathin devices based on 29-DPP-TVT in a linear and b saturation regimes. c Typical output characteristic curve for a 29-DPP-TVT-based ultrathin transistor. d Transfer characteristic curve acquired consecutively in ambient air as a function of time for an ultrathin transistor.

We extracted the apparent field‐effect mobility (µ) according to the gradual channel approximation. The average value is 0.092 cm2 V−1 s−1 in the linear regime (with VDS = −2 V) and 0.098 cm2 V−1 s−1 in the saturation regime (with VDS = −6 V) with a VGS (gate voltage) dependence, as shown in Supplementary Fig. 6. We then calculated the effective mobility (µeff) through the formula: µeff = µ × r, where r is the reliability factor, as described by a recent paper by Choi et al.35. Since we obtained high average values for r, reaching 91% in the linear regime and 88% in the saturation regime, the effective mobilities (Supplementary Table 1) were very close to the apparent µ values (Supplementary Table 3; extraction of RC is reported in Supplementary Table 4). Such solid estimation indicates that mobility achieved with ultrathin devices is in line with what has been consistently reported for conventional low-voltage, printed, DPP-TVT-based OFETs36.

Regarding the environmental stability of the devices, which is a fundamental requirement for applications such as wearable and tattoo electronics, we performed a proof-of-principle test by acquiring a transfer curve of a device every 5 min for 25 h while storing it in air under environmental conditions. Such bias conditions represent the typical operation for sensor applications, where the OFET is switched on and off instead of keeping it at a constant and continuous “on” operational state, while the duration of the stability measurement was chosen to simulate a single‐day disposable usage7. It is worth noting that we did not introduce any further encapsulation, and we tested the self-standing OFET in air as a result of the process described above. After 25 h, the device was still operational, as shown in Fig. 3d, denoting only a concurrent increase in both the On and Off currents, which we attribute to mild p-type doping of the OSC due to its direct exposure to oxygen and moisture37.

To investigate the conformability and mechanical flexibility of the devices, we laminated OFET arrays over a prestretched soft polydimethylsiloxane (PDMS) film with a thickness of ~3 mm, as shown in Fig. 4a (for details, see the Methods – Characterization section). The PDMS release induces wrinkles onto the devices (Fig. 4a–b) as a result of the stress at the transistor-elastomer interface originating from the mismatch between the PVF and PDMS Young’s moduli34. The curvature profile for the active area shows that more than 50% of the curvature maxima have a radius <1 μm, while more than 10% have a radius <0.8 μm, with a minimum of 0.7 μm achieved in several spots of the imaged area, as reported in Supplementary Figs. 8–9. We report in Fig. 4c a comparison of the transfer characteristics of a single device before and after PDMS release, while in Supplementary Fig. 12, the statistics for an array of eight devices are reported. Despite sustaining an extremely low bending radius of 0.7 μm, the transistors retain proper operation, and their electrical performance is not significantly affected by the extreme bending condition, thus reducing the previous record by a factor of 2 in the minimum bending radius26. Moreover, conformal adhesion on a nonplanar surface, such as human skin (Fig. 4d), is obtained and demonstrated as a result of reduced bending stiffness38.

a Schematic procedure to induce wrinkling in the ultrathin transistor sample (left) and optical picture of the wrinkled transistor device (right, scale bar 100 µm); the white box indicates the point in which a specific curvature analysis is performed as reported in (b). b Merged optical image, topographic and curvature mapping of a wrinkled sample acquired in the active area of the transistor by optical profilometry at ×150 magnification (scale bar 10 µm); the curvature (K) mapping is calculated by optical profilometry data (details in Supplementary Figs. 8–9). c Transfer characteristic curves for an ultrathin device in saturation mode when recollected on a prestretched PDMS substrate (flat sample, black line) and after PMDS relaxation, which induces strong buckling on the surface (wrinkled sample, red lines). d A film sample containing an array of devices adhering to the skin to demonstrate conformal adhesion and a high level of transparency.

In conclusion, we have successfully fabricated ultraflexible, sub-150-nm-thick, all-organic field-effect transistors based on an ultrathin solution-processable dielectric bilayer, adopting only solution-based techniques, such as spin-coating and inkjet printing. The devices can operate at low voltage and, thanks to their very low thickness, can conform to human skin in an imperceptible way and sustain bending radii as low as 0.7 μm, without significant variations in their electrical performance, thus setting a new limit in thickness and conformability. Moreover, as shown in Fig. 5 and Supplementary Table 4, in which we summarized the state-of-the-art ultrathin field-effect transistors, this is the first demonstration of ultrathin (<1 μm) fully solution-processable transistors, including the substrate. The electrical characterization showed very good reproducibility, demonstrating the solidity of the proposed fabrication process, and the stability test in air makes the devices in principle compatible with single-day, disposable usage. Furthermore, the employed materials and their very low thickness guarantee a high transparency. In addition to providing an alternative and valid technological solution for the fabrication of ultrathin devices, the proposed approach can be a candidate for a plethora of possible uses ranging from wearable to tattoo/epidermal electronics for sensing, health care or biomedical applications where conformability, ultraflexibility and transparency are necessary.

Methods

PVF nanosheets preparation

Poly(vinyl formal) (PVF) was purchased from SPI Supplies (trade name Vinylec E Polyvinyl Formal Resin). Ethyl lactate (EL, ≥ 98%, Food Chemical Codex, Food Grade) and poly(diallyl dimethylammonium chloride) (PDAC, 20% wt in water solution) were purchased from Sigma–Aldrich. Si wafers (3 inches diameter and 381 ± 25 µm thick) used for PVF nanosheet fabrication were purchased from Silicon Materials (Si-Mat). Commercial poly(methyl methacrylate) (PMMA)—Clear Astariglas® Acrylic sheet (made from 100% virgin MMA (methyl methacrylate monomer), light transmission 92%, thermal expansion 2.1 mm/m)—was purchased as 0.3 cm × 40 cm × 55 cm slabs and cut into rings with internal and external diameter of 12 mm and 18 mm, respectively. A PDAC solution (0.5% wt) was prepared by diluting the commercial 20% wt water solution with deionized water. It was stirred for 15 min immediately before its use. PVF solution (1% wt) was prepared by dissolving PVF in EL by stirring at 650 rpm and at 50 °C overnight. Immediately before use, the PVF solution was heated using a water bath at 50 °C and stirred at 650 rpm to prevent potential polymer aggregate formation. The silicon wafer surface was washed with acetone as a first step and then with isopropanol. Thereafter, the wafer was exposed to O2 plasma for 120 s (O2 pressure 0.4 mbar, power 100 W, Plasma Asher model Femto, Diener Electronic) to improve its wettability. Immediately after, the wafer was functionalized with a subnanometric PDAC layer by spin coating ~2 ml of PDAC solution at 4000 rpm for 15 s, followed by soft baking of the film at 100 °C for 10 s on a hotplate. PDAC excess was rinsed with deionized water. PVF solution was spin-coated on the PDAC layer in a two-step process for a total duration of 10 s: the first 5 s at 300 rpm and the last 5 s at 3000 rpm. Approximately 2 mL of solution was deposited for each PVF nanosheet spinning session. The PVF nanosheet was then baked for 60 s at 50 °C on a hotplate to remove the excess solvent.

Ultra-thin OFETs

Bottom contact OFETs were fabricated employing PEDOT:PSS (Clevios PJ700 formulation, purchased from Heraeus) as source, drain and gate contacts patterned by means of ink-jet printing using a Fujifilm Dimatix DMP2831 through a cartridge with 10 pL nozzles. The source and drain were printed at a drop spacing of 45 μm (one layer), a firing voltage of 40 V, a jetting frequency of 1 kHz and a printer plate temperature of 28 °C. The gate electrode was printed at a drop spacing of 40 μm (one layer), a firing voltage of 40 V, a jetting frequency of 1 kHz and a printer plate temperature of 28 °C. No annealing of the electrodes was performed. The channel width was set to 1 mm, while the channel length was 100 μm. The total area of each transistor is 1 × 10−3 mm2.

As reported in Fig. 2d, these devices show a very high level of transparency, thus making it difficult to identify source and drain contacts without the help of visible elements. For this reason, contact pads were patterned by ink-jet printing a silver nanoparticle-based ink (Silverjet DGP-40LT-15C, purchased from Advanced Nano Products) with the scope of providing a visible element and facilitating the electrical characterization of the transistors. The area of each pad is 440 × 440 μm2. Silver pads are quite far (~1.2 mm) from the active area of the devices and are not required for the correct operation of any transistors presented here.

Poly[2,5-bis(7-decylnonadecyl)pyrrolo[3,4-c]pyrrole-1,4(2H,5H)-dione-(E)-1,2-di(2,2′-bithiophen-5-yl)ethene] was synthesized according to Yu et al.39 while 3,6-diketopyrrolopyrrole-alt-5,5-(2,5-di(thien-2-yl)thieno [3,2-b]thiophene) was synthesized using the method explained by Chen et al.40. They have been used as p-type OSCs patterned by means of inkjet printing using a Fujifilm Dimatix DMP2831. Both semiconductors were printed from a 1,2-dichlorobenzene-based solution at a concentration of 2.5 mg ml−1 through a cartridge with 10 pL nozzles. OSCs were printed at a drop spacing of 50 μm (one layer), a firing voltage of 35 V, a jetting frequency of 1 kHz and a printer plate temperature of 28 °C. No annealing of the OSCs was performed.

Freestanding ultra-thin OFET assembly

First, an array composed of eight source/drain electrodes and the OSC filling the channel was ink-jet printed over a PVF nanosheet (layer-1) before delamination from the silicon wafer. Using a surgery blade, we cut squares of layer-1 and a second PVF nanosheet (layer-2) with suitable dimensions to fit the PMMA ring used for the recollection (internal and diameter 12 mm, external diameter 18 mm). Layer-1 and layer-2 were recollected on top of each other (see Supplementary Video 1). A common gate electrode was ink-jet printed to simultaneously print the gate for all 8 devices.

Characterization

We performed electrical characterization (transfer curves and output curves) of the transistors in an air atmosphere using an Agilent B1500A semiconductor parameter analyser.

PVF nanosheet thickness characterization was performed by means of a mechanical profilometer (Alpha Step-IQ, KLA-Tencor).

Optical microscopic images were acquired by means of a Leica DCM 3D confocal profilometer at ×10 magnification, with multiple image stitching options. The transmission spectra average was obtained by the weighted transmission of different areas of each element of one device (transmission spectra × coverage area), as follows:

-

[PVF] 92% transmission spectra × 72% coverage area;

-

[PEDOT:PSS + PVF] 87% transmission spectra × 15.5% coverage area;

-

[full stack] 82.5 transmission spectra × 12.5% coverage area.

For each curve, averaging was performed in the range of 400–750 nm.

FIM-milled cross-sections and SEM imaging of the ultrathin organic transistor were obtained with a Dual Beam FIB/SEM Helios Nano-Lab 600i (FEI). SEM images of cross-sections were obtained under a sample tilt angle of 52° (accelerating voltage 10 kV).

PVF nanosheet capacitance was extracted using an Agilent 4294 A Impedance Analyzer with a two-probe configuration. The samples were tested in a frequency range from 40 Hz to 1 MHz, applying a signal with a 500 mV amplitude. The capacitors were fabricated by using a couple of 25-nm-thick layers of PFV joined together. The resulting 50-nm-thick PVF layer was sandwiched between two PEDOT:PSS electrodes printed on the outer part of the PVF layer. The parallel plates have an overlapping area of 0.58 mm2.

The mechanical tests were performed by laminating the array of transistors over a prestretched PDMS, which was stretched at 5% before transferring the devices on it. To provide uniform extension, we used metallic clamps. The clamps were 3 cm in width, larger than the PDMS slab, which has a width of ~2 cm. The slab was then fixed at the corresponding 5% extension point using Kapton tape.

The study was performed following the principles outlined in the Helsinki Declaration of 1975, later revised in 2000. All participants signed an informed consent form before the experimental activity began after being informed about the aims and procedures of the experiments.

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

References

Gong, S. et al. A wearable and highly sensitive pressure sensor with ultrathin gold nanowires. Nat. Commun. 5, 3132 (2014).

Kim, D.-H. et al. Epidermal electronics. Science 333, 838 LP–838843 (2011).

Jeong, J.-W. et al. Materials and optimized designs for human-machine interfaces via epidermal electronics. Adv. Mater. 25, 6839–6846 (2013).

Kaltenbrunner, M. et al. An ultra-lightweight design for imperceptible plastic electronics. Nature 499, 458–463 (2013).

Zucca, A. et al. Tattoo conductive polymer nanosheets for skin-contact applications. Adv. Healthc. Mater. 4, 983–990 (2015).

Zhao, D. et al. Engineering intrinsic flexibility in polycrystalline molecular semiconductor films by grain boundary plasticization. J. Am. Chem. Soc. 142, 5487–5492 (2020).

Nawrocki, R. A. et al. Self-adhesive and ultra-conformable, sub-300 nm dry thin-film electrodes for surface monitoring of biopotentials. Adv. Funct. Mater. 28, 1803279 (2018).

Kim, D.-H. et al. Dissolvable films of silk fibroin for ultrathin conformal bio-integrated electronics. Nat. Mater. 9, 511–517 (2010).

Nawrocki, R. A. Super- and ultrathin organic field-effect transistors: from flexibility to super- and ultraflexibility. Adv. Funct. Mater. 29, 1–12 (2019).

Kim, D.-H. et al. Ultrathin silicon circuits with strain-isolation layers and mesh layouts for high-performance electronics on fabric, vinyl, leather, and paper. Adv. Mater. 21, 3703–3707 (2009).

Mack, S., Meitl, M. A., Baca, A. J., Zhu, Z.-T. & Rogers, J. A. Mechanically flexible thin-film transistors that use ultrathin ribbons of silicon derived from bulk wafers. Appl. Phys. Lett. 88, 213101 (2006).

Arias, A. C., MacKenzie, J. D., McCulloch, I., Rivnay, J. & Salleo, A. Materials and applications for large area electronics: solution-based approaches. Chem. Rev. 110, 3–24 (2010).

de Gans, B.-J., Duineveld, P. C. & Schubert, U. S. Inkjet printing of polymers: state of the art and future developments. Adv. Mater. 16, 203–213 (2004).

Viola, F. A. et al. A 13.56 MHz rectifier based on fully inkjet printed organic diodes. Adv. Mater. 32, 1–7 (2020).

Park, K. S. et al. Inkjet-assisted nanotransfer printing for large-scale integrated nanopatterns of various single-crystal organic materials. Adv. Mater. 28, 2874–2880 (2016).

Barsotti, J. et al. Ultrathin, ultra-conformable, and free-standing tattooable organic light-emitting diodes. Adv. Electron. Mater. 7, 2001145 (2021).

Cosseddu, P. et al. Tactile sensors with integrated piezoelectric polymer and low voltage organic thin-film transistors. Proc. IEEE Sensors 2014-Decem, 1734–1736 (2014).

Wang, Y. et al. A highly stretchable, transparent, and conductive polymer. Sci. Adv. 3, e1602076 (2017).

Cosseddu, P., Piras, A. & Bonfiglio, A. Fully deformable organic thin-film transistors with moderate operation voltage. IEEE Trans. Electron Devices 58, 3416–3421 (2011).

Lai, S. et al. Ultra-conformable Organic Field-Effect Transistors and circuits for epidermal electronic applications. Org. Electron. 46, 60–67 (2017).

Viola, F. A., Spanu, A., Ricci, P. C., Bonfiglio, A. & Cosseddu, P. Ultrathin, flexible and multimodal tactile sensors based on organic field-effect transistors. Sci. Rep. 8, 1–8 (2018).

Stucchi, E., Scaccabarozzi, A. D., Viola, F. A. & Caironi, M. Ultraflexible all-organic complementary transistors and inverters based on printed polymers. J. Mater. Chem. C 8, 15331–15338 (2020).

Fukuda, K. et al. Fully-printed high-performance organic thin-film transistors and circuitry on one-micron-thick polymer films. Nat. Commun. 5, 5–12 (2014).

Takeda, Y. et al. Fabrication of ultra-thin printed organic TFT CMOS logic circuits optimized for low-voltage wearable sensor applications. Sci. Rep. 6, 1–9 (2016).

Fukuda, K. et al. Free-standing organic transistors and circuits with sub-micron thicknesses. Sci. Rep. 6, 1–9 (2016).

Nawrocki, R. A., Matsuhisa, N., Yokota, T. & Someya, T. 300-nm Imperceptible, ultraflexible, and biocompatible e-skin fit with tactile sensors and organic transistors. Adv. Electron. Mater. 2, 2–5 (2016).

Ren, H., Tang, Q., Tong, Y. & Liu, Y. 320-Nm flexible solution-processed 2,7-Dioctyl[1] benzothieno[3,2-B]benzothiophene transistors. Materials 10, 1–9 (2017).

Zhou, J., Liu, Y., Shi, Y. & Wan, Q. Solution-processed chitosan-gated IZO-based transistors for mimicking synaptic plasticity. IEEE Electron Device Lett. 35, 280–282 (2014).

Liu, M. et al. Ultrathin free-substrate n-type PTCDI-C13 transistors with bilayer polymer dielectrics. IEEE Electron Device Lett. 39, 1183–1186 (2018).

Ren, H. et al. High-performance, ultrathin, ultraflexible organic thin-film transistor array via solution process. Small 14, 1–8 (2018).

Ji, X. et al. Smart surgical catheter for C-reactive protein sensing based on an imperceptible organic transistor. Adv. Sci. 5, 1–8 (2018).

Zhang, L. et al. Substrate-free ultra-flexible organic field-effect transistors and five-stage ring oscillators. Adv. Mater. 25, 5455–5460 (2013).

Baxamusa, S. H. et al. Enhanced delamination of ultrathin free-standing polymer films via self-limiting surface modification. Langmuir 30, 5126–5132 (2014).

Barsotti, J. et al. Ultraconformable freestanding capacitors based on ultrathin polyvinyl formal films. Adv. Electron. Mater. 4, 1–9 (2018).

Choi, H. H., Cho, K., Frisbie, C. D., Sirringhaus, H. & Podzorov, V. Critical assessment of charge mobility extraction in FETs. Nat. Mater. 17, 2–7 (2017).

Stucchi, E., Dell’Erba, G., Colpani, P., Kim, Y.-H. & Caironi, M. Low-voltage, printed, all-polymer integrated circuits employing a low-leakage and high-yield polymer dielectric. Adv. Electron. Mater. 4, 1800340 (2018).

Lee, J. H. et al. Semiconducting/insulating polymer blends with dual phase separation for organic field-effect transistors. RSC Adv. 7, 7526–7530 (2017).

Ferrari, L. M., Taccola, S., Barsotti, J., Mattoli, V. & Greco, F. Organic Flexible Electronics - Chapter 15. (Elsevier, 2020).

Yu, H. et al. Effect of the alkyl spacer length on the electrical performance of diketopyrrolopyrrole-thiophene vinylene thiophene polymer semiconductors. J. Mater. Chem. C 3, 11697–11704 (2015).

Chen, Z. et al. High-performance ambipolar diketopyrrolopyrrole-thieno[3,2-b]thiophene copolymer field-effect transistors with balanced hole and electron mobilities. Adv. Mater. 24, 647–652 (2012).

Acknowledgements

This work has been in part financially supported by the Italian Ministry for Economic Growth through the project PON Fesr 2017/2020 “Organic Smart Label for IoT” (cup B38I170000200008) and by the National Research Foundation of Korea (NRF) (2018R1A2A1A05078734). F.A.V. and M.C. acknowledge partial support under the European Union’s Horizon 2020 Research and Innovation Programme “Electronic Smart Systems - SiMBiT: Single molecule bio-electronic smart system array for clinical testing”, grant agreement number 824946. The fabrication of the devices was partially carried out at PoliFab, the micro- and nano-technology center of the Politecnico di Milano.

Author information

Authors and Affiliations

Contributions

F.A.V. and J.B. contributed equally to this work. F.A.V. and J.B. conceived the idea of ultrathin all solution processable transistors and designed and carried out the electrical characterization of the devices. They also performed data analysis and statistics for all the electrical and thickness measurements. F.M. carried out the impedance measurements. Y.-H.K. synthesized the organic semiconductors. V.M. carried out the scanning electron microscopy cross sections, optical spectral measurements and optical images. He also analysed the topography and curvature mapping of wrinkled samples, produced graphical elements and arranged the figures. G.L., V.M. and M.C. supervised the entire work and discussed the experimental results. F.A.V., J.B., V.M. and M.C. wrote the manuscript equally. All the authors read and revised the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Peer review information Nature Communications thanks Robert A. Nawrocki and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Viola, F.A., Barsotti, J., Melloni, F. et al. A sub-150-nanometre-thick and ultraconformable solution-processed all-organic transistor. Nat Commun 12, 5842 (2021). https://doi.org/10.1038/s41467-021-26120-2

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-021-26120-2

This article is cited by

-

Fully 3D-printed organic electrochemical transistors

npj Flexible Electronics (2023)

-

Retina-inspired organic neuromorphic vision sensor with polarity modulation for decoding light information

Light: Science & Applications (2023)

-

270 nm ultra-thin self-adhesive conformable and long-term air-stable complimentary organic transistors and amplifiers

npj Flexible Electronics (2023)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.