Abstract

Superconducting computing promises enhanced computational power in both classical and quantum approaches. Yet, scalable and fast superconducting memories are not implemented. Here, we propose a fully superconducting memory cell based on the hysteretic phase-slip transition existing in long aluminum nanowire Josephson junctions. Embraced by a superconducting ring, the memory cell codifies the logic state in the direction of the circulating persistent current, as commonly defined in flux-based superconducting memories. But, unlike the latter, the hysteresis here is a consequence of the phase-slip occurring in the long weak link and associated to the topological transition of its superconducting gap. This disentangles our memory scheme from the large-inductance constraint, thus enabling its miniaturization. Moreover, the strong activation energy for phase-slip nucleation provides a robust topological protection against stochastic phase-slips and magnetic-flux noise. These properties make the Josephson phase-slip memory a promising solution for advanced superconducting classical logic architectures or flux qubits.

Similar content being viewed by others

Introduction

A Josephson junction (JJ) consists of a localized discontinuity (weak link) in the order parameter of two superconducting electrodes1, where the dissipationless current ruled by the Cooper pairs transport is controlled by the macroscopic quantum phase difference (φ) across the junction. Weak links are typically realized in the form of a thin insulator, a semiconductor or metallic wire, or a narrow superconducting constriction1,2. The junction current-phase relation (CPR) strongly depends on the structural attributes of the constriction, i.e., on how its effective length (L, i.e., the distance between the superconducting leads), width (w), and thickness (t) compare with the superconducting coherence length (ξw)2. In a fully superconducting one-dimensional JJ (w, t ≪ ξw) the CPR evolves from the single-valued distorted sinusoidal characteristic, typical of the short-junction limit (L ≪ ξw Fig. 1a) and of non-superconducting weak links, to the multi-valued function obtained in the long regime (L ≫ ξw, Fig. 1b)2. In the latter scenario, multiple (odd) solutions are available to the system at fixed φ, and the steady state will depend on the history of φ. In the specific example of Fig. 1b, three solutions are possible for the Josephson current (Is) at φ close to π. Two of them are energetically stable, they correspond to two local minima in the Josephson energy3 and are topologically discriminated by the parity of the winding number of the superconducting phase along the wire4,5 which reflects into two opposite directions of IS(φ)6, as indicated in Fig. 1b by the even (red) and odd (blue) branches of Is. In order to switch between these two stable branches, a 2π slippage of the superconducting phase along the weak link is required. The slippage passes through the third backward solution in the CPR, a metastable state which corresponds to a saddle point in the Josephson energy separating the two stable minima and forming the barrier of a double-well potential. In analogy with the physics of topological insulators, this intermediate metastable state is gapless, and is associated with the formation of a phase-slip center in the middle of the junction3,7. The large superconducting condensation energy lost in this gapless center is at the origin of the strong phase-slip energy barrier separating the two topological branches. We take advantage of this topologically protected double-well potential to implement a robust and permanent superconducting memory: The Josephson phase-slip memory (PSM). Differing from similar quantum phase-slip memories8, the geometry of the PSM has been conceived for deterministic control of the state via an external magnetic field, while stochastic quantum or thermally-activated phase slips are exponentially suppressed. As described below, these events are negligible thanks to the low resistance of the nanowire RN < RqL/ξw, where Rq = h/e2 = 6.5 kΩ9.

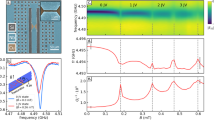

a, b Sketch of the current-phase relation (CPR, Is(φ)) for a S-S′-S weak link (schemed on top) in the short a and long b junction regime. The CPR (yellow curve) evolves from a deformed sinusoid to a multi-valued function as the junction length increases. In the latter, the transition between the two topologically protected states, corresponding to even and odd topological index4, occurs via phase-slips in the wire2,31 and corresponds to the vertical jump indicated by the colored arrows between the two current branches (red and blue). c, d Dependence of the tunnel current (I) on the normalized applied magnetic flux (Φ/Φ0, with Φ0 = h/2e ≃ 2*10−15 Wb the flux quantum), at fixed bias voltage (V) for a SQUIPT in the short c and long d junction regime. In the latter case, the current evolution shows a hysteretic profile (red and blue curves), which stems from the multi-valued CPR. Top: scheme of a voltage-biased DC SQUIPT in a two-wire configuration. Φ is the magnetic flux piercing the ring. e Pseudo-color scanning electron micrograph of a typical PSM. An Al nanowire (green) is inserted in a micron-size Al ring (yellow), whereas an Al0.98Mn0.02 probing electrode (red) is tunnel-coupled to the middle of the nanowire and to a second Al electrode (green) via an insulating oxide layer (gray) to allow the memory operation. Inset: blow-up of the weak-link region. The passive replicas due to the three-angle shadow-mask metal deposition are visible. f Schematic top-view and cross-section of the device.

Results

Implementation of the memory cell

The design of a proof-of-concept PSM requires an architecture enabling the tuning of the superconducting phase and the definition of an efficient readout scheme. To finely control φ, the JJ is inserted in a superconducting loop, where an external magnetic field gives rise to a total flux (Φ) piercing the ring area. Stemming from fluxoid quantization10, the superconducting phase difference across the weak link is given by φ = 2πΦ/Φ0 (where Φ0 ≃ 2.067 × 10−15 Wb is the flux quantum) while the phase drop along the loop is negligible (see “Methods” section for details). The phase difference, together with the topological index, determines the amplitude of the superconducting gap in the local density of states (DOS) of the wire9, which can be probed by a metallic electrode tunnel-coupled to the middle of the junction, thereby implementing a superconducting quantum interference proximity transistor (SQUIPT)11, as sketched on top of Fig. 1c. As a result, at fixed Φ the amplitude of the tunneling current (I) flowing through the probing electrode will depend on the even/odd parity of the topological index of the junction codifying the logic [0] and [1] states of the PSM cell (Fig. 1d). Encoding the memory state in the parity of the winding number is a common feature to all flux-based superconducting memories, including, e.g., nano-SQUIDs12,13 flux qubits14 or kinetic-inductance memories15 from which it shares the low dissipation and high operation speeds. But, differing from the latter approaches, the dynamics of the memory cell here is entirely dominated by the physics of the weak link. The readout in the SQUIPT is based on tunneling spectroscopy of the weak link and the hysteresis in the magnetic flux is not a consequence of an unbalance between the ring and junction inductance but is an intrinsic property of the CPR.

The scanning electron micrograph (SEM) of a representative PSM cell is shown in Fig. 1e together with a top-down and cross-section scheme in Fig. 1f. Realized through a suspended-mask lithography technique (see “Methods” for fabrication details), the weak link consists of a one-dimensional Al nanowire (green, t = 20 nm and w = 90 nm) with a length L ~ 400 nm, embedded in a micron-sized 70-nm-thick Al ring (yellow). In addition, a 15-nm-thick normal metal electrode (red, Al0.98Mn0.02) is tunnel-coupled to the center of the wire (with a normal-state tunnel resistance Rt1 ≃ 65 kΩ). To measure the tunneling current, a second Al lead (green) is tunnel-coupled to the normal metal electrode (with a normal-state resistance Rt2 ≃ 90 kΩ)16. Based on the device structural parameters, we estimate the ratio L/ξw,0 ≃ 6, where ξw,0 ≃ 65 nm is the zero-temperature coherence length17, thereby providing the frame of the long-junction regime2,9 (see “Methods” for details). Within these geometrical constrains and thanks to the low resistivity of Al (ρ < Rqξw), both quantum and thermally-activated phase slips are negligibly small, with rates < 10−289 Hz (see “Methods” for more details on the estimate). Notably, the PSM is completely made of aluminum compounds thus ensuring high-quality tunnel barriers and full compatibility of all fabrication steps for industrial scaling.

Magneto-electric response

To test the PSM transport properties and assess the operation parameters of the memory cell, we first performed a preliminary magneto-electric characterization at bath temperature T = 25 mK. Figure 2a shows the current vs voltage characteristics (I(V)) of a typical device measured at Φ = 0 (black curve) and Φ = Φ0/2 (orange curve). At zero magnetic flux, the quasiparticle tunnel current is suppressed for ∣V∣ ≲ 400 μV due to the presence of two S-I-N tunnel junctions in series and is consistent with the Al gap of ≃200 μeV for both the readout lead (ΔAl) and the weak link (Δw(Φ = 0)). The latter can be modulated by the external magnetic flux11,16, showing a reduction of about 50% at Φ = Φ0/2 (orange line), Δw(Φ = Φ0/2) ≃ 100 μeV (see also Supplementary Fig. 1 for more details).

a Current vs voltage characteristics acquired at Φ = 0 (black trace) and Φ = Φ0/2 (orange trace). The magnetic flux modulates Δw and, therefore, the I − V tunnel characteristics. b I(Φ) of a typical memory cell biased at V = 300 μV. The purple and green arrows indicate the magnetic flux sweep directions. The width of the hysteretic loop (δΦ), the current drop (δI), and the current at the hysteresis crossing point (Icp = I(Φ0/2)), are also indicated. c Evolution of I(Φ) acquired for selected values of V, as indicated by the colored arrows in a. Icp increases by rising V. d Dependence of the hysteresis width (δΦ) on V. δΦ monotonically drops by increasing V. e Relative variation of the tunneling current (ζ = δI/Icp) vs V. All these measurements were taken at T = 25 mK.

Differently from short-junction SQUIPTs16,18, the I(Φ) characteristic is not only Φ0-periodic, but it is also strongly hysteretic in Φ. This is highlighted in Fig. 2b, where the tunnel current measured at V = 300 μV as a function of increasing (purple trace) and decreasing (green trace) magnetic flux is shown. The forward trace exhibits periodic maxima followed by sudden jumps corresponding to the nucleation of a phase-slip center in the superconducting nanowire2,7,9. Accordingly, the backward trace evolves in a totally specular fashion. The evolution of I(Φ) on the bias voltage is shown in Fig. 2c. The hysteresis loop drawn by the back and forth I(Φ) exhibits a reduction of its width (δΦ) by increasing V, as quantified also in Fig. 2d. This trend can be ascribed to a local overheating in the weak link induced by the quasiparticle current flowing through the probing junction which enlarges ξw(T)1 thereby deviating the CPR towards the single-valued non-hysteretic form2,9. The relative separation between the two I(Φ) branches can be quantified by a parameter (ζ) defined as the ratio between the current drop at the phase-slip transition and the current at the hysteresis crossing point, ζ = δI/I(Φ = nΦ0/2), where n is an integer odd number. A large ζ improves the visibility of the PSM logic states. Similarly to δΦ, the increase of V induces a monotonic reduction of ζ, as shown in Fig. 2e.

Memory operation with DC readout

The typical operation cycle of the PSM memory cell is sketched in Fig. 3a. A bias flux (ΦB) is required to access the multi-valued state enclosed within the hysteretic domain (\({{{\Phi }}}_{{{{{{{{\rm{B}}}}}}}}\_\min }=({{{\Phi }}}_{0}-\delta {{\Phi }})/2,{{{\Phi }}}_{{{{{{{{\rm{B}}}}}}}}\_\max }=({{{\Phi }}}_{0}+\delta {{\Phi }})/2\)). Writing (erasing) operations are performed by lowering (increasing) the total flux below (above) the hysteretic domain by means of short pulses. As a consequence, the parity of the topological index switches between odd and even and the tunneling current between low and high current state. Figure 3b shows a real-time writing/erasing operation in the continuous-read mode, i.e., with a fixed a bias voltage V = 300 μV. The bias flux is set at 0.54Φ0, just above the crossing point of the hysteresis to avoid degeneracy in the current amplitude (Fig. 2c). The memory is then initialized in the [0] state corresponding to a current I ≃ 43 pA. By applying a negative flux pulse down to ΦW = 0.33Φ0, the PSM logic state suddenly transits to [1] as detected by the current jump to I ≃ 90 pA. Conversely, the logic state [0] is recovered via a positive erasing flux pulse up to ΦE = 0.75Φ0. The device unequivocally shows the typical behavior of a memory cell upon many erasing/writing cycles. From the real-time characteristic is also possible to quantify the energy required for the writing/erasing operations. This can be estimated from the energy difference of the system in the two flux configurations that can be simplified in \(E({{{\Phi }}}_{{B}_{{{max}}},{B}_{{{min}}}})-E({{{\Phi }}}_{0})\simeq \frac{{{{\Phi }}}_{0}}{2{{{{{{{{\mathcal{L}}}}}}}}}_{{{{{{\mathrm{K}}}}}}}}\frac{\delta {{\Phi }}}{2}\), where \({{{{{{{{\mathcal{L}}}}}}}}}_{{{K}}}\) is the kinetic inductance of the JJ8. In our experimental configuration, the estimated energy is ~0.1 eV, which is consistent with the predictions for the energy of the topological barrier \(U \sim {{{\Delta }}}_{{{{{w}}}}}\frac{\hslash }{{e}^{2}{R}_{{{N}}}}\frac{L}{{\xi }_{{{w}}}}\)9. Notably, differing from conventional flux-based superconducting memories, the inductance of the PSM ring is not relevant for the device which can be made negligibly small without any loss of hysteresis or functionality. This allows the miniaturization of the PSM that could be further operated with a flux generated by supercurrents directly injected in a small portion of the superconducting ring19, therefore eliminating the requirement of an external magnetic field but with the disadvantage of an additional feed line integrated in the device.

a Sketch of the memory operation principle at a constant voltage bias (V). Low (blue, I[0]) and high (red, I[1]) current branches at the bias flux (\({{{\Phi }}}_{{{{{{{{\rm{B}}}}}}}}}\in ({{{\Phi }}}_{0}/2,{{{\Phi }}}_{{{{{{{{\rm{B}}}}}}}}\_\max })\)) encode the [0] and [1] logic states, respectively. The erase (write) operation is performed by applying a flux pulse with amplitude \({{{\Phi }}}_{{{{{{{{\rm{E}}}}}}}}} > {{{\Phi }}}_{{{{{{{{\rm{B}}}}}}}}\_\max }\) (\({{{\Phi }}}_{{{{{{{{\rm{W}}}}}}}}} < {{{\Phi }}}_{{{{{{{{\rm{B}}}}}}}}\_\min }\)). The memory can also be operated in the complementary part of the hysteresis at \({{{\Phi }}}_{{{{{{{{\rm{B}}}}}}}}}\in ({{{\Phi }}}_{{{{{{{{\rm{B}}}}}}}}\_\min },{{{\Phi }}}_{0}/2)\) by exchanging the erase and write fluxes. b Evolution of the readout tunneling current (top panel) measured at V = 300 μV for Φ composed by a bias flux ΦB = 0.54Φ0 (yellow trace) interrupted by writing (ΦW = 0.33Φ0, red) and erase (ΦE = 0.75Φ0, blue) pulses (bottom panel). c Same as in b but now the voltage bias (central panel, green trace) is applied only during the readout operation to minimize power consumption and demonstrate the non-volatility of the memory cell. All the measurements were taken at T = 25 mK.

The ability of a memory cell to retain the data even when the power is temporarily turned off is called non-volatility, which, even if not essential for RAM memory, is an adding value for energy saving and data storage. The PSM requires two power sources: one to generate the bias flux ΦB and one for the readout signal. The former was provided by an external superconducting magnet controlled by a current source, then power dependent. To overcome this limitation ΦB could also be generated by a permanent dissipationless superconducting coil as well as a metallic ferromagnetic layer buried in the semiconducting substrate or by directly employing a ferromagnetic insulator as dielectric substrate20,21. Alternatively, a proper phase bias might be generated with an additional ferromagnetic pi-junction22 inserted in the ring or through a phase-battery23. The readout voltage is only required to probe the resistance state of the PSM. As demonstrated in Figure 3c, temporarily and repeated measures of both logic states do not affect the stored data with a readout dissipation as low as P[0] ≃ 25 fW and P[1] ≃ 40 fW for the logic state [0] and [1], respectively, and only limited by the noise of the current amplifier. This low dissipated power combined with the intrinsic cutoff time τR ≃ 30 ps estimated from the RC circuit of the tunnel junctions (see “Methods” section for details) yields predicted tiny energy required per bit readout J[0] = P[0]τR ≃ 4.7 μeV and J[1] = P[1]τR ≃ 7.5 μeV. These values were only estimated and stem from the severe bandwidth limitations of the cryogenic filters. Similar to rapid single flux quantum, the writing/erasing process is expected with a switching time of ~1 ps which is typical for small superconducting loops24,25,26. The PSM speed is therefore expected to be on par with current state-of-the-art superconducting memories both in the reading and in the writing/erasing process24,25,27,28,29.

Memory robustness and operation with AC readout

The robustness of the PSM against flux fluctuations is tested by superimposing to the working biasing flux a sizable sinusoidal signal (ΦAC, Fig. 4a). The PSM shows optimal stability with respect to flux oscillations, as shown in Fig. 4b for V = 300 μV and ΦB = 0.56Φ0. The memory preserves the stored state and keeps the readout value of the two logic states well separated for fluctuations ΦAC ≃ 0.08Φ0, then ~ 50% of the hysteretic domain of the memory δΦ, at least. Interestingly, thanks to the opposite sign of the magnetoconductance of PSM in the two topological states (visible for instance in Fig. 2b, c), the AC flux modulation induces an AC response in the tunneling current which acquires a π shift when switching between the two logic states [0] and [1]. This phase shift provides a complementary and efficient method to probe the parity of the JJ winding number, which is not affected by the position of ΦB within the hysteretic domain, or by the low visibility of the DC readout signal (see also Supplementary Figs. 4 and 5 for more details). This allows operating the memory cell also in the degenerate point ΦB = Φ0/2, where the energies of the [0] and [1] states are equal, a basic condition to implement a phase-slip qubit8,14. Therefore, the PSM provides an alternative low-frequency method for the qubit readout. With the phase-based readout, the persistency of the PSM have been tested up to almost three days, as shown in Fig. 4c. The memory is initialized to logic state [1], and the readout is performed every 4 h. No sign of signal degradation has been observed even after ~3 days of measurement confirming the vanishing phase-slip rate (~10−289 Hz) as estimated from our parameters7,9 (see “Methods” for details on the estimate). As a consequence, the memory error rate expected for quantum and thermally-activated phase slips is infinitesimally small and errors can be generated only by large magnetic-flux fluctuations (≳δΦ) of the driving magnetic flux. The other source of error that might degrade the memory state is the reading current which could switch the memory via inductive coupling to the ring or by quenching the superconductivity of the weak-link, as commonly happens for superconducting kinetic inductance memories13. Differing from the latter, the high resistance of the probing tunnel barrier strongly limits the reading current to ≲nA, then much smaller than the current required for switching (~mA)19 and the critical current of the weak-link (≳μA for an Al nanowire30). This makes also the error rate during readout operation negligible. High temperature can degrade the performance of PSM by increasing ξw(T)1 thereby lowering the JJ effective length and driving the nanowire junction towards the non-hysteretic single-valued CPR occurring for L ≲ 3.5ξw2,31. In addition, thermal activation can substantially increase the phase-slip rate in the vicinity of the transition, that is at \(\phi \,\lesssim\, {\phi }_{{B}_{{{max}}}}\) and \(\phi \, \gtrsim\, {\phi }_{{B}_{{{min}}}}\)9. Figure 5a shows the evolution of the hysteresis loop at several bath temperatures (T). The hysteresis progressively fades out by increasing T, but persists up to 1.1 K, which corresponds to ~85% of the nanowire critical temperature, with δΦ reduced to about the 12% of the base temperature value (Fig. 5b). Consequently, also the contrast ζ(T) lowers by increasing T, as shown in Fig. 5c. Still, the visibility of the hysteresis loop at high temperatures demonstrates the strength of the PSM with substantial protection of the topological state even in the presence of a sizable amount of hot quasiparticles4. Although the low δΦ achieved at high temperature degrades the robustness of the memory with respect to flux noise, it also allows writing the memory cell with smaller fluxes for a total cost of operation down to ~10 meV.

a Sketch of the memory operation in the presence of a sinusoidal flux oscillation (ΦAC, yellow trace) around \({{{\Phi }}}_{{{{{{{{\rm{B}}}}}}}}}\in ({{{\Phi }}}_{0}/2,{{{\Phi }}}_{{{{{{{{\rm{B}}}}}}}}\_\max })\). b Evolution of the readout current (top panel) measured at V = 300 μV and Φ composed by a flux bias (ΦB = 0.56Φ0) superimposed with a sinusoidal oscillation ΦAC = ± 0.04Φ0 (yellow trace in the bottom panel). Write (ΦW = 0.32Φ0, red) and erase (ΦE = 0.81Φ0, blue) flux pulses are applied to switch the logic state of the memory cell. Notice that the two current signals oscillate with a π shift making the phase of the AC signal a very sensitive readout observable. Vertical dashed lines highlight the signals phase shift with respect to the magnetic flux. c Demonstration of persistent memory operation at Φ = Φ0/2 obtained by measuring the signal phase with a lock-in amplifier (top) every 4 h and only when the readout voltage is turned on (V = 300 μV, bottom). State [1] was measured for almost 3 days showing no sign of degradation, and low dissipation being V = 0 for most of the time. The error bar was estimated from the root mean square of the sampled signal. All the data were recorded at T = 25 mK.

a Current modulation I(Φ) for several bath temperatures (T) at V = 300 μV. The hysteresis loop narrows and fades out by increasing the temperature since the superconducting nanowire approaches the short-junction limit at high T. Inset: blow-up of the I(Φ) characteristics around Φ0/2 at 1.1 K. Forward (purple) and backward (green) traces highlight the presence of hysteresis. b Temperature dependence of δΦ measured at V = 300 μV. δΦ monotonically decreases with temperature. c ζ vs T for selected values of V. ζ drops with temperature, and by increasing V. Black lines in panels b and c are guides for the eye.

Discussion

In summary, we have envisioned and demonstrated an original persistent Josephson phase-slip single memory cell that takes advantage of fluxoid quantization to codify two logic states in the topological index of the system, i.e., the parity of the superconducting winding number5. Differing from conventional superconducting loops12,13,25, here the separation between the two topological states is provided by the large phase-slip barrier, which is unique to long superconducting JJs4,9. Moreover, its operation mechanism is completely independent of the size or inductance of the superconducting loop thus allowing device miniaturization only limited by fabrication capabilities. The memory exploits conventional superconductors thereby avoiding the use of complex ferromagnetic metals typical of present superconducting memories24,26,27,28,29,32. Notably, the performances of the PSM are competing with state-of-the-art superconducting memories with an extremely low energy dissipation per bit operation (~10−24 J and ~10−20 J for readout and write, respectively) and high operation speed (up to ~30 ps and ~1 ps for readout and write, respectively). Thanks to the topological protection, the PSM shows endurance, persistence, and high-temperature operation (up to ~1 K), only limited by the Al critical temperature. The use of vanadium18 or niobium33, therefore, could extend the memory operation above liquid He temperature, and further promote miniaturization thanks to the lower coherence length of these metals with respect to Al.

In addition, our phase-based readout scheme ensures protection against magnetic flux fluctuations and provides ideal visibility in all the operation ranges. In fact, despite being intrinsically slower than conventional methods (high-speed lock-in amplifiers reach nowadays a clock frequency of ~600 MHz), the phase-based readout can be a valuable approach for the readout of phase-slip qubits. Furthermore, scalability to large arrays of PSM cells might be designed by taking advantage of the well-known architectures employed for transition-edge sensors, since both devices are based on precise resistance measurement. In particular, frequency-domain multiplexing or microwave resonators together with SQUID amplifiers34 could be used for the selective readout of each PSM composing the total memory.

Sneak currents can be avoided by employing strongly non-linear resistors between each single memory unit, such as superconductor/insulator/normal metal/insulator/superconductor Josephson junctions. Integrating superconducting current feed lines in the ring19 will allow scaling also the writing procedure with the additional cost of wiring complexity. Yet, the presence of independent write and read lines, with the former characterized by a low impedance, increases stability against perturbations of the read current and might simplify the integration of the PSM with existing superconducting logic elements including rapid single flux quantum24,25,26, reciprocal quantum logic35, quantum flux parametrons36, Josephson field-effect transistors37, and gate-controlled cryotrons17,38,39. Yet, the strong topological protection and stability observed in the PSM make our approach promising in light of the implementation of phase-slip flux qubits8,14 and quantum memories.

Methods

Device fabrication details

The hybrid memory cells were realized by the shadow-mask lithography technique. The suspended resist-mask was defined by electron-beam lithography (EBL) onto a SiO2 wafer. All metal-to-metal clean interfaces, and metal-to-oxide barriers were realized in an ultra-high vacuum (UHV) electron-beam evaporator (EBE) with a base pressure of 10−11 Torr equipped with a tiltable sample holder suitable for multi-directional depositions. In order to obtain wire/ring transparent interfaces, which is crucial for the device operation, the use of the same material is strongly recommended16. Therefore, the nanowire and the ring of the PSM were realized with aluminum. Furthermore, the Al film evaporation is relatively simple, and its high-quality native oxide allows the realization of good tunnel barriers through oxygen exposure at room temperature. At first, 15 nm of Al0.98Mn0.02 were evaporated at an angle of −18° to realize the normal metal electrode. Subsequently, the sample was exposed to 60 mTorr of O2 for 5 min in order to form the thin insulating AlMnOx layer. Next, the sample holder was tilted to 10° for the deposition of 20 nm of Al realizing the SQUIPT nanowire (length L = 400 nm, width w = 90 nm, and thickness t = 20 nm) and the superconducting electrodes. Finally, a thicker layer of Al (tR = 70 nm) was evaporated at 0° to realize the superconducting loop of circumference ~ 7.6 μm, and average width wR,ave ≃ 600 nm.

Magneto-electric characterization

The magneto-electric characterization of the samples was performed at cryogenic temperatures in a 3He–4He dilution refrigerator (Triton 200, Oxford Instruments) equipped with RC-filters of resistance ~2kΩ. The out-of-plane magnetic field was applied via a superconducting magnet driven by a low-noise current source (Series 2600, Keithley Instruments). The DC measurements were performed in a two-wire voltage-bias configuration through a low-noise voltage DC source (GS200, Yokogawa) coupled with a room-temperature current preamplifier (Model 1211, DL Instruments) (Fig. 1c). The AC characterization was performed via a combination of DC bias and low-frequency lock-in technique. A DC bias voltage (V) was applied to the device. A current given by the sum of a DC and AC sinusoidal modulation energized the superconducting magnet. The readout current oscillations induced by variation of Φ, and the phase of the signal (with respect to the flux oscillations) were recorded by a lock-in amplifier (SR830, Stanford Research Systems). Further details on the readout scheme can be found in the note 5 of the Supplementary Information.

Device parameters

Based on the device structure, we estimate the zero-temperature nanowire coherence length ξw,0 = \(\sqrt{\hslash D/{{{\Delta }}}_{{{{{w}}}},0}}\simeq 65\) nm, where ℏ is the reduced Planck constant, D ≃ 18 cm2/s is the diffusion coefficient, and Δw,0 ≃ 200 μeV is the zero-temperature gap in Al. The nanowire critical temperature is TC,w = Δw,0/1.764kB ≃ 1.31 K, where kB is the Boltzmann constant. At low temperature, the ratio L/ξw,0 ≃ 6 confirming the frame of the long JJ regime for the PSM2. The single-valued CPR limit (achieved for ξw,short ≳ L/3.5 ~ 114 nm) is reached at temperature \({T}_{{{{{{\mathrm{short}}}}}}}={T}_{{{{{{\mathrm{C}}}}}},{{w}}}(1-0.85{2}^{2}\frac{{\xi }_{{{w}},0}l}{{\xi }_{{{w}},{{{{{\mathrm{short}}}}}}}^{2}}) \sim 1.29\) K2, where l = 3D/vF ≃ 3 nm is the nanowire mean free path, and vF = 2.03 × 106 m/s is the Fermi velocity of Al.

The kinetic inductance (\({{{{{{{{\mathcal{L}}}}}}}}}_{{{K}}}\)) of a long JJ depends on the geometry and superconducting properties of the nanowire9. In our case, at 25 mK it takes the value \({{{{{{{{\mathcal{L}}}}}}}}}_{{{K}}}=\frac{{R}_{{{N}}}\hslash }{\pi {{{\Delta }}}_{{{{{w}}}}}}\frac{1}{\tanh \frac{{{{\Delta }}}_{{{{{w}}}}}}{2{k}_{{{B}}}T}}\simeq 18\) pH40. The nanowire normal-state resistance is given by \({R}_{{{N}}}=\frac{L}{wt\sigma }\simeq 17\ {{\Omega }}\), where σ = DNfe2 ≃ 1 × 107 S/m is the Al film conductance (with Nf = 2.15 × 1047/J/m3 the density of states at the Fermi energy of Al). Analogously, the ring total inductance (including both the geometric and kinetic contributions) takes the value \({{{{{{{{\mathcal{L}}}}}}}}}_{{{{{{\mathrm{R}}}}}}} \sim\) 1 pH16 (with normal-state resistance RR ≃ 1.4 Ω). The contribution of the ring to the total inductance of the SQUIPT yields a screening parameter \(\beta ={{{{{{{{\mathcal{L}}}}}}}}}_{{{{{{\mathrm{R}}}}}}}/{{{{{{{{\mathcal{L}}}}}}}}}_{{{K}}}\,\lesssim\, 0.1\). The small β cannot account for the hysteretic behavior of the PSM, which stems, differently, from the long-junction regime of the Josephson nanowire. The writing/erasing time (τW,E) is mainly due to the time required to polarize the SQUIPT with the external flux. It is given by \({\tau }_{{{{{{\mathrm{W}}}}}},{{{{{\mathrm{E}}}}}}}={{{{{{{{\mathcal{L}}}}}}}}}_{{{{{{\mathrm{SQUIPT}}}}}}}/{R}_{{{{{{\mathrm{SQUIPT}}}}}}} \sim\) 1 ps, where \({{{{{{{{\mathcal{L}}}}}}}}}_{{{{{{\mathrm{SQUIPT}}}}}}}={{{{{{{{\mathcal{L}}}}}}}}}_{{{K}}}+{{{{{{{{\mathcal{L}}}}}}}}}_{{{{{{\mathrm{R}}}}}}}\) and RSQUIPT = RN + RR are the total inductance and resistance of the SQUIPT, respectively. The readout time (τR) is predominantly limited by the characteristic time of the two tunnel barriers, τR = τt1 + τt2 ~ 30 ps, where τt1 = Rt1Ct1 ~ 20 ps is the characteristic time of the first tunnel junction, and τt2 = Rt2Ct2 ~ 10 ps is the time constant of the second junction. The junctions capacitances (Ct1 ~ 0.3 fF and Ct1 ~ 0.1 fF) are estimated from the area and the typical specific capacitance of AlOx tunnel barriers ~50 fF/μm2.

Phase-slip rates

Stochastic phase-slips are possible via quantum tunneling and thermal activation. They scale exponentially with the phase-slip barrier, the former with −U/Δw,0 while the latter with −U/kBT. Both of them are small for Rξ < Rq (where Rξ = RNξw/L), as demonstrated in the following. The quantum phase-slip rate is8:

where \({{{\Omega }}}_{{{qps}}}\simeq 0.85\frac{{{{\Delta }}}_{{{{{w}}}}}}{\hslash }\frac{L}{{\xi }_{{{w}}}}\sqrt{\frac{{R}_{{{{{{\mathrm{q}}}}}}}}{{R}_{\xi }}}\simeq 75\) THz is the quantum phase-slips attempt frequency. With the parameters of our experiment, we obtain the negligibly small Γqps ~ 2 × 10−289 Hz. Thermally-activated phase-slips rate reads7:

where \(\delta F=2.7\frac{T_{{{{{\mathrm{c}}}}}}-T}{T}U\) is the free energy difference of the potential barrier and \({{{\Omega }}}_{{{TAPS}}}\simeq 5.5\frac{{k}_{{{B}}}T}{\hslash }\frac{L}{{\xi }_{{{w}}}}\sqrt{\frac{\delta F}{{k}_{{{B}}}T}}\) is the attempt frequency. In the temperature range of the experiment T < < Tc, ΓTAPS is expected to be even smaller than Γqps. As an example, at T = 100 mK the attempt frequency is ΩTAPS ≃ 500 THz and ΓTAPS ~ 10−474 Hz. From these equations is possible to see that ΓTAPS is relevant only at a temperature very close to Tc.

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

References

Tinkham, M. Introduction to Superconductivity 2nd edn (Dover Publ, Mineola, NY, 2004).

Likharev, K. K. Superconducting weak links. Rev. Mod. Phys. 51, 101–159 (1979).

Langer, J. S. & Ambegaokar, V. Intrinsic resistive transition in narrow superconducting channels. Phys. Rev. 164, 498–510 (1967).

Little, W. A. Decay of persistent currents in small superconductors. Phys. Rev. 156, 396–403 (1967).

Strambini, E. et al. The ω-SQUIPT as a tool to phase-engineer Josephson topological materials. Nat Nano 11, 1055–1059 (2016).

Petković, I., Lollo, A., Glazman, L. I. & Harris, J. G. E. Deterministic phase slips in mesoscopic superconducting rings. Nat Commun 7, 1–7 (2016).

Arutyunov, K. Y., Golubev, D. S. & Zaikin, A. D. Superconductivity in one dimension. Phys. Rep. 464, 1–70 (2008).

Mooij, J. E. & Harmans, C. J. P. M. Phase-slip flux qubits. New J. Phys. 7, 219–219 (2005).

Virtanen, P., Ronzani, A. & Giazotto, F. Spectral characteristics of a fully superconducting SQUIPT. Phys. Rev. Appl. 6, 054002 (2016).

Doll, R. & Näbauer, M. Experimental proof of magnetic flux quantization in a superconducting ring. Phys. Rev. Lett. 7, 51–52 (1961).

Giazotto, F., Peltonen, J. T., Meschke, M. & Pekola, J. P. Superconducting quantum interference proximity transistor. Nat. Phys. 6, 254 (2010).

Murphy, A., Averin, D. V. & Bezryadin, A. Nanoscale superconducting memory based on the kinetic inductance of asymmetric nanowire loops. New J. Phys. 19, 063015 (2017).

Ilin, E. et al. Supercurrent-controlled kinetic inductance superconducting memory element. Appl. Phys. Lett. 118, 112603 (2021).

Mooij, J. E. & Nazarov, Y. V. Superconducting nanowires as quantum phase-slip junctions. Nat. Phys 2, 169–172 (2006).

Chen, G., Rosenthal, P. & Beasley, M. Kinetic inductance memory cell. IEEE Trans. Appl. Supercond. 2, 95–100 (1992).

Ronzani, A., D’Ambrosio, S., Virtanen, P., Giazotto, F. & Altimiras, C. Phase-driven collapse of the Cooper condensate in a nanosized superconductor. Phys. Rev. B 96, 214517 (2017).

De Simoni, G., Paolucci, F., Solinas, P., Strambini, E. & Giazotto, F. Metallic supercurrent field-effect transistor. Nat. Nanotechnol. 13, 802–805 (2018).

Ligato, N., Marchegiani, G., Virtanen, P., Strambini, E. & Giazotto, F. High operating temperature in V-based superconducting quantum interference proximity transistors. Sci. Rep. 7, 8810 (2017).

Enrico, E., Croin, L., Strambini, E. & Giazotto, F. On-chip tuning of electrodes quasiparticles population in fully superconducting SQUISETs. Preprint at https://arxiv.org/abs/1901.01248 [cond-mat] (2019).

Strambini, E. et al. Revealing the magnetic proximity effect in EuS/Al bilayers through superconducting tunneling spectroscopy. Phys. Rev. Mater. 1, 054402 (2017).

De Simoni, G., Strambini, E., Moodera, J. S., Bergeret, F. S. & Giazotto, F. Toward the absolute spin-valve effect in superconducting tunnel junctions. Nano Lett. 18, 6369–6374 (2018).

Ryazanov, V. V. et al. Coupling of two superconductors through a ferromagnet: evidence for a π Junction. Phys. Rev. Lett. 86, 2427–2430 (2001).

Strambini, E. et al. A Josephson phase battery. Nat. Nanotechnol. 15, 656–660 (2020).

Golod, T., Iovan, A. & Krasnov, V. M. Single Abrikosov vortices as quantized information bits. Nat. Commun 6, 1–5 (2015).

Zhao, Q.-Y. et al. A compact superconducting nanowire memory element operated by nanowire cryotrons. Supercond. Sci. Technol. 31, 035009 (2018).

Ryazanov, V. V. et al. Magnetic Josephson junction technology for digital and memory applications. Phys. Proc. 36, 35–41 (2012).

Vernik, I. V. et al. Magnetic Josephson junctions with superconducting interlayer for cryogenic memory. IEEE Trans. Appl. Supercond. 23, 1701208–1701208 (2013).

Gingrich, E. C. et al. Controllable 0 − π josephson junctions containing a ferromagnetic spin valve. Nat. Phys. 12, 564–567 (2016).

Madden, A. E., Willard, J. C., Loloee, R. & Birge, N. O. Phase controllable Josephson junctions for cryogenic memory. Supercond. Sci. Technol. 32, 015001 (2018).

Bours, L., Mercaldo, M. T., Cuoco, M., Strambini, E. & Giazotto, F. Unveiling mechanisms of electric field effects on superconductors by a magnetic field response. Phys. Rev. Res. 2, 033353 (2020).

Troeman, A. G. P. et al. Temperature dependence measurements of the supercurrent-phase relationship in niobium nanobridges. Phys. Rev. B 77, 024509 (2008).

Baek, B., Rippard, W. H., Benz, S. P., Russek, S. E. & Dresselhaus, P. D. Hybrid superconducting-magnetic memory device using competing order parameters. Nat. Commun. 5, 3888 (2014).

Jabdaraghi, R. N., Peltonen, J. T., Saira, O.-P. & Pekola, J. P. Low-temperature characterization of Nb-Cu-Nb weak links with Ar ion-cleaned interfaces. Appl. Phys. Lett. 108, 042604 (2016).

Ullom, J. N. & Bennett, D. A. Review of superconducting transition-edge sensors for x-ray and gamma-ray spectroscopy. Supercond. Sci. Technol. 28, 084003 (2015).

Herr, Q. P., Herr, A. Y., Oberg, O. T. & Ioannidis, A. G. Ultra-low-power superconductor logic. J. Appl. Phys. 109, 103903 (2011).

Hosoya, M. et al. Quantum flux parametron: a single quantum flux device for Josephson supercomputer. IEEE Trans. Appl. Supercond. 1, 77–89 (1991).

Doh, Y.-J. et al. Tunable supercurrent through semiconductor nanowires. Science 309, 272–275 (2005).

Paolucci, F. et al. Magnetotransport experiments on fully metallic superconducting Dayem bridge field-effect transistors. Phys. Rev. Appl. 11, 024061 (2019).

Paolucci, F. et al. Field-effect control of metallic superconducting systems. AVS Quantum Sci. 1, 016501 (2019).

Meservey, R. & Tedrow, P. M. Measurements of the kinetic inductance of superconducting linear structures. J. Appl. Phys. 40, 2028–2034 (1969).

Acknowledgements

We acknowledge M. Cuoco and P. Virtanen for fruitful discussions. N.L., E.S., and F.G. acknowledge partial financial support from the European Union’s Seventh Framework Program (FP7/2007-2013)/ERC Grant No. 615187- COMANCHE. N.L., E.S., and F.G. were partially supported by EU’s Horizon 2020 research and innovation program under Grant Agreement No. 800923 (SUPERTED). The work of F.P. was partially supported by the Tuscany Government (Grant No POR FSE 2014-2020) through the INFN-RT2 172800 project. The authors acknowledge the European Union (Grant No. 777222 ATTRACT) through the T-CONVERSE project.

Author information

Authors and Affiliations

Contributions

E.S. and F.G. conceived the experiment. N.L. fabricated the samples with inputs from F.P. N.L. and E.S. performed the measurements. N.L. analyzed the experimental data with inputs from E.S. and F.G. All the authors discussed the results and their implications equally at all stages and wrote the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Peer review information Nature Communications thanks Karl Berggren and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Ligato, N., Strambini, E., Paolucci, F. et al. Preliminary demonstration of a persistent Josephson phase-slip memory cell with topological protection. Nat Commun 12, 5200 (2021). https://doi.org/10.1038/s41467-021-25209-y

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-021-25209-y

This article is cited by

-

Demonstration of a Josephson vortex-based memory cell with microwave energy-efficient readout

Communications Physics (2024)

-

Calorimetry of a phase slip in a Josephson junction

Nature Physics (2023)

-

Sign reversal diode effect in superconducting Dayem nanobridges

Communications Physics (2023)

-

Word and bit line operation of a 1 × 1 μm2 superconducting vortex-based memory

Nature Communications (2023)

-

Thermal superconducting quantum interference proximity transistor

Nature Physics (2022)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.