Abstract

The realization of hybrid superconductor–semiconductor quantum devices, in particular a topological qubit, calls for advanced techniques to readily and reproducibly engineer induced superconductivity in semiconductor nanowires. Here, we introduce an on-chip fabrication paradigm based on shadow walls that offers substantial advances in device quality and reproducibility. It allows for the implementation of hybrid quantum devices and ultimately topological qubits while eliminating fabrication steps such as lithography and etching. This is critical to preserve the integrity and homogeneity of the fragile hybrid interfaces. The approach simplifies the reproducible fabrication of devices with a hard induced superconducting gap and ballistic normal-/superconductor junctions. Large gate-tunable supercurrents and high-order multiple Andreev reflections manifest the exceptional coherence of the resulting nanowire Josephson junctions. Our approach enables the realization of 3-terminal devices, where zero-bias conductance peaks emerge in a magnetic field concurrently at both boundaries of the one-dimensional hybrids.

Similar content being viewed by others

Introduction

Hybrid superconducting/semiconducting nanowires are a promising material platform for the formation of one-dimensional topological superconductors bounded by pairs of Majorana modes1,2,3. Owing to their non-Abelian exchange statistics, these localised Majorana bound states (MBS) are the fundamental constituents for fault-tolerant topological quantum computing4,5. Individual qubits comprise at least four MBS in several interconnected nanowire segments with a hard induced superconducting gap6,7. Residual fermionic states within the gap would compromise the topological protection of the Majorana modes. Hence, a fundamental challenge in the development of topological qubits is the engineering of complex, interconnected hybrid devices with hard superconducting gaps and clean, homogeneous interfaces8,9.

Here, we introduce a fabrication technique that resolves these challenges and provides high-quality hybrid quantum devices, reflected by the absence of chemical intermixing, a high interface transparency and hard induced gaps, while involving minimal nanofabrication steps compared with previously established methods10,11. Our approach is based on the deposition of superconducting thin films at a shallow angle onto semiconducting nanowires, which have been selectively placed on substrates with pre-patterned gates and shadow-wall structures. It enables complex hybrid devices while eliminating lithography, etching, and other fabrication steps after the deposition of the superconductor, in the following referred to as post-interface fabrication. While shadow-wall lithography is compatible with a large variety of materials, we utilise InSb nanowires coated with Al half-shells to induce superconducting correlations – a suitable material combination to study Majorana physics11,12. The homogeneity of the interface between InSb and Al ultimately determines the device quality, but it is known to have very limited chemical and thermal stability9,13. Therefore, the reduction or elimination of post-interface fabrication steps represents a paradigm shift that enables pristine hybrid interfaces. Similar advances in quality and reproducibility (Supplementary Note 1) were made possible by the reverse fabrication process established for carbon nanotube devices14.

In this article, we investigate the transport properties of hybrid nanowire shadow-wall devices. Initially, we examine Josephson junctions and detect subharmonic gap features that arise from multiple Andreev reflections15. These junctions exhibit gate-tunable supercurrents of up to 90 nA, which is exceptionally large for InSb/Al nanowires compared to previous works on InSb Josephson junction devices9,16,17. The shadow-wall method also facilitates 3-terminal hybrid devices with two normal metal/superconductor (N–S) interfaces, which are crucial to corroborate earlier Majorana signatures18,19,20. We investigate the transport at a single N–S interface and observe a crossover between a hard induced gap and pronounced Andreev enhancement upon increasing the junction transparency, consistent with the expected behaviour for ballistic junctions21,22. Finally, we report the emergence of discrete subgap states in the tunnelling conductance at both nanowire ends and detect stable zero-energy conductance peaks that coexist at certain magnetic fields and chemical potentials.

Our fabrication method paves the way for more advanced nanowire devices, including qubit implementations6,7,23 and other multi-terminal devices that are essential for fundamental research on topological superconductors18,24. The versatility of the shadow-wall technique introduces a convenient and quick way to implement new device geometries with various combinations of semiconductor and superconductor materials.

Results

Shadow-wall lithography

A well-established approach to realise hybrid devices is based on the epitaxial growth of nanowires followed by the in-situ evaporation of a superconductor10,25. This method requires a subsequent etching step to expose gate-tunable wire segments without metal. Nanowires have also been grown on opposite crystal facets of etched trenches11,26, which enables the formation of shadowed junctions without the need to etch the superconductor11. The native oxide that forms during the ex-situ processing is removed prior to the deposition of the superconductor. Another recent study employed growth chips with bridges and trenches that act as selectively shadowing objects during the evaporation of a superconductor27. Common to those methods is that the hybrid nanowires are removed from the growth substrate following the evaporation and undergo several post-interface fabrication steps such as alignment via scanning electron microscopy (SEM), electron-beam lithography involving resist coating, or etching. The latter, in particular, degrades the electrical device performance compared with shadowed junctions13. Moreover, hybrid devices are prone to degradation. High-temperature processing (e.g. certain dielectric deposition methods or resist baking) cannot be performed, as it would lead to chemical intermixing at the super-/semiconductor interface28,29. The limited chemical stability of the interface requires sample storage in vacuum at a temperature T < 0 ∘C, which is hardly compatible with standard fabrication methods. The low thermal budget and the additional fabrication steps limit the achievable device performance in terms of electrical noise, lithographical alignment accuracy, contamination and disorder. The considerable variation from device to device imposes singular rather than standardised designs and results in a limited reproducibility of basic transport measurements.

In contrast, the core principle of our approach is to minimise or eliminate post-interface fabrication. We have engineered scalable substrates that comprise all desired functionalities without being subject to any fabrication restrictions (e.g. thermal budget limitations) since the semiconductor nanowires are only introduced right before the superconductor deposition. As depicted in Fig. 1a, we transfer InSb nanowires30 to these substrates onto pre-patterned bottom gates covered by a continuous dielectric layer in the vicinity of shadow-wall structures. The nanowires are loaded into a customised evaporation chamber where the native oxide is removed at T = 550 K by exposure to a directed flow of atomic hydrogen radicals. Without breaking the vacuum, Al is subsequently deposited onto the samples at T = 140 K. The superconductor is evaporated at a shallow angle of 30∘ with respect to the substrate plane, which creates a 3-facet nanowire shell that is connected to the leads and bond pads on the substrate (Fig. 1d). As illustrated in Fig. 1b, the shadow walls enable selective deposition on both the nanowires and the substrate. Adding gaps at critical locations along the shadow walls (Fig. 1c) ensures that the leads are electrically isolated from one another while eliminating the need for post-interface fabrication such as lift-off patterning or Al etching. Figure 2a shows an exemplary device without local gates that is directly bonded to a printed circuit board for low-temperature transport measurements. Here, the p+-doped Si substrate enables back-gate control of the electron density in the nanowire (see Fig. 2b).

a Micromechanical transfer of the nanowires onto local bottom gates (covered by Al2O3 dielectric) in the proximity of the Si3N4 shadow walls. b Illustration of a final device following the H radical cleaning and Al deposition at a shallow angle. c False-colour SEM image of an exemplary sample prior to Al deposition. Shadow walls are designated in blue and bond pads, which are enclosed by the shadow walls, are shaded in dark yellow. Gaps are placed at critical locations along the shadow walls (cf. green circle and the illustration in the blow-up following Al deposition). This ensures that bond pads with leads are isolated from each other after the Al deposition. The area illustrated in panel a is indicated by the orange box. d Schematic of the InSb nanowire cross-section during H radical cleaning (top). The native oxide of the semiconductor is denoted by a dark green layer. The Al thin film deposited at a shallow angle of 30∘ forms an electrical connection from the nanowire to the substrate (bottom).

a False-colour SEM image of an InSb nanowire Josephson junction. b Schematic of the measurement setup. The back-gate voltage, VBG, is applied to the p+-doped Si substrate to tune the electron density in the nanowire. c Cross-sectional EDX elemental composite image of the \(\left[111\right]\) InSb nanowire covered with the Al layer and a protective layer of SiNx. d Line-cuts of the integrated elemental counts within the orange box in panel c. e High-resolution bright-field scanning TEM image of the InSb/Al interface at the location indicated by the blue box in panel c.

Materials analysis

The quality of the InSb nanowires, Al thin films, and InSb/Al interfaces is assessed by transmission electron microscopy (TEM) of cross-sectional lamellae prepared via focused ion beam (FIB). These lamellae are cut out from devices like the one depicted in Fig. 2a (cf. dashed line). A continuous high-quality polycrystalline Al layer is formed on three facets of the InSb nanowires and the samples exhibit a sharp superconductor–semiconductor interface (see Fig. 2c, e and Supplementary Fig. 1). No oxide formation is observed between the Al grains, which is evident in the elemental energy-dispersive X-ray spectroscopy (EDX) composite image (Fig. 2c). The middle facet has twice the Al layer thickness (16 nm) compared to the top and bottom facets (8 nm) due to the evaporation angle of 30∘ with respect to the substrate plane. The InSb/Al interface is clean and there is no residual native oxide (see Fig. 2d, e), which confirms that our procedure of atomic hydrogen radical cleaning can effectively remove the oxide without damaging the InSb crystal structure. The nanowires are single-crystalline, defect-free, and exhibit a hexagonal geometry. The polycrystalline Al layer forms a continuous metallic connection from the nanowire to the substrate. This connection is crucial for the contact between the shell and the thin Al lead on the substrate and it is fundamental for more complex devices such as superconducting interferometers (see Supplementary Fig. 30) and 3-terminal Majorana devices that can reveal the opening of a topological gap18.

Highly transparent Josephson junctions

We employ mesoscopic InSb/Al Josephson junctions like the one depicted in Fig. 2a to study the induced superconductivity in the nanowires. Each device comprises two Al contacts (1.8 μm wide) separated by a 110–150-nm-long bare nanowire segment that is tunable by the back-gate voltage, VBG. The source–drain voltage, VSD, is applied or measured between the two Al electrodes (Fig. 2b). Figure 3a shows the differential resistance, R = dVSD/dISD, as a function of bias current, ISD, and temperature for a typical device. The blue region (R = 0 Ω) denotes the superconducting phase, which persists up to ~1.8 K, consistent with the enhanced superconducting critical temperature for thin films with respect to bulk Al31. At low temperatures (T < 0.6 K), the hysteretic behaviour of the asymmetric VSD–ISD traces is caused by self-heating of the junction. This effect disappears at higher temperatures (T > 0.6 K), which can be attributed to enhanced thermalisation via electron–phonon coupling32. Remarkably, at T = 30 mK, the switching current, Isw, i.e. the observable supercurrent, ranges from 30 to 90 nA across all devices in the open-channel regime. The magnitude of the intrinsic supercurrent, Ic, in ballistic and short junctions can be predicted via the Ambegaokar–Baratoff formula: IcRN = πΔind/2e, with the normal-state resistance RN, the induced gap Δind, and the electron charge e33. Here, the typical IswRN product is ~110 μV, i.e. only one-third of πΔind/2e ~ 360 μV. The discrepancy between Isw and Ic is consistent with previous experiments16,17,34 and can be explained by premature switchings due to thermal activation and current fluctuations35,36. We note that the magnitude of Isw as well as the normalised quantity eIswRN/Δind ~ 0.5 are significantly larger than in previous reports on InSb Josephson junctions9,16,17.

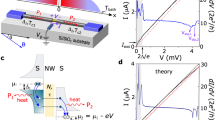

a Differential resistance, R, as a function of ISD (upward sweep direction) and T for device 1 at VBG = 13.65 V. The switching current reaches a maximum of ~ 90 nA at T = 30 mK and persists up to 1.8 K. The peaks at ISD > Isw arise from quasiparticle transport via multiple Andreev reflections. b Conductance line traces (red) versus source–drain voltage for device 1 at VBG = 5.1 V (top) and for device 2 at VBG = 3.0 V (bottom). The theoretical fits (green) yield the transmissions, Tn, of the one-dimensional subbands with index n: T1 = 0.91, T2 = 0.17 (top) and T1 = 0.93, T2 = 0.71, T3 = 0.01 (bottom). c Differential conductance, G, as a function of VSD and magnetic field, B∥, which is oriented along the nanowire, for device 2 at VBG = −0.9 V.

In Fig. 3b, we show the differential conductance, G = dISD/dVSD, as a function of VSD (red curves) for the same Josephson junction (top) and for a second device (bottom). The traces display subharmonic conductance peaks originating from multiple Andreev reflection (MAR) processes15. By fitting the conductance with a coherent scattering model (green curves), we can estimate the induced superconducting gap, Δind (235 μeV and 229 μeV for device 1 and 2, respectively), and the gate-tunable tunnelling probability of the different subbands (see Supplementary Figs. 8–10)37.

In Fig. 3c, we report the evolution of the MAR pattern as a function of magnetic field, B∥, parallel to the nanowire axis of device 2. Here, the presence of subgap states close to the gap edge alters the typical MAR pattern and gives rise to an intricate energy dispersion in magnetic field that is further discussed in Supplementary Note 3. Eventually, the magnetic field quenches the superconductivity at a critical value of Bc = 1.2–1.3 T. This limit can be enhanced to about 2 T by using a thinner Al shell (Supplementary Fig. 14). These values are well above the magnetic field at which a topological phase transition should occur in hybrid InSb/Al nanowires38.

In Fig. 3c, the out-of-gap conductance displays a dense pattern of faint peaks with an average spacing of about 30 μV and an effective Landé g factor of ~20 (extracted from the energy dispersion in magnetic field). This g factor is larger than in Al (∣g∣ = 2) but smaller than in InSb (∣g∣ = 30–50), which indicates that these peaks stem from discrete states of the nanowire hybridised with the ones in the metal39. The observation of this structure might be correlated with our choice of nanowire surface treatment. In fact, the gentle atomic hydrogen cleaning preserves the pristine semiconductor crystal quality, unlike the invasive chemical or physical etching methods adopted in previous works9,16,17,34,40.

Hard induced gap and ballistic superconductivity

A common technique to search for evidence of Majorana bound states is N–S tunnelling spectroscopy, which probes the local density of states. Signatures of MBS in proximitized InSb nanowires are zero-bias peaks (ZBPs) in the differential conductance at moderately large magnetic fields41. The ZBP height in the zero-temperature limit is predicted to be G0 = 2e2/h, independent of the tunnel-coupling strength, due to resonant Andreev reflection via a Majorana zero mode42. ZBPs of non-topological origin, which mimic the subgap behaviour of MBS, may arise from disorder or potential inhomogeneities43. A major challenge is to reduce the detrimental role of disorder at the superconductor–semiconductor interface, which determines the final device quality. The measure of success is a hard induced gap at a finite magnetic field and quantised Andreev enhancement as a signature of ballistic transport44,45.

An exemplary N–S device is depicted in Fig. 4a. Here, the N contact to the InSb nanowire was formed in a post-interface fabrication step, similar to the contacting of conventional shadow junctions (Supplementary Note 1). Alternatively, Al leads that are defined by the shadow walls – microns away from the N–S junction – can serve as N contacts but require additional bottom gates to render all nanowire segments fully conducting (cf. Fig. 1b). Another option to fabricate N contacts in situ involves using two deposition angles, which we describe in detail elsewhere46. In Fig. 4b, we present voltage-bias spectroscopy of the N–S junction in Fig. 4a where the transmission is tunable via a pre-fabricated bottom tunnel gate. The line-cuts in Fig. 4c at low tunnel-gate voltage, VTG, highlight the pronounced suppression of the subgap conductance, GS, by about two orders of magnitude compared with the normal-state conductance, GN (cf. Supplementary Fig. 23). As the first one-dimensional subband starts to conduct fully at VTG > 0.6 V, the above-gap conductance reaches the conductance quantum, 2e2/h, and the quantisation manifests itself as a plateau in the tunnel-gate dependence (Fig. 4d). At the same time, the conductance below the gap edge reaches 4e2/h owing to two-particle transport via Andreev reflection21. This pronounced doubling of the normal-state conductance together with the quantisation of GN signifies a very low disorder strength in the junction and a strong coupling at the nanowire/Al interface47. While the subgap conductance reaches up to 2G0, it drops again at VTG ~ 0.8 V, possibly due to inter-subband scattering as a result of residual disorder44,47,48,49. The plot of GS versus GN (Fig. 4e) follows the Beenakker model22 reasonably well without any fitting parameter, which shows that in the single-subband regime electrical transport below the gap edge is dominated by Andreev processes. The data are well-described by the BTK theory21 across the entire gate voltage range, demonstrating a hard induced gap of Δind ~ 230 μeV (see Methods and Supplementary Fig. 25). Discrete subgap states and ZBPs appear at a finite magnetic field and field-dependent voltage-bias spectroscopy for this N–S device is presented in Supplementary Fig. 26.

a False-colour SEM image of an exemplary N–S junction. The W bottom gates (brown) underneath the 100-nm-wide InSb nanowire (green) are covered by 18 nm of Al2O3 dielectric. b Differential conductance, G, as a function of source–drain voltage, VSD, and bottom tunnel-gate voltage, VTG. The so-called super gate, which controls the chemical potential of the hybrid nanowire segment, is grounded. c G versus VSD line-cuts of the data in panel b at the locations designated by the coloured lines. d Subgap conductance (green) and above-gap conductance (red) averaged over the VSD intervals designated in panel b. e GS (subgap conductance at zero bias) as a function of GN (normal-state conductance at VSD = 650 μV) together with the theoretically predicted dependence, which assumes Andreev-dominated transport in a single channel (blue line trace).

Emergence of zero-bias peaks at both nanowire ends

The shadow-wall technique enables 3-terminal Majorana devices for nonlocal correlation experiments18,19 by harnessing the continuous connection of the Al shell to the substrate, as depicted in Fig. 5a. Here, the Al thin film serves as the superconducting drain lead. Established fabrication methods do not allow for the implementation of such devices since etching away the superconductor causes disorder at the InSb surface and contacting the Al shell requires selective removal of the native oxide of Al, which affects the integrity of the thin film. As shown in Fig. 5a, optional Ti/Au contacts are again added at both nanowire ends in the same fabrication run and on the same substrate as the sample in Fig. 4. With this device type, we can study the simultaneous emergence of ZBPs at both N–S boundaries in a magnetic field oriented along the wire. Here, the hybrid nanowire segment is 1 μm long and the chemical potential, μ, is controlled via a bottom gate (super gate) at potential VSG. The differential conductance is measured concurrently at both N–S boundaries by alternating the VSD sweep between the left and right N terminals for every increment of B∥ or VSG. Using this technique, we demonstrate the formation of zero-energy subgap states at both nanowire ends for VSG = 0 V (see Fig. 5e, f). The effective g factor extracted from the linear energy dispersion at the two boundaries is ~10, albeit the values of g can be strongly gate-dependent12. Many experiments have demonstrated ZBPs in tunnelling spectroscopy at a single N–S boundary, indicating the presence of a robust state at zero energy41,49,50,51. The robustness of ZBPs in the parameter space (defined by chemical potential and magnetic field) has been used to substantiate their topological origin52. So far, no experiment has revealed the emergence of ZBPs concurrently at both boundaries of a long hybrid nanowire. Recent experimental studies reported correlations between bound states at both ends of short (up to 400 nm long) hybrid nanowire devices53,54. ZBPs often originate from trivial Andreev bound states (ABS). In topological nanowires, ABS can form by overlapping MBS due to local variations in the chemical potential or random disorder, which emphasises the need for long and pristine hybrids43. A topological phase with well-separated MBS requires that potential inhomogeneities along the hybrid segment, Δμ, are much smaller than the width of the topological phase, \(2\sqrt{{E}_{{{{{{{{\rm{Z}}}}}}}}}^{2}-{{{\Delta }}}_{{{{{{{{\rm{ind}}}}}}}}}^{2}}\), where EZ is the Zeeman energy1,55. We see in Fig. 5e,f that the ZBPs at the two boundaries do not exhibit the same onset field, which is defined as the field where the zero-bias conductance reaches half of its maximum value. In Fig. 5d, this corresponds to 0.85T on the left and 0.78T on the right side (grey arrows). This observation could be explained by the presence of long-range inhomogeneities that result in a difference in Δμ at the two nanowire ends of ~70 μeV, considering g = 10. A possible origin of this inhomogeneity might be a variation in the deformation potential along the length of the hybrid due to a slight bend in the nanowire56. At larger values of μ, potential variations are expected to be suppressed due to screening. This might be supported by another data set measured at a larger chemical potential (VSG ~ 0.5 V) presented in Supplementary Fig. 28, where we observe the same ZBP onset field at both N–S boundaries. The concomitant evolution as a function of VSG at both nanowire ends is shown in Supplementary Figs. 28 and 29. This observation might corroborate the signatures of MBS19,55, but it cannot be regarded as conclusive evidence for truly separated MBS43.

a False-colour SEM image of the correlation device based on an 80-nm-wide InSb nanowire with a 1-μm-long hybrid segment. b, c Line-cuts of the differential conductance at zero field (blue) and at B∥ = 1.05 T (orange) taken from panel e and f, respectively. d G versus B∥ line-cut at VSD = 0 μV taken from panel e (left) and f (right). Shaded areas (light purple) illustrate the variation in conductance assuming an uncertainty of ±0.5 kΩ in the series resistance. For the line-cut at the right N–S junction, this variation is less than the line width. e, f Differential conductance, G = dISD/dVSD, as a function of bias voltage, VSD, and magnetic field, B∥, measured concurrently at the left and right junction, respectively. Here, the super gate underneath the hybrid nanowire segment is grounded (VSG = 0 V).

Figure 5b,c show differential conductance line-cuts, which reveal a zero-bias conductance close to 2e2/h for the ZBP at the left boundary of the device, as highlighted in Fig. 5d. While ZBP conductance close to G0 has been observed for several N–S junctions, it depends on the fine-tuning of the tunnel barriers, which can be strongly affected by transmission resonances. Experimentally, ZBPs are in general substantially lower than the expected value of G042,50. Theoretical studies recently pointed out that partially or fully overlapping MBS can cause quantised ZBPs, indistinguishable from those resulting from isolated MBS55,57,58. Hence, the quantised ZBP conductance is a critical but not sufficient hallmark of MBS54,58.

Discussion

The 3-terminal hybrid nanowire devices provide a fundamental tool to study the evolution of the induced superconducting gap in the bulk of the hybrid, where electron- and hole-type bands become inverted at the topological phase transition. There, the closing and reopening of the induced gap are accompanied by the emergence of delocalised MBS, hallmarked by ZBPs at both boundaries of the hybrid nanowire20. Here, we demonstrate hard-gap N–S junctions in a magnetic field where only discrete subgap states move to zero energy to form ZBPs at both boundaries and that respond similarly to variations in the chemical potential. While these are critical signatures of MBS, upcoming studies will attempt to correlate the local tunnelling conductance with the evolution of the induced bulk gap via the nonlocal conductance between the two N terminals18.

Our approach promotes the development of intriguing nanowire-based quantum devices. The ballistic hard-gap N–S junctions together with the thin Al connections across the substrate represent a vital starting point for realising a topological qubit. A qubit implementation with a single read-out loop7 would allow for measuring the projection of the qubit state on one axis of the Bloch sphere. A schematic of the loop qubit is presented in Fig. 6a. It is made from a single nanowire with two superconductor–semiconductor segments connected via a superconducting loop that encircles a central shadow-wall pillar. Bottom gates at the centre of the device are used to define a read-out quantum dot in the nanowire with tunable tunnel couplings to the MBS denoted as γ2 and γ3 in the schematic. Parity read-out will be performed by measuring the quantum capacitance via radio-frequency gate reflectometry6,7,59. In Fig. 6b, we present an exemplary realisation of the basic elements of such a device via the shadow-wall technique. It comprises a superconducting loop to provide a connection for the exchange of Cooper pairs that acts as a blocker for quasiparticle transport between the two hybridised nanowire segments. The shadow-wall technique is ideally suited to realise these superconducting interconnects across the substrate for multi-terminal devices without the need for post-interface fabrication.

a Schematic of a single-nanowire loop-qubit device. The presumable locations of the MBS at the boundaries of the two hybrid segments are denoted by γi, where \(i\in \left\{1,2,3,4\right\}\). The electron parity is fixed due to the finite charging energy of the loop qubit. This configuration offers the desired ground-state degeneracy for a single qubit and can provide information on decoherence and quasiparticle poisoning. b False-colour SEM image of an InSb nanowire following the shadow-wall deposition. Two segments of the nanowire are covered with a superconducting 3-facet Al shell. These hybrid segments are interconnected via an Al loop running across the substrate.

Methods

Nanowire growth

The InSb nanowires are grown on InSb (111)B substrates covered with a pre-patterned SiNx mask via metalorganic vapour-phase epitaxy (MOVPE). These nanowires are not grown on top of InP stems but nucleate instead directly on the growth substrate at Au catalyst droplets30. The investigated nanowires have an average diameter of 100 nm, which is controlled by the Au droplet size and the growth mask openings, and a typical length in the order of 10 μm.

Device fabrication

Bottom gates are fabricated on Si/SiO2 substrates via dry-etching of W thin films, which are subsequently covered by Al2O3 gate dielectric via atomic layer deposition (ALD). Shadow walls of ~600 nm height are created via reactive-ion etching of thick layers of Si3N4 formed via plasma-enhanced chemical vapour deposition (PECVD). Using a micromanipulator, individual nanowires are placed deterministically next to the shadow walls. The native oxide of the nanowires is removed via atomic hydrogen radical cleaning (see Supplementary Note 1). The Al thin films are deposited by evaporation under a shallow angle that forms continuous contacts between the nanowires and the substrate and creates segments on the chip that are electrically isolated from one another. This allows to immediately cool down the devices without the need for additional post-interface fabrication steps. We have not observed a decreased stability or performance of devices that were made with an extra fabrication step to create N contacts. We attribute this to the fact that the hybrid segments are not directly exposed and resist baking is avoided during the fabrication of the contacts.

TEM analysis

The cross-sectional lamellae for TEM are prepared using the focused ion beam technique with a Helios G4 UX FIB/SEM from Thermo Fisher Scientific after capping the devices with a protective layer of sputtered SiNx. TEM analysis is carried out at an acceleration voltage of 200 kV with a Talos electron microscope from Thermo Fisher Scientific equipped with a Super-X EDX detector.

Transport measurements

Electrical transport measurements are carried out in dilution refrigerators equipped with 3-axes vector magnets. The base temperature is ~15 mK, corresponding to an electron temperature of ~30 mK measured with a metallic N–S tunnel junction thermometer. The sample space is evacuated by a turbomolecular pump for at least 1 day prior to the cool-down to remove surface adsorbates that limit the device performance. Conductance measurements are performed using a standard low-frequency lock-in technique. For voltage-bias measurements, the excitation voltage is VAC ≤ 20 μV at a lock-in frequency of at least 20 Hz. For all two-terminal conductance measurements we only subtract setup-related series resistances without making any assumptions about additional contact resistances of the metal–semiconductor interface. Current-driven measurements are carried out in a four-point configuration.

After taking the data, we became aware of the relatively low bandwidth of the employed current-to-voltage amplifiers. Hence, we recalibrated the lock-in data via a mapping according to the measured DC conductance that does not suffer from any bandwidth limitations and is insensitive to the reactive response of the circuit (Supplementary Note 4).

Superconducting gap extraction

The BCS–Dynes term is given by a smeared BCS density of states with the broadening parameter Γ60:

For all of our N–S devices, the fit of the BCS–Dynes term yields typical broadening parameters of <10 μeV. The model by Blonder, Tinkham and Klapwijk (BTK) incorporates the transition between BCS tunnelling and Andreev reflection in the open channel regime21. Fits of the BCS–Dynes term and of the BTK model to the N–S junction data (including the data in Fig. 4b) are presented in Supplementary Note 4.

The subgap conductance for a ballistic N–S junction with a single subband, where the transport is dominated by Andreev processes, has been described by Beenakker22. At a large enough chemical potential61, it is given by

where the transmission probability, T, has been substituted with the normal-state conductance, GN, in units of 2e2/h. This function is plotted together with the measured data in Fig. 4e.

Data availability

The data that support the plots within this paper and other findings of this study are available at https://doi.org/10.5281/zenodo.5034524.

Code availability

The code used to calculate Andreev transport in Josephson junctions is available from the corresponding author upon reasonable request.

References

Oreg, Y., Refael, G. & von Oppen, F. Helical liquids and Majorana bound states in quantum wires. Phys. Rev. Lett. 105, 177002 (2010).

Lutchyn, R. M., Sau, J. D. & Das Sarma, S. Majorana fermions and a topological phase transition in semiconductor-superconductor heterostructures. Phys. Rev. Lett. 105, 077001 (2010).

Lutchyn, R. M. et al. Majorana zero modes in superconductor-semiconductor heterostructures. Nat. Rev. Mater. 3, 52–68 (2018).

Kitaev, Y. A., Unpaired Majorana fermions in quantum wires. Phys.-Uspekhi 44, 131–136 (2001).

Nayak, C., Simon, S. H., Stern, A., Freedman, M. & Das Sarma, S. Non-Abelian anyons and topological quantum computation. Rev. Mod. Phys. 80, 1083–1159 (2008).

Plugge, S., Rasmussen, A., Egger, R. & Flensberg, K. Majorana box qubits. New J. Phys. 19, 012001 (2017).

Karzig, T. et al. Scalable designs for quasiparticle-poisoning-protected topological quantum computation with Majorana zero modes. Phys. Rev. B 95, 235305 (2017).

Takei, S., Fregoso, B. M., Hui, H.-Y., Lobos, A. M. & Das Sarma, S. Soft superconducting gap in semiconductor Majorana nanowires. Phys. Rev. Lett. 110, 186803 (2013).

Gül, Ö. et al. Hard superconducting gap in InSb nanowires. Nano Lett. 17, 2690–2696 (2017).

Krogstrup, P. et al. Epitaxy of semiconductor-superconductor nanowires. Nat. Mater. 14, 400 (2015).

Gazibegovic, S. et al. Epitaxy of advanced nanowire quantum devices. Nature 584, 434–438 (2017).

de Moor, M. W. A. et al. Electric field tunable superconductor-semiconductor coupling in Majorana nanowires. New J. Phys. 20, 103049 (2018).

Khan, S. A. et al. Highly transparent gatable superconducting shadow junctions. ACS Nano 14, 14605–14615 (2020).

Cao, J., Wang, Q. & Dai, H. Electron transport in very clean, as-grown suspended carbon nanotubes. Nat. Mater. 4, 745–749 (2005).

Octavio, M., Tinkham, M., Blonder, G. E. & Klapwijk, T. M. Subharmonic energy-gap structure in superconducting constrictions. Phys. Rev. B 27, 6739–6746 (1983).

Nilsson, H. A., Samuelsson, P., Caroff, P. & Xu, H. Q. Supercurrent and multiple Andreev reflections in an InSb nanowire Josephson junction. Nano Lett. 12, 228–233 (2012).

Li, S. et al. Coherent charge transport in ballistic InSb nanowire Josephson junctions. Sci. Rep. 6, 24822 (2016).

Rosdahl, T. Ö., Vuik, A., Kjaergaard, M. & Akhmerov, A. R. Andreev rectifier: a nonlocal conductance signature of topological phase transitions. Phys. Rev. B 97, 045421 (2018).

Lai, Y.-H., Sau, J. D. & Das Sarma, S. Presence versus absence of end-to-end nonlocal conductance correlations in Majorana nanowires: Majorana bound states versus Andreev bound states. Phys. Rev. B 100, 045302 (2019).

Pan, H., Sau, J. D. & Das Sarma, S. Three-terminal nonlocal conductance in Majorana nanowires: Distinguishing topological and trivial in realistic systems with disorder and inhomogeneous potential. Phys. Rev. B 103, 014513 (2021).

Blonder, G. E., Tinkham, M. & Klapwijk, T. M. Transition from metallic to tunneling regimes in superconducting microconstrictions: excess current, charge imbalance, and supercurrent conversion. Phys. Rev. B 25, 4515–4532 (1982).

Beenakker, C. W. J. Quantum transport in semiconductor-superconductor microjunctions. Phys. Rev. B 46, 12841–12844 (1992).

Vijay, S. & Fu, L. Teleportation-based quantum information processing with Majorana zero modes. Phys. Rev. B 94, 235446 (2016).

Béri, B. & Cooper, N. R. Topological Kondo effect with Majorana fermions. Phys. Rev. Lett. 109, 156803 (2012).

Bjergfelt, M. et al. Superconducting vanadium/indium-arsenide hybrid nanowires. Nanotechnology 30, 294005 (2019).

Rieger, T. et al. Crystal phase transformation in self-assembled InAs nanowire junctions on patterned Si substrates. Nano Lett. 16, 1933–1941 (2016).

Carrad, D. J. et al. Shadow epitaxy for in situ growth of generic semiconductor/superconductor hybrids. Adv. Mater. 32, 1908411 (2020).

Boscherini, F. et al. Exchange reaction, clustering, and surface segregation at the Al/InSb(110) interface. Phys. Rev. B 35, 9580–9585 (1987).

Thomas, C. et al. Toward durable Al-InSb hybrid heterostructures via epitaxy of 2ML interfacial InAs screening layers. Phys. Rev. Mater. 3, 124202 (2019).

Badawy, G. et al. High mobility stemless InSb nanowires. Nano Lett. 19, 3575–3582 (2019).

Meservey, R. & Tedrow, P. M. Properties of very thin aluminum films. J. Appl. Phys. 42, 51–53 (1971).

Courtois, H., Meschke, M., Peltonen, J. T. & Pekola, J. P. Origin of hysteresis in a proximity Josephson junction. Phys. Rev. Lett. 101, 067002 (2008).

Ambegaokar, V. & Baratoff, A. Tunneling between superconductors. Phys. Rev. Lett. 10, 486–489 (1963).

Doh, Y.-J. et al. Tunable supercurrent through semiconductor nanowires. Science 309, 272–275 (2005).

Fulton, T. A. & Dunkleberger, L. N. Lifetime of the zero-voltage state in Josephson tunnel junctions. Phys. Rev. B 9, 4760–4768 (1974).

Tinkham, M. Introduction to Superconductivity (Dover Publications, 1996).

Scheer, E., Joyez, P., Esteve, D., Urbina, C. & Devoret, M. H. Conduction channel transmissions of atomic-size aluminum contacts. Phys. Rev. Lett. 78, 3535–3538 (1997).

Nijholt, B. & Akhmerov, A. R. Orbital effect of magnetic field on the Majorana phase diagram. Phys. Rev. B 93, 235434 (2016).

Antipov, A. E. et al. Effects of gate-induced electric fields on semiconductor Majorana nanowires. Phys. Rev. X 8, 031041 (2018).

Abay, S. et al. High critical-current superconductor-InAs nanowire-superconductor junctions. Nano Lett. 12, 5622–5625 (2012).

Mourik, V. et al. Signatures of Majorana fermions in hybrid superconductor-semiconductor nanowire devices. Science 336, 1003–1007 (2012).

Law, K. T., Lee, P. A. & Ng, T. K. Majorana fermion induced resonant Andreev reflection. Phys. Rev. Lett. 103, 237001 (2009).

Pan, H. & Das Sarma, S. Physical mechanisms for zero-bias conductance peaks in Majorana nanowires. Phys. Rev. Res. 2, 013377 (2020).

Chang, W. et al. Hard gap in epitaxial semiconductor-superconductor nanowires. Nat. Nanotechnol. 10, 232–236 (2015).

Kjaergaard, M. et al. Quantized conductance doubling and hard gap in a two-dimensional semiconductor-superconductor heterostructure. Nat. Commun. 7, 12841 (2016).

Borsoi, F. et al. Single-shot fabrication of semiconducting-superconducting nanowire devices. Adv. Funct. Mater. 2102388 (2021).

Zhang, H. et al. Ballistic superconductivity in semiconductor nanowires. Nat. Commun. 8, 16025 (2017).

Heedt, S. et al. Adiabatic edge channel transport in a nanowire quantum point contact register. Nano Lett. 16, 4569–4575 (2016).

Gül, Ö. et al. Ballistic Majorana nanowire devices. Nat. Nanotechnol. 13, 192–197 (2018).

Nichele, F. et al. Scaling of Majorana zero-bias conductance peaks. Phys. Rev. Lett. 119, 136803 (2017).

Grivnin, A., Bor, E., Heiblum, M., Oreg, Y. & Shtrikman, H. Concomitant opening of a bulk-gap with an emerging possible Majorana zero mode. Nat. Commun. 10, 1940 (2019).

Chen, J. et al. Experimental phase diagram of zero-bias conductance peaks in superconductor/semiconductor nanowire devices. Sci. Adv. 3, e1701476 (2017).

Anselmetti, G. L. R. et al. End-to-end correlated subgap states in hybrid nanowires. Phys. Rev. B 100, 205412 (2019).

Yu, P. et al. Non-Majorana states yield nearly quantized conductance in proximatized nanowires. Nat. Phys. 17, 482–488 (2021).

Moore, C., Stanescu, T. D. & Tewari, S. Two-terminal charge tunneling: disentangling Majorana zero modes from partially separated Andreev bound states in semiconductor-superconductor heterostructures. Phys. Rev. B 97, 165302 (2018).

Gielen, A. W. J. & Valega Mackenzie, F. O. Thermo-mechanical effects in Majorana type quantum devices. Microelectron. Reliab. 62, 50–57 (2016).

Vuik, A., Nijholt, B., Akhmerov, A. R. & Wimmer, M. Reproducing topological properties with quasi-Majorana states. SciPost Phys. 7, 61 (2019).

Pan, H., Cole, W. S., Sau, J. D. & Das Sarma, S. Generic quantized zero-bias conductance peaks in superconductor-semiconductor hybrid structures. Phys. Rev. B 101, 024506 (2020).

de Jong, D. et al. Rapid detection of coherent tunneling in an InAs nanowire quantum dot through dispersive gate sensing. Phys. Rev. Appl. 11, 044061 (2019).

Dynes, R. C., Narayanamurti, V. & Garno, J. P. Direct measurement of quasiparticle-lifetime broadening in a strong-coupled superconductor. Phys. Rev. Lett. 41, 1509–1512 (1978).

Liu, C.-X., Setiawan, F., Sau, J. D. & Das Sarma, S. Phenomenology of the soft gap, zero-bias peak, and zero-mode splitting in ideal Majorana nanowires. Phys. Rev. B 96, 054520 (2017).

Acknowledgements

We are grateful to Olaf Benningshof for valuable technical support and to Emrah Yücelen, Gijs de Lange, Bernard van Heck, Andrey E. Antipov and Jay D. Sau for fruitful discussions. We thank Morteza Aghaee for support with dielectric deposition and TNO for providing access to their cleanroom facilities. This work has been financially supported by the Dutch Organization for Scientific Research (NWO), the Foundation for Fundamental Research on Matter (FOM) and Microsoft Corporation Station Q. M.P.N. acknowledges support within the POIR.04.04.00-00-3FD8/17 project as part of the HOMING programme of the Foundation for Polish Science co-financed by the European Union under the European Regional Development Fund.

Author information

Authors and Affiliations

Contributions

S.H., M.Q.P., F.B., N.d.J., P.A., K.v.H. and L.P.K. conceived the experiment. S.H., M.Q.P., F.B., N.v.L., G.P.M., J.S. and M.A.Y.v.d.P. contributed to the fabrication and/or electrical transport measurements of the devices. S.H. and F.B. analysed the transport data. A.F. fabricated the substrates. M.P.N. performed numerical simulations of the MAR processes. M.A. made critical upgrades to the equipment and provided technical support. G.B., S.G. and E.P.A.M.B. carried out the nanowire synthesis. K.L. prepared the FIB lamellae. S.K. performed the TEM analysis. S.H., M.Q.P. and F.B. wrote the manuscript. All authors provided critical feedback. L.P.K. supervised the project.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Peer review information Nature Communications thanks Hongqi Xu, Thomas Sand Jespersen and the other, anonymous, reviewer(s) for their contribution to the peer review of this work. Peer reviewer reports are available.

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Heedt, S., Quintero-Pérez, M., Borsoi, F. et al. Shadow-wall lithography of ballistic superconductor–semiconductor quantum devices. Nat Commun 12, 4914 (2021). https://doi.org/10.1038/s41467-021-25100-w

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-021-25100-w

This article is cited by

-

Hard superconducting gap in germanium

Communications Materials (2023)

-

Spin-filtered measurements of Andreev bound states in semiconductor-superconductor nanowire devices

Nature Communications (2023)

-

Realization of a minimal Kitaev chain in coupled quantum dots

Nature (2023)

-

Electrostatic control of the proximity effect in the bulk of semiconductor-superconductor hybrids

Nature Communications (2023)

-

Joule spectroscopy of hybrid superconductor–semiconductor nanodevices

Nature Communications (2023)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.