Abstract

The development of organic thin-film transistors (OTFTs) with low power consumption and high gain will advance many flexible electronics. Here, by combining solution-processed monolayer organic crystal, ferroelectric HfZrOx gating and van der Waals fabrication, we realize flexible OTFTs that simultaneously deliver high transconductance and sub-60 mV/dec switching, under one-volt operating voltage. The overall optimization of transconductance, subthreshold swing and output resistance leads to transistor intrinsic gain and amplifier voltage gain over 5.3 × 104 and 1.1 × 104, respectively, which outperform existing technologies using organics, oxides and low-dimensional nanomaterials. We further demonstrate battery-powered, integrated wearable electrocardiogram (ECG) and pulse sensors that can amplify human physiological signal by 900 times with high fidelity. The sensors are capable of detecting weak ECG waves (undetectable even by clinical equipment) and diagnosing arrhythmia and atrial fibrillation. Our sub-thermionic OTFT is promising for battery/wireless powered yet performance demanding applications such as electronic skins and radio-frequency identification tags, among many others.

Similar content being viewed by others

Introduction

Organic thin-film transistors (OTFTs) have been extensively pursued for printable and flexible electronic applications owing to their intrinsic flexibility and low-cost processing1,2,3,4,5,6. Many applications, such as Internet of Things (IoT) and wearable electronics, require low-voltage operation while providing high enough current to drive the circuits or high gain to amplify small signals. So far, however, there exist considerable challenges to make OTFT competitive over carbon nanotube films7, two-dimensional (2D) materials8 and oxides9. First, the mobility of organic semiconductors is generally lower than their inorganic counterparts. This leads to low transconductance (gm) and intrinsic gain (\(A_{\mathrm{i}} \,=\, g_{\mathrm{m}} \cdot r_0\), where r0 is output resistance). Second, the contact resistance, which partly arises the vertical access resistance from the finite film thickness and disorders introduced by conventional fabrication processes (such as lithography and metal deposition), is a major limiting factor towards high-frequency operation10. Third, the switching of OTFTs is often far from ideal, which results in large operating voltage (Vdd)11. Despite significant efforts, it remains a challenge to maintain subthreshold swing (SS) close to the Boltzmann thermionic limit (\(ln\left( {10} \right)\frac{{k_BT}}{q} \approx 60\,{\mathrm{mV}}/{\mathrm{dec}}\), where q is elementary charge, kB is Boltzmann’s constant, and T is temperature) over extended range and Vdd low enough for complete battery/wireless operation12,13,14.

Recently, negative capacitance (NC) effect from ferroelectric hafnium oxides provides a promising solution for low-power and complementary metal-oxide-semiconductor (CMOS) compatible electronics15,16,17,18,19,20,21,22,23,24. Experimentally, NC transistors have been implemented on silicon25,26,27, germanium28 and 2D materials29,30, showing evidence of sub-60 mV/dec switching and enhanced gm. Moreover, a transition from negative to positive drain-induced barrier lowing (DIBL) was theoretically predicted and experimentally observed in NC transistors16,29. This would lead to infinite r0 and intrinsic gain near the transition region, which is desirable for high-gain analog amplifiers. However, this unique advantage of NC transistors has not been fully exploited so far.

Here, we combine solution-processed OTFT with ferroelectric HfZrOx (HZO) gating to demonstrate flexible sub-thermionic organic transistors as well as ultra-high-gain amplifier circuits. Our technology has several unique features. First, the monolayer organic crystal film ensures excellent gate control while maintaining high channel mobility up to 10.4 cm2 V−1 s−1. Second, the double-well energy landscape of ferroelectric gating and associated NC effect break the thermionic limit in SS (60 mV/dec) and transconductance efficiency (38.7 S/A) and simultaneously enhances on-current and gm by saving overdrive voltage loss15,23,29,30. In addition, the negative DIBL introduced by ferroelectric HZO16,29 produces large r0 ~1010 Ω. Third, the uniform film morphology and van der Waals (vdW) integration of metal electrodes31 ensure direct and damage-free contact with the channel, giving contact resistance below 60 Ωcm. Together, these systematic optimizations not only significant improve the performance and power consumption of OTFTs, but also deliver the highest gain for any TFT technologies. Finally, our sub-thermionic OTFTs are low-temperature solution processed, scalable to large area and compatible with flexible substrates, which allow us to fabricate integrated wearable sensors health monitoring and diagnosis.

Results

Device fabrication and characterizations

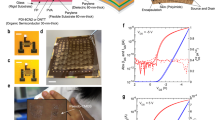

For device fabrication, we first grew HZO/Al2O3 gate dielectrics on highly doped silicon wafers by atomic layer deposition (ALD) and carried out solution shearing of p-type 2,9-didecyldinaphtho[2,3-b:2′,3′-f]thieno[3,2-b]thiophene (C10-DNTT) as channel material32,33 (see “Methods” section for experimental details). The Hf:Zr atomic ratio was close to 1:1 as revealed by X-ray photoelectron spectroscopy (Supplementary Fig. 1b). The HZO showed low surface roughness (~0.3 nm) and ferroelectric properties as confirmed by atomic force microscopy (AFM), piezoelectric force microscopy, and polarization-electric field (P-E) loop measurements (Supplementary Fig. 1). Highly uniform monolayer organic films were obtained by optimizing the substrate temperature and blade speed in the shearing process34 (Supplementary Fig. 2). Figure 1a, f show optical images of monolayer C10-DNTT films on 2-in. silicon wafer and polyimide, respectively. The film thickness was characterized by ellipsometry and AFM, both showing ~4 nm (corresponding to monolayer) with excellent wafer-scale uniformity (Fig. 1b, c). The films were highly crystalline with herringbone lattice, consistent with C10-DNTT bulk crystals (Fig. 1d). Under optimized conditions, the domain size could reach several millimeters (Fig. 1e), which effectively reduced domain boundaries within device channel. The average field-effect mobility of monolayer OTFTs on Al2O3 dielectrics was 8.44 ± 1.61 cm2 V−1 s−1 (Supplementary Fig. 3), further proving the high quality of C10-DNTT films. On ultra-thin polyimide substrate, the monolayer film was highly transparent (>97%) and conformable to epidermis to allow the construction of skin-like wearable devices (Fig. 1g, Supplementary Figs. 2b and 4).

a Photograph of uniform monolayer C10-DNTT film on 2-in. Si wafer. b The thickness mapping of the sample in a using spectral ellipsometry. AFM (c), high-resolution AFM (d) and cross-polarized optical micrograph (e) of the monolayer C10-DNTT film. Photograph of monolayer C10-DNTT film on polyimide substrate (f) and flexible device array laminated on a fingertip (g).

It is well-known that conventional OTFT fabrication processes can damage the organic films, especially for monolayer35. To this end, we developed solvent-free and low-energy vdW fabrication process as illustrated in Supplementary Fig. 5. This approach is readily scalable to wafer-scale with nearly 100% yield and micrometer resolution (Fig. 2a). Briefly, we first prepared patterned Au contact electrodes on a silicon wafer. The electrodes were mechanically released using PMMA and thermal release tape and gently laminated onto the pre-patterned channel areas. Such low-energy process preserved the integrity of monolayer C10-DNTT channel and contact interface as shown by the cross-sectional transmission electron microscopy (TEM) image (Fig. 2b). After removing the tape, electron-beam lithography (EBL) was performed to remove the PMMA on probing pads for electrical measurements. The intimate and damage-free contact to the monolayer channel indeed led to contact resistance of 59.4 ± 5.3 Ωcm as measured by transfer length method (Supplementary Fig. 6), close to the record for OTFTs (Supplementary Table 1).

a Photographs of device arrays fabricated on silicon substrate. The length to width ratio (L/W) of device channel is 5 μm/180 μm. b False-color cross-section TEM image of a device contact region, clearly showing the Au/C10-DNTT/Al2O3/HZO/Si stack. c Double-sweep Ids − Vgs curves of the sub-thermionic OTFT at Vds = −0.1 V (blue) and −1 V (red). No hysteresis is observed. The black-dashed line is the gate leakage current. d Ids − Vds curves of the sub-thermionic OTFT. From bottom to top, Vgs is from −0.3 to −1 V. e SS (black) and transconductance efficiency (red) as a function of Ids for the device in c. The Boltzmann limit reference corresponds to 300 K under which our measurements were taken. f Statistical distributions of one-decade SS for 50 devices. g Comparison of Ion/Ioff and normalized transconductance at |Vgs(on) − Vgs(off)| = 1 V among OTFT technologies using different dielectrics. The extracted data are listed in Supplementary Table 2. h Comparison of intrinsic gain among different TFT technologies.

Electrical performance of sub-thermionic OTFTs and device modeling

Figure 2c, d presents the room temperature transfer (Ids − Vgs) and output (Ids − Vds) characteristics of a typical sub-thermionic monolayer OTFT under Vdd = 1 V. We observed several remarkable features, including extended subthreshold region with a steep slope, close-to-zero threshold voltage (Vth), on/off ratio over 108, excellent saturation behavior, and no hysteresis. The derived point SS was below 60 mV/dec for more than two decades (Fig. 2e). The average SS was 58.6 and 60.9 mV/dec for one and five decades of Ids, respectively. The device also delivered superior on-state performance. In particular, the normalized gm reached high value of 0.41 μSμm−1 under one-volt operation (Supplementary Table 2), suggesting possible radio-frequency applications10. More importantly, the transconductance efficiency, \(\frac{{g_m}}{{I_{ds}}} \,=\, 41.6\) S/A, exceeded the theoretical limit of \(\frac{q}{{k_BT}} \,=\, 38.7\) S/A4 imposed by Boltzmann distribution of carriers (Fig. 2e). The high transconductance efficiency was maintained over several orders of Ids, which was desirable in analog circuit design but difficult for CMOS36. To evaluate the device variations, we measured 50 OTFTs (the transfer characteristics and statistics are shown in Supplementary Fig. 7). Figure 2f presents the histogram of SS (over one decade of Ids rather than point SS), showing Gaussian-like distribution with 2.5% variation as measured from the full-width at half-maximum. Sub-60 mV/dec switching was observed in 68% (34 out of 50) devices.

To demonstrate the advantage of sub-thermionic OTFTs, we fabricated monolayer OTFTs on 24 nm Al2O3/Si substrate (without HZO). The minimum SS of these “normal” devices was 65–75 mV/dec and degraded quickly with Ids (Supplementary Fig. 8a). Consequently, sub-thermionic OTFTs delivered more than one order of magnitude higher on-current and gm under the same Vdd (Supplementary Fig. 8). These observations were consistent with a recent theoretical model based on realistic capacitance analysis23.

To gain further insight of the device physics, we performed quantitative modeling using an equivalent circuit model in Supplementary Fig. 9. To achieve simultaneous hysteresis-free and sub-thermionic switching, the ferroelectric HZO capacitance (CFE) needs to fall between that of Al2O3 (CAlOx) and \(C_{{\mathrm{MOS}}} \approx \big( {C_{{\mathrm{AlO}}_{\mathrm{x}}}^{ - 1} \,+\, \big( {C_{{\mathrm{j}},{\mathrm{S}}} \,+\, C_{{\mathrm{j}},{\mathrm{D}}}} \big)^{ - 1}} \big)^{ - 1}\), where Cj,S/D are S/D Schottky junction capacitances (Supplementary Fig. 9)23. The low dielectric constant and low channel doping of organic channel generate Cj,S/D ≈ 6 × 10−7 F/cm2, which is about one order of magnitude smaller than CAlOx (3.6 × 10−6 F/cm2, 2 nm Al2O3). This defines an extended design space for CFE. The thin Al2O3 also reduces the minimum thickness of HZO to achieve sub-60 mV/dec switching. Supplementary Figure 9d (solid blue line) plots SS as a function of \(C_{FE}^{ - 1}\) using our experimental device geometry. The CFE of 22 nm HZO (derived from fitting of P-E loop, Supplementary Fig. 1d) gives SS = 56.5 mV/dec (red star), in good agreement with experimental data. The correct capacitance matching of sub-thermionic OTFTs also makes the hysteresis of Ids − Vgs curve negligible16,23. Furthermore, we quantitatively calculated the transistor characteristics using a compact model incorporating time-dependent depolarization and multi-domain Landau–Khalatnikov theory37. Supplementary Figure 9e, f shows that the calculated transfer and output curves match experiments very well, which validates the above model analysis.

We further benchmark our sub-thermionic OTFTs with other TFT technologies. Figure 2g compares the gm and on/off ratio (data from ten devices) with several representative OTFT technologies, under the same |Vgs(on) − Vgs(off)| = 1 V (see Supplementary Table 2 for details). Our data points are located at the upper right corner of the plot, exhibiting significantly improved gm while maintaining on/off ratio greater than 108. Figure 2h summarizes the intrinsic gain of various TFT technologies. Our monolayer sub-thermionic OTFTs exhibit the highest Ai of 5.3 × 104, which is more than one order of magnitude higher than oxides38 and Schottky barrier TFTs4,39, and more than two orders of magnitude higher than 2D materials40 and silicon. Other than gm, an important reason for the high Ai is large r0 ~1010 Ω due to near-zero DIBL in the subthreshold region (Supplementary Fig. 10). This can be understood as a consequence of the transition from negative to positive DIBL, leading to infinite r0 at the transition (Supplementary Fig. 10). This is a unique property of NC transistors16,29 and is also captured by our modeling (Supplementary Fig. 9g). It is important to note that the overall improvement of transistor performance (gm, r0, Ai, SS) is accomplished by systematic optimization, including high mobility material, monolayer channel, clean contact interface and ferroelectric dielectrics. To verify the importance of monolayer channel, we fabricated devices with thicker channel and observed inferior SS, on-current and gm due to poor electrostatics and contact resistance35,41 (Supplementary Fig. 8).

The devices also had good temperature and operational stability. The sub-60 mV/dec switching was preserved after 2-month storage at room temperature, with only slight shift of Vth and decrease of on-current (Supplementary Fig. 11a). Variable-temperature measurements showed that the SS was below thermionic limit from 250 to 375 K (Supplementary Fig. 11e, f), owing to the high Curie temperature of the HZO19. In addition, continuous bias stress measurements under Vds = Vgs = −1.5 V also showed little degradation of device performance after 104 s (Supplementary Fig. 11b, c). Further, we conducted cycle stability test for the transistors, showing excellent cycle stability under repeated gate voltage pulses with 1 Hz frequency (Supplementary Fig. 11d). The stability can be further improved by proper passivation. In terms of frequency limit, previous studies have shown that HZO can properly function up to MHz42, which is adequate for OTFT applications.

Ultra-high-gain amplifier circuits

By designing proper electrode patterns, we could build functional circuits, such as inverter and logic gates using local backgate devices (Fig. 3, Supplementary Fig. 12, see “Methods” section for detailed fabrication processes). There is practically no limit in the circuit complexity by vdW integration as long as the transistors are co-planar. For very large-scale integration that requires multiple layers of interconnects, the upper layers can be fabricated by conventional lithography or printing as they are separated from the channel. Figure 3a shows the circuit and optical image of an enhancement-depletion mode inverter using two sub-thermionic OTFTs with different dimensions (the transfer characteristics are presented in Supplementary Fig. 13a). The inverter exhibited full swing output near zero input voltage with peak power of ~50 nW (Fig. 3b and Supplementary Fig. 13b). Remarkably, we obtained giant voltage gain (Av) of 4.1 × 103 (1.1 × 104) under Vdd = −1 V (−3 V) (Fig. 3c). On the other hand, control amplifiers fabricated on Al2O3/Si substrate showed 40 times lower Av (Supplementary Fig. 13c, d). Therefore, we conclude that the high gain is enabled by steep switching in the transistor characteristics, which are unique properties of sub-thermionic OTFTs. Figure 3d benchmarks the Av of similar amplifier structures based on organics, metal oxides, 2D materials and carbon nanotubes (see Supplementary Table 3 for details). The gain of our devices again outperforms these existing technologies by orders of magnitude while maintaining low Vdd, which hold promise for wearable electronics and IoT applications.

a Equivalent circuit diagram (left) and optical microscope image (right) of an enhancement-depletion mode amplifier. The dotted boxes indicate organic film areas for load and drive transistors. b Voltage transfer characteristics under Vdd = −1, −2 and −3 V, respectively. c Av as a function of input voltage derived from b. d Comparison of Av among similar amplifier circuits using different materials and processes. The extracted data are listed in Supplementary Table 3.

Flexible sub-thermionic OTFTs and circuits

For wearable applications, it is important to examine the device performance on flexible substrates. To this end, polyimide was used because it was compatible with the processing temperature of HZO. Spin-coated polyimide (~10 μm thick) on sacrificial Si substrate ensured low surface roughness for solution shearing and mechanical reliability under extreme folding or crumpling. Figure 4a illustrates the structure and photograph of device arrays with local backgates. The transfer characteristics of 100 devices exhibit small variations in Vth and SS (Fig. 4b, c). Importantly, the steep slope and high gain were preserved on polyimide substrate, with 75% (75 out of 100) devices exhibiting sub-60 mV/dec switching and lowest SS = 56.5 mV/dec (Fig. 4c). Figure 4d presents the transfer curves of a flexible inverter with Av = 9.7 × 103, which was comparable to that on Si substrate. Furthermore, the devices were robust under mechanical bending. Both gm and SS showed little degradation during 104 repeated bending tests to 10 mm radius of curvature (Fig. 4e).

a Photograph of OTFT arrays fabricated on 2-in. polyimide substrate (left) and schematic view of the device structure (right). b Ids − Vgs curves of 100 devices under Vds = −1 V. The L/W of device channel is 5 μm/180 μm. c Statistical distributions of SS for the devices in b. d Voltage transfer characteristics (solid lines) and Av (symbols) of an enhancement-depletion mode amplifier on flexible substrate, under Vdd = −1 and −3 V. e Bending test of a device on polyimide substrate. Both gm and SS remain stable during 104 bending cycles. Inset shows a photograph of flexible device arrays under bending.

Integrated wearable ECG and pulse sensors

Next, we demonstrated the applications of sub-thermionic OTFT technology in wearable electrocardiogram (ECG) and pulse sensors. Human body constantly produces vital physiological signals, such as biopotentials and metabolites, in the range of microvolt to millivolt43,44,45,46. Therefore, on-site signal amplification using low-voltage and high-gain circuitry is essential for integrated wearable sensors but very challenging. We integrated a flexible enhancement-depletion mode amplifier on a custom-designed flexible circuit board, which could be easily laminated on the front chest (Fig. 5a, b). All the amplifiers were operated under Vdd = −1 V with the peak Av greater than 1000. The Vdd was supplied either by an external voltage source or a 1.5 V coin battery (Fig. 5c, a voltage divider was used to reduce Vdd), showing similar performance (Supplementary Fig. 14). Figure 5d plots the amplified ECG signal of a healthy male subject, clearly showing all the expected waveforms (P, Q, R, S, T and U waves). The signal amplitude was ~350 mV, corresponding to an amplification factor of 324. The raw ECG signal could be obtained by deconvoluting the amplifier transfer curve (the blue solid line in Fig. 5e, see Supplementary Fig. 15 for details), which agreed well with the data recorded by a clinical grade commercial equipment (Prince 180B by Heal Force, the gray-dashed line in Fig. 5e). Figure 5g, h demonstrates continuous monitoring of ECG over several minutes. The signal fidelity, waveform and amplification factor remained stable during the test, which was essential for long-term health monitoring. To further prove the signal fidelity, we simultaneously measured the ECG signal by our sensor and commercial equipment (Supplementary Movie 1). Figure 5f compares the power spectral density. We can see that the amplified ECG shares the same waveform with the commercial equipment, with the most prominent peak at 1.29 Hz corresponding to the heart rate of the subject. Importantly, the amplitude of power density was enhanced by ~105 times, consistent with the amplification factor of ~300. Battery-powered ECG also showed similar power spectral density.

a Cartoon illustration of the use of amplifier circuit to acquire human ECG signals. b Photograph of a flexible amplifier module attached to a human chest. c Photograph of the amplifier module, with a coin battery, a voltage divider and amplifier circuit integrated on a flexible circuit board. d Amplified ECG signal of a human subject. e Deconvoluted ECG signal using the amplifier’s transfer curve (blue solid line) and the ECG signal taken by commercial equipment on the same human subject (black-dashed line). f The power spectral density of ECG signals taken by commercial equipment (gray), our amplifier with external voltage source (red) and battery (green) as power supply. g Long-term ECG monitoring using our sensor. h The ECG signal of the 1st (upper panel) and 245th (lower panel) cycle in g. i Amplified ECG signal of a human subject with known arrhythmia history (bottom panel) and the corresponding heart rate (upper panel). j ECG signal of another human subject with AF, recorded by our sensor (bottom panel) and a clinical equipment (upper panel). k Photograph of an integrated pulse sensor using flexible carbon nanotube films and our amplifier circuit. Inset shows the circuit diagram. l Unconditioned and amplified pulse signal taken on the same human subject.

With excellent sensitivity and signal fidelity, our ECG sensors are capable of facilitating cardiopathy diagnoses. To this end, two hospital volunteers were tested. On subject A (female, mid-20s) who was diagnosed with arrhythmia, our sensor clearly captured the irregular heartbeat with a sudden change from 83 to 43 beats per minute (bpm) (Fig. 5i). On subject B (male, 80 s) who was diagnosed with atrial fibrillation (AF), our sensor was capable of detecting f wave with a frequency of 357 bpm, which was a direct signature of AF (Fig. 5j, lower panel). In contrast, the clinical ECG of same subject did not resolve f wave due to its weak amplitude (Fig. 5j, upper panel, taken by NIHON KOHDEN ECG-1350P). Currently, AF is the most common arrhythmia globally associated with the increased risk of stroke and heart failure. The ability to directly identify f wave will significantly increase the sensitivity and specificity of clinical diagnosis. Without any post-processing, the signal-to-noise ratio (SNR) of our ECG signal reached 42 dB, exceeding previously reported results47,48. The improved sensitivity and the ability to detect extremely weak signals are remarkable considering the simple circuity of our sensors.

As another example, we connected the amplifier to a flexible carbon nanotube sensor to measure wrist pulse signals (Fig. 5k). The pulse pressure-induced resistance change in the carbon nanotube film, resulting in a slight shift of amplifier input voltage. Figure 5l shows the measured pulse waveforms of a human subject with ~120 mV peak-to-valley amplitude, corresponding to amplification factor of 900. The details of the pulse waveforms including a systolic peak, a dicrotic notch, a reflected systolic peak and an end-diastolic notch were clearly resolved. The higher amplification compared to ECG was due to the smaller input signal amplitude (~0.13 mV vs. ~1 mV for ECG), which allowed the amplifier to work at the peak gain point. Compared to literatures, our ECG and pulse sensors show advantages in terms of Vdd, gain and SNR (Supplementary Table 4).

Discussion

We demonstrate the first sub-thermionic flexible OTFT technology by combining solution-processed monolayer organic channel, ferroelectric gate dielectrics and vdW device integration. The devices operate under one-volt and exhibit sub-60 mV/dec switching and record-high intrinsic gain. We further build amplifier circuits with ultra-high voltage gain of 1.1 × 104, which outperform existing TFT technologies by more than one order of magnitude. The flexible amplifiers are capable of amplifying human physiological signals by several hundred times with high fidelity, and detecting extremely weak ECG signals to facilitate clinical diagnosis. By developing more robust amplification schemes (such as differential amplification)48 and wireless data transmission49, we can envision all-organic, battery-powered patches for high-precision health monitoring and real-time cloud-based diagnosis.

Methods

Preparation of HZO/Al2O3 dielectrics

The HZO film was deposited by ALD on p++ silicon (100) substrate at 200 °C and base pressure of ~1 Pa using Tetrakis(dimethylamido) hafnium as Hf source, Tetrakis(dimethylamido) zirconium as Zr source and H2O as oxidant. We used 20 sccm N2 as carrier gas. The HfOx and ZrOx were deposited sequentially with 1:1 ratio. Then 2 nm AlOx capping layer was deposited by ALD in situ for capacitance matching, using trimethylaluminium and H2O as sources. The pulse/purge time for Hf, Zr and H2O precursors were 250 ms/30 s, 20 ms/30 s and 30 ms/30 s, respectively. The substrate was undergone 350 °C rapid thermal annealing for 1 min in N2 to crystallize the HZO.

We fabricated the HZO/Al2O3 dielectrics on polyimide substrate using the similar method mentioned above. To prepare the polyimide substrate, we spin-coated polyimide solution (AA-49, KANEKA) on SiO2/Si substrate, and then baked at 350 °C for 1 h on a hotplate.

Solution shearing of monolayer C10-DNTT films

The C10-DNTT powder was dissolved in 1,2,3,4-tetrahydronaphthalene (tetralin) at 85 °C with a concentration of 0.2 mg/mL. The growth of monolayer C10-DNTT was carried out in a home-built solution shearing setup with heaters on both the blade and substrate (Supplementary Fig. 2). The temperature of the blade and substrate was set to 65 °C. Overall, 150 μL of C10-DNTT solution was injected for a 2 in. size substrate and a constant shear velocity of 3 μm/s was established by using a linear translation stage during the shearing processes.

Characterizations of C10-DNTT film and OTFTs

We used ellipsometry mapping, high-resolution AFM and cross-polarized optical microscopy to characterize the monolayer C10-DNTT film. The ellipsometry mapping was performed on a Woollam RC2-XI mapping ellipsometer in the wavelength range of 210–2500 nm. For high-resolution AFM, the experiments were conducted on Asylum Cypher under ambient conditions. The cross-polarized optical reflection micrographs were performed by the ScanPro spectro-microscope under the white light. We used cross-sectional TEM to characterize the interface and thickness of sub-thermionic OTFTs. The TEM specimens were prepared using a FEI Scois Dualbeam focused ion beam. After that, the specimens were characterized using a high-resolution JEOL JEM-2100F TEM with acceleration voltage of 200 kV equipped with energy-dispersive spectroscopy detector.

vdW integration of contacts

First, we prepare patterned gold electrodes with 50 nm thickness on a silicon substrate using EBL and electron-beam evaporation (EBE). Next, a PMMA layer was spin-coated, followed by the lamination of thermal released tape (TRT). The TRT/PMMA/Au electrode stack was carefully released from silicon substrate and was align transferred to patterned monolayer C10-DNTT film. Then the TRT was separated at 90 °C. Finally, the PMMA layer was patterned by EBL to remove the PMMA on probing pads for electrical measurements.

Fabrication of amplifiers with local backgate

First, we fabricated 10 nm Ti/20 nm Au backgate electrodes on SiO2/Si substrate using EBL and EBE. Then, HZO/Al2O3 was deposited using ALD. EBL and inductive coupled plasma reactive ion etching (BCl3 and Cl2) were adopted to etch HZO/Al2O3 and open via holes to backgate electrodes. Then, monolayer C10-DNTT films were grown by the solution shearing process. Finally, the source/drain electrodes (50 nm Au) were align transferred onto the C10-DNTT films. For the device on the polyimide substrate, the processes are similar.

Electrical measurements

Electrical measurements were carried out by an Agilent B1500 semiconductor parameter analyzer in a probe station under ambient conditions. And the temperature during the OTFT’s electrical measurement was set at 300 K.

Electrocardiogram and pulse detection

The flexible amplifier connected with two conventional gel electrodes to obtain the ECG signal. One was placed on the skin above the lower left part of heart and connected to a bias voltage to set the signal at the amplifier optimal work point. And another was placed on the upper right part of the heart as the input signal of the amplifier. We use Agilent B1500 to collect ECG signal and the sampling frequency was 40 Hz. Fast Fourier transforms were applied to identify the power density of the recorded ECG signal. The SNR was calculated by the maximum peak value of the signal divided by the root mean square of the noise area. Inset of Fig. 5k shows the circuit diagram for pulse detection. The resistance of the flexible carbon nanotube sensor is about 1 kΩ. By connecting it with a 1 kΩ divider resistor, the resistance change of the sensor was converted into a voltage signal, then as the input of the amplifier. Agilent B1500 was used to collect the pulse signal.

The authors affirm that human research participants provided informed consent for publication of the video in Supplementary Movie 1. All human subjects involved in the ECG and pulse tests provided informed consent, and the study protocol was approved by local ethics committee on human research of Nanjing Drum Tower Hospital (2019-190-01).

Data availability

All data that support the findings of this study are available from the corresponding author upon reasonable request.

References

Sirringhaus, H. 25th anniversary article: organic field-effect transistors: the path beyond amorphous silicon. Adv. Mater. 26, 1319–1335 (2014).

Kaltenbrunner, M. et al. An ultra-lightweight design for imperceptible plastic electronics. Nature 499, 458–463 (2013).

Wang, S. et al. Skin electronics from scalable fabrication of an intrinsically stretchable transistor array. Nature 555, 83 (2018).

Jiang, C. et al. Printed subthreshold organic transistors operating at high gain and ultralow power. Science 363, 719 (2019).

Klauk, H., Zschieschang, U., Pflaum, J. & Halik, M. Ultralow-power organic complementary circuits. Nature 445, 745 (2007).

Wang, C., Dong, H., Jiang, L. & Hu, W. Organic semiconductor crystals. Chem. Soc. Rev. 47, 422–500 (2018).

Tang, J. et al. Flexible CMOS integrated circuits based on carbon nanotubes with sub-10 ns stage delays. Nat. Electron. 1, 191–196 (2018).

Akinwande, D., Petrone, N. & Hone, J. Two-dimensional flexible nanoelectronics. Nat. Commun. 5, 5678 (2014).

Myny, K. The development of flexible integrated circuits based on thin-film transistors. Nat. Electron. 1, 30–39 (2018).

Klauk, H. Will we see gigahertz organic transistors? Adv. Electron. Mater. 4, 1700474 (2018).

Liu, A., Zhu, H., Sun, H., Xu, Y. & Noh, Y.-Y. Solution processed metal oxide high-κ dielectrics for emerging transistors and circuits. Adv. Mater. 30, 1706364 (2018).

Borchert, J. W. et al. Flexible low-voltage high-frequency organic thin-film transistors. Sci. Adv. 6, eaaz5156 (2020).

Ji, D. et al. Copolymer dielectrics with balanced chain-packing density and surface polarity for high-performance flexible organic electronics. Nat. Commun. 9, 2339 (2018).

Yokota, T. et al. Flexible low-voltage organic transistors with high thermal stability at 250°C. Adv. Mater. 25, 3639–3644 (2013).

Salahuddin, S. & Datta, S. Use of negative capacitance to provide voltage amplification for low power nanoscale devices. Nano Lett. 8, 405–410 (2008).

Pahwa, G. et al. Analysis and compact modeling of negative capacitance transistor with high on-current and negative output differential resistance—part II: model validation. IEEE Trans. Electron Devices 63, 4986–4992 (2016).

Khan, A. I. et al. Negative capacitance in a ferroelectric capacitor. Nat. Mater. 14, 182–186 (2015).

Böscke, T. S., Müller, J., Bräuhaus, D., Schröder, U. & Böttger, U. Ferroelectricity in hafnium oxide thin films. Appl. Phys. Lett. 99, 102903 (2011).

Müller, J. et al. Ferroelectricity in simple binary ZrO2 and HfO2. Nano Lett. 12, 4318–4323 (2012).

Íñiguez, J., Zubko, P., Luk’yanchuk, I. & Cano, A. Ferroelectric negative capacitance. Nat. Rev. Mater. 4, 243–256 (2019).

Alam, M. A., Si, M. & Ye, P. D. A critical review of recent progress on negative capacitance field-effect transistors. Appl. Phys. Lett. 114, 090401 (2019).

Hoffmann, M. et al. Unveiling the double-well energy landscape in a ferroelectric layer. Nature 565, 464–467 (2019).

Cao, W. & Banerjee, K. Is negative capacitance FET a steep-slope logic switch? Nat. Commun. 11, 196 (2020).

Wang, H. et al. New insights into the physical origin of negative capacitance and hysteresis in NCFETs. In2018 IEEE Int. Elec. Dev. Meeting. 31.1.1–31.1.4 (IEEE, San Francisco, 2018).

Li, K. et al. Sub-60mV-swing negative-capacitance FinFET without hysteresis. In 2015 IEEE Int. Elec. Dev. Meeting. 22.6.1–22.6.4 (IEEE, Washington, DC, 2015).

Lee, M. H. et al. Prospects for ferroelectric HfZrOx FETs with experimentally CET = 0.98nm, SSfor = 42mV/dec, SSrev = 28mV/dec, switch-off <0.2V, and hysteresis-free strategies. In 2015 IEEE Int. Elec. Dev. Meeting. 22.5.1–22.5.4 (IEEE, Washington, DC, 2015).

Kwon, D. et al. Improved subthreshold swing and short channel effect in FDSOI n-channel negative capacitance field effect transistors. IEEE Electron Device Lett. 39, 300–303 (2018).

Zhou, J. et al. Ferroelectric HfZrOx Ge and GeSn PMOSFETs with sub-60 mV/decade subthreshold swing, negligible hysteresis, and improved Ids. In 2016 IEEE Int. Elec. Dev. Meeting. 12.2.1–12.2.4 (IEEE, San Francisco, 2016).

Si, M. et al. Steep-slope hysteresis-free negative capacitance MoS2 transistors. Nat. Nanotechnol. 13, 24–28 (2018).

Yu, Z. et al. Negative capacitance 2D MoS2 transistors with sub-60 mV/dec subthreshold swing over 6 orders, 250 μA/μm current density, and nearly-hysteresis-free. In 2017 IEEE Int. Elec. Dev. Meeting. 23.6.1–23.6.4 (IEEE, San Francisco, 2017).

Liu, Y., Huang, Y. & Duan, X. Van der Waals integration before and beyond two-dimensional materials. Nature 567, 323–333 (2019).

Kang, M. J. et al. Alkylated dinaphtho[2,3-b:2′,3′-f]Thieno[3,2-b]Thiophenes (Cn-DNTTs): organic semiconductors for high-performance thin-film transistors. Adv. Mater. 23, 1222–1225 (2011).

Peng, B., Huang, S., Zhou, Z. & Chan, P. K. L. Solution-processed monolayer organic crystals for high-performance field-effect transistors and ultrasensitive gas sensors. Adv. Funct. Mater. 27, 1700999 (2017).

Giri, G. et al. Tuning charge transport in solution-sheared organic semiconductors using lattice strain. Nature 480, 504–508 (2011).

He, D. et al. Ultrahigh mobility and efficient charge injection in monolayer organic thin-film transistors on boron nitride. Sci. Adv. 3, e1701186 (2017).

Terry, S. C. et al. Comparison of a BSIM3V3 and EKV MOSFET model for a 0.5 /spl mu/m CMOS process and implications for analog circuit design. IEEE Trans. Nucl. Sci. 50, 915–920 (2003).

Zhao, Y. et al. Surface potential-based compact model for negative capacitance FETs compatible for logic circuit: with time dependence and multidomain interaction. In 2019 IEEE Int. Elec. Dev. Meeting. 7.5.1–7.5.4 (IEEE, San Francisco, 2019).

Li, S. et al. Nanometre-thin indium tin oxide for advanced high-performance electronics. Nat. Mater. 18, 1091–1097 (2019).

Lee, S. & Nathan, A. Subthreshold Schottky-barrier thin-film transistors with ultralow power and high intrinsic gain. Science 354, 302 (2016).

Chang, H.-Y. et al. High-performance, highly bendable MoS2 transistors with high-K dielectrics for flexible low-power systems. ACS Nano 7, 5446–5452 (2013).

Peng, B. et al. Crystallized monolayer semiconductor for ohmic contact resistance, high intrinsic gain, and high current density. Adv. Mater. 32, 2002281 (2020).

Yu, Z. et al. Toward high-mobility and low-power 2D MoS2 field-effect transistors. In 2018 IEEE Int. Elec. Dev. Meeting. 22.4.1–22.4.4 (IEEE, San Francisco, 2018).

Kim, D.-H. et al. Epidermal electronics. Science 333, 838 (2011).

Chung, H. U. et al. Binodal, wireless epidermal electronic systems with in-sensor analytics for neonatal intensive care. Science 363, eaau0780 (2019).

Ershad, F. et al. Ultra-conformal drawn-on-skin electronics for multifunctional motion artifact-free sensing and point-of-care treatment. Nat. Commun. 11, 3823 (2020).

Lee, S. et al. Ultrasoft electronics to monitor dynamically pulsing cardiomyocytes. Nat. Nanotechnol. 14, 156–160 (2019).

Sekitani, T. et al. Ultraflexible organic amplifier with biocompatible gel electrodes. Nat. Commun. 7, 11425 (2016).

Sugiyama, M. et al. An ultraflexible organic differential amplifier for recording electrocardiograms. Nat. Electron. 2, 351–360 (2019).

Fiore, V. et al. An integrated 13.56-MHz RFID Tag in a printed organic complementary TFT technology on flexible substrate. IEEE Trans. Circuits Syst. I: Regul. Pap. 62, 1668–1677 (2015).

Acknowledgements

This work is supported by National Natural Science Foundation of China 61927808, 61521001, 61734003, 61851401, 91964202, 61861166001, 51861145202, 61821091, 61888102, 61825403 and 11922215; Natural Science Foundation of Jiangsu Province BK20202005; Strategic Priority Research Program of Chinese Academy of Sciences XDB 30000000; General Research Fund (GRF) HKU 17264016, HKU 17204517; Key Laboratory of Advanced Photonic and Electronic Materials, Collaborative Innovation Center of Solid-State Lighting and Energy-Saving Electronics, and the Fundamental Research Funds for the Central Universities, China.

Author information

Authors and Affiliations

Contributions

X.W. conceived and supervised the project. Z.L., B.P., J.Z., Z.Y., D.H., H.N., W.M., W.H., X.C., W.L., D.P., X.T., X.H., Y.S. X.F. and P.K.L.C. contributed to sample preparation, characterization, device fabrication, measurements and data analysis. Y.Z., J.W., L.L. and M.L. carried out circuit simulation and theoretical analysis. Z.L., J.Z., J.X., R.L., Y.Y. and D.S. performed the electrocardiogram test. Z.M. and L.P. fabricated and tested pulse sensors. K.C. and Y.L. performed TEM and data analysis. Z.L., Z.Y. and X.W. co-wrote the manuscript with input from other authors. All authors contributed to discussions.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Peer review information Nature Communications thanks Yong-Young Noh and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Luo, Z., Peng, B., Zeng, J. et al. Sub-thermionic, ultra-high-gain organic transistors and circuits. Nat Commun 12, 1928 (2021). https://doi.org/10.1038/s41467-021-22192-2

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-021-22192-2

This article is cited by

-

Recent advances on liquid intercalation and exfoliation of transition metal dichalcogenides: From fundamentals to applications

Nano Research (2024)

-

Organic heterojunction synaptic device with ultra high recognition rate for neuromorphic computing

Nano Research (2024)

-

Metal oxide ion gated transistors based sensors

Science China Technological Sciences (2024)

-

Deformable Catalytic Material Derived from Mechanical Flexibility for Hydrogen Evolution Reaction

Nano-Micro Letters (2024)

-

Ultralow contact resistance in organic transistors via orbital hybridization

Nature Communications (2023)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.