Abstract

Integrated photodetectors are essential components of scalable photonics platforms for quantum and classical applications. However, most efforts in the development of such devices to date have been focused on infrared telecommunications wavelengths. Here, we report the first monolithically integrated avalanche photodetector (APD) for visible light. Our devices are based on a doped silicon rib waveguide with a novel end-fire input coupling to a silicon nitride waveguide. We demonstrate a high gain-bandwidth product of 234 ± 25 GHz at 20 V reverse bias measured for 685 nm input light, with a low dark current of 0.12 μA. We also observe open eye diagrams at up to 56 Gbps. This performance is very competitive when benchmarked against other integrated APDs operating in the infrared range. With CMOS-compatible fabrication and integrability with silicon photonic platforms, our devices are attractive for sensing, imaging, communications, and quantum applications at visible wavelengths.

Similar content being viewed by others

Introduction

Integrated photonics platforms are well poised to meet the growing demands of both classical and quantum applications1,2. These platforms can accommodate multiple components on the same chip, including light sources, modulators, and photodetectors3. The use of mature CMOS fabrication processes offers scalable manufacturing and deployment of these devices.

On-chip avalanche photodetectors (APDs) are indispensable components of a fully integrated photonics platform. They provide fast detection speeds, high sensitivity down to single-photon levels, and are compatible with waveguide-based designs. The majority of recent research in this area has been geared toward applications in optical communications networks, focusing on operation at infrared telecommunications wavelengths. These devices have been developed on a variety of material platforms, including III–V semiconductors4, germanium (Ge)5,6,7,8,9,10,11, and Si12,13,14,15,16,17.

However, integrated APDs for visible-light detection have yet to be demonstrated. Such devices, if realized, will greatly benefit numerous application areas. For instance, they can lead to miniaturized devices for biomedical imaging18,19, molecular sensing20, and underwater imaging21. Combined with nanophotonic phased arrays22,23, they can be applied to visible-light communications24,25,26 and bathymetric LIDAR27. As APDs do not require cryogenic environments, unlike integrated superconducting photodetectors, they are advantageous for developing scalable systems for quantum information processing, such as the recently demonstrated 100-mode photonic quantum computer Jiuzhang28. Integrated visible-light APDs will enable the photonic integration of various quantum systems operating at visible wavelengths, such as trapped ions, color centers in diamond, quantum dots, and 2D materials29.

A key difficulty in achieving visible-light operation is optical coupling. For integrated APDs, besides the photodetection efficiency of the active APD structure, the coupling of input light from the photonic circuit (especially on-chip waveguides) to the APD is also critical to the device performance. Despite the ubiquity and high performance of free-space APDs for visible-light detection, the coupling of visible light to integrated photodetector structures remains a significant technical challenge. While conventional integrated APDs rely on an interlayer transition from an input waveguide above or below the APD5,30,31, using the same approach for visible wavelengths would lead to deteriorations in noise and bandwidth performance15,17. This is due to the much longer coupling length required to achieve efficient coupling at these wavelengths, resulting in device sizes much larger than what is required for efficient photon absorption. A larger device size decreases the bandwidth due to RC limitation, and also increases dark noise due to the larger active volume.

To date, the shortest operating wavelength among integrated APDs is 850 nm, as demonstrated in devices developed for short-reach data communications15,17. To the best of our knowledge, there are no reports of visible-light integrated APDs in the literature.

Here, we present the first demonstration of waveguide-coupled APDs for visible-light detection. To overcome the challenge of input light coupling, we adopt an end-fire coupling configuration between the active APD structure and the input waveguide, which are both fabricated on the same device layer. Our devices are fabricated with CMOS-compatible materials, using silicon nitride (Si3N4, hereafter denoted as SiN) on a silicon-on-insulator (SOI) platform. The APD is based on a doped Si rib waveguide, while SiN is chosen for the input waveguide for its low propagation loss at visible wavelengths. In contrast to the more conventional interlayer coupling, our end-fire-coupled devices are a novel addition to SiN photonics platforms. We fabricate devices with different device geometries and doping profiles, and characterize their performance, including dark current, gain, dynamic range, bandwidth, and eye diagrams. We then benchmark our results against other recently reported integrated APDs, and show that our devices are indeed very competitive across multiple performance metrics.

Results

Device design

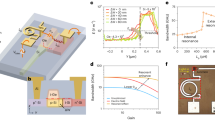

Our device structure is shown in Fig. 1. The primary photodetector structure is a Si rib waveguide of length 16 μm, which has a high absorptivity at visible wavelengths (>96% at 685 nm). Input light is end-fire coupled from an input SiN rectangular waveguide, which allows for low-loss propagation of visible light32,33,34. Both the Si APD and SiN input waveguide have the same width W. Two values of W, 750 and 900 nm, are explored. The height of both the Si APD and SiN waveguide is fixed at 250 nm, and the Si rib height at 125 nm. The structures are fabricated on a SOI substrate on the same device layer, and are cladded with 3 μm of silicon dioxide (SiO2) above and below.

a Schematic of the APD device, consisting of a Si rib waveguide end-fire coupled to an input SiN waveguide. The yellow arrow denotes the propagation direction of input light. The inset shows the simulated optical mode in the Si rib waveguide. b Cross-sectional view of the Si rib waveguide with a lateral doping profile. The junction placed at a distance Δj from the left edge of the waveguide core with a width W. A reverse bias voltage VB is applied via metal contacts deposited on top of heavily doped p++ and n++ regions. c Top view of the Si rib waveguide, showing the lateral and interdigitated doping profiles. a–c are not drawn to scale. d Scanning electron microscope (SEM) image of a fabricated device without the top SiO2 cladding and metal contacts. e, f Fabricated devices imaged under an optical microscope, showing the lensed fiber coupling and Si APD regions, respectively. The red glow is due to the scattering of the 685-nm input light.

To establish electrical connections to the device, metal electrodes are deposited on top of heavily doped p++ and n++ regions at the far ends of the Si slab along the x axis, 3 μm apart.

A careful consideration of the doping profile is required to produce high-performance APDs. Here, we design our APDs to consist of a p–n+ diode in two different doping configurations: lateral and interdigitated (see Fig. 1b, c). Both profiles aim to maximize the spatial overlap between the depletion region on the p-doped side and the optical waveguide mode.

The lateral doping profile features a single continuous junction placed asymmetrically along the length of the APD. The design distance between the junction and the n+ edge of the waveguide Δj is {120, 150} nm for waveguide widths W = {750, 900} nm. We have previously performed simulation studies of this doping profile in Si APDs35,36. Though conceptually simple, this profile requires stringent control of the fabrication process, as a small misalignment of the junction will result in a large mismatch between the optical mode and the depletion region.

The alternative design uses an interdigitated profile, which consists of alternating p and n+ regions, each 1 μm in length. This design is less sensitive to such misalignment errors, but the increased junction lengths could lead to a higher depletion capacitance and hence limit the bandwidth, as is reported for Si modulators37,38.

The n+ (p) doping concentrations of 1 × 1019 (2 × 1017) dopants/cm3 are chosen to ensure that the depletion region covers a large part of the waveguide width in both doping profiles. These doping concentrations are similar to values in other APDs12,39,40.

In most recent reports on waveguide-based APDs for infrared wavelengths, input light is coupled to the detector via a phase-matched interlayer transition5,30,31. However, this is challenging to achieve in a SiN (n = 2.1) to Si (n = 3.8) transition due to the large difference in refractive indices. The increased optical mode confinement at shorter wavelengths means that an efficient interlayer transition would require either long transition lengths, or the narrowing of waveguide dimensions beyond what can be achieved with conventional photolithography32,33,41,42. Therefore, we choose to end-fire couple the input SiN waveguide to the Si rib waveguide in the same layer. From our previous analysis of the optical mode overlap between the waveguide modes, we expect a SiN-Si end-fire coupling loss of ≤1 dB per facet35.

In our fabricated devices, light is coupled into the SiN waveguides via inverse tapers at the edge of the waveguide chip (see Fig. 1e). For both waveguide widths, the inverse tapers are designed to have a taper length of 200 μm and a minimum taper width of 180 nm. The edge-coupled devices are optimized for interfacing with lensed optical fibers; for a focused spot diameter of 2 μm, the expected coupling loss into the SiN waveguide is ~1.5 dB per facet. Detailed characterization of the coupling and propagation losses yield a total insertion loss of 7.1 ± 0.4 dB for our devices (see Supplementary Note 1).

Current–voltage measurements

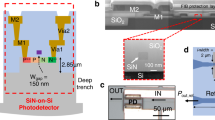

We measure the current–voltage (I–V) characteristics of each device up to the breakdown voltage Vbr, with a series of different input optical powers Popt entering the Si waveguide. The values of Popt are reported after accounting for the insertion loss. Here we consider representative results for a W = 900 nm laterally doped device, as shown in Fig. 2a.

a Current–voltage measurements at different input optical powers Popt. The reverse bias voltage VB is swept till the avalanche breakdown voltage Vbr ≈ 15.5 V, where the dark current Idark reaches 10 μA. Each sweep takes a few seconds; prior to each sweep, the device is reset with the application of a forward bias voltage. b The avalanche gain G at different Popt. The inset is a magnified view of the area marked by the rectangle, showing the curves at larger Popt on a linear scale. Both plots in this figure share the same legend for Popt.

From the I–V data we extract the photocurrent Iph = Idev − Idark, where Idev and Idark are the measured device current and dark current, respectively. We then obtain the avalanche gain G as the ratio of the photocurrent Iph at bias VB to that measured at unity gain point of VB = 2 V, where we consider the quantum efficiency to be nearly maximized, and the effects of avalanche gain to be insignificant:

A discussion of how we determined the unity gain point can be found in Supplementary Note 4.

At VB > 10 V, both Idark and G increase dramatically due to avalanche multiplication. In this regime, the power dependence of the device response becomes obvious, with G decreasing for higher Popt. (see Fig. 2b). This is due to the larger number of multiplied charge carriers causing an increased space charge effect. As a result, the electric field is depressed, leading to saturation of the device current. Thus, while G ~ 10 at VB = 15 V for Popt = −20 dBm, it rises to G > 105 for a low input power of Popt = −71 dBm. Power-dependent characteristics have also been studied in other APDs13,43.

As such, we will separately compare the device performance in low-gain and high-gain regimes.

Performance in the low-gain regime

In the low-gain regime, the APDs can be operated at small bias voltages suited for applications requiring low power consumption. An important example is to monitor optical power levels in integrated photonic circuits, which requires low dark current and wide dynamic range with linear response13,16.

We focus on the primary responsivity Rp = Iph/Popt measured at unity gain, i.e., at VB = 2 V. All device types show linear behavior, with Rp within an overall range of 0.65 ± 0.18 A/W over a dynamic range of >50 dB (see Fig. 3a and Table 1). We expect the actual dynamic range to be even larger since we did not explore higher input powers in detail for all devices, and we had not yet observed the device approaching saturation. Rp is slightly higher for W = 900 nm devices due to the larger absorption volume of a wider waveguide.

a Photocurrent Iph versus input power Popt at the unity gain point of reverse bias VB = 2 V. Straight lines are linear fits, from which we extract the primary responsivity Rp, see Table 1. b Dark current Idark measurements at varying VB. c Avalanche gain G at varying VB with a fixed input power Popt = −63.7 ± 0.7 dBm. b, c share the same legend on the right.

The dark current measurements are shown in Fig. 3b. Idark at VB = 2 V is less than 70 pA for all device types. Laterally doped devices with W = 900 nm exhibit the lowest Idark ~ 1 pA (see also Fig. 2a). We note that in the low bias regime (VB < 10 V), laterally doped devices have about an order of magnitude lower Idark than interdigitated devices. This effect has also been previously reported in other waveguide-based photodetectors13. There are two likely reasons for the higher dark current in interdigitated devices. First, high peak electric field strengths associated with the corners of the interdigitated regions can lead to a higher dark carrier generation rate36 (see Supplementary Note 5 for more details on the electric field profiles). Furthermore, the interdigitated devices have a larger depletion volume where dark carriers can undergo avalanche multiplication, compared to their laterally doped counterparts.

Performance in the high-gain regime

Figure 3c shows the gain G for different device types at a relatively low input power of Popt = −63.7 ± 0.7 dBm, where the devices exhibit high gain. We see that interdigitated devices have a lower breakdown voltage Vbr and a slightly steeper rise in G with respect to VB. These effects can likely be attributed to premature breakdown due to high electric fields at the edges of the interdigitated regions. For both doping profiles, we observe no significant dependence of Vbr on the device width W. This is consistent with our previous simulations for laterally doped devices35.

Applications in integrated photonics typically require low power consumption, thus both Idark and VB should ideally be low as well16. While interdigitated devices achieve similar gain at a lower VB compared to laterally doped devices, Idark tends to be higher. The optimal choice of doping profile in this regime would then require a more in-depth consideration of the operating requirements.

High-speed response and bandwidth

The AC response of the APDs is characterized in the low-gain operation mode, after the device gain has stabilized (see Methods). Figure 4a shows the results of a frequency response measurement for a W = 900 nm laterally doped device. The 3 dB bandwidth, which we define with respect to the device response at 1 GHz, is obtained via a smoothing fit to the data points. Figure 4b, c compares the bandwidth and gain-bandwidth product (GBP) of the different device types. At lower reverse bias VB, the bandwidth generally increases with VB due to a wider depletion region and a lower junction capacitance. However, this effect eventually reaches a limit, beyond which the bandwidth saturates or starts to decrease, due to the device response being limited by avalanche buildup times at large gain16; this occurs at VB ~ 12 V in our devices.

An input power of Popt = −24.5 dBm is used throughout. a Frequency response of a W = 900 nm laterally doped device at various bias voltages VB. The 3 dB bandwidth is obtained from a smoothing fit to the data points (see Methods). b, c The 3 dB bandwidth and gain-bandwidth product (GBP), respectively, for different device types. Both plots share the same legend shown in c. Each data point and error bar in both plots represent the mean and standard deviation, respectively, of several measurements.

We find that the bandwidth is indeed lower in interdigitated devices, as expected from the higher capacitance due to its doping profile. Another potential contributing factor is that a larger proportion of photo-generated charge carriers in interdigitated devices is created in n+-doped regions where the electric field is low, leading to slower carrier diffusion and hence slower device response (see Supplementary Note 5).

A detailed comparison of the best GBP performance for each device is shown in Table 1. The highest observed GBP is 234 ± 25 GHz for the W = 900 nm laterally doped device, at a reverse bias of VB = 20 V. Although its W = 750 nm version has a lower maximum GBP, it also has a much lower dark current, as well as higher 3 dB bandwidths of up to 30 GHz at lower VB. As such, the optimal choice of device parameters might also depend on the specific application and operating conditions.

To demonstrate the performance of our devices in communications systems, we measured eye diagrams of the different device types (see Fig. 5). Lateral devices show open eyes at data rates of up to 56 Gbps at VB = 20 V, where the maximum GBP is observed. We note that these devices can potentially support even higher data rates at lower bias, where the 3 dB bandwidth is higher, but our setup is not capable of generating faster bit patterns. Interdigitated devices show open eyes only at lower data rates, with the W = 750 nm devices performing slightly better (25 Gbps) than W = 900 nm ones (20 Gbps). This is attributed to the narrower devices having a larger gain (G ~ 4 at VB = 16 V, while G ~ 2 for the wider devices), despite having a slightly lower 3 dB bandwidth as seen in Fig. 4b. We note that all devices can be operated at lower data rates with a higher signal-to-noise ratio (SNR); additional eye diagrams showing this can be found in Supplementary Note 3.

Lateral devices show open eyes at data rates of up to 56 Gbps at VB = 20 V, where the maximum GBP is observed. The results for interdigitated devices are obtained at the highest data rate where open eyes could be measured for each device. The signal-to-noise ratio (SNR) is obtained from the sampling oscilloscope.

We note that the high-speed performance of our devices can be adversely affected by factors such as the size of contact pads, which could be further reduced or removed altogether in future large-scale integration with a photonics platform.

Discussion

Table 1 shows the benchmarking of our device performance with other recent reports of integrated APDs. Where possible, we report the performance of each device at the operating conditions where the maximum GBP is observed. For all the devices we benchmark against, we omit the uncertainty values, as only some of the literature reports include this information. We note that in the literature, the primary responsivity and unity gain are reported at varying bias voltages; where not explicitly defined, we have extracted the relevant values at a bias of VB = 1 V, following ref. 16. For our devices, we also note that the values for the dark current Idark in Table 1 are measured in a different regime compared to Fig. 3b, where the reset procedure is used (see Supplementary Note 7).

Our best-performing device is the W = 900 nm laterally doped APD, with a GBP of 234 GHz. Compared to other contemporary devices, this APD shows a strong, balanced performance in the performance metrics of dark current Idark, primary responsivity Rp, gain, and bandwidth. With the exception of ref. 16 which has a very high operating Idark of 88 mA, the 234 GHz GBP of our APD is also comparable to the highest reported values of a few hundred GHz. Yet, our APD also exhibits a much lower Idark of 0.12 μA at the operating bias VB than other high-GBP devices; this would lead to decreased noise and power consumption.

These observations show that our devices are competitive, and are well-suited for visible-light applications requiring high bandwidth and high sensitivity.

In conclusion, we have reported the first fabrication and characterization of waveguide-integrated Si APDs for visible light (685 nm). Our devices feature a small device footprint and are fabricated with a CMOS-compatible process. At a reverse bias of VB = 2 V, a laterally doped APD of 900 nm width exhibited a highest primary responsivity of 0.83 ± 0.05 A/W over a dynamic range of >50 dB, with dark current of ~1 pA. At higher VB, laterally doped devices exhibit superior bandwidth, with a highest 3 dB bandwidth of 30.5 ± 0.2 GHz, and a highest GBP of 234 ± 25 GHz. APDs with an interdigitated doping profile require a lower bias to attain the same DC gain than lateral ones, but have a higher dark current. Our devices perform strongly compared to other state-of-the-art integrated APDs operating at other wavelengths.

The addition of integrated visible-light APDs to the component toolbox of SiN photonics opens up many application possibilities, and greatly expands the versatility of silicon photonics platforms32,33,34. There is potential for further design optimizations, such as alternative doping profiles16 which may enhance the APD gain and reduce the working bias. Future work will also explore the operation of these devices in the Geiger mode for single-photon counting, which will play an important role in the development of integrated quantum photonics platforms, and for interfacing with single-photon sources operating at visible wavelengths.

Methods

Device fabrication

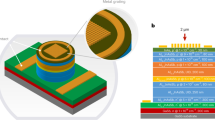

The devices were fabricated at Advanced Micro Foundry and the Institute of Microelectronics, A*STAR. The main fabrication steps of the device are as follows: we start from an 8-inch SOI wafer, with 220 nm Si and 3 μm buried oxide (BOX) layers. An epitaxy of Si (30 nm) tops up the total Si thickness to 250 nm. We then form the Si slab using 248 nm KrF deep-UV lithography and inductively coupled plasma (ICP) etch.

We then deposit a 450-nm thick SiN layer using low-pressure chemical vapor deposition, and reduce it to the same height as the Si slab (250 nm) with chemico-mechanical polishing followed by wet etch. Next, we use lithography and ICP etch with an oxide hard mask to pattern the SiN waveguides and then the Si rib waveguides (125 nm etch into the Si slab) in subsequent steps. The image shown in Fig. 1d was taken after removing the oxide hard mask.

We perform implantation of the p and n+ regions along the Si rib waveguide, followed by the p++ and n++ ohmic contact regions with a subsequent rapid thermal anneal at 1030 °C for 5 s. We then deposit 3 μm of oxide as the top cladding, followed by the opening of contact holes. Finally, we deposit and pattern aluminum to form the contact pads.

Over the course of our measurements, we have tested several tens of devices with different device parameters picked from various locations across an 8" wafer. All tested devices show repeatable results, and we did not observe a single failed device. This indicates that the fabrication is robust and has a high device yield.

Characterization setup

We test the fabricated devices at room temperature using a custom-built light-tight probe station (see Supplementary Note 2 for the setup schematic). We establish electrical connections via 100 × 100 μm contact pads on the chip surface using electrical probes (see Fig. 1f). We use a 685-nm continuous wave diode laser (Thorlabs LP685-SF15) as the optical source. The laser light is coupled to the SiN waveguide using single-mode tapered lensed fibers (OZ Optics TSMJ-3U-633-4/125-1-30-2-9-1, 2 μm spot diameter).

We maintain a horizontal input polarization, which couples to the fundamental TE mode of the SiN waveguide. Although different input polarizations could lead to some variations in the coupling and propagation losses, the APD response itself is not expected to exhibit any significant polarization dependence.

Electro-optic characterization

For I–V measurements, the reverse bias voltage VB is swept from 0 V to the avalanche breakdown voltage Vbr over a few seconds. We define Vbr here as the voltage where the dark current Idark (i.e., without input light) reaches 10 μA; this definition follows other reports of APDs in the literature45,46. We note here that Vbr drifts with time in our devices; as such, to ensure consistent results, it is necessary to reset the device with the application of a forward bias voltage prior to each sweep. More details regarding the drift behavior are discussed in Supplementary Notes 6 and 7.

For bandwidth measurements and eye diagram measurements, the device gain is first stabilized by continuously applying a reverse bias over ~30 min; this is necessary due to the drift behavior. The 685-nm input light is modulated with an RF signal using a 40 GHz electro-optic modulator (EOM, Eospace AZ-AV5-40-PFA-PFA-700). The EOM is operated at 65 °C to mitigate the photorefractive effects caused by high optical input powers. The EOM is maintained at its half transmission point, i.e., the DC bias is adjusted such that the EOM output power is at 50% of its maximum value, before RF modulation is added.

The frequency response is measured with an Agilent E8363C network analyzer, which generates the RF signal for the EOM and measures the APD response. For all devices, we use an input power of Popt = −24.5 dBm. The measured data are corrected for the electro-optic S21 response of the EOM, and smoothed with a Savitzky–Golay filter with a third-order polynomial fit. The 3 dB bandwidth is extracted from the fit function.

For eye diagram measurements, a bit pattern generator (SHF 12104 A together with Anritsu MG3693C) is used to generate non-return-to-zero on-off-keying patterns (NRZ-OOK) with pseudorandom binary sequences (PRBS) of length 27 − 1. These patterns are then amplified (Centellax OA4MVM3) and used to modulate the RF signal driving the EOM. Reference eye diagrams of the EOM output are shown in Supplementary Note 3. The eye diagrams are measured with a sampling oscilloscope (Keysight 86100D with 86116C module). An additional remote sampling head (Keysight N1046A) was used at 56 Gbps to obtain a clearer signal.

References

Thomson, D. et al. Roadmap on silicon photonics. J. Opt. 18, 073003 (2016).

Sibson, P. et al. Integrated silicon photonics for high-speed quantum key distribution. Optica 4, 172–177 (2017).

Stojanović, V. et al. Monolithic silicon-photonic platforms in state-of-the-art CMOS SOI processes. Opt. Express 26, 13106 (2018).

Tossoun, B. et al. Indium arsenide quantum dot waveguide photodiodes heterogeneously integrated on silicon. Optica 6, 1277–1281 (2019).

Liow, T.-Y. et al. Silicon modulators and germanium photodetectors on SOI: Monolithic integration, compatibility, and performance optimization. IEEE J. Sel. Top. Quantum Electron. 16, 307–315 (2010).

Virot, L. et al. Germanium avalanche receiver for low power interconnects. Nat. Commun. 5, 4957 (2014).

Huang, Z. et al. 25 Gbps low-voltage waveguide Si–Ge avalanche photodiode. Optica 3, 793–798 (2016).

Huang, M. et al. 56 GHz waveguide Ge/Si avalanche photodiode. In 2018 Optical Fiber Communications Conference and Exposition (OFC), 1–3 (IEEE, 2018).

Zeng, X. et al. Silicon–germanium avalanche photodiodes with direct control of electric field in charge multiplication region. Optica 6, 772–777 (2019).

Srinivasan, S. A. et al. 27 GHz silicon-contacted waveguide-coupled Ge/Si avalanche photodiode. J. Lightwave Technol. 38, 3044–3050 (2020).

Wang, B. et al. 64 Gb/s low-voltage waveguide SiGe avalanche photodiodes with distributed Bragg reflectors. Photonics Res. 8, 1118–1123 (2020).

Ackert, J. J. et al. 10 Gbps silicon waveguide-integrated infrared avalanche photodiode. Opt. Express 21, 19530–19537 (2013).

Zhu, H. et al. On-chip optical power monitor using periodically interleaved PN junctions integrated on a silicon waveguide. IEEE J. Sel. Top. Quantum Electron. 20, 56–63 (2014).

Souhan, B. et al. Metal-semiconductor-metal ion-implanted Si waveguide photodetectors for C-band operation. Opt. Express 22, 9150–9158 (2014).

Fard, M. M. P., Williams, C., Cowan, G. & Liboiron-Ladouceur, O. High-speed grating-assisted all-silicon photodetectors for 850 nm applications. Opt. Express 25, 5107–5118 (2017).

Zhu, H., Goi, K. & Ogawa, K. All-silicon waveguide photodetection for low-bias power monitoring and 20-km 28-Gb/s NRZ-OOK signal transmission. IEEE J. Sel. Top. Quantum Electron. 24, 1–7 (2018).

Chatterjee, A. et al. High-speed waveguide integrated silicon photodetector on a SiN-SOI platform for short reach datacom. Opt. Lett. 44, 1682–1685 (2019).

Ingargiola, A. et al. 48-spot single-molecule fret setup with periodic acceptor excitation. J. Chem. Phys. 148, 123304 (2018).

Bruschini, C., Homulle, H., Antolovic, I. M., Burri, S. & Charbon, E. Single-photon avalanche diode imagers in biophotonics: review and outlook. Light.: Sci. Appl. 8, 1–28 (2019).

Subramanian, S., Wu, H.-Y., Constant, T., Xavier, J. & Vollmer, F. Label-free optical single-molecule micro-and nanosensors. Adv. Mater. 30, 1801246 (2018).

Maccarone, A., Della Rocca, F. M., McCarthy, A., Henderson, R. & Buller, G. S. Three-dimensional imaging of stationary and moving targets in turbid underwater environments using a single-photon detector array. Opt. Express 27, 28437–28456 (2019).

Poulton, C. V. et al. Large-scale silicon nitride nanophotonic phased arrays at infrared and visible wavelengths. Opt. Lett. 42, 21–24 (2017).

Poulton, C. V. et al. Long-range LiDAR and free-space data communication with high-performance optical phased arrays. IEEE J. Sel. Top. Quantum Electron. 25, 1–8 (2019).

Li, X. et al. Wireless visible light communications employing feed-forward pre-equalization and PAM-4 modulation. J. Lightwave Technol. 34, 2049–2055 (2016).

Zhang, L. et al. A comparison of APD- and SPAD-based receivers for visible light communications. J. Lightwave Technol. 36, 2435–2442 (2018).

Karbalayghareh, M., Miramirkhani, F., Safari, M. & Uysal, M. Vehicular visible light communications with SPAD receivers. In 2019 IEEE Wireless Communications and Networking Conference (WCNC), 1–5 (IEEE, 2019).

Wang, C.-K. & Philpot, W. D. Using airborne bathymetric lidar to detect bottom type variation in shallow waters. Remote Sens. Environ. 106, 123–135 (2007).

Zhong, H.-S. et al. Quantum computational advantage using photons. Science 370, 1460–1463 (2020).

Lee, J. et al. Integrated single photon emitters. AVS Quantum Sci. 2, 031701 (2020).

DeRose, C. T. et al. Ultra compact 45 GHz CMOS compatible germanium waveguide photodiode with low dark current. Opt. Express 19, 24897–24904 (2011).

Fard, M. M. P., Cowan, G. & Liboiron-Ladouceur, O. Responsivity optimization of a high-speed germanium-on-silicon photodetector. Opt. Express 24, 27738–27752 (2016).

Sacher, W. D., Huang, Y., Lo, G.-Q. & Poon, J. K. Multilayer silicon nitride-on-silicon integrated photonic platforms and devices. J. Light. Technol. 33, 901–910 (2015).

Wilmart, Q. et al. A versatile silicon-silicon nitride photonics platform for enhanced functionalities and applications. Appl. Sci. 9, 255 (2019).

Porcel, M. A. et al. Silicon nitride photonic integration for visible light applications. Opt. Laser Technol. 112, 299–306 (2019).

Yanikgonul, S., Leong, V., Ong, J. R., Png, C. E. & Krivitsky, L. 2D monte carlo simulation of a silicon waveguide-based single-photon avalanche diode for visible wavelengths. Opt. Express 26, 15232–15246 (2018).

Yanikgonul, S., Leong, V., Ong, J. R., Png, C. E. & Krivitsky, L. Simulation of silicon waveguide single-photon avalanche detectors for integrated quantum photonics. IEEE J. Sel. Top. Quantum Electron. 26, 1–8 (2019).

Yu, H. et al. Performance tradeoff between lateral and interdigitated doping patterns for high speed carrier-depletion based silicon modulators. Opt. Express 20, 12926–12938 (2012).

Passoni, M., Gerace, D., O’Faolain, L. & Andreani, L. C. Optimizing an interleaved pn junction to reduce energy dissipation in silicon slow-light modulators. Photonics Res. 8, 457–467 (2020).

Lee, M.-J., Sun, P. & Charbon, E. A first single-photon avalanche diode fabricated in standard SOI CMOS technology with a full characterization of the device. Opt. Express 23, 13200–13209 (2015).

Mandai, S., Fishburn, M. W., Maruyama, Y. & Charbon, E. A wide spectral range single-photon avalanche diode fabricated in an advanced 180 nm CMOS technology. Opt. Express 20, 5849–5857 (2012).

Huang, Y., Song, J., Luo, X., Liow, T.-Y. & Lo, G.-Q. CMOS compatible monolithic multi-layer Si3N4-on-SOI platform for low-loss high performance silicon photonics dense integration. Opt. Express 22, 21859–21865 (2014).

Sacher, W. D. et al. Tri-layer silicon nitride-on-silicon photonic platform for ultra-low-loss crossings and interlayer transitions. Opt. Express 25, 30862–30875 (2017).

Lee, M.-J., Rücker, H. & Choi, W.-Y. Optical-power dependence of gain, noise, and bandwidth characteristics for 850-nm CMOS silicon avalanche photodetectors. IEEE J. Sel. Top. Quantum Electron. 20, 211–217 (2014).

Chen, B. et al. Low dark current high gain InAs quantum dot avalanche photodiodes monolithically grown on Si. ACS Photonics 7, 528–533 (2020).

Kang, Y. et al. Monolithic germanium/silicon avalanche photodiodes with 340 GHz gain–bandwidth product. Nat. Photonics 3, 59–63 (2008).

Lee, M.-J. & Choi, W.-Y. A silicon avalanche photodetector fabricated with standard CMOS technology with over 1 THz gain-bandwidth product. Opt. Express 18, 24189–24194 (2010).

Acknowledgements

S.Y. would like to acknowledge the support of the Singapore International Graduate Award (SINGA). The authors thank Mingbin Yu and Shiyang Zhu for their inputs at the initial stage of the project. We acknowledge the support of the National Research Foundation, Singapore (Grant No. NRF-CRP14-2014-04).

Author information

Authors and Affiliations

Contributions

S.Y., S.Y.S., and V.L. designed and performed the experiments. J.R.O. led the device design and simulation work. T.H. contributed to the device fabrication. L.K. conceived the idea. C.E.P. and L.K. supervised the work. All co-authors contributed to writing and proofreading the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Peer review information Nature Communications thanks the anonymous reviewer(s) for their contribution to the peer review of this work. Peer reviewer reports are available.

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Yanikgonul, S., Leong, V., Ong, J.R. et al. Integrated avalanche photodetectors for visible light. Nat Commun 12, 1834 (2021). https://doi.org/10.1038/s41467-021-22046-x

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-021-22046-x

This article is cited by

-

Room-temperature waveguide-coupled silicon single-photon avalanche diodes

npj Nanophotonics (2024)

-

Tuning of silicon nitride micro-cavities by controlled nanolayer deposition

Scientific Reports (2022)

-

Monolithically integrated, broadband, high-efficiency silicon nitride-on-silicon waveguide photodetectors in a visible-light integrated photonics platform

Nature Communications (2022)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.