Abstract

The main advantage of organic transistors with dual gates/bases is that the threshold voltages can be set as a function of the applied second gate/base bias, which is crucial for the application in logic gates and integrated circuits. However, incorporating a dual gate/base structure into an ultra-short channel vertical architecture represents a substantial challenge. Here, we realize a device concept of vertical organic permeable dual-base transistors, where the dual base electrodes can be used to tune the threshold voltages and change the on-currents. The detailed operation mechanisms are investigated by calibrated TCAD simulations. Finally, power-efficient logic circuits, e.g. inverter, NAND/AND computation functions are demonstrated with one single device operating at supply voltages of <2.0 V. We believe that this work offers a compact and technologically simple hardware platform with excellent application potential for vertical-channel organic transistors in complex logic circuits.

Similar content being viewed by others

Introduction

Organic thin-film transistors (OTFTs) can be applied for flat-panel displays1,2,3,4,5, radio frequency identification tags6, and sensor arrays7,8 owing to their excellent properties for realizing flexible, large-area electronic devices9,10,11. Organic-transistor integrated circuits for driving paper-like displays and large-area sensors have been commercially manufactured in the last decades12,13. Despite these advances of organic transistors, one of the major remaining issues on organic-transistor integrated circuits is the control of their threshold voltages (Vth)14,15, i.e., the gate bias at which the transistor switches between the high current accumulation regime and the low current depletion regime. The Vth control is crucial for the design and manufacture of complicated integrated circuits. For logic gates, the Vth determines the trip point, which is the input bias at which the gate inverts the output signal16. For sensing applications, the Vth signifies the bias at which the largest change in current occurs, i.e., the point of the highest sensitivity17,18. Although there are reports in which the Vth of organic transistors is changed by the chemical channel doping of the organic semiconductors replacing the covalently bonded silane layers bearing sulfonic acid groups19 and by modifying the surface of the gate dielectric layers20,21, such approaches are still far from practical use due to the limited reliability of the manufacturing process.

To address the threshold control issue, dual-gate transistors, consisting of a single thin-film transistor with an additional second gate and second dielectric, have been developed7,14,16,18,22. Since the electrostatic potential and the carrier density in the whole film become a function of the second gate bias, the Vth and the off-state current can be easily tuned. Lateral-channel organic dual-gate transistors with a steeper subthreshold slope, improved carrier mobility, and an increased on/off ratio have been demonstrated16,23. The second gate effectively doubles the width of the channel, yielding a higher current. In addition, the opposing gate improves the gate modulation by deeper depletion of the bulk semiconductor, leading to a steeper subthreshold slope. Furthermore, the Vth shift in the transistors depends linearly on the capacitive coupling (ratio between the top and bottom gate capacitance), and the control of Vth by the second gate has been demonstrated in logic and integrated circuits15. Dual-gate digital integrated circuits have been used to drive actuators in a Braille sheet display and to be configured as self-contained logic gates7.

Vertical organic transistors have been intensively investigated in the last years24,25,26,27,28,29. Because of their short effective channel length, they can overcome the limits of conventional OTFTs such as a low on-current density. Organic permeable-base transistors (OPBTs)30, including a central electrode (base) between two outer contacts (emitter and collector) separated by organic layers, have reached a record transition frequency of 40 MHz (ref. 31), exhibiting great potential for switching applications. Given that the lateral-channel organic dual-gate transistors can realize high-performance logic circuits via tuning Vth, thus powerful vertical stacked dual-gate/base organic transistors are highly desirable. However, to the best of our knowledge, there have been no vertical organic dual gate/base transistors reported until now. It is still challenging to precisely construct and control the dual gate/base in the vertical-channel organic transistors.

Here, we report a device concept of vertical organic permeable dual-base transistors (OPDBTs) combining two spatially separated base electrodes to simultaneously enable to change the on-currents and tune the Vth. Accordingly, a high on-current density of 1.54 A cm−2, a large current gain of 9.2 × 105, and a high transmission value of 99.998% are demonstrated in the present OPDBTs. The transmission value can be defined as differential transmission (α = dIC/dIE), the maximum differential transmission is a lower limit for the highest possible direct transmission of charge carriers through the base contact. Meanwhile, logic circuits acting as an inverter, NAND gates and AND gates operation are realized in a single-stacked OPDBT combined with a resistive load.

Results

Device structure and characterization

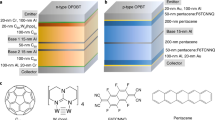

A schematic of an OPDBT is shown in Fig. 1a. The transistor consists of simple sandwich-like architecture, four parallel electrodes (gray and green) are separated by an organic semiconductor (orange). The electron conductive material C60 is used to realize an n-type OPDBT. All base contacts consist of a 15-nm-thick Al layer, which are covered by a thin native oxide layer formed after exposure to air. In this transistor, a 20-nm-thick layer of C60 doped with an efficient n-dopant W2(hpp)4 (n-C60, dopant concentration of 1.0 wt.%) is inserted underneath the emitter electrode in order to reduce the contact resistance and enable an Ohmic-like injection from the metal electrode32,33,34.

a Structure schematic view of an OPDBT measured using common-emitter configuration, and cross-section TEM image of an OPDBT. b SEM image of a 15-nm-thick Al covered on a C60 layer after oxidation in ambient air. c Optical image of the active area in an OPDBT. The active area Aact is defined by the overlap of four electrodes: the emitter (E), base1 (B1), base2 (B2), and collector (C). An insulating layer of SiO is used to confine the active area. The current flow happens in an effective region of 250 µm × 250 µm. d Photograph of our OPDBTs on a glass substrate (edge length: 1 in.), including four active OPDBT pixels. With applied base1-emitter voltages (VB1) and base2-emitter voltages (VB2), electrons can pass through the base and hence reach the collector (a). Except for a minor leakage current into the bases IB1 and IB2 (blue dotted arrows), the emitter current IE (solid blue arrow) can finally arrive at the collector, forming the collector current IC.

Cross-section transmission electron microscopy (TEM) in Fig. 1a shows the stacked layer of an OPDBT device. The top and bottom electrodes are made of Al and Cr, the C60 semiconductor layer with contact doping is interfacing the emitter electrode. The scanning electron microscopy (SEM) image in Fig. 1b depicts the surface morphology of the base electrode on the C60 film after exposure to ambient air. The base electrode is realized by 15 nm of Al evaporated at a rate of 1 Å s−1. A subsequent air exposure for 15 min in the dark supported the formation of a native oxide layer insulating the base. The element distribution (Al, O) in Al electrodes have been analyzed in our previous publication35, the AlOx thickness on the bottom and top sides of the base electrode is about 5 nm, the density of pinholes is up to 50 µm−2, and the diameter of pinholes is about 5 nm. The native oxide layer is sufficiently thick to act as an insulating layer, which can be seen from the following low base leakage and the high transmission values in the transfer curves. To confine the active area of the devices, two insulating layers of thermally evaporated SiO are inserted before depositing the emitter (Fig. 1a). The insulating layers have two crossed stripe-like open windows which define a quadratic active area of 250 µm in length and 250 µm in width (Fig. 1c) in OPDBTs. Figure 1d shows our OPDBT devices on a glass substrate including four transistors.

Before we examine dual-base transistors, the quality of the permeable-base electrodes in an OPDBT is firstly investigated by floating one base. In the following, all electrical measurements refer to the common-emitter configuration (emitter on ground). Figure 2a, c depicts the transfer characteristics of OPDBTs measured by floating base1 and base2, respectively. Both cases show a reliable transistor behavior with on-currents of >1.19 A cm−2 when floating base1, and 2.25 A cm−2 when floating base2 at VC = 2.0 V. Supplementary Table 1 summarizes the performance parameters of OPDBTs when floating one of the bases. Transfer curves of the OPDBTs with floating base1 reveal a transmission value of 99.996%, an on/off current ratio of 6.6 × 103, corresponding to a current gain of 7.7 × 105 at VB1 = VC = 2.0 V. For floating base2, the device shows a transmission value of 99.965%, and an on/off current ratio of 1.6 × 104, corresponding to a current gain of 1.4 × 105 at VB2 = VC = 2.0 V. The current gain (β = IC/IB) and transconductance (gm = dIC/dVB) curves of OPDBTs operating when floating one of the bases are shown in Supplementary Figs. 1 and 2, respectively. High current gain values indicate that the base leakage current is effectively suppressed by the native oxide layer formed on the base electrodes. Furthermore, the capacitance and phase curves versus base voltages at different supplied frequencies (1, 10, and 100 kHz) are shown in Supplementary Fig. 3. The frequency-independent depletion capacitance of the base oxide together with the phase remaining close to −90°, indicates good insulating properties of the base oxide layer36,37.

a–c Transfer characteristics (a) and output characteristics (b) of OPDBTs when floating base1. c, d Transfer characteristics (c) and output characteristics (d) of OPDBTs when floating base2. The insets in a and c show the circuit connections used for the measurements. The base leakage current is negligible compared to the collector current, which underlines the high quality of our permeable-base electrodes.

The output curves are measured at different base voltages of the OPDBTs for floating base1 and base2 electrodes in Fig. 2b, d, respectively. The output curves show promising behavior with a large degree of current control and saturation, even though the curves exhibit a slight nonlinear behavior at low VC due to the contact resistance at the electrode interface38,39,40. The breakdown voltages of OPDBTs are also tested, as shown in Supplementary Fig. 4. The transistor is set into the off-state by applying one base with a voltage of −0.5 V and floating another one. By varying the collector voltage, OPDBTs can withstand a potential drop of 15.0 V. Hence, OPDBTs are sufficiently robust for logic circuit operation and all these results confirm the promising nature for our OPDBTs and thus excellent potential for applications.

The electrical performance of our OPDBTs for simultaneous variation of the base1 and base2 potential is shown in Fig. 3. The transfer characteristics of the OPDBTs are measured in Fig. 3a. The corresponding calculated performance parameters of the transfer curves, e.g. transmission values, on-current density, on–off ratio, the Vth, transconductance (gm.max.), subthreshold swing (SS) and current gain (βmax.), are also summarized in Supplementary Table 2. Figure 3a shows the IC-VB2 curves of the OPDBTs measured with various VB1 from 0 to 2.0 V. When VB1 = 0 V, the collector current stays at the lowest value (~10−7 A) in the range of the base2 sweep bias, indicating the OPDBT stays in its off-state. As VB1 increases from 0 to 0.5 V, the OPDBTs can be turned on. The on-current can reach ~10−5 A at VB2 = 2.0 V, increasing by two orders of magnitude. As the voltage of base1 further increases, the on-state current also increases sharply, the peak of on-current reaches 1.54 A cm−2. Also in terms of on/off-ratio, OPDBTs are not as good as single-base devices because of larger base leakage when the OPDBTs are in the off-state, leading to a lower ON/OFF ratio of 104. Overall, the operation of the OPDBTs is determined not only by the base2 voltage but also by the base1 voltage.

a Transfer curves as a function of VB2 at different VB1 of 0, 0.5, 1.0, 1.5, and 2.0 V, respectively. b Output curves of OPDBTs measured under constant VB1 of 2.0 V and VB2 of 0, 0.5, 1.0, 1.5, and 2.0 V, respectively. c Transfer curves as a function of VB1 at different VB2 of 0, 0.5, 1.0, 1.5, and 2.0 V, respectively. d Output curves of OPDBTs measured under constant VB2 of 2.0 V and VB1 of 0, 0.5, 1.0, 1.5, and 2.0 V, respectively.

Importantly, for the base2 sweeps, the transfer curves shift with the applied base1 bias from 0.5 to 2.0 V, so that the Vth also gradually shift from 0.04 to 0.52 V (the Vth is extracted by the point where the collector current starts to rise exponentially with the base voltage). As shown in the Supplementary Fig. 5, Vth of OPDBTs are dependent on the base1 bias during the base2 sweep. They show slight device-to-device variations measured over 61 devices. By introducing a second base layer, we can reliably control the threshold voltages of vertical organic transistors. Similarly, for base1 sweeps (Fig. 3c), transfer curves also present the on-current change and Vth shifts (from 0.68 to 0.92 V) with the applied base2 bias from 0.5 V to 2.0 V. Thus, the OPDBT allows setting the Vth of the transistor at a desired value by varying the voltages of both base electrodes. Moreover, as can be seen in Supplementary Table 2, the transmission values increase as the bias of the other control base increases from 0 to 2.0 V. Accordingly, we can modulate the charge transmission by tuning the driving voltages of base electrodes, which consequently sets the Vth of the transistors. Comparing to the single-base case when floating the additional one base, the on-current densities of 1.54 and 1.41 A cm−2 of OPDBTs are comparable to 1.19 and 2.25 A cm−2. The maximum transmission values of 99.996% and 99.965% in Fig. 2a, c are close to the maximum values of 99.998% and 99.942% in Fig. 3a, c, respectively. In addition, on/off ratios of 1.6 × 104 and 6.6 × 103 of OPDBTs with one floating base are also in good agreement with the values of 8.0 × 103 and 7.9 × 103 of OPDBTs with two bases biased. Overall, the transfer characteristics show that the extracted parameters in Fig. 3a, c match well with the ones extracted in Fig. 2a, c.

Energy diagrams relating to the four operation modes of the OPDBTs are shown in Supplementary Fig. 6. When base1 is at low potential (Supplementary Fig. 6a), the electrons can not flow to the base1 electrode, representing the off-state of the OPDBTs. The built-in potential can lead to an electric field, which would push the electrons away from the base1 region and thus prevents the current flow through the base1 electrode. When the base1 is at a high potential and the base2 at a low potential, electrons will accumulate at base1 and can not pass through base2, as shown in Supplementary Fig. 6b. Because the base electrodes are wrapped by the native oxide layer, electrons can also not flow into base1, leading to the disturbing base1 leakage41. Hence, the desirable result that electrons can pass through the openings in both base layers and reach the collector only happens when the base1 potential is non-zero and base2 potential larger than that of base1 (Supplementary Fig. 6c).

The base leakage currents for base1 sweeps with fixed base2 voltages from 0 to 2.0 V and for base2 sweep with fixed base1 voltages from 0 to 2.0 V are shown in Supplementary Fig. 7a, b, respectively. Compared to the base leakage in Fig. 2a, at higher base2 voltage, the base2 leakage is lower than that of the floating base1 transistor. Consequently, we obtain a large current gain of 9.6 × 105 at a fixed VB1 of 2.0 V, and equal VC = VB2 = 2.0 V in Fig. 3a, and 7.6 × 104 for the base2 sweeps (Supplementary Fig. 8). However, at lower base2 voltage, the base leakage is larger than that of the floating one base transistor, which does not have an effect on the off-current level although. In Supplementary Fig. 7b, the base1 sweep shows larger base1 leakage than base2 sweep, which is attributed to the oxidation quality of base1 electrode. Furthermore, in Supplementary Fig. 9, the forward and backward sweep curves exhibit a slight hysteresis at base1 biases of 0.5, 1.0, and 1.5 V, respectively. The slight hysteresis effect which happens when VB2 increases from 0.5 to 1.5 V may be attributed to the trapping at the metal/semiconductor interfaces42,43.

Output characteristics of OPDBTs are measured and presented in Fig. 3b, d where a reasonable degree of saturation in the collector current is observed. There is a non-ideal behavior in the output curves at low VC, which is caused by the space-charge-limited current in the organic semiconductor layer44. A bias stress stability analysis of OPDBTs at VC = VB2 = VB1 = 2.0 V is also performed, as shown in Supplementary Fig. 10. It can be seen that the collector, base1, and base2 currents are very stable during the stress measurement, which matches the stability of single-base OPBTs24. In addition, only a slight corresponding Vth shift (~0.1 V) is observed. The device-to-device reproducibility of OPDBTs is characterized in Supplementary Fig. 11 where the maximum on-current (when VC = VB1 = VB2 = 2.0 V) distribution of 61 OPDBT devices is summarized. As indicated by the Gaussian fitting curve, OPDBTs can exhibit well reproducible and predictable device characteristics, which are critical for practical applications and determine the viability of the technology.

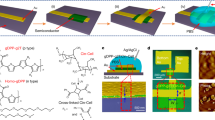

TCAD simulations of OPDBTs

A schematic cross-section of the simulated structure is shown in Fig. 4a along with the device dimensions listed in Supplementary Table 3, based on fabricated OPDBT. The simulated 3D-OPDBT depicts the charge density profile at VB1 = VB2 = VC = 2.0 V (Fig. 4b), where the carrier density through the pinholes can reach the maximum. The device current IC flowing from emitter to collector has to pass the two base layers through the pinholes. To further elucidate the charge transport and device behavior, the measured electrical response has been compared with theoretical models. A Poole-Frenkel mobility model with a square root dependence on the electric field has been used together with the Gaussian density of states (DOS) and quantum tunneling current model. The associated device dimensions and the material parameters employed in the simulations are listed in Supplementary Table 3. The models have been used with their default parameter values except for the calibrated parameters as shown in Supplementary Table 3 (refs. 45,46,47). The simulated DC characteristics (W = 250 μm and L = 250 μm) show a very good agreement between simulations (solid lines) and the experimental measurements (diamonds) (Fig. 4c). Therefore, the calculated device characteristics mimic the measured behavior with high accuracy. Note that the base leakage current is quite small (Fig. 2) and has a negligible impact on the collector current and has been neglected in the simulation. The calibrated simulator has been taken as a reference to further investigate the performance analysis of OPDBTs.

a Schematic cross-section of the simulated OPDBT used for Sentaurus TCAD setup. b 3D-OPDBT structure depicting simulated charge density of the same number of pinholes in base1 and base2 NPin1 = NPin2 = 9, with the emitter being bottom contact and collector the top contact at VB1 = VB2 = VC = 2.0 V. c Transfer characteristics: Collector current IC from experimental data (diamonds) compared with data from TCAD simulation (solid lines), including the negligible measured base2 leakage current IB2 (circles) at VB1 = VC = 2.0 V. d–f Electrostatic potential (d), charge carrier density (e), and current density (f) profiles of OPDBTs at VB1 = VC = 2.0 V and VB2 = 0.5, 1.0, 1.5, and 2.0 V, respectively.

Figure 4d–f displays the electrostatic potential, charge, and current density profiles of the simulated OPDBT in the different operation regions at VB1 = VC = 2.0 V and different base2 voltages VB2 = 0.5, 1.0, 1.5, and 2.0 V. The working principles and the theoretical behavior of the fabricated OPDBTs have been investigated and explored based on the numerical simulation results. In Fig. 4e, when VB1 = VC = 2.0 V, and VB2 = 0.5 V, the semiconductor exhibits a higher density of accumulated charge carriers around base1 injected from the emitter. The charge density is very low around the base2 due to lower applied potential (VB2 = 0.5 V). The carriers accumulated at base1 start to move towards base2 when VB2 increases from 1.0 to 1.5 and to 2.0 V. Therefore, the charge density is increasing around base2, resulting in a control of the collector current IC by modulating the voltage of base2.

It is worth noting that the applied base1 voltage of 2.0 V causes carrier injection from the emitter and leads to the accumulation of charges around the base1. Thus increasing the base2 voltages VB2 = 1.0, 1.5, and 2.0 V, causes carrier migration from base1 through the pinholes toward base2 and the pinholes, allowing more carriers to pass towards the collector. Thus the device total current IC increases (see Fig. 4f). The highest density of charge carriers in the on-state is observed in the openings (pinholes) which have a diameter of a few nanometers.

Logic circuits realized by OPDBTs

By integrating a dual-base transistor with a resistive load, a logic inverter, NAND gate and AND gate circuits are realized experimentally, as illustrated in Fig. 5. The circuit diagram, static and dynamic voltage transfer characteristics (VTCs), and truth table of a resistive load inverter composed of a 400 kΩ external resistance and an OPDBT are shown in Fig. 5a, b for different supply voltages, respectively. In this configuration, only one of the base electrodes of OPDBTs is employed while the other one is kept floating. The VTCs are fine-tuned by changing VCC and the highest voltage gain (dVOUT/dVIn) is 14 as the input voltage varies from 0 to 2.0 V (see Supplementary Fig. 12). Besides the exceptionally small supply voltage, this gain is among the best values reported for unipolar inverters based on organic transistors48,49. The dynamic performance of the inverter is evaluated by applying a square-wave input with a frequency (f) of 1 MHz and an amplitude (VIN) of 2.0 V. It can be seen that the inverter operates well at 1 MHz. Presumably, the capacitance in OPDBTs may limit the dynamic response of the inverter50. Thus, OPDBTs can work well in the MHz region. A good performance and the highest voltage gain of 23 is also obtained for inverters with a depletion load as shown in Supplementary Fig. 13. In this case, the base of a second OPDBT is connected to the output of the inverter while the voltage of base1 is swept again between 0 and 2.0 V (VCC = 2.0 V). Thus, the logic inverters can be simply implemented by using OPDBTs with one base input.

a, c, e Circuit diagrams and static voltage transfer characteristics of an inverter (a), a NAND gate logic circuit (c), and an AND gate logic circuit (e). b, d, f Dynamic characteristics and truth tables of the above corresponding logic circuits. The resistive load inverter is realized by an OPDBT and a 400 kΩ external resistor. GND represents the ground.

In Fig. 5c, d, the NAND gate operation is realized with an OPDBT as a function of base2 input voltage (VIN2) and fixed base1 voltage (VIN1 = 0, 2.0 V), under a supply voltage of 2.0 V. While, Fig. 5e, f show the static and dynamic VTCs of an AND gate when the base1 voltages (VIN1) are fixed at 0 and 2.0 V and the base2 voltage (VIN2) is swept from 0 to 2.0 V under a supply voltage of VCC = 2.0 V. The VTCs in Fig. 5c, e exhibit well high and low states which are the result of the steep transfer curves of the OPDBTs in the logics. From the dynamic characteristics of Fig. 5d, f, NAND gate and AND gate logic circuits can operate well as expected at 1 MHz.

We conclude that logic circuits can be easily realized with our OPDBTs by using two base inputs simultaneously. Unlike conventional unipolar NAND/AND gates consisting of at least two transistors, we implement the NAND/AND gate by using only one vertically stacked dual-base transistors. The independent base control enables the transistor to work at different states by tuning the voltages of two bases (two inputs). OPDBTs with two inputs simplify the fabrication of logic circuits without compromising performance and the reduction of the total number of transistors offers great advantages for integrated circuits. Hence, since OPDBTs represent a compact and technologically simple hardware platform, they offer excellent application perspectives of vertical-channel organic transistors in complex logic circuits. Furthermore, since OPBTs are the organic transistors with the highest operation frequency reported today, further studies and device optimization might enable OPDBTs to be used in high-frequency logic circuits by further study.

Discussion

In summary, a device concept of organic dual-base transistors has been demonstrated. By employing this vertical-channel dual-base structures in organic transistors, we can easily control the Vth which is a main requirement for designing efficient logic circuits. Excellent electrical performance is obtained for this transistor design, e.g., a high on-current density of 1.54 A cm−2, a large current gain of 9.2 × 105, corresponding to a high transmission value of 99.998%, which is almost comparable to single-base OPBTs reported. The numerical TCAD simulation of the structure will help to study structure engineering towards optimizing the performance of OPDBTs. The good agreement between experimental data and numerical simulation confirms the viability of the proposed device design with a channel length in the range of only a few hundreds of nanometers. The functionality enhanced device structure enables to design logic circuits with just one single transistor. To prove the advantage and feasibility of the design, which are investigated as building blocks of the large-scale circuits, we also demonstrate logic gates including inverters, AND gates, and NAND gates which are operating at a voltage as low as 2.0 V.

Methods

Device fabrication

The OPDBTs presented are fabricated in a single chamber UHV-tool and one glass substrate previously cleaned with N-Methylpyrrolidone, distilled water, ethanol, and Ultra Violet Ozone Cleaning System. By using thermal vapor deposition at high vacuum (p < 10−7 mbar), the layer stack (Fig. 1a) is realized by subsequently depositing thin films through laser-cut, stainless steel shadow masks. The deposition system includes a wedge for realizing samples of different layer thicknesses in one run while other layers remain equal. The layer stack, evaporation rates and treatments of the OPDBTs are: Al 100 nm (2 Å s−1)/Cr 10 nm (0.1 Å s−1)/i-C60 100 nm (1 Å s−1)/Al 15 nm (1 Å s−1)/15 min oxidation in ambient air/i-C60 60 nm (1 Å s−1)/Al 15 nm (1 Å s−1)/15 min oxidation in ambient air/i-C60 100 nm (1 Å s−1)/n-C60 20 nm (0.4 Å s−1) co-evaporating C60 with W2 (hpp)4 (purchased from Novaled AG, Dresden) using 1 wt.%/1 x or 2 x (perpendicular to each other) SiO 100 nm with a free stripe of 0.2 mm (1 Å s−1)/Cr 10 nm (0.1 Å s−1)/Al 100 nm (2 Å s−1)/encapsulation under nitrogen atmosphere (<1 ppm O2 and H2O) using UV cured epoxy glue and cavity glasses without UV exposure of the active area/annealing for 2 h at 150 °C on a hotplate in a nitrogen glove-box.

Device characterization

Transistor characteristics are measured by using two Keithley 236 together with a Keithley 2400 SMU in a glovebox. For the impedance spectroscopy, an HP 4284 A LCR-Meter is used. For all the electrical characterizations, the measurement software SweepMe! (sweep-me.net) is used. The optical image is taken by optical microscopy. The scanning electron microscope (SEM) images are captured using a Zeiss Gemini SEM 500. TEM measurements are carried out with a Libra200 (Carl Zeiss Microscopy GmbH, Germany) operated at an acceleration voltage of 200 kV. The lamella for TEM is prepared by lift-out focused ion beam (FIB) technique in NEON40 FIB/SEM (Carl Zeiss Microscopy GmbH, Germany).

TCAD simulation

Synopsys’ Sentaurus TCAD simulator has been used to simulate 3D structures. The device structure is created by a 3D Sentaurus structure editor. It incorporates advanced physical models and robust numeric methods and simulates the electrical behavior of semiconductor devices. The non-local tunneling model is used to include the contributions of the total tunneling current. Gaussian Density-of-States has been used to better represent effective DOS in disordered organic semiconductors. A simple constant carrier generation model is used.

Data availability

The data that support the plots within this paper and other findings of this study are available from the corresponding author upon reasonable request.

References

Zaumseil, J. & Sirringhaus, H. Electron and ambipolar transport in organic field-effect transistors. Chem. Rev. 107, 1296–1323 (2007).

Oh, J. Y. et al. Intrinsically stretchable and healable semiconducting polymer for organic transistors. Nature 539, 411–415 (2016).

Klauk, H. Organic thin-film transistors. Chem. Soc. Rev. 39, 2643–2666 (2010).

Gelinck, G. H. et al. Flexible active-matrix displays and shift registers based on solution-processed organic transistors. Nat. Mater. 3, 106–110 (2004).

Sirringhaus, H. 25th anniversary article: organic field-effect transistors: the path beyond amorphous silicon. Adv. Mater. 26, 1319–1335 (2014).

Khan, H. U. et al. In situ, label-free DNA detection using organic transistor sensors. Adv. Mater. 22, 4452–4456 (2010).

Spijkman, M. J. et al. Dual-gate thin-film transistors, integrated circuits and sensors. Adv. Mater. 23, 3231–3242 (2011).

Zhu, C., Wu, H. C., Nyikayaramba, G., Bao, Z. & Murmann, B. Intrinsically stretchable temperature sensor based on organic thin-film transistors. IEEE Electron Device Lett. 40, 1630–1633 (2019).

Mas-Torrent, M. & Rovira, C. Role of molecular order and solid-state structure in organic field-effect transistors. Chem. Rev. 111, 4833–4856 (2011).

Ortiz, R. P., Facchetti, A. & Marks, T. J. High-k organic, inorganic, and hybrid dielectrics for low-voltage organic field-effect transistors. Chem. Rev. 110, 205–239 (2010).

Ben-Sasson, A. J. et al. Self-assembled metallic nanowire-based vertical organic field-effect transistor. ACS Appl. Mater. Interfaces 7, 2149–2152 (2015).

Myny, K. The development of flexible integrated circuits based on thin-film transistors. Nat. Electron. 1, 30–39 (2018).

Sekitani, T., Zschieschang, U., Klauk, H. & Someya, T. Flexible organic transistors and circuits with extreme bending stability. Nat. Mater. 9, 1015–1022 (2010).

Iba, S. et al. Control of threshold voltage of organic field-effect transistors with double-gate structures. Appl. Phys. Lett. 87, 023509 (2005).

Meijer, E. J. et al. Solution-processed ambipolar organic field-effect transistors and inverters. Nat. Mater. 2, 678–682 (2003).

Chua, L. L., Friend, R. H. & Ho, P. K. H. Organic double-gate field-effect transistors: logic-AND operation. Appl. Phys. Lett. 87, 253512 (2005).

Pfattner, R. et al. Dual-gate organic field-effect transistor for pH sensors with tunable sensitivity. Adv. Electron. Mater. 5, 1800381 (2019).

Liu, N. et al. Enhancing the pH sensitivity by laterally synergic modulation in dual-gate electric-double-layer transistors. Appl. Phys. Lett. 106, 073507 (2015).

Marchl, M. et al. Tuning the threshold voltage in organic thin-film transistors by local channel doping using photoreactive interfacial layers. Adv. Mater. 22, 5361–5365 (2010).

Kobayashi, S. et al. Control of carrier density by self-assembled monolayers in organic field-effect transistors. Nat. Mater. 3, 317–322 (2004).

Halik, M. et al. Low-voltage organic transistors with an amorphous molecular gate dielectric. Nature 431, 963–966 (2004).

Cui, T. & Liang, G. Dual-gate pentacene organic field-effect transistors based on a nanoassembled SiO2 nanoparticle thin film as the gate dielectric layer. Appl. Phys. Lett. 86, 064102 (2005).

Gelinck, G. H. & van Veenendaal, E. Dual-gate organic thin-film transistors. Appl. Phys. Lett. 87, 073508 (2005).

Dollinger, F. et al. Electrically stable organic permeable base transistors for display applications. Adv. Electron. Mater. 5, 1900576 (2019).

Lenz, J., Giudice, F., Geisenhof, F. R., Winterer, F. & Weitz, R. T. Vertical, electrolyte-gated organic transistors show continuous operation in the MA cm−2 regime and artificial synaptic behaviour. Nat. Nanotechnol. 14, 579–586 (2019).

Ben-Sasson, A. J. et al. Patterned electrode vertical field effect transistor fabricated using block copolymer nanotemplates. Appl. Phys. Lett. 95, 213301 (2009).

Guo, E. et al. High-performance static induction transistors based on small-molecule organic semiconductors. Adv. Mater. Technol. 5, 2000361 (2020).

Lim, K. G. et al. Anodization for simplified processing and efficient charge transport in vertical organic field-effect transistors. Adv. Funct. Mater. 30, 2001703 (2020).

Kleemann, H., Krechan, K., Fischer, A. & Leo, K. Review of vertical organic transistors. Adv. Funct. Mater. 30, 1907113 (2020).

Fischer, A., Scholz, R., Leo, K. & Lüssem, B. An all C60 vertical transistor for high frequency and high current density applications. Appl. Phys. Lett. 101, 213303 (2012).

Kheradmand-Boroujeni, B. et al. A pulse-biasing small-signal measurement technique enabling 40 MHz operation of vertical organic transistors. Sci. Rep. 8, 7643 (2018).

Menke, T., Ray, D., Meiss, J., Leo, K. & Riede, M. In-situ conductivity and Seebeck measurements of highly efficient n-dopants in fullerene C60. Appl. Phys. Lett. 100, 093304 (2012).

Lüssem, B. et al. Doped organic transistors. Chem. Rev. 116, 13714–13751 (2016).

Günther, A. A., Sawatzki, M., Formánek, P., Kasemann, D. & Leo, K. Contact doping for vertical organic field-effect transistors. Adv. Funct. Mater. 26, 768–775 (2016).

Dollinger, F. et al. Vertical organic thin-film transistors with an anodized permeable base for very low leakage current. Adv. Mater. 31, 1900917 (2019).

Diesing, D., Hassel, A. W. & Lohrengel, M. M. Aluminum oxide tunnel junctions: Influence of preparation technique, sample geometry and oxide thickness. Thin Solid Films 342, 282–290 (1999).

Wang, M., Liu, Y. & Yang, H. A unified thermodynamic theory for the formation of anodized metal oxide structures. Electrochim. Acta 62, 424–432 (2012).

Zschieschang, U. et al. Roadmap to gigahertz organic transistors. Adv. Funct. Mater. 30, 1903812 (2019).

Borchert, J. W. et al. Small contact resistance and high-frequency operation of flexible low-voltage inverted coplanar organic transistors. Nat. Commun. 10, 1119 (2019).

Lamport, Z. A. et al. A simple and robust approach to reducing contact resistance in organic transistors. Nat. Commun. 9, 5130 (2018).

Kaschura, F. et al. Operation mechanism of high performance organic permeable base transistors with an insulated and perforated base electrode. J. Appl. Phys. 120, 094501 (2016).

Tang, W. et al. Bias stress stability improvement in solution-processed low-voltage organic field-effect transistors using relaxor ferroelectric polymer gate dielectric. IEEE Electron Device Lett. 38, 748–751 (2017).

Subbarao, N. V. V., Gedda, M., Iyer, P. K. & Goswami, D. K. Enhanced environmental stability induced by effective polarization of a polar dielectric layer in a trilayer dielectric system of organic field-effect transistors: a quantitative study. ACS Appl. Mater. Interfaces 7, 1915–1924 (2015).

Klinger, M. P. et al. Organic power electronics: transistor operation in the kA/cm2 Regime. Sci. Rep. 7, 44713 (2017).

Synopsys. Sentaurus device user manual version 2018.06. Synopsys https://www.synopsys.com/silicon/tcad/device-simulation/sentaurus-device.html (2018).

Darbandy, G. et al. Unraveling structure and device operation of organic permeable base transistors. Adv. Electron. Mater. 6, 2000230 (2020).

Zhao, W. & Kahn, A. Charge transfer at n-doped organic-organic heterojunctions. J. Appl. Phys. 105, 123711 (2009).

Khim, D. et al. Control of ambipolar and unipolar transport in organic transistors by selective inkjet-printed chemical doping for high performance complementary circuits. Adv. Funct. Mater. 24, 6252–6261 (2014).

Greenman, M., Yoffis, S. & Tessler, N. Complementary inverter from patterned source electrode vertical organic field effect transistors. Appl. Phys. Lett. 108, 043301 (2016).

Noh, Y. Y., Zhao, N., Caironi, M. & Sirringhaus, H. Downscaling of self-aligned, all-printed polymer thin-film transistors. Nat. Nanotechnol. 2, 784–789 (2007).

Acknowledgements

E.G. and S.X. thank the financial support from China Scholarship Council (No.201706890003 and 201706070125). Z.W. acknowledges the Alexander von Humboldt Foundation. G.D. and A.K. are grateful to the German Research Foundation (DFG) under the grants KL 1042/9-2 (SPP FflexCom). K.L. also gratefully acknowledges the German Research Foundation (DFG) under the grants LE 747/52-2 (SPP FflexCom). We acknowledge Petr Formanek (IPF) for assistance with TEM, and Tseng Hsin for help with dynamic characterization of logic circuits.

Funding

Open Access funding provided by Projekt DEAL.

Author information

Authors and Affiliations

Contributions

Z.W., H.K., and K.L. proposed and supervised the project. E.G. and Z.W. designed the experiment. E.G., Z.W., S.X., and S.W. performed the device characterization. G.D. and A.K. performed the TCAD simulation. A.T. did the SEM analysis and M.G. prepared the FIB lamella for TEM. E.G., Z.W., G.D., H.K., and K.L. analyzed the data and co-wrote the manuscript. All authors discussed the results and commented on the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Peer review information Nature Communications thanks Antonio Facchetti, Mario Caironi and Yong-Young Noh for their contribution to the peer review of this work.

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Guo, E., Wu, Z., Darbandy, G. et al. Vertical organic permeable dual-base transistors for logic circuits. Nat Commun 11, 4725 (2020). https://doi.org/10.1038/s41467-020-18576-5

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-020-18576-5

This article is cited by

-

Vertical organic electrochemical transistors for complementary circuits

Nature (2023)

-

Analytical modeling of organic permeable-base transistors based on geometrical parametrization

Journal of the Korean Physical Society (2023)

-

Organic bipolar transistors

Nature (2022)

-

35 years of organic transistors

Nature Electronics (2021)

-

Efficient and low-voltage vertical organic permeable base light-emitting transistors

Nature Materials (2021)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.