# **ARTICLE**

1

https://doi.org/10.1038/s41467-020-17006-w

**OPFN**

# Lithium-ion electrolytic substrates for sub-1V high-performance transition metal dichalcogenide transistors and amplifiers

Md Hasibul Alam 1, Zifan Xu², Sayema Chowdhury¹, Zhanzhi Jiang², Deepyanti Taneja¹, Sanjay K. Banerjee¹, Keji Lai², Maria Helena Braga 3 & Deji Akinwande 1 □

Electrostatic gating of two-dimensional (2D) materials with ionic liquids (ILs), leading to the accumulation of high surface charge carrier densities, has been often exploited in 2D devices. However, the intrinsic liquid nature of ILs, their sensitivity to humidity, and the stress induced in frozen liquids inhibit ILs from constituting an ideal platform for electrostatic gating. Here we report a lithium-ion solid electrolyte substrate, demonstrating its application in high-performance back-gated n-type MoS<sub>2</sub> and p-type WSe<sub>2</sub> transistors with sub-threshold values approaching the ideal limit of 60 mV/dec and complementary inverter amplifier gain of 34, the highest among comparable amplifiers. Remarkably, these outstanding values were obtained under 1V power supply. Microscopic studies of the transistor channel using microwave impedance microscopy reveal a homogeneous channel formation, indicative of a smooth interface between the TMD and underlying electrolytic substrate. These results establish lithium-ion substrates as a promising alternative to ILs for advanced thin-film devices.

<sup>&</sup>lt;sup>1</sup> Microelectronics Research Center, Department of Electrical and Computer Engineering, The University of Texas, Austin, TX 78758, USA. <sup>2</sup> Department of Physics, The University of Texas, Austin, TX 78712, USA. <sup>3</sup> LAETA, Engineering Physics Department, Engineering Faculty, University of Porto, R. Dr. Roberto Frias s/n, 4200-465 Porto, Portugal. <sup>⊠</sup>email: deji@ece.utexas.edu

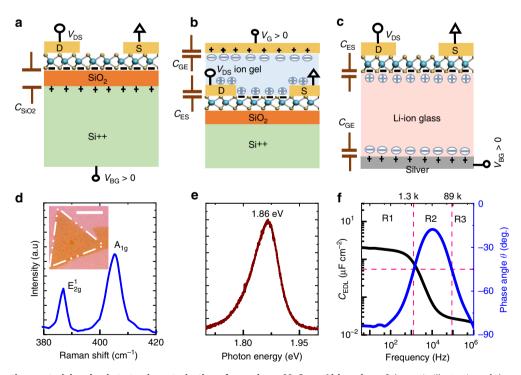

ield-effect transistors (FETs), wherein charge carrier modulation occurs via gating through the formation of electric double layers (EDLs), have been studied for various classes of channel materials and electrolytes over the past few decades 1-6. In addition to realizing electric double layer transistors (EDLTs)<sup>7-9</sup>, EDL has also shown success in modulating superconductor-insulator transition<sup>10,11</sup>, electrically induced ferromagnetism<sup>12</sup>, thermoelectric properties<sup>13,14</sup>, and mimicking biological synaptic functions 15,16. An EDLT comprises of two EDLs, forming at the interfaces of the electrolyte (see Fig. 1a-c): the first one at the metal gate and electrolyte interface (GE interface) and the second one at the interface of electrolyte and semiconductor channel (ES interface). When a positive bias is applied on the gate electrode, positive mobile ions (inorganic solid electrolytes are often cationic conductors) in the electrolyte get repelled from the GE interface, leaving a layer of negatively charged counter-ions at the interface, thereby forming the GE EDL to realign the Fermi levels of gate electrode and electrolyte. In case of ES interface, the positive mobile ions driven away from the GE interface accumulate at the ES interface and in turn induce electrons in the semiconductor channel, hence forming the ES EDL. Analogously, the application of a negative bias on the gate electrode leads to the accumulation of holes in the channel. The distance between the participating opposite charges in an EDL is around 3-8 Å (depending on the ionic concentration, temperature, and dielectric constant)<sup>17,18</sup>, and this subnanometer parallel-plate capacitor gives rise to extremely high capacitances, which can lead to a large carrier density (>1014 cm <sup>-2</sup>) even at very low gate voltages<sup>1</sup>. With conventional dielectrics, accumulation of such high carrier densities would require either extremely high gate voltages or an ultra-thin dielectric. However, the low breakdown field of bulk dielectrics (<10 MV cm<sup>-1</sup> for

SiO<sub>2</sub>) limits the applicability of the former<sup>19</sup>, while the latter makes the transistor highly susceptible to excessive gate leakage currents.

Ionic liquids are the most extensively studied electrolytes for EDLTs for semiconductors till date, where the high mobility and diffusivity of the ions make them suitable for faster operation<sup>1,20</sup>. However, the usage of ionic liquid presents several issues: (i) it is not suitable for surface characterization studies, as it covers the surface of the active region, (ii) it is not viable for precise or practical transistor studies due to its liquid nature, (iii) some ionic liquids are sensitive to humidity, and (iv) channel material can be stressed or damaged once the liquid is frozen at low temperatures. Ion gel, the solid counterpart of ionic liquid, overcomes some of these limitations, but is still susceptible to humidity and lacks a well-defined physical size<sup>9,21</sup>. Recently, various air-stable solidstate electrolytes (SSEs) have been developed, thanks to the extensive progress in battery technology. Li- and Na-ion-based SSEs have already been used to investigate charge carrier tuning in graphene<sup>22,23</sup>. Gate tunable insulator-to-metal transition has also been studied in MoS<sub>2</sub> with a LaF<sub>3</sub>-based solid electrolyte<sup>24</sup>. Recently, electrostatic gating in WSe2 FET with a Li-ion-based solid electrolyte has been reported with limited characterization and analysis, which are essential for understanding the principle of electrolytic gating<sup>25</sup>. As such, a detailed and comprehensive study of transition metal dichalcogenide (TMD) transistors based on solid electrolytes is yet to be conducted.

In this work, we systematically investigate the transport properties of both n-type ( $MoS_2$ ) and p-type ( $WSe_2$ ) TMD backgated transistors fabricated on Li-ion glass substrate, which works both as the gate dielectric and the supporting substrate. Unlike liquid electrolyte gating, we obtain only unipolar conduction for the TMDs (n-type for  $MoS_2$  and p-type for  $WSe_2$ )<sup>1,20</sup>. All the

**Fig. 1 Device operation, material and substrate characterization of monolayer MoS<sub>2</sub> on Li-ion glass.** Schematic illustration of the working principle of **a** solid dielectric-gated FET, **b** ion gel-gated FET and, **c** Li-ion glass-gated FET. The sketches are shown for positive gate bias. The circles and the arrows in the connection schemes represent the bias and ground, respectively. **d** Raman spectrum of the monolayer CVD MoS<sub>2</sub> transferred onto glass substrate. Inset shows dark-field optical micrograph of the transferred CVD MoS<sub>2</sub>. The boundary of the flake is marked with white dash-dotted lines to aid visualization. Scale bar is 10 μm. **e** Photoluminescence spectrum of the same flake. **f** Capacitance/Phase angle vs. frequency of Li-ion glass substrate with Ni (20 nm) as both top and bottom electrode. The frequency spectrum can be divided into three distinct regions: (i) R1 where the EDL is formed, (ii) R2 where ion migration dominates, and (iii) R3 where the bulk Li-ion glass works as a dielectric.

transistors operate under enhancement mode (e-mode) with a small threshold voltage, a desirable feature. For the best devices, a near-ideal sub-threshold swing (SS) of 60 mV/dec (WSe2) and 64 mV/dec (MoS<sub>2</sub>) are observed at room temperature with decent ON/OFF ratios above 10<sup>6</sup>. The output characteristics show a relatively high ON current, Ohmic-like contacts and current saturation. Subsequently, a CMOS inverter amplifier is realized by connecting the n-type and p-type FETs, affording a high voltage gain (~34 V/V), which is the highest gain reported so far with a 1 V power supply. Finally, we investigate the microscopic evolution of local conductivity in the MoS<sub>2</sub> channel by the microwave impedance microscopy (MIM) technique. Within the mesoscopic length scale (~100 nm), the formation of conductive channel is found to be spatially uniform, in contrast to the observation of strong inhomogeneity in MoS2 FETs on conventional SiO2/Si substrate<sup>26</sup>.

#### **Results**

Glass substrate and material characterization. To realize EDLT with TMDs, a double-sided polished glass sheet (150 µm thick, from Ohara Corp.), made of a NASICON type crystal structure containing lithium ions (Li ions) as mobile charge carriers, is used as a solid electrolyte substrate. This air-stable, high-temperature compatible and flat (average roughness ~0.93 nm, Supplementary Fig. 1) substrate is referred to as lithium-ion containing glass or simply Li-ion glass throughout the text. A 3D drawing of a prototypical Li-ion glass EDLT is shown in Supplementary Fig. 2, where silver coating is used as the back-gate metal. As described previously, the two EDLs in a Li-ion glass EDLT are illustrated in Fig. 1c. The major physical difference in EDL formation between an ion gel-gated and Li-ion glass-gated transistor is that the ion gel spreads on the top (Fig. 1b), thereby impeding any surface probe experiments in contrast to the glass, which is underneath the channel. Like EDL formation in ion gel and in Li-ion glass, conventional dielectrics work via electrostatic action, seeking dynamic alignment of the Fermi levels of the materials in electrical contact, leading to uniformly distributed charges of opposite polarity on either side of the dielectric as depicted in Fig. 1a. Although, electrostatic field effect is key to the realization of EDLTs, in some cases, especially at high voltage, Li ions may intercalate into the TMD and cause electrochemical doping<sup>27,28</sup>. However, no electrochemical action or Li intercalation is observed within the extended gate voltage range ( $V_{BG} = -3 \text{ V}$  to +3 V), confirmed from the absence of redox-reactions (characterized by the presence of I vs V 'duck'-shaped curve) for several devices studied in this work.

Initial studies began with single-layer MoS2 that is chemical vapor deposition (CVD)-grown on SiO2/Si and subsequently transferred onto Li-ion glass substrate using the conventional poly (methyl methacrylate) (PMMA) based wet-transfer method (Supplementary Fig. 3). The quality and integrity of the transferred material was verified with Raman and Photoluminescence (PL) spectroscopy as shown in Fig. 1d, e, respectively. Peak separation between  $E_{2g}^{1}$  and  $A_{1g}$  is ~18.5 cm<sup>-1</sup>, which is typical for a single layer<sup>29</sup>. The full width at half maximum (FWHM) for in-plane  $(E_{2g}^1)$  and out of plane  $(A_{1g})$  Raman modes are <3 cm $^{-1}$  and <6 cm $^{-1}$ , respectively, which signifies good crystalline quality of the transferred material<sup>30</sup>. The PL peak of the same flake is located at 1.86 eV and the FWHM is ~80 meV, similar to the reported values in literature for good-quality materials<sup>31</sup>. As the optical contrast of ultra-thin TMD is not easily distinguishable against the underlying substrate in bright field, we used dark-field optical microscopy to identify the monolayers. The capacitance (C<sub>EDL</sub>) of the Li-ion glass is measured with an LCR meter (HIOKI IM 3536) in the frequency range of 4 Hz- 1 MHz with an AC

signal of 100 mV. At 4 Hz, the phase angle reaches close to  $-83^{\circ}$ with a capacitance value of 2 μF cm<sup>-2</sup> (Fig. 1f). By using quasistatic capacitance measurement (Keysight B1500), we obtain capacitance values with an average of ~2.15 μF cm<sup>-2</sup> (Supplementary Fig. 4). In this work, we use 2.10 uF cm<sup>-2</sup>, the average of the quasi-static and low-frequency capacitances, as the value of  $C_{\rm EDL}$ . As the quantum capacitance of TMDs is an order of magnitude higher ( $C_{\rm Q} = \frac{q^2 m^*}{\pi \hbar^2}$ , therefore  $C_{\rm Q,MoS2} \sim 38 \, \mu \rm F \, cm^{-2}$  and  $C_{\rm Q,WSe2} \sim 30 \, \mu \rm F \, cm^{-2})^{32-34}$  than  $C_{\rm EDL}$ , we can neglect the quantum capacitance. We note that this value of  $C_{\rm EDL}$  is close to the value obtained for a fluoride-ion solid electrolyte capacitor<sup>24</sup>. The equivalent oxide thickness (EOT) calculated from the effective capacitance value is ~1.64 nm. Similar to ionic liquid/ gel<sup>35,36</sup>, the frequency (f) spectrum can be divided into three distinct regions: (i) R1 (f < 1.3 kHz) where EDL is formed, (ii) R2 (1.3 kHz < f < 89 kHz) where ion migration dominates, and (iii) R3 (f > 89 kHz) where the bulk Li-ion glass behaves like a conventional dielectric (Supplementary Fig. 5). By utilizing the frequency-dependent impedance data of Fig. 1f, a room temperature Li ion conductivity (factor affecting device speed, see Supplementary Note 1) of ~0.22 mS cm<sup>-1</sup> (Supplementary Fig. 6), as expected for Li-ion glass<sup>37</sup>, has been obtained; the liquid electrolytes, alternatively, have conductivities of the order of 1 mS cm $^{-138}$ .

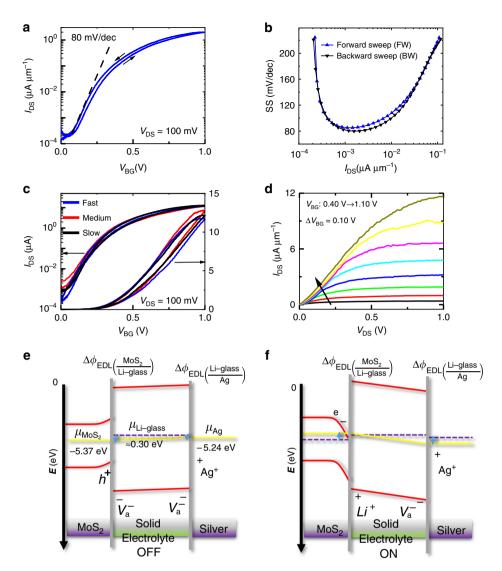

**Transistor properties of n-type MoS<sub>2</sub>**. An FET device ( $L = 1 \mu m$ ,  $W = 5 \,\mu\text{m}$ ) was fabricated on the transferred monolayer CVD MoS<sub>2</sub> by patterning source-drain electrodes using e-beam lithography (EBL) and contact metal (Ni/Au 20 nm/30 nm) evaporation followed by lift-off. The channel is then defined with another e-beam lithography followed by Ar/Cl<sub>2</sub> plasma etching. Both the forward and backward sweeps in the transfer characteristics (Fig. 2a) are in very close agreement with each other resulting in a small hysteresis (< 70 mV). The small hysteresis can be attributed to the dielectric nature of the electrolyte, allowing for fast shortrange displacement ionic currents with back-gate voltage, even at a sweeping speed of 9 mV s<sup>-1</sup>. We note an anticlockwise hysteresis in the gate transfer characteristics, which might be due to the displacement current caused by mobile ions, whereas the clockwise hysteresis in conventional dielectric-gated FET is usually caused by charged trapping at the channel interface<sup>39</sup>. The effect of the high capacitance of the EDLs formed in the solid electrolyte is reflected in the transfer characteristics resulting in a minimum SS of 80 mV/dec, a decent ON/OFF ratio (~104), and a low gate leakage current (Supplementary Fig. 7a). To understand the sub-threshold behavior, local SS values are plotted in Fig. 2b after fitting of the experimental data to facilitate differentiation. The basic equation for SS can be expressed as:

$$SS = \eta \frac{kT}{a} \ln(10) \tag{1}$$

where  $\eta$  is the ideality factor and can be expressed as:

$$\eta = 1 + \frac{C_{\rm IT} + C_{\rm D}}{C_{\rm EDL}} \tag{2}$$

$C_{\rm IT}$ ,  $C_{\rm D}$ , and  $C_{\rm EDL}$  represent the interface trap capacitance, depletion capacitance, and effective electrolyte capacitance, respectively. Owing to the ultra-thin body of few-layer TMDs explored in this work, the channel can be assumed to be fully depleted ( $C_{\rm D}$  ~0 F).

Using the minimum SS value of 80 mV/dec in Eq. (1), a value of  $\eta=1.33$  is obtained for the CVD MoS<sub>2</sub> FET, which leads to a minimum value of  $C_{\rm IT}$  that is equal to 0.70  $\mu \rm F$  cm<sup>-2</sup>. The deviation of  $\eta$  from ideal value ( $\eta=1$ ) in transferred CVD MoS<sub>2</sub> FETs can be attributed to the incorporation of impurities from

**Fig. 2 Electrical transport characteristics of monolayer CVD MoS**<sub>2</sub> **transferred onto Li-ion glass.** a Transfer characteristics of a back-gated CVD MoS<sub>2</sub> FET ( $L=1\,\mu\text{m}$ ,  $W=5\,\mu\text{m}$ ).  $V_{TH}$  is ~0.4 V. **b** SS vs.  $I_{DS}$  for the same FET. SS calculated at points in the sub-threshold region of **a**. SS<sub>min</sub> for forward and backward sweeps are ~85 mV/dec and 80 mV/dec, respectively. **c** Transfer characteristics at different gate sweeping speeds. Sweeping rates for fast, medium, and slow sweeps are 44 mV s<sup>-1</sup>, 9 mV s<sup>-1</sup>, and 1 mV s<sup>-1</sup>, respectively. **d** Output characteristics of the FET at various back-gate voltages. **e**, **f** Schematics illustrating the band diagram for ON/OFF states of MoS<sub>2</sub> FET. Purple dashed and yellow solid lines represent the initial and final states of the chemical potentials, respectively (see Supplementary Fig. 16 for further details).

transfer and fabrication process, as well as intrinsic crystal defects, which collectively lead to a finite interface trap capacitance  $(C_{\rm TT})^{40}$ .

Next, the field-effect mobility can be calculated using:

$$\mu = \frac{\partial I_{\rm DS}}{\partial V_{\rm BG}} \cdot \frac{L}{W} \cdot \frac{1}{C_{\rm EDL} V_{\rm DS}} \tag{3}$$

where  $C_{\rm EDL}$ , L, and W are the effective electrolyte capacitance, channel length, and width, respectively.

Using the maximum slope from the linear  $I_{\rm DS}$ - $V_{\rm BG}$  of Fig. 2a and a  $C_{\rm EDL}$  value of ~2.10  $\mu \rm F$  cm<sup>-2</sup>,  $\mu_{\rm e}$  ~ 18 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for the CVD MoS<sub>2</sub> FET, which is consistent with the mobility values obtained for good-quality back-gated CVD MoS<sub>2</sub> transistors<sup>41,42</sup>.

Next, we investigate the effect of voltage sweep rates on transfer characteristics. Sweep rates of 44 mV s $^{-1}$ , 9 mV s $^{-1}$ , and 1 mV s $^{-1}$  are designated as fast, medium, and slow speeds, respectively. No significant variation is observed in transfer characteristics for these three different speeds, as shown in Fig. 2c, except for the hysteresis voltage,  $\Delta V_{\rm TH}$ , which is 49 mV, 63 mV, and

112 6mV for slow, medium, and fast speeds, respectively (Supplementary Fig. 8). Notably, the  $\Delta V_{TH}$  change between slow and medium sweep rates is negligible and of the order of thermal voltage (~25 mV). As a result, a medium sweep rate  $(9 \text{ mV s}^{-1})$  is used throughout this work, unless otherwise stated. Output characteristics for the same device are shown in Fig. 2d. At small drain voltages, the output characteristics are linear, suggesting an Ohmic-like contact (Supplementary Fig. 7b). At high drain voltages ( $V_{DS} > V_{BG} - V_{TH}$ ), current reaches saturation similar to a well behaved conventional FET<sup>43</sup>. Importantly, we note from the I<sub>D</sub>-V<sub>D</sub> output characteristics of MoS<sub>2</sub> FET, a crossover between channel pinch-off ( $I_{D,sat} \alpha V_{OV}^2$ ) and velocity saturation ( $I_{D,vsat} \alpha V_{OV} v_{sat}$ ) regime (see Supplementary Fig. 9 and Supplementary Note 2 for further clarification), at an overdrive voltage  $(V_{OV} = V_{BG} - V_{TH})$  of ~0.5 V  $(V_{BG} = 0.9 \text{ V},$  $V_{\rm TH} = 0.4 \, \rm V$ ), similar to the observation of a previous report<sup>44</sup>. Similar electrical characteristics (SS ~75 mV/dec, and ON/OFF ratio ~10<sup>5</sup>) are obtained for another CVD MoS<sub>2</sub> FET (Supplementary Fig. 10).

With four-probe technique, the contact resistance ( $R_c$ ) for a single-layer CVD MoS $_2$  FET has been determined to be ~40 k $\Omega$ .µm at  $n > 10^{13}$  cm $^{-2}$  (Supplementary Fig. 11), which is of the same order of magnitude as the reported values (10–100 k $\Omega$ .µm) for a SiO $_2$ /Si back-gated FET with the same contact metal (Ni/1 L CVD MoS $_2$ ) under a similar deposition condition (e-beam, ~10 $^{-6}$  Torr) $^{45}$ . Similar studies with ionic liquid top-gated devices have shown a significant reduction of contact resistance for both electrons and holes $^{1,46,47}$ . This, however, results in ambipolar transport. In this work, a desirable unipolar electron branch has been observed in Li-ion back-gated MoS $_2$  FET (see Supplementary Note 3 for more details), which is favorable for realizing CMOS circuits.

To better understand the electrostatics of the Li-ion glass-based FET, schematics illustrating the chemical potentials of the Li-ion glass and species in contact (Ag and MoS<sub>2</sub>) with it are shown in Fig. 2e, f. In the OFF state, the spontaneous alignment of the Fermi levels (electrochemical potential, not shown here) is made by the diffusion of Li ions in the Li-ion glass into the inner region, leaving negatively charged vacancies (anions) behind (at the surfaces); therefore, the electrolyte may align its Fermi level to the Fermi levels of both materials in electrical contact with its surfaces by locally changing its composition and by the formation of EDLs to finally have  $\bar{\mu}_{Ag} - \bar{\mu}_{MoS_2} = 0 = \mu_{Ag} - \mu_{MoS_2} + e\Delta V_{OCV}$ , where  $\bar{\mu}_{Ag}$ ,  $\bar{\mu}_{MoS_2}$  are electrochemical potentials or Fermi levels,  $\mu_{Ag}$ ,  $\mu_{\mathrm{MoS}_2}$  are the chemical potentials and  $\mathrm{e}\Delta V_{\mathrm{OCV}}$  is the open-circuit voltage in eV. The semiconductor and silver cannot change their chemical potentials without an exchange of electrons or holes, and therefore, in OFF state, the Fermi levels alignment is made by the electrolyte as shown in Fig. 2e. Once the back-gate voltage is applied to the silver end, the chemical potential of the silver decreases, whereas that of the MoS2 increases. MIM measurements in Fig. 5 show that the channel is formed at 0.30 V, which indicates that the Fermi level of the Li-ion glass is surpassed at 0.30 eV and the electrons at the surface of the MoS<sub>2</sub> form an EDL with the Li-ion glass mobile cations to dynamically align their Fermi levels (Fig. 2f).

Further experiments are performed on MoS<sub>2</sub>, which is exfoliated directly onto Li-ion glass, in order to study the transport characteristics of multi-layer MoS<sub>2</sub> FETs. The layers are identified by optical microscopy and confirmed using Raman spectroscopy (Supplementary Fig. 12). Transfer characteristics for mono-, bi-, tri-, and four-layer MoS<sub>2</sub> FETs are shown in Supplementary Fig. 13, with device performance near 60 mV/dec. However, the limited device statistics preclude drawing conclusions on the thickness-dependent effect on the electrolytic substrate. The best field-effect device is obtained for 4 L MoS<sub>2</sub> which demonstrates a SS of ~64 mV/dec, and an ON/OFF ratio above 10<sup>6</sup>, with a field-effect mobility approximately equal to ~20 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> (Supplementary Fig. 13).

**Transistor properties of p-type WSe<sub>2</sub> FET**. To study the effect of EDL on p-type semiconductors, WSe<sub>2</sub>, a p-type 2D material, was exfoliated onto Li-ion glass substrate using commercial bulk WSe<sub>2</sub> (from HQ Graphene). Transport characteristics for 2 L, 4 L, and bulk WSe<sub>2</sub> FETs were investigated. The flakes are identified using optical microscopy and evaluated by Raman and PL characterization, which show good crystalline quality (Supplementary Fig. 14). Sub-threshold swings approaching the ideal limit of  $\sim$ 60 mV/dec were obtained from electrical transfer characteristics of WSe<sub>2</sub> FETs as shown in Fig. 3. A field-effect mobility of  $\sim$ 25 -40 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> has been calculated for the WSe<sub>2</sub> FETs based on the capacitance of the EDL ( $C_{\rm EDL}$ ). Negative threshold voltage and lack of electron transport indicates unipolar conduction with

desirable e-mode transistor operation. The  $I_{\rm OFF}$  is limited by the gate leakage current, similar to MoS<sub>2</sub> FET (Supplementary Fig. 15a–c). A linear relationship at low  $V_{\rm DS}$  (Supplementary Fig. 15d–f) and current saturation at higher  $V_{\rm DS}$  (Fig. 3d–f) mostly caused by channel pinch-off similar to a well-behaved FET<sup>43</sup>, are observed (see Supplementary Fig. 9 and Supplementary Note 2 for further details).

Using the chemical potential of silver ( $-5.24\,\mathrm{eV}$ ) as reference<sup>48</sup>, the Li-ion glass chemical potential,  $\mu$ , is calculated to be  $\mu$  (Li-ion glass)  $\approx -5.07\,\mathrm{eV}$ , which makes  $\mu$  (MoS<sub>2</sub>) =  $-5.37\,\mathrm{eV}$  and  $\mu$ (WSe<sub>2</sub>) =  $-4.73\,\mathrm{eV}$ ,  $\mu$  (MoS<sub>2</sub>) –  $\mu$ (WSe<sub>2</sub>) =  $-0.64\,\mathrm{eV}$  (Supplementary Fig. 16). Experimental results obtained in the literature show,  $\mu$  (MoS<sub>2</sub>) =  $-4.77\pm0.45\,\mathrm{eV}^{48}$  and  $\mu$ (WSe<sub>2</sub>) =  $-4.61\pm0.20\,\mathrm{eV}^{49}$ ,  $\mu$  (MoS<sub>2</sub>) –  $\mu$ (WSe<sub>2</sub>) =  $-0.16\,\mathrm{eV}$ . Surface phenomena such as the direction of the cut, crystalline disorder, polarization, and the number of atomic layers may influence the work functions; on the other hand, the Fermi levels are bulk dependent and, therefore, utilizing work functions are not always the best option to calculate the Fermi levels.

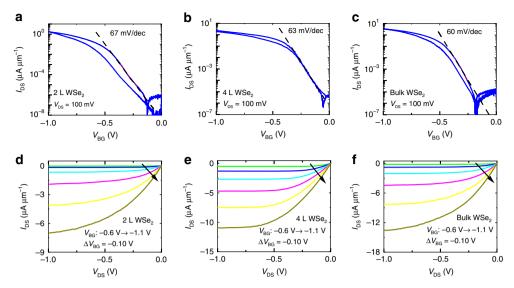

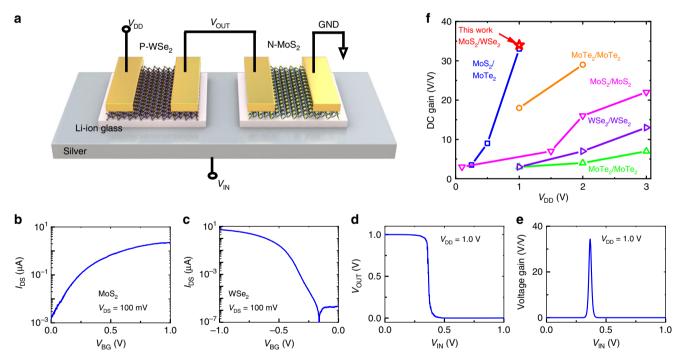

CMOS inverter amplifier. With suitable electrostatic and transport characteristics in both n-type MoS<sub>2</sub> and p-type WSe<sub>2</sub> FETs, a CMOS inverter was realized by connecting these two types of FETs. Figure 4a-c show a schematic diagram of the CMOS inverter with the biasing scheme and the associated transfer characteristics. Voltage transfer characteristics (VTC) of the CMOS inverter are shown in Fig. 4d. The VTC has a full logic swing with a 1 V supply, and offers a steep transition between the two logic states (LOW and HIGH). The mid-point (where  $V_{IN} = V_{OUT}$ ) or the switching threshold voltage  $V_{\rm M} = 0.38 \, \text{V}$  is slightly less than the ideal value of  $V_{\rm DD}/2 = 0.5 \, \text{V}$ . Input/output high/low voltages are found from the VTC curve where the slope = -1. The values are as follows:  $V_{IH} =$ 0.40 V,  $V_{IL} = 0.33 \text{ V}$ ,  $V_{OH} = 0.96 \text{ V}$ , and  $V_{OL} = 0.06 \text{ V}$ . Noise margin high/low are calculated to be  $NM_H (V_{OH} - V_{IH}) = 0.56 V$ and NM<sub>L</sub>  $(V_{IL} - V_{OL}) = 0.27 \text{ V}$  at a supply voltage of  $V_{DD} = 1 \text{ V}$ . By normalizing the values with respect to supply voltage ( $V_{\rm DD}$  = 1 V), we get a noise margin of 56% (NMH) and 27% (NML) from high/low to low/high transitions, respectively. This means that 56% (27%) noise can be tolerated in the process of high (low) to low (high) logic conversion, with the state detectable without error. By using different channel widths, an identical ON-current can be achieved for both n-type and p-type FETs, which may facilitate a symmetric VTC and better noise margins.

Another important figure of merit for CMOS inverters is the DC voltage gain (Fig. 4e), which is calculated from the slope  $(dV_{\rm OUT}/dV_{\rm IN})$ . A maximum gain of ~34 is obtained at an input voltage of  $V_{\rm IN}=0.37$  V. For comparison, the DC gain vs. supply voltage characteristics of other TMD-based realistic CMOS inverters are plotted together in Fig. 4f. We note that the DC gain in this work, obtained at a supply voltage of 1 V, is higher than the other reported values of practical solid-state CMOS inverters. Detailed information (such as supporting substrate, gate dielectric, input voltage range) of other reported works are summarized in Supplementary Table 1. The output current and static DC power (Power =  $V_{\rm DD} \times I_{\rm OUT}$ ) are determined to be ~0.30 µA and ~300 nW, respectively (Supplementary Fig. 17).

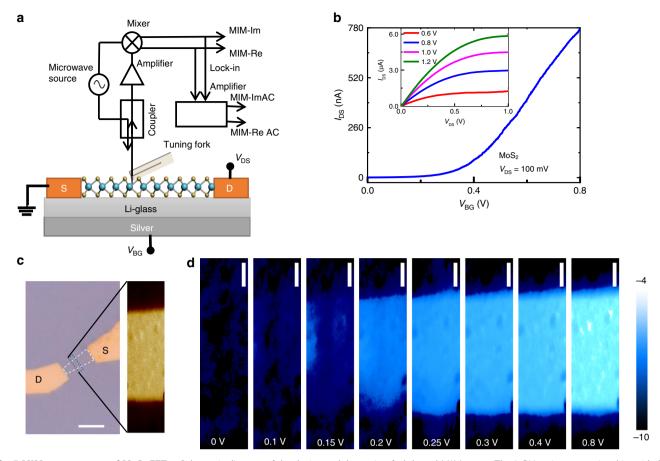

Microwave impedance microscopy (MIM). The transistor-based measurements discussed above provide information on the global transport behavior over the entire channel area. In order to gain more insight on the gate-dependent local conductance, we have performed tuning-fork (TF) based microwave impedance microscopy (MIM)<sup>50</sup>, as schematically illustrated in Fig. 5a. An electrochemically etched tungsten tip (~120 nm) is attached to a

**Fig. 3 Electrical transport characteristics of exfoliated WSe<sub>2</sub> on Li-ion glass.** Transfer characteristics of **a** 2 L, **b** 4 L, and **c** bulk (-14 nm thick) WSe<sub>2</sub> FETs all featuring  $I_{ON}/I_{OFF}$  ~ 10<sup>7</sup> and hysteresis voltage < 120 mV.  $|V_{TH}|$  is ~0.6 V, 0.34 V, and 0.5 V for 2 L, 4 L, and bulk, respectively. Output characteristics of **d** 2 L, **e** 4 L, and **f** bulk WSe<sub>2</sub> FET. For small drain bias, a linear  $I_D$ - $V_D$  is observed indicating Ohmic-like contact. For higher drain bias, current saturation is observed.

**Fig. 4 CMOS inverter based on n-type MoS<sub>2</sub> and p-type WSe<sub>2</sub> FETs. a** Schematic of a CMOS inverter with the drain of p-WSe<sub>2</sub> FET connected to the drain of n-MoS<sub>2</sub> FET. Transfer characteristics of **b** n-type MoS<sub>2</sub> FET.  $V_{TH}$  is ~0.25 V. **c** p-type WSe<sub>2</sub> FET.  $V_{TH}$  is ~-0.50 V. **d** Output vs input voltage characteristics of the inverter. The mid-point voltage  $V_M$  is 0.38 V. Noise margin high (NM<sub>H</sub>) and low (NM<sub>L</sub>) as calculated from the graph are 0.56 V and 0.27 V, respectively. **e** Voltage gain vs. input voltage curve with a maximum gain of ~34 at  $V_{IN}$  = 0.37 V. **f** DC gain vs. supply voltage ( $V_{DD}$ ) of our n-MoS<sub>2</sub>/p-WSe<sub>2</sub> CMOS inverter (red) along with other CMOS inverters from the literature such as n-MoS<sub>2</sub>/p-MoTe<sub>2</sub> (blue)<sup>60</sup>, n-MoTe<sub>2</sub>/ p-MoTe<sub>2</sub> (orange)<sup>61</sup>, n-MoS<sub>2</sub>/p-MoS<sub>2</sub> (magenta)<sup>62</sup>, n-WSe<sub>2</sub>/p-WSe<sub>2</sub> (violet)<sup>63</sup>, and n-MoTe<sub>2</sub>/p-MoTe<sub>2</sub> (green)<sup>64</sup>.

quartz TF to provide the topographic feedback. The 1 GHz microwave signal is delivered to the tip and the reflected signal is detected by the MIM electronics. The distance modulation leads to the periodic change of MIM signals at the TF frequency, which are demodulated by a lock-in amplifier to form AC\_MIM images (Methods and Supplementary Fig. 18). Quantification of the AC MIM signals into local sheet conductance using finite-

element analysis (FEA) can be found in Supplementary Fig. 18. The transfer characteristics of a long-channel MoS<sub>2</sub> FET (L=6 µm) at  $V_{\rm DS}=100$  mV are shown in Fig. 5b. Figure 5d shows the gate-dependent channel conductance maps in a section of the same device (Fig. 5c). The insulator-to-metal transition can be clearly observed from the images. For  $V_{\rm BG}$  below 0.1 V, there is little contrast between the MoS<sub>2</sub> region and the substrate,

Fig. 5 MIM measurement of MoS $_2$  FET. a Schematic diagram of the device and the tuning-fork-based MIM setup. The 1-GHz microwave signal is guided to the tip through an impedance match section, and the reflected signal is detected by the MIM electronics. The carrier density is tuned by the back-gate voltage  $V_{BG}$ . b Transfer characteristics of the MoS $_2$  FET ( $L=6\,\mu m$ ) for  $V_{DS}=100\,m V$ . Inset: Output characteristics for gate voltages from 0.60 V to 1.20 V in steps of 200 mV. c Optical image of the device, where white dashed lines show the channel boundary and the blue dotted line shows the section of the channel where MIM is performed. Inset shows MIM map of the selected channel region. Scale bar is 5  $\mu m$ . d Sheet conductance map in a section of the FET channel at different gate voltages. The color scale represents the common logarithm of sheet conductance in S/ $\Box$ . All scale bars are 500 nm.

indicating that the channel is highly resistive. As  $V_{BG}$  gradually increases to 0.15 V, charge carriers start to appear near the two electrodes, similar to the behavior observed in the ion gel-gated ZnO FET<sup>51</sup>. The conductive regions continue to extend towards the center at  $V_{\rm BG} = 0.20\,\mathrm{V}$ . Finally, as the FET is turned on beyond  $V_{\rm BG} = 0.3 \, \text{V}$ , the MoS<sub>2</sub> channel is uniformly conductive within the spatial resolution of the MIM (~100 nm). Interestingly, the behavior is in sharp contrast to that in a previously reported MoS<sub>2</sub> FET fabricated on conventional SiO<sub>2</sub>/Si substrate and capped by an Al<sub>2</sub>O<sub>3</sub> layer, where strong mesoscopic inhomogeneity was observed<sup>26</sup>. The result may be indicative of a smooth interface between the TMD and electrolytic substrate. The homogeneous channel formation may also be attributed to the suppression of charged impurity scattering effect (usually distributed non-uniformly over the channel) by increased and efficient dielectric screening of the underlying high- $\kappa$  dielectric ( $\kappa$  = 35 for Li-ion glass)<sup>52</sup> substrate<sup>53,54</sup>. Under these circumstances, surface polar phonons of the underlying substrate (Li-ion glass) possibly limit the electron transport (and mean free path) in MoS<sub>2</sub> on Li-ion solid electrolytic substrate<sup>55–57</sup>.

# **Discussion**

In summary, we have presented a lithium-ion based solid electrolyte as a promising platform substrate for transistor device studies. In addition to offering significant advantages over the

ionic liquid gating technique, this substrate can be readily exploited as a back-gate with ideal gate control. As an exemplary nanomaterial, 2D transition metal dichalcogenide semiconductor transistors afford sub-threshold control approaching the ideal limit of 60 mV/dec, high ON/OFF ratios above 10<sup>6</sup>, and relatively high-mobility within the range of 18–40 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>. Remarkably these performance metrics are achieved with a 1 V voltage supply for relatively long (micro-meter) channel lengths, indicating promising prospects for devices with smaller channel dimensions particularly with regards to power supply reduction under field-invariant scaling theory<sup>58</sup>.

In addition, a CMOS inverter amplifier has been realized using n-type  $MoS_2$  and p-type  $WSe_2$ , which individually display the desirable unipolar characteristics. The CMOS amplifier boasts a voltage gain of  $\sim 34$ , which is the highest reported for similar amplifiers with low voltage supply ( $\leq 1$  V). These features of the Li-ion glass, together with the formation of a uniform conduction channel in the TMD upon gating, as evidenced by MIM measurement, make this substrate an attractive choice for advanced thin-film devices and associated device physics.

#### Methods

**Substrate preparation.** Li-ion glass substrate is composed of Li<sub>2</sub>O-Al<sub>2</sub>O<sub>3</sub>-SiO<sub>2</sub>-P<sub>2</sub>O<sub>5</sub>-TiO<sub>2</sub>-GeO<sub>2</sub> and came in the form of polished plates named as Lithium-Ion Conductive Glass Ceramic (LICGC<sup>TM</sup>) AG-01 from Ohara Corporation. We purchased polished square plates (25.4 mm by 25.4 mm and 150  $\mu$ m thick) of

AG-01 LICGC and patterned alignment marks on them using photolithography and a subsequent e-beam metal (20 nm/30 nm Ni/Au) evaporation step. The samples with alignment marks are then cut into standard sizes (6.3 mm  $\times$  6.3 mm) with a dicing saw (ADT 7100 Series System) using a resin blade (CA-010-325-100-H). Back-side of the electrolyte substrate is silver-coated with a Q-tip for back-gate measurement.

**2D materials preparation.** Bulk MoS $_2$  (natural) and WSe $_2$  (synthetic) crystals are purchased from commercial vendors 2D Semiconductors and HQ Graphene, respectively. MoS $_2$  and WSe $_2$  is exfoliated from bulk crystal using ultra tape (Ultra Tape 1310) and transferred onto Li-ion glass substrates from ultra-tape using polydimethylsiloxane (PDMS) stamp. A subsequent annealing step is done in high vacuum ( $10^{-7}$  Torr) at 340 °C for ~8 h to remove tape/organic residues introduced during exfoliation/transfer process. CVD MoS $_2$  is grown on a pre-cleaned highly doped SiO $_2$ /Si substrate in a single zone furnace at 850 °C using molybdenum oxide (MoO $_3$ ) and sulfur (S) powders as precursors. The CVD grown material is then transferred on Li-ion glass substrate by poly (methyl methacrylate) (PMMA)-assisted wet transfer using sodium hydroxide (NaOH) of 6 M (6 mols of NaOH in 1 liter of H $_2$ O) as etchant.

**2D materials characterization**. Optical characterization was done using Olympus microscope (BX53M) and their proprietary software Stream Essentials. Since the contrast of the flakes on glass is not good in bright field, we use darkfield mode to see and capture the images. Raman and PL spectroscopy are performed in a Renishaw in Via micro-Raman system. Excitation wavelength of 532 nm with an incident beam power of ~1 mW and exposure time of 10 s is used for Raman. A 3000 l/mm grating is used for < 5 cm<sup>-1</sup> resolution. For photoluminescence spectroscopy, excitation wavelength of 532 nm with incident power <1 mW and exposure time ~10 s is used. A 1200 l/mm grating is used for PL measurements.

**Device fabrication**. EBL is used to pattern contact and measurement pads. E-beam metal evaporation is then used to deposit contact metals. Ni/Au (20 nm/30 nm) and Pd/Au (5 nm/5 nm) are used for MoS<sub>2</sub> and WSe<sub>2</sub> contact metals, respectively. The channel region is defined with an EBL and a subsequent plasma etching step. CF<sub>4</sub>/O<sub>2</sub> and Cl<sub>2</sub>/O<sub>2</sub> plasmas are used to etch WSe<sub>2</sub> and MoS<sub>2</sub>, respectively. In some of the EBLs, we employ an e-spacer charge compensation layer, but no significant difference is observed with/without this step.

**Electrical characterization**. All electrical DC measurements are performed on a Cascade Microtech Summit 11000B-AP probe station using an Agilent 4156C parameter analyzer in ambient at room temperature. Quasi-static CV is measured with Keysight B1500 parameter analyzer. For frequency-dependent capacitance, HIOKI 3536 LCR meter has been used.

**TF-MIM.** A tuning-fork-based MIM is employed to map the local conductivity. The technique utilizes a tuning-fork-based AFM combined with a 1 GHz microwave signal guided by an electrochemically etched tungsten tip (25 µm diameter wire), which is glued on the tuning fork (resonant frequency ~38 kHz). A Zurich HF2LI lock-in amplifier is used to drive the tuning-fork tip at its resonant frequency in the driving amplitude modulation (DAM) mode<sup>50</sup>. The topography feedback is realized by a commercial AFM system (Park XE-70). The AC\_MIM signals are demodulated by an SR830 lock-in amplifier and then acquired by the Park system. During the measurements, source and drain electrodes are grounded, DC offset of the tip is set to zero through a bias-tee, and the back-gate voltage is applied using Keithley 2400 Source Measurement Unit (SMU) to modulate the carrier density.

**Finite-element analysis (FEA).** Finite-element analysis is performed by COMSOL 4.4 to verify the response of AC\_MIM signals on MoS<sub>2</sub> devices. Since the lateral dimensions of flakes are much larger than the MIM tip diameter (120 nm), the 2D axisymmetric model can be used here. The device and substrate are characterized by the following parameters: MoS<sub>2</sub>: t (thickness) = 3 nm, w (width) = 6 μm and  $\varepsilon$  (dielectric constant) =  $7^{59}$ . Li-ion glass substrate: t = 150 μm,  $\varepsilon = 35^{52}$ . We followed the standard procedure described in ref.  $^{50}$  to convert the demodulated tip—sample admittance to the AC\_MIM output based on the calibration of our electronics. The tip taps at 0.5 nm height above the sample surface with an amplitude of 14 nm and a frequency of 38 kHz.

# **Data availability**

The data that support the plots within this paper and other findings of this study are available from corresponding author upon reasonable request.

Received: 25 January 2020; Accepted: 4 June 2020; Published online: 24 June 2020

#### References

- Perera, M. M. et al. Improved carrier mobility in few-layer MoS2 field-effect transistors with ionic-liquid gating. ACS Nano 7, 4449-4458 (2013).

- Uesugi, E., Goto, H., Eguchi, R., Fujiwara, A. & Kubozono, Y. Electric doublelayer capacitance between an ionic liquid and few-layer graphene. Sci. Rep. 3, 1595 (2013).

- Yuan, H. et al. High-density carrier accumulation in ZnO field-effect transistors gated by electric double layers of ionic liquids. *Adv. Funct. Mater.* 19, 1046–1053 (2009).

- Yang, D. et al. Hysteresis-suppressed high-efficiency flexible perovskite solar cells using solid-state ionic-liquids for effective electron transport. *Adv. Mater.* 28, 5206–5213 (2016).

- Rosenblatt, S. et al. High performance electrolyte gated carbon nanotube transistors. Nano Lett. 2, 869–872 (2002).

- Na, S. R. et al. Clean graphene interfaces by selective dry transfer for large area silicon integration. *Nanoscale* 8, 7523–7533 (2016).

- Kim, B. J. et al. High-performance flexible graphene field effect transistors with ion gel gate dielectrics. *Nano Lett.* 10, 3464–3466 (2010).

- Yuan, H. et al. Liquid-gated ambipolar transport in ultrathin films of a topological insulator Bi2Te3. Nano Lett. 11, 2601–2605 (2011).

- Pu, J. et al. Highly flexible MoS2 thin-film transistors with ion gel dielectrics. Nano Lett. 12, 4013–4017 (2012).

- Steinberg, H., Gardner, D. R., Lee, Y. S. & Jarillo-Herrero, P. Surface state transport and ambipolar electric field effect in Bi2Se3 nanodevices. *Nano Lett.* 10, 5032–5036 (2010).

- Goldman, A. M. Superconductor-insulator transitions in the two-dimensional limit. Phys. E: Low.-dimensional Syst. Nanostruct. 18, 1–6 (2003).

- Yamada, Y. et al. Electrically induced ferromagnetism at room temperature in cobalt-doped titanium dioxide. Science 332, 1065–1067 (2011).

- Takayanagi, R., Fujii, T. & Asamitsu, A. Control of thermoelectric properties of ZnO using electric double-layer transistor structure. *Jpn. J. Appl. Phys.* 53, 111101 (2014).

- Yanagi, K. et al. Tuning of the thermoelectric properties of one-dimensional material networks by electric double layer techniques using ionic liquids. *Nano Lett.* 14, 6437–6442 (2014).

- Zhu, L. Q., Wan, C. J., Guo, L. Q., Shi, Y. & Wan, Q. Artificial synapse network on inorganic proton conductor for neuromorphic systems. *Nat. Commun.* 5, 3158 (2014).

- Shi, J., Ha, S. D., Zhou, Y., Schoofs, F. & Ramanathan, S. A correlated nickelate synaptic transistor. *Nat. Commun.* 4, 2676 (2013).

- Translated, T. by M. J. B. 'The theory of electrolytes. I. Freezing point depression and related phenomena' (Debye & Hückel, 1923). 47 (1923).

- 18. Bardeen, J. Surface states and rectification at a metal semi-conductor contact. *Phys. Rev.* **71**, 717–727 (1947).

- Klein, N. & Gafni, H. The maximum dielectric strength of thin silicon oxide films. IEEE Trans. Electron Devices ED-13, 281–289 (1966).

- Prakash, A. & Appenzeller, J. Bandgap extraction and device analysis of ionic liquid gated WSe2 Schottky barrier transistors. ACS Nano 11, 1626–1632 (2017).

- Allain, A. & Kis, A. Electron and hole mobilities in single-layer WSe2. ACS Nano 8, 7180–7185 (2014).

- Zhao, J. et al. Lithium-ion-based solid electrolyte tuning of the carrier density in graphene. Sci. Rep. 6, 34816 (2016).

- Zhao, J. et al. Application of sodium-ion-based solid electrolyte in electrostatic tuning of carrier density in graphene. Sci. Rep. 7, 1–6 (2017).

- Wu, C.-L. et al. Gate-induced metal-insulator transition in MoS2 by solid superionic conductor LaF3. Nano Lett. 18, 2387–2392 (2018).

- Philippi, M., Gutiérrez-Lezama, I., Ubrig, N. & Morpurgo, A. F. Lithium-ion conducting glass ceramics for electrostatic gating. *Appl. Phys. Lett.* 113, 033502 (2018)

- Wu, D. et al. Uncovering edge states and electrical inhomogeneity in MoS<sub>2</sub> field-effect transistors. Proc. Natl Acad. Sci. USA 113, 8583–8588 (2016).

- Shi, W. et al. Superconductivity series in transition metal dichalcogenides by ionic gating. Sci. Rep. 5, 12534 (2015).

- Xiong, F. et al. Li intercalation in MoS2: in situ observation of its dynamics and tuning optical and electrical properties. Nano Lett. 15, 6777–6784 (2015).

- Li, H. et al. From bulk to monolayer MoS2: evolution of Raman scattering. Adv. Funct. Mater. 22, 1385–1390 (2012).

- Laskar, M. R. et al. Large area single crystal (0001) oriented MoS2. Appl. Phys. Lett. 102, 252108 (2013).

- Splendiani, A. et al. Emerging photoluminescence in monolayer MoS2. Nano Lett. 10, 1271–1275 (2010).

- Ma, N. & Jena, D. Carrier statistics and quantum capacitance effects on mobility extraction in two-dimensional crystal semiconductor field-effect transistors. 2D Mater. 2, 015003 (2015).

- Liu, L., Kumar, S. B., Ouyang, Y. & Guo, J. Performance limits of monolayer transition metal dichalcogenide transistors. *IEEE Trans. Electron Devices* 58, 3042–3047 (2011).

- Fallahazad, B. et al. Shubnikov-de Haas oscillations of high-mobility holes in monolayer and bilayer WSe 2: Landau level degeneracy, effective mass, and negative compressibility. *Phys. Rev. Lett.* 116, 086601 (2016).

- Pudasaini, P. R. et al. Ionic liquid versus SiO2 gated a-IGZO thin film transistors: a direct comparison. ECS J. Solid State Sci. Technol. 4, Q105 (2015).

- Choi, Y. et al. Proton-conductor-gated MoS2 transistors with room temperature electron mobility of >100 cm2 V-1 s-1. Chem. Mater. 30, 4527-4535 (2018).

- Nakajima, K., Katoh, T., Inda, Y. & Hoffman, B. Lithium ion conductive glass ceramics: properties and application in lithium metal batteries. in Symposium on Energy Storage Beyond Lithium Ion: Materials Perspective (2010).

- Sato, T., Masuda, G. & Takagi, K. Electrochemical properties of novel ionic liquids for electric double layer capacitor applications. *Electrochim. Acta* 49, 3603–3611 (2004).

- Ma, X. et al. A sputtered silicon oxide electrolyte for high-performance thinfilm transistors. Sci. Rep. 7, 1–6 (2017).

- Zhao, P. et al. Evaluation of border traps and interface traps in HfO2/ MoS2gate stacks by capacitance-voltage analysis. 2D Mater. 5, 031002 (2018).

- Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Singlelayer MoS<sub>2</sub> transistors. *Nat. Nanotechnol.* 6, 147–150 (2011).

- Novoselov, K. S. et al. Two-dimensional atomic crystals. PNAS 102, 10451–10453 (2005).

- Streetman, B. G. & Banerjee, S. Solid state electronic devices (Pearson Prentice Hall. 2006).

- Smithe, K. K. H., English, C. D., Suryavanshi, S. V. & Pop, E. High-field transport and velocity saturation in synthetic monolayer MoS2. *Nano Lett.* 18, 4516–4522 (2018).

- English, C. D., Shine, G., Dorgan, V. E., Saraswat, K. C. & Pop, E. Improved contacts to MoS2 transistors by ultra-high vacuum metal deposition. *Nano Lett.* 16, 3824–3830 (2016).

- 46. Zhang, Y., Ye, J., Matsuhashi, Y. & Iwasa, Y. Ambipolar MoS2 thin flake transistors. *Nano Lett.* 12, 1136–1140 (2012).

- Braga, D., Gutiérrez Lezama, I., Berger, H. & Morpurgo, A. F. Quantitative determination of the band gap of WS2 with ambipolar ionic liquid-gated transistors. *Nano Lett.* 12, 5218–5223 (2012).

- Trasatti, S. The absolute electrode potential: an explanatory note (Recommendations 1986). Pure Appl. Chem. 58, 955–966 (1986).

- Schlaf, R., Lang, O., Pettenkofer, C. & Jaegermann, W. Band lineup of layered semiconductor heterointerfaces prepared by van der Waals epitaxy: charge transfer correction term for the electron affinity rule. J. Appl. Phys. 85, 2732–2753 (1999).

- Wu, X. et al. Quantitative measurements of nanoscale permittivity and conductivity using tuning-fork-based microwave impedance microscopy. Rev. Sci. Instrum. 89, 043704 (2018).

- Ren, Y. et al. Direct imaging of nanoscale conductance evolution in ion-gelgated oxide transistors. Nano Lett. 15, 4730–4736 (2015).

- Kumar, A. et al. Nanometer-scale mapping of irreversible electrochemical nucleation processes on solid Li-ion electrolytes. Sci. Rep. 3, 1621 (2013).

- Giannazzo, F., Sonde, S., Nigro, R. L., Rimini, E. & Raineri, V. Mapping the density of scattering centers limiting the electron mean free path in graphene. *Nano Lett.* 11, 4612–4618 (2011).

- Sonde, S. et al. Role of graphene/substrate interface on the local transport properties of the two-dimensional electron gas. Appl. Phys. Lett. 97, 132101 (2010).

- Zeng, L. et al. Remote phonon and impurity screening effect of substrate and gate dielectric on electron dynamics in single layer MoS2. *Appl. Phys. Lett.* 103, 113505 (2013).

- Ma, N. & Jena, D. Charge scattering and mobility in atomically thin semiconductors. *Phys. Rev. X* 4, 011043 (2014).

- Yu, Z. et al. Realization of room-temperature phonon-limited carrier transport in monolayer MoS2 by dielectric and carrier screening. *Adv. Mater.* 28, 547–552 (2016).

- Baccarani, G., Wordeman, M. R. & Dennard, R. H. Generalized scaling theory and its application to a ¼ micrometer MOSFET design. *IEEE Trans. Electron Devices* 31, 452–462 (1984).

- Kumar, A. & Ahluwalia, P. K. Tunable dielectric response of transition metals dichalcogenides MX2 (M=Mo, W; X=S, Se, Te): Effect of quantum confinement. *Phys. B: Condens. Matter* 407, 4627–4634 (2012).

- Pezeshki, A. et al. Static and dynamic performance of complementary inverters based on nanosheet α-MoTe2 p-channel and MoS2 n-channel transistors. ACS Nano 10, 1118–1125 (2016).

- Lim, J. Y. et al. Homogeneous 2D MoTe2 p-n Junctions and CMOS Inverters formed by atomic-layer-deposition-induced doping. Adv. Mater. 29, 1701798 (2017)

- Lan, Y.-W. et al. Scalable fabrication of a complementary logic inverter based on MoS2 fin-shaped field effect transistors. *Nanoscale Horiz.* 4, 683–688 (2019).

- Tosun, M. et al. High-gain inverters based on WSe2 complementary fieldeffect transistors. ACS Nano 8, 4948–4953 (2014).

- Larentis, S. et al. Reconfigurable complementary monolayer MoTe2 fieldeffect transistors for integrated circuits. ACS Nano 11, 4832–4839 (2017).

# **Acknowledgements**

D.A. acknowledges the PECASE award from the Army Research Office (ARO) and the NSF MRSEC Center (DMR-1720595). The MIM experiment was supported by the U.S. Department of Energy (DOE), Office of Science, Basic Energy Sciences, under the award no. DE-SC0019025. Z.X. acknowledges partial support by the Welch Foundation award F-1814. This work was performed in part at the University of Texas Microelectronics Research Center, a member of the National Nanotechnology Coordinated Infrastructure (NNCI), which is supported by the National Science Foundation (ECCS-1542159). We are thankful to Andrew Murchison from John Goodenough group of UT Austin for the collaborative discussion regarding solid-state electrolyte. We also thank Jo Wozniak of Texas Advanced Computing Center (TACC) for her help with the three-dimensional renderings.

# **Author contributions**

M.H.A. and D.A. conceived and designed this experiment. M.H.A conducted material exfoliation, sample preparation, characterization, device fabrication and electrical transport measurements. S.C. provided CVD  $\rm MoS_2$  samples and performed material transfer under the guidance of S.K.B. Z.X. and Z.J. conducted the MIM measurement and the FEA simulation under the supervision of K.L. M.H.B. contributed in preparation of energy band diagrams to explain transistor turn ON/OFF. D.T. contributed in data analysis and manuscript preparation. Electrical data were analyzed by M.H.A. and D.A. All authors contributed to the article based on the draft written by M.H.A. and D.A. All authors have given approval to the final version of the manuscript.

# **Competing interests**

The authors declare no competing interests.

# **Additional information**

**Supplementary information** is available for this paper at https://doi.org/10.1038/s41467-020-17006-w.

Correspondence and requests for materials should be addressed to D.A.

Peer review information Nature Communications thanks Filippo Gianazzo and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Reprints and permission information is available at http://www.nature.com/reprints

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Open Access** This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing,

adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

© The Author(s) 2020, corrected publication 2021