Abstract

In atomically-thin two-dimensional (2D) semiconductors, the nonuniformity in current flow due to its edge states may alter and even dictate the charge transport properties of the entire device. However, the influence of the edge states on electrical transport in 2D materials has not been sufficiently explored to date. Here, we systematically quantify the edge state contribution to electrical transport in monolayer MoS2/WSe2 field-effect transistors, revealing that the charge transport at low temperature is dominated by the edge conduction with the nonlinear behavior. The metallic edge states are revealed by scanning probe microscopy, scanning Kelvin probe force microscopy and first-principle calculations. Further analyses demonstrate that the edge-state dominated nonlinear transport shows a universal power-law scaling relationship with both temperature and bias voltage, which can be well explained by the 1D Luttinger liquid theory. These findings demonstrate the Luttinger liquid behavior in 2D materials and offer important insights into designing 2D electronics.

Similar content being viewed by others

Introduction

Surface states of bulk three-dimensional (3D) semiconductors are critical factors to be considered in designing and fabricating electronic devices, as they can result in trapping and scattering, or acting as recombination centers for free carriers1. An in-depth understanding of the surface states has enabled scientists and engineers to optimize the performance of integrated circuits during the past a few decades. Analogous to the surface states of bulk crystals, the edge termination and reconstruction in monolayer two-dimensional (2D) materials (e.g., molybdenum disulfide (MoS2) and graphene) can lead to the edge electronic states2,3,4,5, which bring remarkable properties to these 2D materials and spark considerable intriguing applications6. The metallic electronic states at the edges of 2D transition metal dichalcogenides (TMD) have been predicted by first-principle calculations7,8. However, experimental investigations of the 2D edge states are scarce and little is known about the effects as well as the fundamental mechanism of edge states on electronic transport and performance of monolayer TMD-based electronic devices, which are critical for evaluating their performance for future nanoelectronic devices.

Herein we report a systematic investigation of the edge contribution to charge transport property in monolayer MoS2 and WSe2 field-effect transistors (FETs) and discovery of edge state-induced nonlinear electronic transport and underlying mechanism. Scanning probe microscopy (SPM), scanning Kelvin probe force microscopy (SKPFM) and first-principle calculations reveal that the edge states dominate the charge transport and are responsible for this nonlinear behavior. We further find that the current–voltage characteristics of charge transport show a power-law scaling with respect to both temperature and bias voltage, which is consistent with Luttinger liquid theory and suggests that the edge states are one-dimensional metal with dominant electron–electron interactions.

Results

Edge states conductance quantization

To quantitatively evaluate the contribution of charge transport along the edge states at different gate voltages and temperatures, we fabricated multi-probe device from one monolayer MoS2 flake (Fig. 1a). This method can eliminate contributions from contact9,10,11. Figure 1b shows the output characteristic curves (\(I_{{{\mathrm{D}}_{1}} {{\mathrm{S}}_{1}}}\)–\(V_{12}\,{\mathrm{curves}}\)) of the monolayer MoS2 device under gate voltage from 60 to 10 V. The transfer curves (\(I_{{{\mathrm{D}}_{1}}{{\mathrm{S}}_{1}}}\)–\(V_{{\mathrm{G}}}\)) at \(V_{{{\mathrm{D}}_{1}}{{\mathrm{S}}_{1}}} = 1\; {\mathrm{V}}\) bias with different temperature are shown in Fig. 1c. More importantly, the conductance contributed from the edge and bulk can be separated by measuring and quantifying the characteristic curves (I–V) curves of the devices with different edge lengths and bulk area (Supplemental Note 1). Notably, experimental data from 6.3 to 350 K reveal the edge conductance ratios (Gedge/Gtotal) increase with decreasing temperature, and become larger than 50% at the temperature below 50 K (Fig. 1d), which indicates that the edge transport plays a dominant role over the bulk transport at low temperature. This higher contribution from edge transport at lower temperature may be attributed to the carrier freezing out in bulk semiconducting MoS2. With increasing gate voltage, more carriers populate at the semiconducting MoS2 bulk channel, leading to higher bulk conductance and lower edge/total conductance ratio.

a Optical image of monolayer MoS2 FETs with inner probes (V1–V6) to sense voltage drop within channel. The scale bar is 10 μm. b Output (\(I_{{{\mathrm{D}}_{1}}{\mathrm{S}}_{1}}\)–\(V_{{\mathrm{12}}}\)) curves of monolayer MoS2 FET at 250 K with gate voltages 10 to 60 V. c The transfer curves (\(I_{{{\mathrm{D}}_{1}}{{\mathrm{S}}_{1}}}\)–\(V_{{\mathrm{G}}}\)) in MoS2 device measured at \(V_{{{\mathrm{D}}_{1}}{{\mathrm{S}}_{1}}}=1\) V from 250 to 6.3 K. d The ratios of edge conductance (Gedge) to total conductance (Gtotal) over large temperature and gate voltage range based on the experimental measurements as described in the Supplementary Note 1.

To demonstrate the generality of one-dimensional transport behavior in TMDs FETs, a typical p-type monolayer tungsten diselenide (WSe2) FET with hole carrier is studied. It demonstrates a similar trend, with the edge conductance dominating the overall transport at lower temperature regime (Supplementary Fig. 2). Thus, these systematical studies reveal the monolayer TMD exhibit a similar edge state characteristic regardless of the carrier type.

STM/S measurements

To further probe the nature of edge charge transport, high-resolution scanning probe techniques are used to reveal both the topography and the electronic property of monolayer MoS2 crystal (Fig. 2a). The atomic-thin MoS2 is grown on highly oriented pyrolytic graphite (HOPG) conductive substrate, which is good for scanning tunneling microscope and spectroscopy (STM/S) measurements. Figure 2b shows a typical AFM image of a triangular MoS2 island. The apparent height of the island is illustrated by the yellow profile line and is nearly 0.70 nm, which is consistent with the single-layer MoS2 feature. It is notable that no obvious height differences can be found between the edge and the bulk of monolayer MoS2 crystal in the AFM image, which is similar to former studies of MoS2 on HOPG surface12,13. Figure 2c shows a typical STM image of one triangular MoS2 island obtained in an ultrahigh-vacuum chamber (base pressure < 3 × 10−10 mbar). The profile line of the MoS2 island shows its apparent height of 0.72 nm, also confirming the monolayer nature of the MoS2 sample. Notably, the STM image reveals a brim with high brightness contrast around the edge of MoS2 island (Fig. 2c), in contrast to AFM image with a largely flat edge topography.

a Schematic of SPM measurements process. b AFM image of a typical triangular MoS2 island, showing no obvious brightness differences between the edge and the bulk. The profile line (yellow) shows an apparent height of 0.70 nm of the triangular flake, corresponding to the single-layer MoS2 feature. c STM image of the triangular MoS2 island grown alongside the edge of the substrate terrace, clearly showing the electronic edge states with a brim of very high conductance along the island edges. The profile line (yellow) also shows a significant protrusion at the edge. The apparent height of the triangular flake is 0.72 nm, consistent with the AFM measurement in b. d Zoomed-in STM image of the area indicated by the dark-blue rectangle in c. Inset: atomic resolution image of MoS2 obtained from the area indicated by the white dashed square. e dI/dV spectra taken across the MoS2 edge from HOPG to the bulk MoS2. The color of the curves is consisted with the color of marked positions in the inset. The tunneling spectrum (#3) acquired at the MoS2 edge shows clearly electronic states (marked by pink) around Fermi level, revealing its metallic feature. STM scanning parameters: U = −1.0 V, I = 100 pA (c) and (d) U = −1.0 V, I = 800 pA for the inset.

To get more detailed structural and electronic information about the edges, we zoomed in the area near the edge of the MoS2 island marked by the blue dashed-line in Fig. 2c and obtained the image as shown in Fig. 2d. This image presents a significant brightness contrast along the MoS2 edge, which is recognized as the metallic edge states by a brim of very high conductance extending all the way along the edges, consistent with previous STM/STS measurements8,12,14. An atomic resolution STM image reveals the clean MoS2 surface with clear atomic structure (as shown in the inset of Fig. 2d). These AFM and STM studies together demonstrate the atomically clean topography of the MoS2 island and that the bright brim observed in the STM images is not due to different edge topography, but due to the conductive electronic states at the edge. Metallic edge states of the MoS2 crystal are also confirmed by scanning tunneling spectroscopy (STS) measurements. Figure 2e shows dI/dV spectra taken across the MoS2 edge from HOPG to the bulk MoS2 (data-recording positions are shown in the inset). The tunneling spectrum (#3) acquired at the MoS2 edge shows clearly electronic states (marked by pink) around Fermi level compared to spectra (#4 & #5) from MoS2 bulk, revealing its metallic feature. The edge states stay consistently at different positions along the MoS2 edge, as shown in the Supplementary Fig. 3. Differently, the spectra from HOPG (#1 & #2) show metallic and the spectra from MoS2 (#4 & #5) show semiconductor feature.

First-principle calculations

To further understand the origin of the edge electronic states, we conducted first-principle calculations based on density-functional-theory (DFT) and non-equilibrium Green’s function (NEGF) by using the Perdew-Burke-Ernzerhof (PBE) version of the generalized gradient approximation (GGA)15,16,17. The calculated band structure indicates that the appearance of additional bands within bandgap (highlighted by the red line in the Supplementary Fig. 4a), which can be attributed to broken crystalline symmetry and the presence of dangling bonds at the edge. These additional bands cross the Fermi level and are localized at the edge atoms as shown by the calculated charge density distribution (Supplementary Fig. 4b), confirming that the metallic states are associated with the edge atoms.

We have further simulated the electrical charge transport behavior across the triangular MoS2 domain by Atomistix Tool Kit (ATK)15,16,17 by constructing a two-probe model comprised of a semiconducting MoS2 sample with source and drain ends, in which the source and drain are defined by the highly doped (1014 e/cm2) n-type MoS2 to reduce extra calculation time (Fig. 3a). Such MoS2-based device is simulated under different bias voltage conditions (Fig. 3b, c). Figure 3b shows the transmission eigenstates spread along the edge of monolayer MoS2, indicating that the electrons tend to transport along the edge of MoS2 (VG = 0 V and VDS = 0 V). As the back-gate voltage increases from 0 to 0.5 V, a few more transmission eigenstates start to locate at the bulk of MoS2 channel (Fig. 3c), indicating that more electrons populate at the MoS2 bulk, leading to an increase in bulk conductance and a decrease of the relative contribution from the edge conductance contribution, which is consistent with the experimental observations as shown in Fig. 1.

a Schematic of monolayer MoS2 FET (Uppermost row); side view (Middle row) and top view (Lowest row) of monolayer MoS2. The isosurface plots for transmission eigenstates of the MoS2 channel at the k-point Γ(0,0) and the energy of 0.05 eV under the conditions of VDS = 0 V and VG = 0 V in b, and VDS = 0 V and VG = 0.5 V in c. The evolving of the carriers in bulk is revealed as highlighted by the red ellipse in b and c, although only a small gate voltage (0.5 V) is applied in simulation.

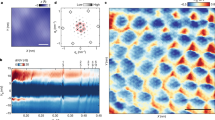

SKPFM measurement

To directly reveal the role of the 1D metallic edge state in monolayer MoS2 device, we have further mapped the local electrical potential of the monolayer MoS2 FET through the SKPFM measurements18,19, which is an AFM-based method that can record the local potential variation of a sample surface, relative to a metallic probe. Using this method, local potential variation, resulting from edge states, and bulk states in the MoS2 sample, can be directly imaged under working conditions, and thus the electronic transport path can be visualized. The optical image of the channel region of the monolayer MoS2 device is depicted in Fig. 4a. The AFM image depicted from the white rectangle in Fig. 4a is shown in Fig. 4b, and its corresponding SKPFM potential mapping is shown in Fig. 4c with working conditions (VDS = 8 V, and VG = 0 V). Two typical potential curves (as depicted by Line A and Line B across the edge and the bulk of the triangle-shaped MoS2 sample, respectively) are shown in Fig. 4d. We can see that significant potential contrast is exhibited along the edge (depicted by Line A) and the bulk (Line B). The potential difference along the edge, about 524 mV, is much larger than the one along bulk, 137 mV (in equal perpendicular distance). These results clearly reveal that the electrons prone to flow along the edge of the MoS2 sample under the given bias voltage. Furthermore, the potential cross the MoS2 channel is simulated by the finite-element method as shown in Fig. 4e, which is consistent with the experimental observation in Fig. 4c. Additionally, this observations agree well with the previous results measured by microwave impedance microscopy, which shows that the electron charge is prone to flow at the edge by measuring the local conductance contrast in edge and bulk material20.

a Optical image of the MoS2 FET device. The white rectangle region is the one selected for SKPFM measurement. b AFM image of the selected region. c Local potential map of the selected region at the bias voltage of VDS = 8 V and VG = 0 V. Line scans of the potential both across the edge (Line A) and the bulk (Line B) of the MoS2 flake. d Voltage potential comparison between the experimental data and simulation data. The experimental potential difference at the edge is 524 mV (Circles in Line A) and the difference at the bulk is 137 mV (Circles in Line B). The significant high potential at the edge indicates that charges flow at edge under the given bias voltage. The simulation results (Solid line) match well with the experimental results. e Simulated potential mapping of MoS2 channel based on the finite-element method, consistent with the experimental mapping in c.

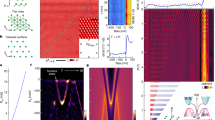

Nonlinear charge transport

We have further investigated the temperature dependence of the electrical transport in monolayer MoS2 FET device. Figure 5a shows the output (IDS–V12) curves of the device at large temperature range from 350 to 6.3 K, where the channel current decreases rapidly with decreasing temperature T. The linear (IDS–V12) characteristics are retained above 50 K, indicating an ohmic behavior. With further decreasing temperature, the characteristic (IDS–V12) curves show clear nonlinear behavior above the threshold voltages (VT)11,21 (Fig. 5b). A possible mechanism of the nonlinear power-law dependence of (IDS–V12) characteristics is due to Coulomb blockade (CB)22. However, this theory requires isolated conductive dots separated by a very thin tunneling layer, and the threshold voltage VT extracted in CB model depends linearly on temperature23. These two characteristics of CB model do not agree with our results, suggesting a new mechanism of nonlinear transport in our devices (Supplementary Note 6).

a Typical (IDS–V12) curves measured under VG = 60 V, varying temperature from 350 to 6.3 K. b The (IDS–V12) below 50 K are shown, illustrating clear nonlinear charge transport behavior in monolayer MoS2 FET. c Power law relation of conductance G with temperature (G ∼ Tα) at low bias V12 = 0.1 V, obtaining a fitting exponent α = 2.2 from the red fitting curve. d Power law relation of the current with the voltage \(I_{{\mathrm{DS}}}\sim V_{{\mathrm{12}}}^\beta\) at low temperature T = 6.3 K, having a fitting exponent β = 2.2. e The output transport data and the corresponding curve plotted by IDS/T1+α against qV12/kBT under the gate voltage of VG = 60 V. The nonlinear (IDS–V12) data scale well onto a universal curve over the temperature range from 50 to 6.3 K. The fitting curve indicates nonlinear Luttinger liquid behavior. f (IDS–V12) data scale onto the universal curve replotted as IDS/T1+α versus qV12/kBT under other gate biases: VG = 30, 40, and 50 V, respectively.

Another theory used for nonlinear charge transport is Luttinger liquid model. In this theory, the tunneling amplitude of an electron into an Luttinger liquid vanishes as a power–law relation with the energy of the tunneling electron24,25,26, which results in a power–law dependence of conductance G with temperature by formula of (G = I/V ∝ Tα) and the current with voltage by I ∝ Vβ, in which α and β are the tunneling exponents. In our experimental measurements, the conductance G = IDS/V12 shows a power–law behavior with temperature as G ∼ Tα and gives α = 2.2 at V12 = 0.1 V (Fig. 5c). Similarly, at T = 6.3 K, \(I_{{\mathrm{DS}}}\sim V_{{\mathrm{12}}}^\beta\) shown in Fig. 5d gives β = 2.2. These experimental results are consistent with the prerequisite of the Luttinger liquid model.

An additional feature of the Luttinger liquid theory is that the universal scaling curve of all (IDS–V12) curves at different temperatures can be obtained when IDS/T1+α is plotted against eV12/kBT as27,28,29:

where Γ(x) is the gamma function, kB is the Boltzmann constant, α and β are the tunneling exponents as mentioned above, I0 is the fitting parameter and γ−1 denotes the number of tunnel barriers in the transport path of Luttinger liquid.

According to Eq. (1), we plot IDS/T1+α against eV12/kBT with our experimental results (Fig. 5e). The nonlinear (IDS–V12) curves scale well onto a universal curve over the temperature range from 50 to 6.3 K. This universal curve can be well fitted to Eq. (1), as shown by the solid curve in Fig. 5e, in which the parameters’ values α = 2.2, β = 2.2, and γ−1 = 200 are derived. These extracted data of α and β are identical to the values from the power exponent of G ∼ Tα (Fig. 5c) and \(I_{{\mathrm{DS}}}\sim V_{{\mathrm{12}}}^\beta\) (Fig. 5d) as obtained above, respectively. In Fig. 5f, the output data are plotted as IDS/T1+α versus eV12/kBT at various gate voltages (VG = 30, 40, 50 V). Under these different gate voltages, the fitting parameter γ−1 based on Eq. (1), is again constantly equal to 200. The parameter γ−1 is related to the number of tunneling barriers that lies along the transport path and determines a crossover from ohmic behavior to a power–law dependence in the Luttinger liquid27,28. Here, the constant γ−1 under different gate voltages further validates Luttinger liquid model. For monolayer WSe2 FET, the output curves (IDS–V12) at low temperature shows nonlinear behavior and the corresponding curves can also be scaled to a universal curve with α = 2.15, β = 3, and γ−1 = 100 according to the Eq. (1) (Supplementary Fig. 7).

This parameter γ−1 is further discussed in the Supplementary Note 8 with MoS2 devices with various channel lengths (edge lengths). In these devices, the cross points obtained by fitting output data as IDS/T1+α against eV12/kBT are analyzed, and the linear dependence of γ−1 as function of edge length is again obtained in the Supplementary Fig. 8, in which the number of tunneling barriers (γ−1) increase with increasing channel lengths (edge lengths).

Based on the different α values extracted from MoS2 and WSe2 FETs, the electron interaction (MoS2) or hole interaction (WSe2) parameter g can be calculated to be 0.102 and 0.106, respectively (Supplementary Note 9). The parameters from all MoS2 and WSe2 devices are summarized in the Supplementary Table 1 in Supplemental Information. All these data here demonstrates that the Luttinger parameter g ≪ 1, as often discussed in Luttinger model24,27,30,31, indicating a strong repulsive electron–electron (hole–hole) interactions along 1D charge transport path in edge-state-dominated MoS2 (WSe2) crystals and this result can be generally extended to all semiconducting TMD crystals.

Discussion

These findings raise interesting implications on the generality of the Luttinger model for monolayer MoS2 transistors. We note that the agreement with Eq. (1) has been advocated as a clear evidence for tunneling into 1D or quasi-1D Luttinger metallic liquid28,32. Thus, direct evidences from both theory and experiment suggest that the edge states are 1D Luttinger metallic liquid in 2D crystal, which accounts for the nonlinear charge transport at low temperature. A schematic process of edge-state-dominated 1D metallic charge transport in atomic-thin 2D crystal based on Luttinger metallic liquid model is shown in Supplementary Fig. 11. It shows that electron transport from one Luttinger liquid to another Luttinger liquid through 1D tunneling across possible defects or impurities along the metallic edges in monolayer 2D materials, as shown above by the example of MoS2 and WSe2 crystals.

We have witnessed two previous works demonstrate that the metallic mirror-twin boundaries in MoS233 and MoSe234 show Luttinger liquid behavior, in which the Luttinger parameter g are extracted to be 0.2 for MoS233 and 0.5 for MoSe234, respectively. These values are much larger than the parameter g (0.11–0.08) extracted in our experiment from edge states, indicating that stronger electron–electron (or hole–hole) repulsive interactions along the edges of TMD than the one at the grain boundaries of TMD. In addition, a more general argument could be strengthened that metallic line defects (edges or grain boundaries) in 2D semiconductors all show Luttinger liquid behavior and are ideal 1D systems.

Peierls transition have seen observed in many 1D metallic systems34,35, in which the periodic lattice deformation, resulting in a sudden increase in sample resistance at the transition temperature. However, all the temperature-dependency resistances of our samples in the Supplementary Fig. 12 do not show sudden transition as same as ref. 34. Thus, we believed that the likelihood of Peierls transition is low in metallic edge states of TMD (Supplementary Note 12).

Together, our studies demonstrate for the first time that the metallic edge states in 2D TMD materials behave like a 1D Luttinger liquid, which leads to nonlinear transport at smaller gate voltages and lower temperature. Importantly, the electron–electron interaction in such edge states in 2D-TMDs may be fine-tuned by the gate voltage, offering a new interesting model system for probing 1D quantum transport. The apparent metallic edge states may also lead to important implications for 2D-TMD devices. For example, the metallic edge state may suggest a possible pathway to engineer proper edge contact to 2D materials and facilitate charge injection36.

Methods

Device fabrication

Monolayer MoS2 (WSe2) were exfoliated from the commercial MoS2 (WSe2) crystals (SPI Supplies) by scotch-tape method on Si/SiO2 substrate. The source and drain contacts (10 nm Ti/70 nm Au for MoS2 and 70 nm Au for WSe2) were formed through electron beam lithography (EBL), electron beam evaporation and then a lift-off process. The rectangular MoS2 (WSe2) channels were patterned by a second EBL step and subsequently etched using O2/SF6 plasma.

Electrical measurements

Electrical measurements were conducted by using a Keithley 4200 semiconductor parameter analyzer and a Lakeshore probe station. The multi-probe measurement configuration is also shown in Fig. 1a. The inner probes (V1 ~ V6) sense voltage drop. A bias voltage (VDS) is applied across the drain and source terminals. The channel current IDS is measured at the end of drain terminal. The voltage drops measured in this configuration can exclude any effects related to contacts, in which the voltage difference (V12 = V1 − V2, V34 = V3 − V4, and V56 = V5 − V6) is measured between the two inner terminals.

Scanning tunneling microscopy/spectroscopy

STM measurements were carried out in a custom-built multi-chamber ultra-high vacuum system. The base pressure was better than 3 × 10−10 mbar. Before STM measurements, the sample was annealed at 150 °C for over 12 h to remove possible adsorbates. A chemically etched tungsten tip was used for imaging. The STM images were recorded in constant current mode with tunneling current in the range 100–800 pA. The MoS2/HOPG sample was transferred to the ultrahigh-vacuum chamber and degassed at 150 °C for 12 h before STM analyses. STS measurements were using standard lock-in techniques with a voltage modulation of 10 mV and frequency of 973 Hz. Before real-sample STS measurements, the tip was calibrated on a clean Au(111).

First-principles calculations

The electronic transport properties are carried out by ATK toolkit on the basis of density-functional theory in combination with the nonequilibrium Green’s function15,16. The local density approximation (LDA) and the wave function is expanded by the single-zeta plus polarization basis for all atoms17. The MoS2 device configuration and a cut-plane representation of the transmission eigenstates throughout the device central region under different gate voltages are shown in Fig. 3. In calculations, the parameters are set as follows: The k-point sampling is 1, 1, and 100 in the A, B, and C directions, respectively. The real space grid techniques are used with the energy cutoff of 150 Ry in numerical integrations. The quantum mechanical transmission probability of electrons T(E,V) can be given as16,17:

where E, V are the energy and applied voltage, respectively, ΓL/R is the contact broadening functions related with the left/right electrode and GR/A is the retarded/advanced Green’s function of the central region.

First-principles calculations for edge states based on density functional theory (DFT) in Part S5 of Supplementary Information were conducted using the Perdew-Burke-Ernzerhof (PBE) version of the generalized gradient approximation (GGA).

Data availability

All data needed to evaluate the conclusions in the paper are present in the paper and/or the Supplementary Materials. Additional data related to this paper may be requested from the authors.

References

Bardeen, J. Surface states and rectification at a metal semi-conductor contact. Phys. Rev. 71, 717–727 (1947).

Yao, W., Yang, S. A. & Niu, Q. Edge states in graphene: from gapped flat-band to gapless chiral modes. Phys. Rev. Lett. 102, 096801 (2009).

Plotnik, Y. et al. Observation of unconventional edge states in ‘photonic graphene’. Nat. Mater. 13, 57–62 (2014).

Xu, H. et al. Oscillating edge states in one-dimensional MoS2 nanowires. Nat. Commun. 7, 12904 (2016).

Wang, X. et al. Graphene nanoribbons with smooth edges behave as quantum wires. Nat. Nanotechnol. 6, 563 (2011).

Voiry, D. et al. The role of electronic coupling between substrate and 2D MoS2 nanosheets in electrocatalytic production of hydrogen. Nat. Mater. 15, 1003–1009 (2016).

Li, Y., Zhou, Z., Zhang, S. & Chen, Z. MoS2 nanoribbons: high stability and unusual electronic and magnetic properties. J. Am. Chem. Soc. 130, 16739–16744 (2008).

Bollinger, M. V. et al. One-dimensional metallic edge states in MoS2. Phys. Rev. Lett. 87, 19683 (2001).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Schmidt, H. et al. Transport properties of monolayer MoS2 grown by chemical vapor deposition. Nano Lett. 14, 1909–1913 (2014).

Liu, W., Sarkar, D., Kang, J., Cao, W. & Banerjee, K. Impact of contact on the operation and performance of back-gated monolayer MoS2 field-effect-transistors. ACS Nano 9, 7904–7912 (2015).

Zhang, C., Johnson, A., Hsu, C.-L., Li, L.-J. & Shih, C.-K. Direct imaging of band profile in single layer MoS2 on graphite: quasiparticle energy gap, metallic edge states, and edge band bending. Nano Lett. 14, 2443–2447 (2014).

Lu, C.-I. et al. Graphite edge controlled registration of monolayer MoS2 crystal orientation. Appl. Phys. Lett. 106, 181904 (2015).

Helveg, S. et al. Atomic-scale structure of single-layer MoS2 nanoclusters. Phys. Rev. Lett. 84, 951 (2000).

Xie, F. et al. Tuning of the electronic and transport properties of phosphorene nanoribbons by edge types and edge defects. Org. Electron. 42, 21–27 (2017).

Taylor, J., Guo, H. & Wang, J. Ab initio. Phys. Rev. B 63, 245407 (2001).

Brandbyge, M., Mozos, J.-L., Ordejón, P., Taylor, J. & Stokbro, K. Density-functional method for nonequilibrium electron transport. Phys. Rev. B 65, 165401 (2002).

Dumcenco, D. et al. Large-area epitaxial monolayer MoS2. ACS Nano 9, 4611–4620 (2015).

Melitz, W., Shen, J., Kummel, A. C. & Lee, S. Kelvin probe force microscopy and its application. Surf. Sci. Rep. 66, 1–27 (2011).

Wu, D. et al. Uncovering edge states and electrical inhomogeneity in MoS2 field-effect transistors. Proc. Natl Acad. Sci. USA 113, 8583–8588 (2016).

Radisavljevic, B. & Kis, A. Mobility engineering and a metal-insulator transition in monolayer MoS2. Nat. Mater. 12, 815–820 (2013).

Kronemeijer, A. J. et al. Universal scaling in highly doped conducting polymer films. Phys. Rev. Lett. 105, 156604 (2010).

Akai-Kasaya, M., Okuaki, Y., Nagano, S., Mitani, T. & Kuwahara, Y. Coulomb blockade in a two-dimensional conductive polymer monolayer. Phys. Rev. Lett. 115, 196801 (2015).

Egger, R. Luttinger liquid behavior in multiwall carbon nanotubes. Phys. Rev. Lett. 83, 5547 (1999).

Aleshin, A. N., Lee, H. J., Park, Y. W. & Akagi, K. One-dimensional transport in polymer nanofibers. Phys. Rev. Lett. 93, 196601 (2004).

Kane, C., Balents, L. & Fisher, M. P. A. Coulomb interactions and mesoscopic effects in carbon nanotubes. Phys. Rev. Lett. 79, 5086–5089 (1997).

Bockrath, M. et al. Luttinger-liquid behaviour in carbon nanotubes. Nature 397, 598–601 (1999).

Yuen, J. D. et al. Nonlinear transport in semiconducting polymers at high carrier densities. Nat. Mater. 8, 572–575 (2009).

Gao, B., Komnik, A., Egger, R., Glattli, D. C. & Bachtold, A. Evidence for Luttinger-liquid behavior in crossed metallic single-wall nanotubes. Phys. Rev. Lett. 92, 216804 (2004).

Gong, Y. et al. Electronic transport properties of graphene nanoribbon arrays fabricated by unzipping aligned nanotubes. Phys. Rev. B 87, 165404 (2013).

Zhao, S. et al. Correlation of electron tunneling and plasmon propagation in a Luttinger liquid. Phys. Rev. Lett. 121, 047702 (2018).

Venkataraman, L., Hong, Y. S. & Kim, P. Electron transport in a multichannel one-dimensional conductor: molybdenum selenide nanowires. Phys. Rev. Lett. 96, 076601 (2006).

Jolie, W. et al. Tomonaga-Luttinger liquid in a box: electrons confined within MoS2 mirror-twin boundaries. Phys. Rev. X 9, 011055 (2019).

Ma, Y. et al. Angle resolved photoemission spectroscopy reveals spin charge separation in metallic MoSe2 grain boundary. Nat. Commun. 8, 14231 (2017).

Barja, S. et al. Charge density wave order in 1D mirror twin boundaries of single-layer MoSe2. Nat. Phys. 12, 751 (2016).

Allain, A., Kang, J., Banerjee, K. & Kis, A. Electrical contacts to two-dimensional semiconductors. Nat. Mater. 14, 1195 (2015).

Acknowledgements

The authors are indebted to L. Balents for many valuable discussions. This work was supported in part by the National Natural Science Foundation of China (Grant Nos. 61725404, 61725107, 61890944, 61874134, 61804170, 61574166, 61821091, 61888102, 61720106013, 61404164, and 11874405), the National Key Research and Development Program (Grant Nos. 2019YFA0308000, 2018YFA0208503, 2017YFB0701703, 2016YFA0201802, 2016YFA0202300, and 2016YFA0202304), by the Beijing Training Project for the Leading Talents in S&T under Grant No. Z151100000315008, Strategic Priority Research Program of the Chinese Academy of Sciences (Grant Nos. XDB12030400, XDB30000000) and Beijing Natural Science Foundation (Grant Nos. 4192054 and Z19J00015).

Author information

Authors and Affiliations

Contributions

M.L., H.J.G., L.Li., Y.L.W. and X.F.D. coordinated the research project. G.H.Y., J.B.N., Y.H. and C.Y.L. fabricated and measured the devices. Y.S., J.Q., Y.C., Z.L.L., L.W.L., Y.H., Y.L.W. and G.H.Y. fabricated the samples and carried out the SPM experiments. X.L.M., J.Z.C., Z.Q.F., X.W.J., W.W., and N.D.L. performed the DFT calculations. X.C.C., J.W.W., J.C.C., H.H., G.W.X., X.W.S., Z.Y.J., D.G., L.Liao., W.Q.D., Z.W.Z., Y.L. and X.D.D. provided technical supports. All authors analyzed the data and discussed the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Peer review information Nature Communications thanks Matthias Batzill and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Yang, G., Shao, Y., Niu, J. et al. Possible Luttinger liquid behavior of edge transport in monolayer transition metal dichalcogenide crystals. Nat Commun 11, 659 (2020). https://doi.org/10.1038/s41467-020-14383-0

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-020-14383-0

This article is cited by

-

A tied Fermi liquid to Luttinger liquid model for nonlinear transport in conducting polymers

Nature Communications (2021)

-

Shallowing interfacial carrier trap in transition metal dichalcogenide heterostructures with interlayer hybridization

Nano Research (2021)

-

Intriguing one-dimensional electronic behavior in emerging two-dimensional materials

Nano Research (2021)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.