Abstract

Coherent optical communications provides the largest data transmission capacity with the highest spectral efficiency and therefore has a remarkable potential to satisfy today’s ever-growing bandwidth demands. It relies on so-called in-phase/quadrature (IQ) electro-optic modulators that encode information on both the amplitude and the phase of light. Ideally, such IQ modulators should offer energy-efficient operation and a most compact footprint, which would allow high-density integration and high spatial parallelism. Here, we present compact IQ modulators with an active section occupying a footprint of 4 × 25 µm × 3 µm, fabricated on the silicon platform and operated with sub-1-V driving electronics. The devices exhibit low electrical energy consumptions of only 0.07 fJ bit−1 at 50 Gbit s−1, 0.3 fJ bit−1 at 200 Gbit s−1, and 2 fJ bit−1 at 400 Gbit s−1. Such IQ modulators may pave the way for application of IQ modulators in long-haul and short-haul communications alike.

Similar content being viewed by others

Introduction

Electro-optic modulators that deal with highest data rates on smallest footprints while being energy efficient1,2,3,4,5,6,7,8 are urgently needed to cope with the rapidly growing bandwidth requirements of future communication networks9,10,11,12,13. Particularly, cloud-based services drive an annual traffic growth of 60%, with data centers reaching 80,000 servers10. In recent years, coherent communications has emerged as a solution offering the highest data transmission capacity and spectral efficiency14,15,16. It actually is one of the few schemes with the potential to satisfy the ever-growing bandwidth demands of today’s information society10. However, coherent communications requires in-phase/quadrature (IQ) modulators15,17,18, which allow encoding of information onto the phase and the amplitude of light. Ideally, such modulators should feature high-speed, offer a compact fooptrint, and operate energy efficiently. And while IQ modulators have already convincingly demonstrated operation at highest speed19,20,21, they are still too bulky to be a convincing solution for short-reach communication systems of the future. If these modulators would be energy-efficient, cost-efficient and densely integrated on a chip, they could find significantly broader applications. They might find deployment in applications ranging from classical long-haul communications to the rapidly growing, capacity-hungry inter-datacenter and intra-datacenter communications11, to access networks22,23, and potentially even in chip-to-chip communications and data transfer between cores of multi-core processors13.

To evaluate compactness, energy efficiency, and speed of an electro-optic modulator, the voltage-length product and the achievable line rate have emerged as useful Figures of Merit (FoMs). The voltage-length product UπL defines the device length required to switch from the on- to the off-state with 1 V, which is a convenient measure to evaluate compactness as well as prospects for dense integration and parallelization. The most successful IQ modulator technology to date is based on lithium niobate (LiNbO3). It is the standard in any long-haul optical communication system24 and offers line rates up to 600 Gb s−1 per wavelength and polarization20,25 with fiber-to-fiber losses around 10 dB. Nevertheless, LiNbO3 devices have typical length in the order of cm (UπL ≈ 1–10 V cm, active length ≈ 1–10 cm), which hampers any dense integration and ergonomic parallelization. Conversely, indium phosphide (InP) modulators have been identified as a promising and more compact solution (UπL ≈ 1 Vcm, active length ≈ 3.6 mm)26. They offer similar line rates of up to 660 Gb s−119,21,27, with fiber-to-fiber losses around 9 dB. However, these devices rely on more demanding fabrication technologies and lack the intriguing prospect of monolithic co-integration with CMOS electronics. The silicon platform in contrast promises the co-integration of electronics and photonics on a single chip4,28. Silicon photonic (SiP) IQ modulators offer relatively compact footprints. They have typical lengths of a few mm (UπL ≈ 1 Vcm26,29, active length ≈ 4.5 mm), and already have operated up to 350 Gb s−1 with fiber-to-fiber losses of around 15 dB30. By introducing organic electro-optic (OEO) materials to the SiP platform31,32,33 even shorter devices with 0.5-mm-long active sections (UπL ≈ 0.5–1 Vmm32,33) and line rates of up to 400 Gb s−1 33 became possible with fiber-to-fiber losses of around 17.5 dB33. Even though all of these platforms offer highest line rates, the dimensions of these devices are still relatively large. The photonic nature of these devices and the traveling wave electrode designs required for high-speed operation ultimately limit dense integration capabilities. Supplementary Table 1 summarizes the performance of state-of-the-art IQ modulators.

In addition to speed and compactness, drive voltages compatible with CMOS levels (≤1 V) and small device capacitances are required in order to keep electronics and on-chip heat management relaxed. These requirements can be expressed by the energy that an electrical driver has to provide to modulate one bit, Ebit34, which ideally would be below a femtotjoule per bit (fJ bit−1). While intensity modulators have already demonstrated sub-fJ bit−1 modulation8,35,36 only few have shown to operate with lowest energy consumption at highest-speed (70 Gbit s−1)8.

Recently, plasmonic approaches have emerged as a promising alternative37. The success of these schemes relies on a combination of plasmonic slot-waveguides and an organic38 or ferroelectric39 nonlinear material. These modulators promise lowest voltage-length products (UπL ≈ 40 V µm)40, ultra-fast electro-optic modulation featuring an extraordinary electro-optical bandwidth beyond 500 GHz41,42,43 and modulation up to the THz44, and a most compact footprint5,40. The small size has already enabled dense modulator arrays for interconnect applications demonstrated on a microscopic footprint45,46. And while plasmonics has already shown compact footprints, and low electrical energy consumptions47, it is not clear if the technology can also offer lowest-drive voltages with sub-fJ bit−1 electrical energy consumptions at highest-speed.

In this paper, we demonstrate compact plasmonic IQ modulators on silicon with an active section occupying as little as 4 × 25 µm × 3 µm of footprint (four phase modulators with a footprint of 25 µm × 3 µm each) and show stable operation at data rates up to 400 Gb s−1 with a small UπL ≈ 130 V µm. Furthermore, the devices operate with sub-1 V driving electronics at 100 GBd. Since the devices feature capacitances of a few femtofarad only, this technology features among the lowest electrical energy consumption of any IQ modulator technology demonstrated to date. We calculate electrical energy consumptions to be as low as 0.07 fJ bit−1 at 50 Gb s−1, 0.3 fJ bit−1 at 200 Gb s−1, and 2 fJ bit−1 at 400 Gb s−1. This new IQ modulator implementation takes advantage of the combination of silicon photonics48,49, organic electro-optics50,51, and plasmonic sub-wavelength light confinement52,53,54,55, all of which allow for efficient electro-optic modulation on micrometer footprints. In detail, organic electro-optics and plasmonics offer compact footprints and high-speed modulation. By combining these high-speed modulators with silicon photonic thermo-optic phase shifters, low-loss waveguides, and on-chip power splitters we are able to show highest-speed modulation with lowest drive voltages, high extinction ratios and lowest electrical energy consumptions. The content of this work is in part based on preliminary results first presented at the CLEO conference56.

Results

Plasmonic IQ modulators

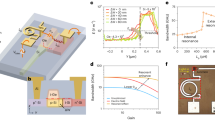

The plasmonic-organic hybrid IQ modulators discussed here, consist of two imbalanced high-speed plasmonic Mach-Zehnder modulators (MZMs)57 integrated into a SiP Mach-Zehnder interferometer (MZI), see Fig. 1a. The phase delay between I and Q branches can be adjusted either by a thermo-optic phase shifter (heater) or by tuning the wavelength, enabled by the imbalance in the SiP MZI. DC biases are used to independently adjust the operating points of the two MZMs. The active sections of the MZMs consist of 15 or 20 µm long plasmonic slot waveguides58 with a slot width of 130 nm, Fig. 1b. The metal-insulator-metal (MIM) plasmonic slot waveguide is filled with the organic electro-optic (OEO) material composite HD-BB-OH/YLD12459. Within the active section, both the electrical RF driving field and the optical field are tightly confined to the plasmonic slot and are overlapping nearly perfectly, Fig. 1c, d.

Plasmonic IQ modulator on the silicon platform. a Colorized scanning electron microscope picture of a plasmonic IQ modulator consisting of two Mach-Zehnder modulators (MZMs). b Zoom into the active section of the modulator, a plasmonic slot waveguide. Light from silicon (Si) feeding waveguide is coupled to the gold (Au) slot waveguide by tapered mode converters. The slot is filled with an organic electro optic (OEO) material (not depicted). c, d Cross section of the plasmonic slot waveguide with simulated c electrical driving field and d optical field

The linear electro-optic effect in the OEO material allows efficient encoding of the electrical driving signal onto the optical carrier3. The devices feature voltage-length products of UπL ≈ 130 V µm and on-chip optical losses of 11.2 dB for the device with 15 μm and 13.7 and 14.5 dB for the devices with 20 μm length. The on-chip losses can be attributed to photonic-plasmonic conversion losses of ~ 1.7 dB per converter and phase shifter losses of ~0.5 dB µm−1. These losses are higher than what was expected from previous fabrication runs (~0.5 dB per converter, 0.38 dB µm−1 38). In addition, we measure fiber-to-chip coupling losses of 4 dB per coupler. With optimized fabrication and coupling techniques, fiber-to-fiber losses below 10 dB should already now be possible. By further exploiting the design freedom offered by organic electro-optics, higher in-device nonlinearies may be expected60. Ultimately, fiber-to-fiber losses below 6 dB should become practical, see Methods section.

High-speed data modulation with driving amplifiers

The plasmonic IQ modulators introduced here offer high line-rate complex modulation up to 400 Gb s−1 on a compact footprint. The active sections occupy only 4 × 25 µm × 3 µm, the contacting electrodes for easy testing consume ~400 µm × 600 µm—but are not needed if cointegrated with electronics. The devices were tested for high-speed signal generation at 50 GBd and 100 GBd, each with QPSK and 16QAM. This corresponds to line rates from 100 Gb s−1 up to 400 Gb s−1. Figure 2 plots the measured bit error ratios (BERs) for three investigated devices IQ1–IQ3 (see Supplementary Table 2) as a function of the line rate. For QPSK modulation, all devices showed BERs well below the KP4 forward error correction (FEC) limit of 2 × 10−4 at both 50 and 100 GBd61. For 16QAM modulation, BERs are well below the HD-FEC limit of 3.8 × 10−3 at 50 GBd and below the SD-FEC limit of 4 × 10−2 at 100 GBd (400 Gbit s−1)25. At 400 Gbit s−1 the device IQ3 dissipates an electrical energy as low as 2 fJ bit−1 when operated with a driving signal of Umeas50Ω,pp = 1.48 V. The voltage is provided by an electrical driving amplifier and has been measured using a 50 Ω oscilloscope. Measurements displayed in Fig. 2 are summarized in Supplementary Table 3.

Results of the high-speed data modulation experiments. a BER as a function of the line rate for three devices, IQ1-3 (blue, red, and yellow). QPSK: circles, 16QAM: diamonds. Operation well below the KP4 FEC threshold for all QPSK measurements. Operation below the 7% HD-FEC threshold at 50 GBd 16QAM and the SD-FEC limit 100 GBd 16QAM. Measurements with BERs below 1 × 10−5 are grouped. b Constellation diagrams for 100 GBd 16QAM and QPSK

Furthermore, we test the compatibility of plasmonic IQ modulators in systems without electronic equalization. Table 1 summarizes the performed measurements. We found BERs below the KP4 FEC limits for at 50/100 GBd QPSK and below the SD-FEC limit at 50 GBd 16QAM. At 100 GBd, a static digital post distortion was applied to account for the strong low-pass characteristics of the electronic components. The experimental setup and the used DSP can be found in the Methods section.

High-speed data modulation with sub-1 V driving electronics

Plasmonic IQ modulators offer high-speed data modulation without the use of expensive and energy-hungry electrical RF amplifiers. Sub-1 V driving electronics in combination with device capacitances in the range of ~3 fF allows for sub-fJ bit−1 electrical energy consumptions up to 200 Gb s−1. The electrical energy efficiency of a modulator is determined by its drive voltage Upp and device capacitance C. It can be estimated to be proportional to CUpp2, derived in the ref. 62 and adapted for QAM modulation formats in the ref. 40. Note that the voltage drop UIQ,pp across the plasmonic IQ’s active section is estimated to be twice the voltage measured with a 50 Ω oscilloscope, hence, Upp,IQ ≈ 2Upp,meas50Ω, see Methods section. Neither heaters nor driving amplifiers were used to operate the device.

Table 2 shows selected constellation diagrams at (a) 100 GBd, (b, c) 50 GBd, and (d) 25 GBd, all operated with sub-1 V driving electronics. At 200 Gb s−1 the device was operated with a drive voltage of Umeas50Ω,pp = 567 mV, resulting in an electrical energy consumptions of 0.3 fJ bit−1. At 50 Gb s−1, the device was operated with Umeas50Ω,pp = 145 mV resulting in an electrical energy consumption of 0.07 fJ bit−1. The slight asymmetry that can be seen in the constellation diagrams of the QPSK signals (a) and (d) is due to an imperfect IQ angle and led to a small BER penalty. Please note that the total system energy consumption is strongly influenced by the transmitter (DAC, DC sources, clock source, laser source), and receiver components (photodiodes, optical amplifiers, oscilloscope) and is strongly defined by the energy efficiencies of these components. Measurements performed with low driving voltages are summarized in Supplementary Table 4.

Stable device operation

Plasmonic IQ modulators offer reliable and stable operation. We demonstrate stable operation for >10 h as well as operation at elevated temperatures of up to 75 °C. The plasmonic IQ modulator IQ1 (see Supplementary Table 2) was operated for ~8 h before we started testing at elevated temperatures. To perform experiments at higher temperatures, the device was mounted on a temperature-controlled sample stage. The sample stage was then heated to the desired temperature. The surface temperature of the stage was measured, see Methods section. Due to the optical power in the slot the temperature in the slot is expected to exceed the set value. However, the temperature in the slot is expected to be at least ~30 °C below the materials glass transition temperature, as no depoling was observed during the measurements. Figure 3 depicts the operating temperature and error vector magnitudes (EVM) taken at five different measurement points M1–M5 (circles) during the operating time of this experiment. After a reference measurement at 42 °C was performed (measurement M1), the device was heated and operated for 70 min at 65 °C and for 80 min at 75 °C. Test measurements M1–M5 have been recorded during this time span. We observe the expected burn-in within the first ~30 min at 60 °C, the EVM increases from 18 to 20%. This originates from a slight increase of the modulator’s UπL product. During this burn-in process the OEO molecules relax to a stable orientation, after which a stable device performance is found. No further degradation of the modulation performance was observed during the temperature tests, the EVM stayed around 20%. More information on the operation at elevated temperatures can be found in the Methods section.

Optical modulation at elevated temperatures for the device IQ1. Operation temperature (solid red) and EVM (dashed blue) as a function of the operating time. The EVM remains nearly constant and stays around 20% for all temperatures. All measurements at 50 GBd QPSK. More information on measurements M1–M5 can be found in the Supplementary Table 5

We identified ~75 °C as the upper temperature limit for stable device operation for the OEO material used in this work. While device IQ1 was operating stably at this temperature during and after the test, we observed de-poling of device IQ3. This temperature of 75 °C is slightly below the temperature of ~80 °C where we noticed de-poling in an earlier experiment5. At these temperatures even small variations in temperature and optical power may induce de-poling, which typically occurs around 30 °C63,64,65 below the OEO material’s glass transition temperature Tg (in this work, Tg ~ 110 °C)59. It is important to note that high-Tg and cross-linked OEO materials potentially offer much better long-term stability at higher temperatures.51,66,67

Discussion

We have presented compact IQ modulators with an active section occupying 4 × 25 µm × 3 µm operating with drive voltages below 1.5 V at up to 400 Gb s−1. We furthermore show high-speed operation of the modulators with sub-1 V driving electronics. We demonstrate low electrical energy consumptions of 0.07 fJ bit−1 at 50 Gb s−1, 0.3 fJ bit−1 at 200 Gbit s−1. At 400 Gb s−1 and a drive voltage of ~1.5 V we find an electrical energy consumption of 2 fJ bit−1 These devices have optical on-chip losses between 11 and 15 dB, demonstrate stable performance (tested for >10 h), and operation at elevated temperatures up to 75 °C. Due to the compactness and energy-efficiency of our modulators, they can be easily parallelized on a tiny footprint at low cost.

The plasmonic modulator technology is a solution that can meet the energy and footprint needs of future optical communications systems. It enables highly parallelized, high-speed coherent communications on a most compact footprint. With this technology, coherent optical communications may become accessible to a much broader field of applications ranging from inter/intra datacenter communications all the way up to access and backbone networks11,22,23. Potentially, considering advances in fabrication technology and organic electro-optics, these devices may be envisioned to even find applications in chip-to-chip communications and communications between cores of multi-core processors13.

Methods

Devices

Within this work, three similar devices (IQ1–IQ3) have been investigated. They feature the properties given in Supplementary Table 2. Losses were measured at maximum transmission. On-chip silicon photonic losses as well as fiber-to-chip coupling losses have been determined by silicon photonic reference structures and photonic cutback structures on the same chip. Plasmonic propagation losses have been determined by plasmonic cutback measurements. Photonic-to-plasmonic converter losses have been derived indirectly from the loss contributions of the individual components.

Taking into account these losses, the maximum optical power within one slot was 8 dBm. In the plasmonic section, light propagates well confined to the slot waveguide. No crosstalk originating from plasmons propagation along the top surface of the gold electrodes can be observed.

Note that both the fiber-to-fiber and the on-chip loss leave room for improvement. By relying on dedicated fabrication processes and the use of established coupling techniques, fiber-to-fiber losses of below 10 dB should be within reach.

By switching to established coupling techniques of the industry, the fiber-to-fiber losses can be reduced by 5 dB to ~14.2 dB. Our current fiber-to-chip coupling of ~4 dB per coupler is higher than what is offered by the industry. SiP foundries offer ~2.5 dB per coupler68. Blazed GCs similar to the ones used within this work, but optimized for perpendicular incidence offer ~1.5 dB per coupler69. Standard edge coupling offers similar losses of ~1–1.5 dB per coupler68.

Furthermore, the photonic-to-plasmonic converters (PPCs) used in this work were optimized for slot widths of 80 nm instead of 130 nm and show higher losses than expected. These linearly tapered PPCs introduce losses of ~1.7 dB per converter while ~0.5 dB per converter are possible with optimized structures. These more efficient converters would improve the fiber-to-fiber losses by another 2.4 dB to ~11.8 dB. Plasmonic propagation losses were estimated using four IQ modulators with two different lengths to be 0.5 dB µm−1, being in good agreement with reference structures on the same chip. In previous experiments, such losses of 0.5 dB µm−1 have been found in 80 nm wide slots38,57, while slot widths of 130 nm should result in values below 0.38 dB µm−1 38. We attribute these increased losses compared to previous runs to higher roughness and impurity of gold, deposited in a multi-user and multi-material deposition system. Switching to a dedicated deposition tool should reduce the fiber-to-fiber losses further to 9.9 dB. Alternatively, a higher gold quality would permit reduction of the slot width to 80 nm, while keeping the losses the same. This would reduce the voltage-length product from UπL ≈ 130 V µm by a factor of approximately two to UπL ≈ 65 V µm. Hence, with current fabrication techniques and coupling options sub-10 dB fiber-to-fiber losses are within reach.

Additionally, the plasmonic-organic hybrid modulator technology offers an intriguing route to improve performance without altering the device structure: the technology can be used with alternative, higher performance OEO materials that have been recently been developed or proposed. While in the current experiment, in-device nonlinearities of ~160 pm V−1 are achieved, higher in-device nonlinearity EO materials with good thermostability are within reach. A doubling of the EO coefficient from ~160 pm V−1 with the current material to 320 pm V−1 (recently demonstrated in-device nonlinearity: 390 pm V−1)70, would allow to reduce the length of the device by a factor of two, potentially reducing the fiber-to-fiber losses to 6 dB. Because the required drive voltage of a plasmonic MZM depends linearly on the length of the plasmonic section and the nonlinearity of the OEO material38, a doubling of the material’s nonlinearity would allow for a 50% shorter device, while keeping the drive voltage constant. Alternatively, the drive voltage could be reduce by a factor of two.

Optimizing OEO materials for plasmonic applications promises further improvements with nonlinearities of >1000 pm V−1 60,71 and consequently will allow to further reduce the fiber-to-fiber loss and the voltage-length product.

Energy consumption per bit and drive voltage

The energy consumption per bit Ebit has emerged as a figure-of-merit (FOM) to compare different electro-optic modulator technologies62. It depends mainly on the device impedance (capacitance) and the electrical drive voltage. Low Ebit values indicate that the devices can be operated with energy efficient electrical driver circuits.

The Ebit FOM of a purely capacitive Mach-Zehnder modulator operated with an NRZ signal is given by35,62 \(E_{{\mathrm{bit}}} = 1/4 \cdot C_{{\mathrm{dev}}}U_{{\mathrm{pp}}}^2{\mathrm{/bit}}\), where Cdev is the device capacitance and Upp is the peak-to-peak drive voltage. For complex modulation formats such as QPSK and 16QAM:40

where CMZM is the capacitance of a single MZM.

The electrical peak-to-peak voltage Upp applied to the device can be measured using an electrical oscilloscope. Most driving electronics and RF measurement equipment have an impedance of 50 Ω. However, the plasmonic modulators are purely capacitive72. When applied to a standard 50 Ω source, twice the 50 Ω-specified voltage can be utilized by the capacitive device35,72. For calculation of Ebit we consider twice the measured voltage Upp = 2Umeas50Ω,pp. We do not take the frequency dependent RF-probe loss into account amounting to between ~0.25 dB at 7 GHz and ~1.1 dB at 67 GHz. Therefore, the effective drive voltages applied to the device is slightly lower than the values in this manuscript.

Figure 4 shows a measured electrical eye diagram used to determine the electrical drive voltage Umeas50Ω,pp. It shows the in-phase component of a 25 GBd QPSK signal. The peak-to-peak drive voltage Umeas50Ω,pp is measured using the probability density function (PDF) at the maximum eye opening. In this example, it is measured to Umeas50Ω,pp = 145 mV. This measurement was performed for in-phase and quadrature signals for all electrical driving signals used in this work.

Device capacitance

The modulator impedance was determined with and without RF contact pads using frequency domain simulations in CST microwave studio. We follow the method published in ref. 72, where simulations and experimental verifications can be found. For the simulation without RF contact pads, the MZM was modeled as a 1 µm wide strip separated by narrow gaps from two ground planes on either side, see Fig. 2.14 and Table 1 in ref. 72. The device impedance was calculated from the simulated reflection coefficient S11 at the device input using \(Z_{\mathrm{d}} = Z_{\mathrm{L}}(1 + S_{11})/(1 - S_{11})\) with ZL = 50 Ω. The capacitance was determined from the simulated imaginary part of Zd with \(C_{\mathrm{d}} = - \frac{1}{{{\mathrm{Im}}\left\{ {Z_{\mathrm{d}}2\pi f} \right\}}}\), yielding Cd = 3.4fF at 20 GHz (IQ1: 2.6 fF). When including the electrical contact pads, the capacitance yielded \(C_{\mathrm{d}} = 36\,{\mathrm{fF}}\). Even if the large pads are added, the energy consumption is below 1 fJ bit−1 at 50 Gb s−1 and below 5 fJ bit−1 at 200 Gb s−1.

High-speed experiments with driving amplifiers

The high-speed experiments were performed using the setup depicted in Fig. 5. At the transmitter, electrical signals (100 GBd NRZ and 50 GBd NRZ, QPSK and 16QAM) are generated offline and are sent to two (one for in-phase (I) and one for quadrature (Q) component) digital-to-analog converters (DAC, Micram DAC4, 100 GSa s−1, 3 dB BW: 40 GHz, vertical resolution of 6 bit). Subsequently, the electrical signals were amplified by electrical driving amplifiers (RF amps: 3 dB BW: 55 GHz or 3 dB BW: 65 GHz) before they were combined with a DC bias to control the operating points of the MZMs (between 0 and 8 V) using bias tees (3 dB BW: 65 GHz). The electrical signals are fed by two RF probes (ground-signal-ground (GSG) configuration, 1 dB BW: ~60 GHz) to the device under test (DUT). The IQ bias was adjusted by using the thermo-optic phase shifter, with an electrical heating power between 0 and ~20 mW.

Light from an external cavity laser (ECL) (wavelength around 1550 nm) was amplified to 15 dBm – 20 dBm using an erbium-doped fiber amplifier (EDFA) and was fed to- and from the chip using fiber-to-chip grating couplers. The modulated light is coupled back to fiber and send to the optical coherent receiver. At the receiver the signal is amplified by and EDFA and mixed with the local oscillator in a 90° optical hybrid. Two balanced photo diodes (3 dB BW: 70 GHz) receive the signal which is digitized by a real-time oscilloscope (160 GSa s−1 3 dB BW: 63 GHz).

High-speed data modulation with sub-1 V driving electronics

The experimental setup used during low drive voltage experiments is depicted in Fig. 6. It is similar to setup Fig. 5, however, the electrical driving amplifiers have been removed. Electrical 6 dB attenuators have been inserted to achieve sub-300 mV electrical drive voltages. The thermo-optic phase shifter has not been used during experiments without electrical driver amplifiers. The IQ operating point was adjusted by using the operating wavelength.

In the transmitter, electrical output swing voltages between 350 and 650 mV have been set. To measure the electrical drive voltage applied to the device, the bias tees have been removed from the RF-probes and connected to a real-time oscilloscope. Peak-to-peak voltages between 145 and 570 mV have been measured. Note, that the RF probes introduce additional losses of ~0.25 dB at 7 GHz and ~1.1 dB at 67 GHz. These additional RF losses are not taken into account.

Offline digital signal processing (DSP)

Offline DSP for waveform generation and synchronization was applied. Before the actual measurements, the setup was calibrated in an electrical back-to-back configuration.

The electrical transmitter consisted of a 100 GSa s−1 DAC (Micram DAC4). The realization of different symbol rates was done by tuning the oversampling ratio in the transmitter DSP. To maximize the statistically relevance of our measurements, we always generated waveforms derived from randomly distributed bits with a length as close to the memory size of the DAC of 219 samples as possible.

The optical receiver detected the in-phase and quadrature part of the waveform and sampled the signal with 160 GSa s−1. For the 100 GBd measurements, we applied a static digital post-distortion filter at the beginning of the DSP73. The following steps were timing synchronization, carrier recovery and linear and non-linear equalization. Finally, we measured the bit to error ratio (BER). The noise distribution of the synchronized symbols was used to estimate EVM and SNR74. In case of very few or no counted bit errors, the BER was estimated using the SNR.

Temperature stability measurement

The chip was mounted on top of a thermo-electric heater with thermal paste. The surface temperature of the heater was measured using a PT1000 temperature sensor and set to the desired temperature by feeding an electrical current through the thermo-electric heater. For each measurement the DC bias of the individual MZMs was adjusted in a range between ±8 V, the IQ bias was adjusted using the on-chip thermo-optic phase shifter.

Device fabrication

The plasmonic IQ modulators were fabricated in-house on a silicon-on-insulator (SOI) wafer consisting of a 220-nm-thick silicon device layer and a 3-μm-thick buried oxide. Electron-beam lithography using a Vistec EBPG5200 system was applied to pattern the structures in all process steps. A negative tone electron-beam resist was used to pattern photonic components comprising waveguides, MMIs and fiber-to-chip grating couplers (GCs)69. The patterns were transferred into the silicon device layer (fully etched structures) by applying an inductively coupled plasma—reactive ion etching (ICP-RIE). Partial etching (70 nm deep) of blazed GCs was realized with the use of a positive tone electron-beam resist and the ICP-RIE process as in the case of the fully etched silicon structures. A 700-nm-thick SiO2 cladding layer was deposited by plasma-enhanced chemical vapor deposition (PECVD) and locally opened in the active plasmonic sections using reactive ion etching (RIE). The SiO2 cladding reduces the influence of the OEO cladding on the GC performance. Plasmonic MIM waveguides and electrodes as well as the heater structure were produced with a lift-off process applied to a 150-nm-thick e-beam evaporated layer of gold. The organic electro-optic (OEO) material composite 75% wt HD-BB-OH/25% wt YLD12459 was deposited in a post-processing step by spin coating. Subsequently, a poling process induced the nonlinearity38. Envisioning co-integration with other devices, the OEO cladding material may be locally removed by an additional lithography step followed by structuring, e.g., by an O2 plasma-etching process.

Data availability

A comparison of state-of-the-art IQ modulators is provided in Supplementary Table 1. Information on the IQ modulators used in this work is provided in Supplementary Table 2. Detailed information on the measurements displayed in Fig. 2 are provided in Supplementary Table 3. Detailed information on the measurements performed with sub-1V driving electronics, are provided in Supplementary Table 4. Data of measurements displayed in Fig. 3 is provided in Supplementary Table 5. The datasets generated during and/or analysed during the current study are available from the corresponding author on reasonable request.

References

Xu, Q., Schmidt, B., Pradhan, S. & Lipson, M. Micrometre-scale silicon electro-optic modulator. Nature 435, 325–327 (2005).

Timurdogan, E. et al. An ultralow power athermal silicon modulator. Nat. Commun. 5, 4008 (2014).

Haffner, C. et al. All-plasmonic Mach–Zehnder modulator enabling optical high-speed communication at the microscale. Nat. Photon. 9, 525–528 (2015).

Sun, C. et al. Single-chip microprocessor that communicates directly using light. Nature 528, 534–538 (2015).

Ayata, M. et al. High-speed plasmonic modulator in a single metal layer. Science 358, 630–632 (2017).

Haffner, C. et al. Low-loss plasmon-assisted electro-optic modulator. Nature 556, 483–486 (2018).

Sorianello, V. et al. Graphene–silicon phase modulators with gigahertz bandwidth. Nat. Photon. 12, 40–44 (2017).

Wang, C. et al. Integrated lithium niobate electro-optic modulators operating at CMOS-compatible voltages. Nature 562, 101–104 (2018).

Doerr, C. R. Silicon photonic integration in telecommunications. Front. Phys. 3, 37 (2015).

Winzer, P. J. & Neilson, D. T. From scaling disparities to integrated parallelism: a Decathlon for a decade. J. Lightwave Technol. 35, 1099–1115 (2017).

Zhou, X., Liu, H., Urata, R. & Zebian, S. Scaling large data center interconnects: challenges and solutions. Opt. Fiber Technol. 44, 61–68 (2018).

Levi, A. F. Silicon photonics’ last-meter problem: economics and physics still pose challenges to “fiber to the processor” tech. IEEE Spectrum 55, 38–43 (2018).

Thraskias, C. A. et al. Survey of photonic and plasmonic interconnect technologies for intra-datacenter and high-performance computing communications. IEEE Commun. Surv. Tutor. 20, 2758–2783 (2018).

Schmogrow, R. et al. 512QAM Nyquist sinc-pulse transmission at 54 Gbit/s in an optical bandwidth of 3 GHz. Opt. Express 20, 6439–6447 (2012).

Kikuchi, K. Fundamentals of coherent optical fiber communications. J. Lightwave Technol. 34, 157–179 (2016).

Wang, Y., Okamoto, S., Kasai, K., Yoshida, M. & Nakazawa, M. Single-channel 200 Gbit/s, 10 G symbol/s-1024 QAM injection-locked coherent transmission over 160 km with a pilot-assisted adaptive equalizer. Opt. Express 26, 17015–17024 (2018).

Shimotsu, S. et al. Single side-band modulation performance of a LiNbO3 integrated modulator consisting of four-phase modulator waveguides. IEEE Photonic Technol. Lett. 13, 364–366 (2001).

Griffin, R. A. et al. 10 Gb/s optical differential quadrature phase shift key (DQPSK) transmission using GaAs/AlGaAs integration. Optical Fiber Communications Conference, Anaheim, CA, USA, FD6 (2002).

Going, R. et al. Multi-channel InP-based coherent PICs with hybrid integrated SiGe electronics operating up to 100 GBd, 32QAM. European Conference on Optical Communication, Gothenburg, Sweden, Th.PDP.C.3 (2017).

Raybon, G. et al. 180-GBaud All-ETDM single-carrier polarization multiplexed QPSK transmission over 4480 km. Optical Fiber Communications Conference, San Diego, CA, USA, Th4C.3 (2018).

Ogiso, Y. et al. Ultra-high bandwidth InP IQ modulator co-assembled with driver IC for beyond 100-GBd CDM. Optical Fiber Communications Conference, San Diego, CA, USA, Th4A.2 (2018).

Shahpari, A. et al. Coherent access: a review. J. Lightwave Technol. 35, 1050–1058 (2017).

Suzuki, N., Miura, H., Matsuda, K., Matsumoto, R. & Motoshima, K. 100 Gb/s to 1 Tb/s based coherent passive optical network technology. J. Lightwave Technol. 36, 1485–1491 (2018).

Wooten, E. L. et al. A review of lithium niobate modulators for fiber-optic communications systems. IEEE J. Sel. Top. Quant. Electron. 6, 69–82 (2000).

Schuh, K. et al. Single carrier 1.2 Tbit/s transmission over 300 km with PM-64 QAM at 100 GBaud. Optical Fiber Communications Conference, Los Angeles, CA, USA, Th5B.5 (2017).

Doerr, C. Coherent optics in Si photonics. Optical Fiber Communications Conference, San Diego, CA, USA, Tu2E.5 (2018).

Maher, R. et al. Constellation shaped 66 GBd DP-1024QAM transceiver with 400 km transmission over standard SMF. European Conference on Optical Communication, Gothenburg, Sweden, Th.PDP.B.2 (2017).

Xiong, C. et al. Monolithic 56 Gb/s silicon photonic pulse-amplitude modulation transmitter. Optica 3, 1060–1065 (2016).

Dong, P. et al. Silicon in-phase/quadrature modulator with on-chip optical equalizer. J. Lightwave Technol. 33, 1191–1196 (2015).

Lin, J., Sepehrian, H., Rusch, L. A. & Shi, W. CMOS-compatible silicon photonic IQ modulator for 84 Gbaud 16QAM and 70 Gbaud 32QAM. Optical Fiber Communications Conference, San Diego, CA, USA, Tu2E.4 (2018).

Leuthold, J. et al. Silicon-organic hybrid electro-optical devices. IEEE J. Sel. Top. Quant. 19, 114–126 (2013).

Heni, W. et al. Silicon-organic and plasmonic-organic hybrid photonics. ACS Photon. 4, 1576–1590 (2017).

Wolf, S. et al. Coherent modulation up to 100 GBd 16QAM using silicon-organic hybrid (SOH) devices. Opt. Express 26, 220–232 (2018).

Miller, D. A. B. Attojoule optoelectronics for low-energy information processing and communications. J. Lightwave Technol. 35, 346–396 (2017).

Koeber, S. et al. Femtojoule electro-optic modulation using a silicon-organic hybrid device. Light Sci. Appl. 4, e255 (2015).

Sorger, V. J. et al. Scaling vectors of attoJoule per bit modulators. J. Opt. 20, 014012 (2017).

Emboras, A. et al. Electrically controlled plasmonic switches and modulators. IEEE J. Sel. Top. Quant. 21, 1–8 (2015).

Heni, W. et al. Nonlinearities of organic electro-optic materials in nanoscale slots and implications for the optimum modulator design. Opt. Express 25, 2627–2653 (2017).

Messner, A. et al. Plasmonic ferroelectric modulators. J. Lightwave Technol. 37, 281–290 (2019).

Haffner, C. et al. Plasmonic organic hybrid modulators—scaling highest speed photonics to the microscale. Proc. IEEE 104, 2362–2379 (2016).

Hoessbacher, C. et al. Plasmonic modulator with >170 GHz bandwidth demonstrated at 100 GBd NRZ. Opt. Express 25, 1762–1768 (2017).

Ummethala, S. et al. Terahertz-to-optical conversion using a plasmonic modulator. Conference on Lasers and Electro-Optics, San Jose, CA, USA, STu3D.4 (2018).

Burla, M. et al. 500 GHz plasmonic Mach-Zehnder modulator enabling sub-THz microwave photonics. arXiv preprint: https://arxiv.org/abs/1901.00477 (2018).

Benea-Chelmus, I. C. et al. Three-dimensional phase modulator at telecom wavelength acting as a terahertz detector with an electro-optic bandwidth of 1.25 terahertz. ACS Photon. 5, 1398–1403 (2018).

Heni, W. et al. High speed plasmonic modulator array enabling dense optical interconnect solutions. Opt. Express 23, 29746–29757 (2015).

Koch, U. et al. Ultra-Compact Terabit Plasmonic Modulator Array. J. Lightwave Technol. 37, 1484–1491 (2019).

Baeuerle, B. et al. Driver-less sub 1 V pp pperation of a plasmonic-organic hybrid modulator at 100 GBd NRZ. Optical Fiber Communications Conference, San Diego, CA, USA, M2I.1 (2018).

Soref, R. The past, present, and future of silicon photonics. IEEE J. Sel. Top. Quant. 12, 1678–1687 (2006).

Bogaerts, W. et al. Nanophotonic waveguides in silicon-on-insulator fabricated with CMOS technology. J. Lightwave Technol. 23, 401–412 (2005).

Dalton, L. R., Sullivan, P. A. & Bale, D. H. Electric field poled organic electro-optic materials: state of the art and future prospects. Chem. Rev. 110, 25–55 (2009).

Luo, J. et al. Tailored organic electro-optic materials and their hybrid systems for device applications. Chem. Mater. 23, 544–553 (2010).

Pile, D. F. P. et al. Two-dimensionally localized modes of a nanoscale gap plasmon waveguide. Appl. Phys. Lett. 87, 261114 (2005).

Schuller, J. A. et al. Plasmonics for extreme light concentration and manipulation. Nat. Mater. 9, 193–204 (2010).

Gramotnev, D. K. & Bozhevolnyi, S. I. Plasmonics beyond the diffraction limit. Nat. Photon. 4, 83–91 (2010).

Hayashi, S. & Okamoto, T. Plasmonics: visit the past to know the future. J. Phys. D 45, 433001 (2012).

Heni, W. et al. 100 GBd plasmonic IQ modulator. Conference on Lasers and Electro-Optics, San Jose, CA, USA, SM1I.4 (2018).

Heni, W. et al. 108 Gbit/s plasmonic Mach-Zehnder modulator with >70-GHz electrical bandwidth. J. Lightwave Technol. 34, 393–400 (2016).

Melikyan, A. et al. High-speed plasmonic phase modulators. Nat. Photon. 8, 229–233 (2014).

Elder, D. L. et al. Effect of rigid bridge-protection units, quadrupolar interactions, and blending in organic electro-optic chromophores. Chem. Mater. 29, 6457–6471 (2017).

Robinson, B. H. et al. Optimization of plasmonic-organic hybrid electro-optics. J. Lightwave Technol. 36, 5036–5047 (2018).

El-Fiky, E. et al. First demonstration of a 400 Gb/s 4λ CWDM TOSA for datacenter optical interconnects. Opt. Express 26, 19742–19749 (2018).

Miller, D. A. Energy consumption in optical modulators for interconnects. Opt. Express 20, A293–A308 (2012).

Kaatz, P. et al. Relaxation processes in nonlinear optical polyimide side-chain polymers. Macromolecules 29, 1666–1678 (1996).

Pretre, P. et al. Relaxation processes in nonlinear optical polymers: a comparative study. Macromolecules 31, 1947–1957 (1998).

Dalton, L. R., Günter, P., Jazbinsek, M., Sullivan, P. A. & Kwon, O.-P. Organic Electro-Optics and Photonics: Molecules, Polymers and Crystals. (Cambridge University Press, Cambridge, 2015).

Lauermann, M. et al. Generation of 64 GBd 4ASK signals using a silicon-organic hybrid modulator at 80 °C. Opt. Express 24, 9389–9396 (2016).

Jin, D. et al. EO polymer modulators reliability study. Proceedings of SPIE 7599, Organic Photonic Materials and Devices XII. 75990H-75990H-75998 (2010).

Carroll, L. et al. Photonic packaging: transforming silicon photonic integrated circuits into photonic devices. Appl. Sci. 6, 426 (2016).

Watanabe, T., Ayata, M., Koch, U., Fedoryshyn, Y. & Leuthold, J. Perpendicular grating coupler based on a blazed antiback-reflection structure. J. Lightwave Technol. 35, 4663–4669 (2017).

Kieninger, C. et al. Ultra-high electro-optic activity demonstrated in a silicon-organic hybrid modulator. Optica 5, 739–748 (2018).

Haffner, C. et al. Harnessing nonlinearities near material absorption resonances for reducing losses in plasmonic modulators. Opt. Mater. Express 7, 2168–2181 (2017).

Hoessbacher, C. Plasmonic switches and modulators for optical communications—Section 2.33, “RF Characteristics”. PhD Thesis thesis, ETH Zurich. 10.3929/ethz-b-000219646, (2017).

Josten, A., Baeuerle, B., Bonjour, R., Heni, W. & Leuthold, J. Optical transmitters without driver amplifiers—optimal operation conditions. Appl. Sci. 8, 1652 (2018).

Schmogrow, R. et al. Error vector magnitude as a performance measure for advanced modulation formats. IEEE Photon. Technol. Lett. 24, 61–63 (2012).

Acknowledgements

The authors thank Aldo Rossi for technical support. This work was partly carried out in the Binnig and Rohrer Nanotechnology Center as well as in the FIRST cleanroom facility at the ETH Zurich. The work was partially funded by: EU-project PLASMOfab (688166), ERC PLASILOR (670478), NSF (DMR-1303080) and AFOSR (FA9550-15-1-0319).

Author information

Authors and Affiliations

Contributions

W.H. conceived the concept, designed and developed the devices, designed and performed the experiments and analyzed the data. Y.F. developed the fabrication process and fabricated the devices. B.B. and A.J. developed the infrastructure for high-speed data experiments, designed and developed the algorithms for data analysis, and contributed to the experiments and data analysis. C.B.H. determined the device capacitance and contributed to the design of the devices. A.M. developed the setup for operation at elevated temperatures. C.H. contributed to the design and development of the devices. T.W. designed the fiber-to-chip grating couplers. Y.S. and U.K. contributed to the design of the devices. D.L.E. and L.R.D. developed and synthesized the HD-BB-OH/YLD124 nonlinear material. J.L. conceived the concept and supervised the project. All authors have contributed to the writing of the manuscript.

Corresponding authors

Ethics declarations

Competing interests

W.H., B.B., C.B.H., and J.L. are involved in activities towards commercializing plasmonic modulators at Polariton Technologies Ltd. The remaining authors declare no competing interests.

Additional information

Journal peer review information: Nature Communications thanks the anonymous reviewers for their contribution to the peer review of this work.

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Heni, W., Fedoryshyn, Y., Baeuerle, B. et al. Plasmonic IQ modulators with attojoule per bit electrical energy consumption. Nat Commun 10, 1694 (2019). https://doi.org/10.1038/s41467-019-09724-7

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-019-09724-7

This article is cited by

-

Enhancing on/off ratio of a dielectric-loaded plasmonic logic gate with an amplitude modulator

Scientific Reports (2023)

-

Resonant plasmonic micro-racetrack modulators with high bandwidth and high temperature tolerance

Nature Photonics (2023)

-

An approach for designing energy-efficient integrated silicon photonics transmitters

Nature Electronics (2023)

-

Integrated optical memristors

Nature Photonics (2023)

-

Plasmonic Slot Waveguide Propagation Analysis

Plasmonics (2023)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.