Abstract

Charge carrier-selective contacts transform a light-absorbing semiconductor into a photovoltaic device. Current record efficiency solar cells nearly all use advanced heterojunction contacts that simultaneously provide carrier selectivity and contact passivation. One remaining challenge with heterojunction contacts is the tradeoff between better carrier selectivity/contact passivation (thicker layers) and better carrier extraction (thinner layers). Here we demonstrate that the nanowire geometry can remove this tradeoff by utilizing a permanent local gate (molybdenum oxide surface layer) to control the carrier selectivity of an adjacent ohmic metal contact. We show an open-circuit voltage increase for single indium phosphide nanowire solar cells by up to 335 mV, ultimately reaching 835 mV, and a reduction in open-circuit voltage spread from 303 to 105 mV after application of the surface gate. Importantly, reference experiments show that the carriers are not extracted via the molybdenum oxide but the ohmic metal contacts at the wire ends.

Similar content being viewed by others

Introduction

Carrier-selective contacts are an essential component of solar cells1. Traditionally, the semiconductor is doped with specific impurity atoms, raising the electron or hole concentration and hence conductivity in the highly doped regions. However, those regions suffer from increased nonradiative recombination (especially Auger-type), decreased carrier mobility and parasitic light absorption that increases minority carrier conductivity and decreases contact selectivity1. Therefore, high-efficiency wafer-based silicon2,3,4,5,6,7,8,9,10, III-V11,12 (https://www.altadevices.com/technology/), organic13,14, and perovskite15,16,17,18 solar cells all employ heterojunction contacts providing simultaneously a high degree of carrier selectivity in the adjacent large band gap material and excellent interface passivation. One difficulty that arises with heterojunction contacts is that there is often a tradeoff between the need for thicker layers to improve contact selectivity and reduce contact recombination, while needing thin layers to minimize carrier extraction losses (especially at high current density) and parasitic absorption. Even for the 5−10-nm-thin a-Si:H(i) layers that are used to passivate current high-efficiency silicon heterojunction solar cells, a thickness increase, if allowed by removing electrical and optical limitations19, could still lead to an improved open-circuit voltage (VOC) from currently 738 to 750 mV20,21,22 to the Auger limit of about 760 mV (for 110 μm wafer thickness)23 due to strongly thickness-dependent passivation properties for films below approx. 15 nm24,25. Those limitations are also present for the heterojunction interfaces that have been realized for nanowire solar cells26,27,28,29,30. However, nanowire photovoltaics can in principle decouple the carrier selectivity and extraction functions of the heterojunction by using the extreme surface sensitivity to control electron and hole concentrations in the vicinity of the contact. Such an approach is commonly used in electronics where an electrostatic gate voltage can drastically alter the carrier concentration in a narrow surface channel adjacent to electrical contacts, causing accumulation, depletion or even inversion without the need for an interfacial layer in between the contact and channel. Nanowires with a wrap-around gate structure provide the ideal geometry for maximum gate coupling and have already shown excellent performance31,32,33,34,35,36. It is also possible to remove the need for a gate voltage by employing surface layers that either donate or withdraw electric charge to act as a permanent fixed gate37,38,39,40. Taking this one step further, such a surface layer has been used to create a nanowire solar cell without doping28,41. Even though the performance was somewhat worse than that of state-of-the-art nanowire solar cells, the approach is very appealing due to the difficulty of controlled doping at the nanoscale42 and the excellent surface gate coupling.

Here, we show how the strong surface sensitivity of InP nanowires can be used to alter the charge carrier selectivity of the hole contact while keeping the extraction path unchanged. One of the main challenges of InP nanowires, in fact III-V semiconductor materials in general, is the formation of the hole-selective contact, that is traditionally the highly p-type doped region. The most widely used and also here employed p-dopant Zn shows strongly limited incorporation dynamics during growth, strongly increasing diffusion constants with increasing concentration43,44,45 and is known to even cause increased nonradiative recombination46. Therefore, the formation of short (smaller than 500 nm) highly doped p-type nanowire segments with an abrupt doping profile is very challenging47,48. For InP nanowires those problems are even amplified due to Fermi level pinning under the conduction band caused by the native oxide. It is because of those reasons that we focus here on the hole contact while our approach is also applicable to the electron contact, given the successful realization of dopant-free n-type heterojunction contacts in bulk solar cells in the past3,5,11,49. First, we fabricate ohmic contacts to a horizontal InP p-i-n junction nanowire solar cell followed by selective surface modification next to (not underneath) the hole contact. Removing the native oxide by HF etching and depositing MoOX increases the VOC by up to 335 mV, reaching values up to 835 mV. This VOC value is comparable to that obtained for record single InP nanowires (800−890 mV)50,51 and nanowire array InP solar cells (760 mV (17.8% efficiency) and 906 mV (13% efficiency))52,53 and even close to that of record bulk InP solar cells (currently 939 mV)54, which is quite remarkable given no special surface passivation has been applied55. Our results demonstrate that the nanowire geometry allows for a traditional heterojunction layer to act as a surface gate, increasing the local hole concentration and thereby providing excellent carrier selectivity by changing the effective doping concentration, without changing the impurity doping level at the contact. In contrast to traditional heterojunction contacts, the surface gate approach does not require conduction through the often resistive heterojunction contact material itself, making it possible to use very thick surface gate layers without introducing a charge carrier extraction barrier.

Results

Schematic overview

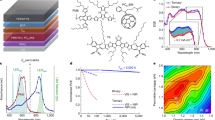

Figure 1 schematically shows three different types of charge carrier-selective contacts: traditional doped semiconductor homojunction, traditional heterojunction, and nanowire surface gating contacts. For traditional homojunction solar cells (Fig. 1a), charge carrier selectivity of a contact is induced by doping the underlying semiconductor region with impurities, thereby increasing the carrier density and conductivity of one charge carrier while decreasing the conductivity for the opposite charge carrier. Traditional heterojunction contacts rely instead primarily on local accumulation/inversion (change in carrier density but not impurity doping level) inside the semiconductor caused by a difference in Fermi level at the interface to establish carrier-selective contacts (Fig. 1b). Importantly, the heterojunction interface is required to be free of charge carrier extraction barriers and to provide asymmetric band offsets for electrons and holes. Furthermore, once a suitable heterojunction contact material is found it often has to be kept thin to limit resistance and absorption losses. In this study, we show that nanowires allow for another type of charge carrier-selective contact, which can strongly reduce the requirements compared to traditional heterojunction interfaces. Nanowires can utilize surface gating layers, such as high or low work function oxides, to induce carrier accumulation/inversion in the semiconductor, i.e. they control the local carrier concentration without changing the doping level (Fig. 1c). However, in stark contrast to traditional solar cells, the charge carriers can be extracted via ohmic metal point contacts at the nanowire end segments; the employed surface layers are not being used for extraction but instead act like a local chemical gate to induce the required selectivity (see also cross-sectional image in Fig. 1c). Therefore, the requirements are strongly reduced compared to traditional heterojunction interfaces.

Different types of charge carrier-selective contacts. a Contact selectivity of traditional solar cells is determined by the doping density of the semiconductor directly underneath the metal contact. b Contact selectivity of heterojunction solar cells is determined by the induced accumulation/inversion region inside the semiconductor directly underneath the metal contact, due to the work function difference between heterojunction contact material and semiconductor. c Nanowires allow for a different type of charge carrier-selective contact; the carriers can be extracted parallel to the surface instead of perpendicular to it (as in doped- and heterojunction contacts) (red and blue arrows). This means that carriers are not extracted through the surface-gate layer. The cross-sectional image shows a possible band alignment and the blocking of radial hole transport at the surface-gate interface. In d−f, the band diagrams in the dark are drawn for the cases in a−c, respectively. We note that band bending in the dark is indicative for the selectivity of a contact but not a sufficient description. For an accurate assessment of charge carrier selectivity the quasi-Fermi level under illumination have to be considered, which have been omitted here for simplicity. The color gradient indicates the charge carrier selectivity with red being very hole selective and blue very selective for electron conduction

Influence of surface gate on open-circuit voltage

To study this nanowire surface gating selective contact, we use single horizontal p-i-n junction InP nanowires grown by selective area epitaxy56,57 (200 nm diameter with a 50 nm SiO2 shell) with ohmic contacts at the ends. The SiO2 shell was used to increase long-term stability, while also avoiding clustering into nanowire bundles during the drop casting on the electrode chips. By using single nanowire devices, the impact of different surface treatments can be studied directly via I−V characteristics and unobscured by average effects over millions of wires on the typical nanowire array level (see optical microscope image in Fig. 2a). After the ohmic contact formation we coat the entire device with electron beam resist and open windows along the p-type segment of the nanowire next to the ohmic metal contact where we apply different surface treatments to induce the surface gate (I, IIa, and IIb in Fig. 2a). Previously, we measured a large difference between the optically implied VOC58,59 and the electrically extracted VOC using similar InP nanowire solar cells indicating that the electrically extracted VOC is limited by contact selectivity for those devices and not by surface or bulk recombination51.

Improving carrier selectivity with MoOX. a Schematic of experimental setup. Contacted single InP nanowire p-i-n junction solar cells are coated with electron-beam resist. A window is opened in the resist next to the hole contact to test the device characteristics before any treatment (I), after HF (IIb) or after HF and 30 nm MoOX layer evaporation (IIa). To prevent degradation of the MoOX work function due to ambient contaminants, a 100 nm Au capping layer (orange) has been evaporated. The right side shows an dark-field optical microscope image of single nanowire solar cells before surface treatment, where the resist windows are visible. b I−V curve before and after HF + MoOX treatment. The vertical dashed lines indicate the open-circuit voltage. c Scatter plot showing each single nanowire solar cell VOC before and after HF etching (yellow) or HF etching + MoOX evaporation (green)

Figure 2b shows the I−V curve before (dashed) and after (solid) the high work function interfacial layer MoOX has been evaporated onto the same device after HF etching (approx. 10 min exposure to air). The work function of MoOX has been determined to be between about 5.7 eV and 6.6 eV, depending on the amount of carbon contamination (decreasing with increasing carbon content)9. For wurtzite InP the valence band lies around 5.75 eV while the band gap is 1.43 eV (300 K)60, explaining the ability of MoOX to create a hole accumulation region inside the semiconductor. The increase in VOC is clearly visible for the depicted device; the VOC increases by 230 mV, reaching 730 mV. All the single InP nanowire solar cells, for which we measured the same device before and after the surface treatment, showed a substantial increase in VOC (Fig. 2c). Interestingly, although there was a very large spread in VOC of the devices relying only on the p-i-n junction doping for the carrier selectivity (454−757 mV), after MoOX surface coating all the devices showed high VOC values (730−835 mV) and no remaining correlation with the original VOC. This suggests that doping nonuniformities were causing nearly all the variation in VOC observed from wire to wire and that MoOX surface coatings are capable of fixing poor carrier selectivity by inducing a higher hole concentration via a surface gate effect. Photoluminescence images before the contact formation indeed indicate doping nonuniformities of the as-grown wires (see Supplementary Figure 1 and Supplementary Note 1).

To further support the surface gate hypothesis we also fabricated device geometries where the MoOX pad covered the n-type part of our nanowire solar cells. This device geometry resulted in strongly decreased performance (Supplementary Figure 2a). Furthermore, experiments on symmetrically doped p-type wires and a MoOX pad covering the central nanowire part showed an increase in conductivity (Supplementary Figure 2b).

Therefore, we can clearly state that the MoOX increases the hole-conductivity and hence selectivity of the p-type part in Fig. 2. Interestingly, several nanowire devices that had a small gap between the surface gate window and original metal contact (due to misalignment in the last lithography step) still showed large VOC improvement (representative example in Supplementary Figure 3). This suggests that the MoOX is not acting as a traditional heterojunction, where carriers are extracted via the heterojunction layer, but instead only as a surface gate, with carriers extracted directly via the metal contact.

Figure 2b shows the occurrence of an s-shaped I−V curve after the surface treatment, while Supplementary Figure 3 clearly shows the s-shaped character already before the treatment. We ascribe the observed extraction barriers to nonideal effective doping concentrations along the hole extraction path (for a detailed discussion see SI). This is further supported by the resistive behavior of our devices in the dark, as shown in Supplementary Figure 4.

While the increase in VOC with MoOX surface modification is consistent across all measured devices, the short-circuit current ISC increases for some devices (e.g. Fig. 2b) or decreases (e.g. Supplementary Figure 3) after the treatment. Importantly, the increase in ISC is only observed for devices with relatively poor initial performance, while for initially good performing devices, the ISC always decreases. The decrease can be explained by the opaque Au coverage of the MoOX, which is used in order to maintain the high MoOX work function and avoid its degradation due to ambient contaminants.

We note that our current results are strongly limited by the horizontal single nanowire device geometry. A wrap-around gate geometry with an ohmic metal contact only at the very tip of a short nanowire can not only remove the observed s-shaped character but also increase hole-selectivity to even higher values, due to more uniform surface gate coupling. Currently, the nanowire region next to the surface facing the substrate will have a smaller change in carrier concentration due to the asymmetric deposition of MoOX in this proof-of-concept geometry.

Motivated by those results, we also fabricated single nanowire devices with the traditional interfacial layer geometry where MoOX (15 nm) is present everywhere between the p-type InP and the Au contact. However, all of the fabricated devices (ca. 50) showed very high resistance or no apparent electrical contact at all. Therefore, we can conclude that the interfacial layer on our devices shown here improved the carrier selectivity indeed without changing the extraction path, as was already indicated by the observation of VOC improvements despite unintended gaps between metal contacts and MoOX pads; even though MoOX is present on the surface, the charge carriers are still being extracted via the ohmic contact at the nanowire end. This observation indicates a large charge carrier extraction barrier at the InP|MoOX interface, which we speculate is related to negative charging of the MoOX layer that is the origin of the upward band bending in the InP (causing hole accumulation) and also causes downward band bending in the MoOX (creating a hole extraction barrier) (see Supplementary Figure 5 and Supplementary Notes 2 and 4). This observation is different from other semiconductor interfaces where MoOX has been shown to essentially act as a high work function metal (5.75−6.70 eV) which establishes a selective hole contact9.

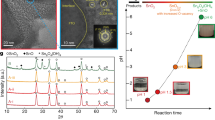

The role of hydrogen fluoride etching

To understand this enhancement in VOC better and isolate the influence of surface recombination in the p-type nanowire region (traditionally part of contact recombination) on the improved contact selectivity,61 we also studied nanowire devices that have only been exposed to HF, that is without the subsequent MoOX evaporation. Nanowires are especially prone to surface recombination which can directly reduce the sustained carrier concentration under illumination and hence the VOC. HF serves as a benchmark surface passivation treatment for InP, because of its ability to completely remove the native oxide62, and therefore the HF-only treatment and rapid subsequent characterization (less than 1 min exposure to air) can be used to investigate the effect of surface passivation without the presence of the MoOX chemical gate. Figure 2c shows that HF treatment did indeed lead to a small and consistent increase in VOC for all devices. The I−V curve of one representative device is shown in Fig. 3a. However, unlike the case of MoOX surface deposition, HF treatment did not remove the large variation in starting VOC value, suggesting that it only passivates the surface and does not improve the carrier selectivity (or only slightly). Figure 3b shows the effect of the native oxide more clearly; immediately after HF etching (less than 1 min exposure to air) the VOC improves, but over time in ambient air it decreases again due to reoxidation. Most of the surface passivation effect is lost even after only 30 min and by 20 h the VOC has returned to its original value. The HF treatment in Fig. 3 therefore has a clearly distinct effect on the nanowires compared to the MoOX + HF treatment in Fig. 2. It increases the VOC by smaller values and it does not remove the initially large spread in VOC even though the wires have been exposed to the ambient for a shorter time (about 1 min) than for the MoOX + HF treatment (about 10 min) (see Methods). These results coupled with the initially highly inhomogeneous PL between and within nanowires (see Supplementary Figure 1 and Supplementary Note 1) suggest that changes in carrier concentration, rather than surface passivation, explain the large improvements caused by the MoOX surface layer deposition. Nonetheless, there is still the possibility that the initial surface passivation varies from wire to wire and even along individual wires, causing all the observed effects. However, our results for devices for which MoOX surface layers were deposited on the n-type side of the solar cells showed a strongly decreased performance (Supplementary Figure 2a). Together with our results in Fig. 2 and the increased conductivity for MoOX pads located on the center of symmetrically doped p-i-p wires (Supplementary Figure 2b) we show that surface gating, rather than simple surface passivation, is primarily responsible for the large increases in VOC and uniformity seen with MoOX deposition.

Effect of HF etching on the VOC. a I−V curve before (dashed line) and after (solid line) HF etching. b The I−V curves of a second sample show the effect of the native oxide regrowth. After the initial increase in performance (yellow), the native oxide slowly grows back (cyan, red, black), reducing the VOC. The vertical dashed lines are guides for the eye

Discussion

We have demonstrated a contact geometry where surface layers traditionally used as heterojunctions can be placed next to, instead of underneath, the metal contact to improve carrier selectivity in nanowire solar cells. The high surface sensitivity in nanowires allows MoOX surface layers to act as a local permanent gate, leading to a p++-type accumulation layer in the underlying InP nanowire and hence increasing the effective doping concentration, which is the mechanism for the increased contact selectivity and VOC. Devices with MoOX underneath instead of next to the contact lead to large charge carrier extraction barriers, proving that the VOC improvements we observe can be ascribed to increased carrier concentration inside the semiconductor, induced by the high work function of the adjacent MoOX, instead of carrier-selective conduction inside the MoOX itself. Our control experiments also show that surface passivation cannot explain the improved performance we observe.

Our results vividly demonstrate an exciting possibility in nanowire solar cells that does not exist in standard bulk or thin-film geometries: an interfacial layer can be used to improve charge carrier selectivity without the requirement of charge carrier extraction; interfaces free of charge carrier extraction barriers and high conductivity in the heterojunction contact material are not required. This removes the traditional tradeoff between wanting thicker heterojunction layers for better carrier selectivity or contact passivation and wanting thinner heterojunction layers for better carrier extraction. One area where this is particularly relevant is for the emerging class of passivating tunnel contacts7,8,63,64. Here an insulating layer is covered by a high or low work function material to provide both carrier selectivity and passivation. Because carriers must tunnel through the insulating layer, its thickness is limited to about 2 nm, setting very challenging requirements on deposition uniformity, control and interfacial quality and removing the possibility of using thick field-effect passivation layers that have proven so valuable in high-efficiency crystalline silicon solar cells. Nanowire surface gating contacts, especially in wrap-around geometries, open the possibility of using any surface passivation scheme also at the contact. It is important to note that such a scheme can improve carrier selectivity and device uniformity dramatically, especially if accurate control over the doping density and profile is challenging, as shown here and often observed for nanoscale systems.

Methods

Sample fabrication

As described previously51, the nanowires are grown at a low pressure in an Aixtron 200/4 metalorganic vapor phase epitaxy (MOVPE) reactor via selective area MOVPE (SA-MOVPE) growth. To define the selective growth areas, a 50-nm-thick silicon nitride layer is used as masking layer. The nitride layer is patterned by soft contact nanoimprint lithography. The underlying substrate is a (111)A oriented p-doped InP wafer with a nominal Zn doping carrier concentration of 2×1018 cm−3 from AXT, USA65,66. H2 is used as carrier gas for the precursors, with a total flow of 15 L min−1. The growth is performed at a temperature of 730 °C and a pressure of 100 mbar. The precursor gases are trimethylindium (TMI) and phosphine (PH3) with molar fractions xi (TMI) = 4.7×10−5 and xi (PH3) = 3.9×10−3, resulting in a V/III ratio of 83. The total growth time is 11 min and the nominal doping profile is p++/p/i/n/n++, with the respective segment growth times of 0.5 min/3 min/4 min/3 min/0.5 min (1 µm/3 μm/4 µm/3 µm/1 µm). The p-type dopant is diethylzinc (DEZn), with molar fractions of 1.3×10−5 in the p++-region and 6.4×10−6 in the p-region. The n-type dopant is ditertbutylsilane (DTBSi), with molar fractions of 9.5×10−6 in the n++-region and 4.9×10−7 in the n-region, respectively. After the growth of the 200 nm diameter wires (±10 nm), a conformal 50-nm-thick SiO2 shell is grown at 300 °C by plasma-enhanced chemical vapor deposition, with the precursors silane and nitrous oxide. The nanowire had a total diameter of 300 nm, a length of 12 µm and SiO2 shell thickness of 50 nm. The InP nanowires form the wurtzite crystal structure, compared to the zincblende crystal structure of bulk wafers. The SA-MOVPE method allows selective semiconductor growth on exposed substrate areas56,57. To grow nanowire structures, as done in this work, the growth has to be selective for the top [111]A surface over the {110} side surfaces. For 730 °C and a pitch smaller than 1000 nm we observed negligible growth on the side facets when studied in a TEM. We note that to our knowledge, a detailed theoretical description of the growth mechanism depending on pitch, nanowire diameter, length, dopants and other parameters is currently lacking. Importantly, our results indicate the absence of any pronounced effect of a possible core-shell structure. The nanowires show rectifying photovoltaic behavior as expected for an p-i-n structure when contacted with the positive pole on the p-type side and the negative one on the n-type side. Under illumination, the holes (electrons) are driven towards the p-type (n-type) side, resulting in a negative photocurrent (e.g. Figure 2). Furthermore, hydrogen fluoride (HF) not only etches the native oxide but also InP itself. Therefore, even if a thin (1 to 2 nm) shell exists initially, the HF treatment for the HF-only and the HF + MoOX + Au treatment is likely to remove this shell. Additionally, the HF treatment is the same for the HF-only and the HF + MoOX + Au treatment. Therefore, the effect of the MoOX is still clearly distinct over the HF treatment alone. Last but not least, the results of our photoluminescence measurements (Supplementary Figure 1), the application of MoOX on the n-type part of p-i-n wires (Supplementary Figure 2a) and symmetric p+-p-p+ wires (Supplementary Figure 2b) are consistent with the assumption of an axial doping geometry, too.

Electrode pads and contacting procedure

After plasma cleaning the glass substrates, UV lithography and metal evaporation are used to fabricate the Au electrodes with alignment markers. Then, the nanowires are randomly dropcast on the substrates by transferring them from the arrays with an area of 200 × 200 µm2 via a pipette in ethanol onto the substrates. To contact the single nanowires to the Au electrodes, electron beam lithography and metal evaporation are used. To allow good Ohmic contact and prevent extraction barriers, the exact placement of the contact on the highly doped nanowire end segments is a crucial step.

The metals used to contact the single nanowires are Ti (200 nm) and Au (30 nm) for the electron contact (on the n−− doped part) and Cr (3 nm), Zn (15 nm), Au (215 nm) for the hole contact (on the p++-doped part). Before metal evaporation, the protective 50 nm SiO2 shell and the native oxide of the InP are removed by etching the exposed and developed substrates in buffered HF (1:7, HF (49%):NH4F (40%)) for 10. The removal of the native oxide is a crucial step, as the latter can cause Fermi level pinning under the conduction band and hence create extraction barriers for the hole contact67. The freshly HF-etched samples are transferred rapidly into the evaporation chamber to minimize the regrowth of the native oxide as much as possible. To diffuse Zn into the p-type InP nanowire and create a highly p-doped layer, an additional annealing step at high temperatures has been reported before68. However, we found this treatment to be damaging to our nanowires as was indicated by a strong decrease in photoluminescence efficiency. Therefore we omit this step, as the in situ doping of our nanowires and the HF etching allow to form Ohmic contacts even without annealing. Nevertheless, we evaporate Zn for the hole contact to prevent possible diffusion of Zn from the nanowire into the contact metal at elevated temperatures during the evaporation and lift-off steps. To form the electron contact, Ti and Au are evaporated with an electron beam evaporator at a pressure of 10−6 mbar at an evaporation rate of 0.3 to 2 Å s−1 and acceleration voltage of 10 keV. For the hole contact Cr, Zn, and Au are evaporated with a thermal evaporator at 2×10−6 mbar at a rate of 0.2 to 1.5 Å s−1. To fabricate the resist windows, a third electron beam lithography step is added.

Solar simulator measurements

The I−V traces are measured by illuminating the samples via a solar simulator (Oriel SOL2 94062A (6 × 6) Class ABA, Newport) with the AM1.5G spectrum at 1 sun (100 mW cm−2) intensity. The temperature of substrates is ca. 50 °C and a silicon reference cell is used to adjust the lamp intensity of the solar simulator. Electrical probes connected to a source-measure unit (Agilent B2910) are used to contact the contact pads on the glass substrate. While measuring the current, the voltage is scanned between −1 V and 1 V in 2001 steps.

HF etching and MoOX evaporation

The exposed nanowire parts were etched for 10 s in buffered HF (1:7, HF (49%):NH4F (40%)) to remove the protective SiO2 shell (50 nm) and the native oxide of the InP under the contact. Afterwards they were immediately characterized (1 min). For the MoOX treatment, first the HF etching has been repeated after which the samples have been loaded into a thermal evaporator as quickly as possible (10 min air exposure after etching). MoOX (MoO3, 99.97% trace metal basis, purchased from Sigma Aldrich) was thermally evaporated from an Mo boat at a rate of around 0.3 to 1 Å s−1 and a pressure of 2×10−6 mbar. The target thickness was 15 nm; however, after a short but very high spike in the evaporation rate, the final thickness was about 20 nm.

We note that the time between HF treatment and characterization was less than 1 min for the samples that have only been exposed to HF, while the time between HF treatment and pumping down for the case of additional MoOX deposition was about 10 min. This difference originates from practical constraints: HF treatment to test surface passivation was done for a single chip at a time in an adjacent lab, while in the case of MoOX deposition the etching/rinsing/drying was done in a serial manner for ten chips, which were then all carried to another part of the building, attached to a sample holder and loaded into the prepared vacuum chamber (10 min).

Data availability

All relevant data are available from the authors upon request.

Change history

03 September 2018

This Article was originally published without the accompanying Peer Review File. This file is now available in the HTML version of the Article; the PDF was correct from the time of publication.

References

Wuerfel, P. & Wuerfel, U. Physics of Solar Cells: From Basic Principles to Advanced Concepts (Wiley-VCH, Weinheim, Germany, 2016).

Brendel, R. & Peibst, R. Contact selectivity and efficiency in crystalline silicon photovoltaics. IEEE J. Photovolt. 6, 1413–1420 (2016).

Bullock, J. et al. Efficient silicon solar cells with dopant-free asymmetric heterocontacts. Nat. Energy 1, 15031 (2016).

Geissbühler, J. et al. 22.5% efficient silicon heterojunction solar cell with molybdenum oxide hole collector. Appl. Phys. Lett. 107, 081601 (2015).

Wan, Y. et al. Magnesium fluoride electron-selective contacts for crystalline silicon solar cells. ACS Appl. Mater. Interfaces 8, 14671–14677 (2016).

Cuevas, A. et al. Skin care for healthy silicon solar cells. In Proceedings of the 42nd IEEE Photovoltaic Specialist Conference (PVSC), New Orleans, LA, USA 1–6 (2015).

Feldmann, F., Bivour, M., Reichel, C., Hermle, M. & Glunz, S. W. A passivated rear contact for high-efficiency n-type silicon solar cells enabling high Vocs and FF>82%. In Proceedings of the 28th European Photovoltaic Solar Energy Conference and Exhibition (EU PVSEC), Paris, France, 988–992 (2013).

Glunz, S. W. et al. the Irresistible charm of a simple current flow pattern – 25% with a solar cell featuring a full-area back contact. In Proceedings of the 31st EU PVSEC Hamburg, Germany, 259–263 (2015).

Battaglia, C. et al. Hole selective MoO x contact for silicon solar cells. Nano Lett. 14, 967–971 (2014).

Battaglia, C. et al. Silicon heterojunction solar cell with passivated hole selective MoO x contact. Appl. Phys. Lett. 104, 113902 (2014).

Yin, X. et al. 19.2% Efficient InP Heterojunction Solar Cell with Electron-Selective TiO 2 Contact. ACS Photonics 1, 1245–1250 (2014).

Kayes, B. M. et al. 27.6% conversion efficiency, a new record for single-junction solar cells under 1 sun illumination. In Proceedings of the 37th IEEE 2011 Photovoltaic Specialists Conference (PVSC), Seattle, WA, USA, 4–8 (2011).

Tress, W., Leo, K. & Riede, M. Optimum mobility, contact properties, and open-circuit voltage of organic solar cells: A drift-diffusion simulation study. Phys. Rev. B 85, 1–11 (2012).

Yin, Z., Wei, J. & Zheng, Q. Interfacial materials for organic solar cells: recent advances and perspectives. Adv. Sci. 3, 1–37 (2016).

Zhang, Y. et al. Charge selective contacts, mobile ions and anomalous hysteresis in organic–inorganic perovskite solar cells. Mater. Horiz. 1, 96 (2015).

Gottesman, R. et al. Dynamic phenomena at perovskite/electron-selective contact interface as interpreted from photovoltage decays. Chem 1, 776–789 (2016).

Fakharuddin, A., Schmidt-Mende, L., Garcia-Belmonte, G., Jose, R. & Mora-Sero, I. Interfaces in perovskite solar cells. Adv. Energy Mater. 7, 1700623 (2017).

Kegelmann, L. et al. It takes two to tango—double-layer selective contacts in perovskite solar cells for improved device performance and reduced hysteresis. ACS Appl. Mater. Interfaces 9, 17245–17255 (2017).

Holman, Z. C. et al. Current losses at the front of silion heterojunction solar cells. IEEE J. Photovolt. 2, 7–15 (2012).

Green, M. A. et al. Solar cell efficiency tables (version 50). Prog. Photovolt. Res. Appl. 25, 668–676 (2017).

Yoshikawa, K. et al. Silicon heterojunction solar cell with interdigitated back contacts for a photoconversion efficiency over 26%. Nat. Energy 2, 17032 (2017).

Taguchi, M. et al. 24.7% Record efficiency HIT solar cell on thin silicon wafer. IEEE J. Photovolt. 4, 96–99 (2014).

Tiedje, T. O. M., Yablonovitch, E. L. I., Cody, G. D. G. D. & Brooks, B. G. B. G. B. G. Limiting efficiency of silicon. IEEE Trans. Electron Devices 31, 711–716 (1984).

Mueller, T., Wong, J. & Aberle, A. G. Heterojunction silicon wafer solar cells using amorphous silicon suboxides for interface passivation. Energy Procedia 15, 97–106 (2012).

Deligiannis, D. et al. Understanding the thickness-dependent effective lifetime of crystalline silicon passivated with a thin layer of intrinsic hydrogenated amorphous silicon using a nanometer-accurate wet-etching method. J. Appl. Phys. 119, 235307 (2016).

Tang, J., Huo, Z., Brittman, S., Gao, H. & Yang, P. Solution-processed core-shell nanowires for efficient photovoltaic cells. Nat. Nanotechnol. 6, 568–572 (2011).

Briseno, A. L. et al. Oligo- and polythiophene/ZnO hybrid nanowire solar cells. Nano Lett. 10, 334–340 (2010).

Li, F. et al. Ultrahigh mobility of p-type CdS nanowires: surface charge transfer doping and photovoltaic devices. Adv. Energy Mater. 3, 579–583 (2013).

Jeong, S. et al. Hybrid silicon nanocone-polymer solar cells. Nano Lett. 12, 2971–2976 (2012).

Zhang, Y. et al. High efficiency hybrid PEDOT:PSS/nanostructured silicon Schottky junction solar cells by doping-free rear contact. Energy Environ. Sci. 8, 297–302 (2015).

Storm, K., Nylund, G., Samuelson, L. & Micolich, A. P. Realizing lateral wrap-gated nanowire FETs: controlling gate length with chemistry rather than lithography. Nano Lett. 12, 1–6 (2012).

Thelander, C. et al. Nanowire-based one-dimensional electronics. Mater. Today 9, 28–35 (2006).

Nylund, G. et al. Transparently wrap-gated semiconductor nanowire arrays for studies of gate-controlled photoluminescence. AIP Conf. Proc. 1566, 427–428 (2013).

Burke, A. M. et al. InAs nanowire transistors with multiple, independent wrap-gate segments. Nano Lett. 15, 2836–2843 (2015).

Mirza, M. M. et al. One dimensional transport in silicon nanowire junction-less field effect transistors. Sci. Rep. 7, 1–8 (2017).

Shen, L. F. et al. High-performance wrap-gated InGaAs nanowire field-effect transistors with sputtered dielectrics. Sci. Rep. 5, 1–9 (2015).

Fang, H. et al. Degenerate n-doping of few-layer transition metal dichalcogenides by potassium. Nano Lett. 13, 1991–1995 (2013).

Kiriya, D., Tosun, M., Zhao, P., Kang, J. S. & Javey, A. Air-stable surface charge transfer doping of MoS2 by benzyl viologen. J. Am. Chem. Soc. 136, 7853–7856 (2014).

Xia, F. et al. Surface charge transfer doping via transition metal oxides for efficient p-type doping of II-VI nanostructures. ACS Nano 10, 10283–10293 (2016).

Zhang, X., Shao, Z., Zhang, X., He, Y. & Jie, J. Surface charge transfer doping of low-dimensional nanostructures toward high-performance nanodevices. Adv. Mater. 28, 10409–10442 (2016).

Shao, Z. et al. MoO3 nanodots decorated CdS nanoribbons for high-performance, homojunction photovoltaic devices on flexible substrates. Nano Lett. 15, 3590–3596 (2015).

Borgström, M. T. et al. Nanowires with promise for photovoltaics. IEEE J. Sel. Top. Quantum Electron. 17, 1050–1061 (2011).

Logan, R. A., Chu, S. N. G., Geva, M., Ha, N. T. & Thurmond, C. D. Zinc incorporation into InP grown by atmospheric pressure metalorganic vapor phase epitaxy. J. Appl. Phys. 79, 1371–1377 (1996).

Chu, S. N. G., Logan, R. A., Geva, M. & Ha, N. T. Concentration dependent ZN diffusion in InP during metalorganic vapor phase epitaxy. J. Appl. Phys. 78, 3001–3007 (1995).

Chu, S. N. G., Logan, R. A., Geva, M., Ha, N. T. & Karlicek, R. F. Substitutional, interstitial, and neutral zinc incorporation into InP grown by atmospheric pressure metalorganic vapor phase epitaxy. J. Appl. Phys. 80, 3221–3227 (1996).

Zhang, W. et al. Recombination dynamics in aerotaxy-grown Zn-doped GaAs nanowires. Nanotechnology 27, 455704 (2016).

Wallentin, J. & Borgström, M. T. Doping of semiconductor nanowires. J. Mater. Res. 26, 2142–2156 (2011).

Wallentin, J. et al. Degenerate p-doping of InP nanowires for large area tunnel diodes. Appl. Phys. Lett. 99, 253105 (2011).

Young, D. L. et al. Carrier selective, passivated contacts for high efficiency silicon solar cells based on transparent conducting oxides. Energy Procedia 55, 733–740 (2014).

Zhong, Z. et al. Efficiency enhancement of axial junction InP single nanowire solar cells by dielectric coating. Nano Energy 28, 106–114 (2016).

Mann, S. A. et al. Quantifying losses and thermodynamic limits in nanophotonic solar cells. Nat. Nanotechnol. 11, 1071–1075 (2016).

Cui, Y. et al. Boosting solar cell photovoltage via nanophotonic engineering. Nano Lett. 16, 6467–6471 (2016).

Wallentin, J. et al. InP nanowire array solar cells achieving 13.8% efficiency by exceeding the ray optics limit. Science 339, 1057–1060 (2013).

Green, M. A. et al. Solar cell efficiency tables (version 51). Prog. Photovolt. Res. Appl. 26, 3–12 (2018).

Black, L. E. et al. Effective surface passivation of InP nanowires by atomic-layer-deposited Al2O3 with POX Interlayer. Nano Lett. 17, 6287–6294 (2017).

Gao, Q. et al. Selective area epitaxial growth of InP nanowire array for solar cell applications. In Proceedings of 2014 Conference on Optoelectronic and Microelectronic Materials & Devices (COMMAD), 252–253 (2014).

Gao, Q. et al. Simultaneous selective-area and vapor–liquid–solid growth of InP nanowire arrays. Nano Lett. 16, 4361–4367 (2016).

Sinton, R. A. & Cuevas, A. Contactless determination of current–voltage characteristics and minority-carrier lifetimes in semiconductors from quasi-steady-state photoconductance data. Appl. Phys. Lett. 69, 2510 (1996).

Cuevas, A. & Sinton, R. A. Prediction of the open-circuit voltage of solar cells from the steady-state photoconductance. Prog. Photovolt. Res. Appl. 5, 79–90 (1997).

Jackson, H. E. et al. Probing the valence band structure of wurtzite InP nanowires by photoluminescence excitation spectroscopy. AIP Conf. Proc. 1399, 481–482 (2011).

Ellis, T. R., Egelhofer, K. E. & Lonergan, M. C. (2018) Limits of Contact Selectivity/Recombination on the Open-Circuit Voltage of a Photovoltaic. ACS Appl. Energy Mater. 1, 1037-1046 (2018)

Pluchery, O., Chabal, Y. J. & Opila, R. L. Wet chemical cleaning of InP surfaces investigated by in situ and ex situ infrared spectroscopy. J. Appl. Phys. 94, 2707–2715 (2003).

Wolf, S. De, Descoeudres, A., Holman, Z. C. & Ballif, C. High-efficiency silicon heterojunction solar cells: a review. Green 2, 7–24 (2012).

Oener, S. Z. et al. Metal–insulator–semiconductor nanowire network solar cells. Nano Lett. 16, 3689–3695 (2016).

Mårtensson, T. et al. Nanowire arrays defined by nanoimprint lithography. Nano Lett. 4, 699–702 (2004).

Pierret, A. et al. Generic nano-imprint process for fabrication of nanowire arrays. Nanotechnology 21, 065305 (2010).

van Weert, M. H. M. et al. Large redshift in photoluminescence of p-doped InP nanowires induced by Fermi-level pinning. Appl. Phys. Lett. 88, 043109 (2006).

Nowzari, A. et al. A comparative study of absorption in vertically and laterally oriented InP core–shell nanowire photovoltaic devices. Nano Lett. 15, 1809–1814 (2015).

Acknowledgements

The work at AMOLF is funded by the “Nederlandse Organisatie voor Wetenschappelijk Onderzoek” (NWO) by the NWO VIDI grant (project number 14846) and by the European Research Council (Grant Agreement No. 337328).

Author information

Authors and Affiliations

Contributions

S.Z.O. and E.C.G. developed the concept and designed the experiment. S.Z.O. and H.S. performed the device fabrication and characterization under the supervision of E.C.G. A.C. grew the nanowires under the supervision of J.E.M.H. and E.P.A.M.B. S.Z.O. and E.C.G. wrote the manuscript with contributions from all authors.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Electronic supplementary material

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article’s Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article’s Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Oener, S.Z., Cavalli, A., Sun, H. et al. Charge carrier-selective contacts for nanowire solar cells. Nat Commun 9, 3248 (2018). https://doi.org/10.1038/s41467-018-05453-5

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/s41467-018-05453-5

This article is cited by

-

Electron and hole relaxation effect on power conversion efficiency of selective energy contacts solar cells

Optical and Quantum Electronics (2023)

-

Photoelectrochemical technology for solar fuel generation, from single photoelectrodes to unassisted cells: a review

Environmental Chemistry Letters (2022)

-

Hot carrier photovoltaics in van der Waals heterostructures

Nature Reviews Physics (2021)

-

Imaging the influence of oxides on the electrostatic potential of photovoltaic InP nanowires

Nano Research (2021)

-

Nanoscale semiconductor/catalyst interfaces in photoelectrochemistry

Nature Materials (2020)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.