## ARTICLE

### Open Access

# A tactile sensor system with sensory neurons and a perceptual synaptic network based on semivolatile carbon nanotube transistors

Sungho Kim<sup>1</sup>, Yongwoo Lee<sup>2</sup>, Hee-Dong Kim<sup>1</sup> and Sung-Jin Choi<sup>6</sup>

#### Abstract

The human sensory system has a fascinating stimulus-detection capability attributed to the fact that the feature (pattern) of an input stimulus can be extracted through perceptual learning. Therefore, sensory information can be organized and identified efficiently based on iterative experiences, whereby the sensing ability is improved. Specifically, the distributed network of receptors, neurons, and synapses in the somatosensory system efficiently processes complex tactile information. Herein, we demonstrate an artificial tactile sensor system with a sensory neuron and a perceptual synaptic network composed of a single device: a semivolatile carbon nanotube transistor. The system can differentiate the temporal features of tactile patterns, and its recognition accuracy can be improved by an iterative learning process. Furthermore, the developed circuit model of the system provides quantitative analytical and product-level feasibility. This work is a step toward the design and use of a neuromorphic sensory system with a learning capability for potential applications in robotics and prosthetics.

#### Introduction

Over the past half-century, device electronics have been successfully advancing the Information Age thanks to consistent performance improvements based on the downscaling of digital devices that can provide reliable logic-gate operations, thus benefiting from their robustness to high levels of noise. Recently, research paradigms have shifted the focus to conventional devices with analog characteristics, which were previously considered a drawback. With an innovative computing architecture used to overcome the energy inefficiency of the conventional von Neumann architecture-typically referred to as a neuromorphic system<sup>1</sup>—the analog behaviors of these devices have begun to be rehighlighted as essential features for the implementation of neuromorphic systems<sup>2</sup>. Given that the numberless internal states of an analog device can be adjusted with minimal energy consumption

Correspondence: Sung-Jin Choi (sjchoiee@kookmin.ac.kr)

<sup>1</sup>Department of Electrical Engineering and Convergence Engineering for Intelligent Drone, Sejong University, Seoul 05006, Korea <sup>2</sup>School of Electrical Engineering, Kookmin University, Seoul 02707, Korea and given that they can be maintained over the long term (i.e., they are nonvolatile)<sup>3</sup>, analog devices can store more data in a single device with better energy efficiency than digital devices. Specifically, recent advances in these analog devices allow them to emulate the functionality of biological synapses and neurons, while the ability of their crossbar arrays to solve cognitive tasks related to learning and recognition has been demonstrated experimentally<sup>4–8</sup>. A neuromorphic system will provide energy-efficient computing power for artificial intelligence that can replicate cognitive function up to the human brain level.

Interestingly, some analog devices exhibit volatile behaviors for input stimuli; i.e., they yield a temporal state enhancement that quickly decays to its initial state, which constitutes one of the essential characteristics of a neuromorphic system. Early research on this volatile behavior focused on the emulation of short-term plasticity (STP) in biological synapses, such as paired-pulse facilitation (PPF)<sup>9,10</sup>. Moreover, recent studies have emulated biological neurons, including their capability to integrate temporal input stimuli<sup>11,12</sup> based on the leaky integrate-and-fire (I&F) neuron

© The Author(s) 2020

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

model<sup>13</sup>. By exploiting the response of the volatile device depending on the frequency of the input stimuli, the spatial or temporal patterns in the input stimuli can be classified. For example, the integration of sensor devices for various external stimuli (e.g., pressure, tactile, or visual stimuli) with processing components (i.e., a volatile analog device as a sensory neuron) has been proposed to capture the similarities of the human sensory perception system<sup>14–19</sup>.

Notably, unlike the volatile or nonvolatile analog devices mentioned above, a specific device can achieve switchable volatile/nonvolatile behaviors, as desired<sup>20,21</sup>. Although this is not a generic term, we will refer to it as a "semivolatile" characteristic (in fact, in the case of a twoterminal-based analog device (memristor), a device with semivolatile behavior has been referred to as a secondorder memristor<sup>22,23</sup>). Previous studies of semivolatile behavior focused only on the capture of a psychological model related to the human brain's processes of memorizing and forgetting (i.e., the transition from short-term memory to long-term learning)<sup>20,21</sup>. However, more attention should be paid to the potential of a semivolatile device to simulate both synaptic and neuronal functions simultaneously, i.e., the processes of leaky integration (in the neuron) and learning/recognition (in the synaptic network) of input stimuli and their emulation with a single type of device. To date<sup>24</sup>, neuromorphic systems have been implemented with an artificial neural network based on the integration of two different types of devices (for neuronal and synaptic devices). If the entire artificial neural network with neuronal/synaptic devices can be implemented with a single device type, a simpler fabrication process for high-density integration will be achieved. Consequently, the goal of achieving large-scale and on-chip implementation of neuromorphic systems can be realized much sooner than expected.

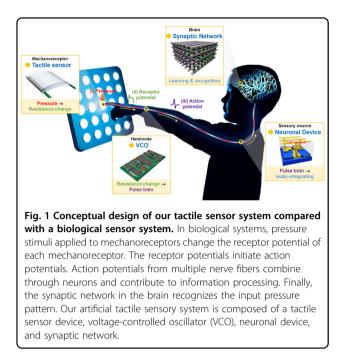

In this paper, we demonstrate a biorealistic tactile sensor system wherein both the sensory neurons and perceptual synaptic network are implemented by a semivolatile carbon nanotube (CNT) transistor. The semivolatile transistor can switch the operation mode according to the bias condition. In this way, a single device type is allowed to play two different roles (neuronal and synaptic functions) simultaneously. In our tactile sensor system (Fig. 1), the sensing receptor, action potential in the axon, sensory neuron that processes information, and synaptic network for perception learning are emulated by a tactile sensor, a voltage-controlled oscillator (VCO) circuit, one neuronal CNT transistor, and the synaptic CNT transistor array, respectively. The tactile sensor converts pressure stimuli into resistance changes. These are then converted to digital signals and modulated such that their frequencies vary with the pressure intensity based on the use of the VCO. Subsequently, the output of the VCO is delivered to the neuronal CNT transistor that operates in volatile mode. A leaky-integrating output corresponding to the frequency of the VCO output is then generated. Finally, the sampled output of the neuronal CNT transistor is fed to the network of synaptic CNT transistors that operate in a nonvolatile mode, and the learning/recognition processes for distinguishing the input stimuli pattern are conducted in a supervised learning manner.

#### Materials and methods

#### Fabrication of the tactile sensor

A flexible and transparent polydimethylsiloxane (PDMS) substrate (thickness of 1 mm) was prepared by mixing PDMS prepolymer (Sylgard 184A, Dow Corning) and a curing agent at a ratio of 10:1 by weight. Subsequently, the substrate was cleaned by oxygen plasma treatment, functionalized with a poly-L-lysine solution  $(0.1\% \text{ w/v in } H_2O$ , Sigma-Aldrich), and acted as an effective adhesion layer for the CNTs. The substrate was thoroughly rinsed with deionized (DI) water and dried with flowing nitrogen gas. Subsequently, the 99% metallic CNT network film was directly formed on the PDMS substrate by spray coating the preseparated metallic CNT solution (concentration of 0.01 mg/mL) on a hot plate (at 100 °C) followed by thorough rinsing with isopropanol and DI water. Two Cu electrodes were then formed at both ends of the CNT network film with silver paste for reading and inducing electrical signals. Subsequently, a top PDMS layer was cast with liquid PDMS with a thermal curing agent onto the CNT network film to fabricate a sandwich-like structure. In the final step, all the layers were annealed at 100 °C for 1 h.

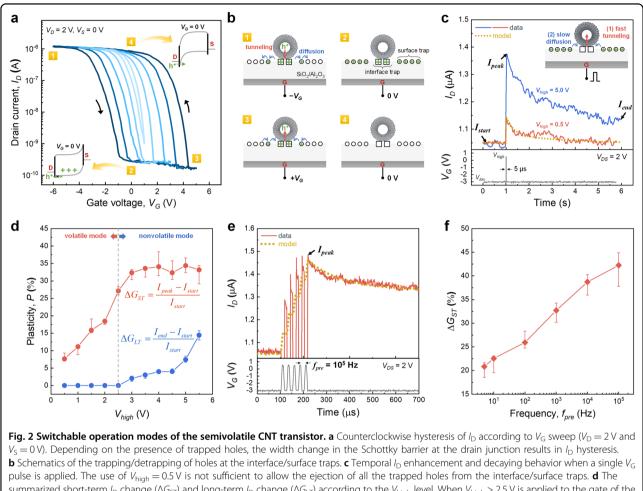

summarized short-term  $I_D$  change ( $\Delta G_{ST}$ ) and long-term  $I_D$  change ( $\Delta G_{LT}$ ) according to the  $V_{high}$  level. When  $V_{high} > 2.5$  V is applied to the gate of the CNT transistor operates in a nonvolatile mode. Moreover, when  $V_{high} < 2.5$  V is applied, the CNT transistor operates in volatile mode. **e** Cumulative  $I_D$  enhancement behavior based on the application of a train of pulses. Because the CNT transistor operates in volatile mode ( $V_{high} = 0.5$  V), the final current level ( $I_{end}$ ) decays to the initial level ( $I_{start}$ ) again (these data are not shown in this graph). **f** Variation in  $\Delta G_{ST}$  as a function of  $f_{pre}$  enables the differentiation of the pressure intensity.

#### Fabrication of the semivolatile CNT transistor array

CNT transistors were fabricated on p-doped rigid silicon substrates with a thermally grown SiO<sub>2</sub> layer with a thickness of 50 nm. We used the local back-gate structure for the modulation of the channels in the CNT transistors. To form the local back-gate, a Ti layer with a thickness of 20 nm was deposited by e-beam evaporation and patterned by a subsequent lift-off process. Subsequently, an  $Al_2O_3$  layer (thickness of 40 nm) and a SiO<sub>2</sub> layer (thickness of 10 nm) were deposited sequentially to form a gate insulator by atomic layer deposition. The top surface of the SiO<sub>2</sub> layer was then functionalized with a 0.1 g/mLpoly-L-lysine solution for 20 min to form an amineterminated layer, which acted as an effective adhesion layer for the deposition of the CNTs. The CNT network channel was then formed by immersing the chip into a 0.01 mg/mL 99% semiconducting CNT solution (NanoIntegris, Inc.) for 8 min at an elevated temperature of 100 °C. The source/drain electrodes that consisted of Ti and Pd layers (each 2 nm and 30 nm, respectively) were then deposited and patterned using conventional thermal evaporation and a lift-off process, respectively. Finally, additional photolithography and oxygen plasma etching steps were conducted to remove unnecessary CNTs other than those in the channel area, thus isolating the devices from one another.

In the case of the crossbar array, Cu (thickness of 80 nm) and  $SiO_x$  (thickness of 150 nm) were sequentially deposited and patterned for the metal line and interlayer dielectric layer (ILD), respectively.

#### **Results and discussion**

The operational principle of our semivolatile CNT transistor is based on different hole-movement mechanisms in the traps (i.e., interface and surface traps). It has been shown in other studies<sup>25</sup> that typical CNT transistors have a drain current  $(I_D)$  hysteresis that is related to the gate voltage  $(V_G)$  sweep (Fig. 2a). The hysteresis is attributed to the trapping/detrapping of holes at (1) the interface trap through the tunneling process and (2) the surface trap through the diffusion process in the lateral direction (see Fig. 2b, Fig. S1, and Supplementary Information Note 1 for a more detailed discussion). Upon the application of negative  $V_{\rm G}$  values, traps are filled by holes. The positively charged traps bend the energy band of the CNT downward, thereby resulting in the suppression of  $I_D$  owing to the enlarged Schottky barrier width at the drain/CNT junction (left inset of Fig. 2a). A positive  $V_{\rm G}$  ejects the trapped holes, and the consequent upward band bending leads to the increase in the  $I_{\rm D}$  owing to the narrowing of the Schottky barrier width (right inset of Fig. 2a). Notably, because the interface trap is adjacent to the CNT channel, the tunneling of holes between them is relatively fast. Conversely, the diffusion of holes between surface traps in the lateral direction is relatively slow. These different hole-movement mechanisms lead to a semivolatile behavior in the CNT transistor. Figure 2c shows one example of a  $I_{\rm D}$  response following the application of a single  $V_{\rm G}$  pulse. The low level of the  $V_{\rm G}$  pulse  $(V_{low} = -3 \text{ V})$  is the undisturbed read voltage for the channel conductance (i.e., -3 V cannot lead to any trapping/detrapping process). Accordingly, the pulse width was minimized to 5 µs to eliminate any time-cumulative effects. Before the onset of the measurements, a negative  $V_{\rm G}$  (-6 V, direct current (DC)) was applied for 1 s to ensure that all the traps were filled by holes at the initial state. When a single  $V_{\rm G}$  pulse was applied, the trapped holes were ejected to the CNT channel. If the high level of the  $V_{\rm G}$  pulse ( $V_{\rm high}$ ) was large enough to cause the ejection of all the trapped holes at the interface and surface traps (given that there are no holes to refill the traps after the pulse is removed), the  $I_{\rm D}$  change, i.e., the nonvolatile mode operation, would be maintained over the long term. By contrast, if  $V_{high}$  is not sufficient to cause the ejection of all the trapped holes (e.g.,  $V_{high} = 0.5$  V, as shown in Fig. 2c),  $I_{\rm D}$  temporarily increases and decays to its initial state subsequently, i.e., the volatile mode operation  $(I_{\text{start}},$  $I_{\text{peak}}$ , and  $I_{\text{end}}$ , denote the initial, peak, and final  $I_{\text{D}}$  levels, respectively). During volatile mode operation, only the holes at the interface trap are ejected by applying the pulse, but most of the holes at the surface trap remain. After the pulse ends, surface traps act as reservoirs of holes and help refill the empty interface traps, which results in the gradual recovery of  $I_{\rm D}$ . Consequently, the level of  $V_{\text{high}}$  determines the operation mode of the semivolatile CNT transistor. Figure 2d shows the summarized channel conductance change (defined as  $\Delta G$ ) according to the level of  $V_{\text{high}}$ . Here, the amount of shortterm enhancement in  $I_{\rm D}$  is defined as  $\Delta G_{\rm ST} = (I_{\rm peak} - I_{\rm start})/$  $I_{\text{start}}$  and the amount of long-term change in  $I_{\text{D}}$  is defined as  $\Delta G_{\rm LT} = (I_{\rm end} - I_{\rm start})/I_{\rm start}$ . Notably,  $\Delta G_{\rm LT}$  is zero until  $V_{\rm high}$  attains a value of 2.5 V, which indicates that there is only a temporary change in the drain current. Moreover,  $\Delta G_{\rm LT}$  gradually increases once  $V_{\rm high}$  exceeds 2.5 V. Therefore, the semivolatile CNT transistor has two switchable operation modes, which can be controlled by adjusting the  $V_{\rm high}$  level.

As mentioned above, the volatile behavior can be exploited to emulate neuronal functions. When a series of pulses (referred to as presynaptic spikes,  $V_{pre}$ ) are applied to the volatile CNT transistor,  $\Delta G_{ST}$  is dependent on the frequency of  $V_{\rm pre}$  ( $f_{\rm pre}$ ). Figure 2e shows one example of the transient  $I_{\rm D}$  behavior when a train of five pulses for which  $f_{\rm pre} = 10^5 \,\text{Hz}$  is applied, and Fig. 2f shows the summarized  $\Delta G_{\rm ST}$  values according to  $f_{\rm pre}$ . As the interval of each pulse becomes shorter (fpre increases), larger cumulative  $I_{\rm D}$  enhancement leads to higher  $I_{\rm peak}$  values. By contrast, as the interval of the pulse train increases, the decaying  $I_{\rm D}$  becomes more dominant, and  $I_{\rm peak}$  is suppressed. Therefore, the volatile CNT transistor can emulate the neuronal leaky-integration function that corresponds to the frequency of the input stimulus. Additionally, the compact circuit model for the volatile CNT transistor is implemented (see also Fig. S2 and Supplementary Information Note 2). Different temporal responses in the tunneling/diffusion processes can be emulated with two resistor-capacitor circuits that have different time constants. As shown in Fig. 2c, e (yellow dotted curves), the circuit model can capture the measured results with high accuracy. This circuit model can be combined with the circuit model for other components in our tactile sensor system, which allows a quantitative analysis of the entire system through the circuit simulation (this concept will be discussed later).

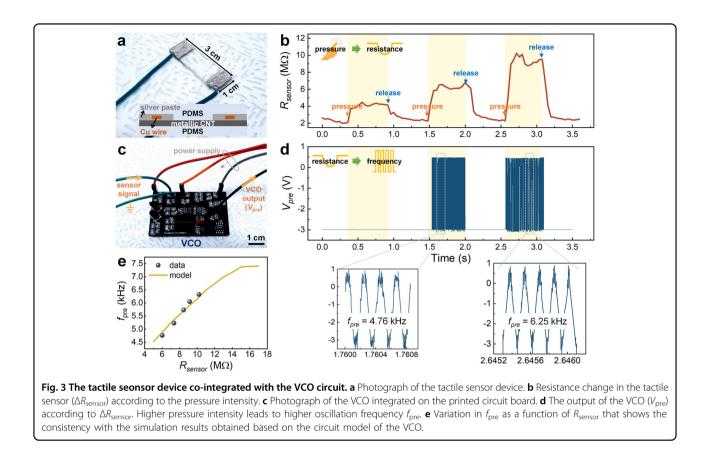

The operations of each component in our tactile sensor system will be discussed in the order of signal flow, wherein all signal flows are manipulated with custommade software (the detailed experimental setup is presented Fig. S3 in Supplementary Information Note 3). First, the pressure stimulus was detected by a previously demonstrated tactile sensor device (Fig. 3a)<sup>26</sup> that was fabricated with the use of the percolated solution that processed 99% of the metallic CNTs owing to their high bendability and material uniformity. The pressure stimulus leads to resistance changes in the tactile sensor  $(\Delta R_{\text{sensor}})$  in the range of 2.5–10 M $\Omega$  (Fig. 3b). The value of  $\Delta R_{\text{sensor}}$  is then converted to the frequency of the presynaptic spike  $(V_{pre})$  by the VCO (Fig. 3c—the detailed design of the VCO is presented Fig. S4 in Supplementary Information Note 4). As the pressure intensity increases,  $V_{\rm pre}$  oscillations are generated at an increasingly higher frequency (Fig. 3d). Consequently,  $f_{\rm pre}$  varies proportionally to the pressure intensity (Fig. 3e). Notably, because the VCO is designed based on a conventional digital

circuit, the signal conversion ( $R_{\text{sensor}}$  versus  $f_{\text{pre}}$ ) can be characterized accurately by circuit simulations (Fig. 3e).

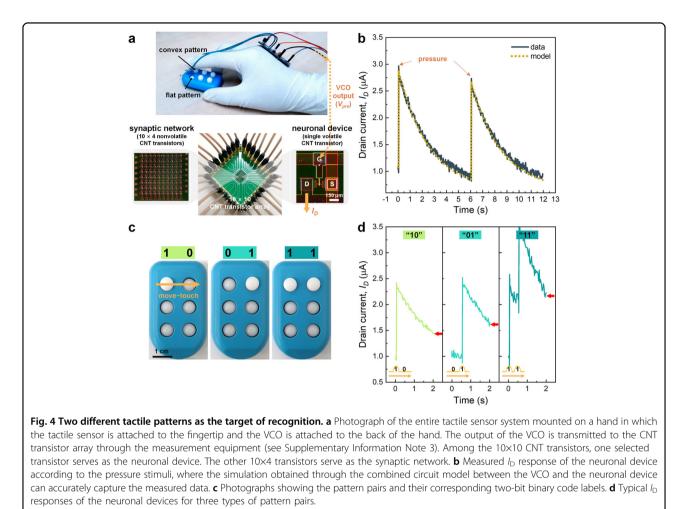

Subsequently, the output of the VCO  $(V_{\text{pre}})$  was delivered to the neuronal device, i.e., to the volatile CNT transistor (Fig. 4a). Among our  $10 \times 10$  CNT transistors<sup>27,28</sup>, one selected CNT transistor served as the neuronal device that operated in volatile mode. The other  $10 \times 4$  CNT transistors acted as a synaptic network that operated in a nonvolatile mode to classify the pattern of input pressure (as discussed in a subsequent part of this section). When the pressure stimulus was detected by the tactile sensor,  $V_{\rm pre}$  was applied to the gate electrode of the neuronal device, and a temporal  $I_{\rm D}$  enhancement and its subsequent decay were observed, as shown in Fig. 4b. Obviously, this transient  $I_{\rm D}$  behavior can be captured accurately through the circuit simulation from the combined VCO model and the volatile CNT transistor model discussed above. Moreover, the neuronal device can integrate temporally correlated tactile stimuli. As a proof of concept, two different tactile patterns in one row (convex or flat) were used as the target of recognition (Fig. 4c), wherein we defined the convex pattern in the pair with the number "1" and the flat pattern with "0". Therefore, the pattern pairs were labeled "'00", "01", "10", and "11". In the experiment, the tactile sensor was attached to a finger, and the finger was brought close to the patterns and was moved from left to right. A complete move/touch action was completed in  $\leq 1$  s. When the tactile sensor passes through the "1" pattern, the pressure stimulus at the sensor causes a temporal increase in  $I_{\rm D}$ . Moreover, the "0" pattern cannot cause any change in  $I_{\rm D}$ . Figure 4d shows the transient  $I_{\rm D}$  responses according to the different tactile patterns. Note that the "11" pattern leads to the largest  $I_{\rm D}$  change because this pattern provides two successive pressure stimuli. Interestingly, although both the "01" and "10" patterns have only one convex pattern, the timing information of the two patterns are different. The response to the "10" pattern decays earlier than the response to the "01" pattern. Therefore, the  $I_D$  value attributed to the "01" pattern is higher than that attributed to the "10" pattern. Because the responses to the pattern pairs are distinguishable, these responses can be used as specific features for recognition.

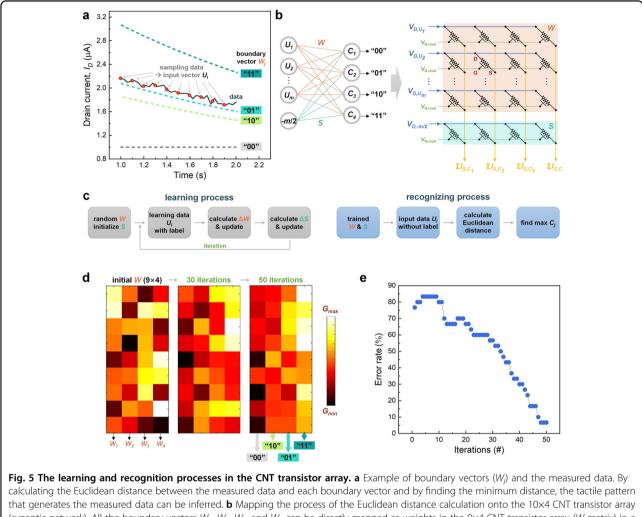

Finally, the biorealistic perceptual learning and recognition processes are demonstrated. In principle, the transient  $I_D$  responses after the completion of the move/ touch action are sampled. For example,  $I_D$  is sampled after a period of 1 s at 0.1 s intervals (i.e.,  $I_D(t_i)$  where i = 1 to m, Fig. 5a). The input vector  $U_i$  is defined as the normalized  $I_D(t_i)$ :  $U_i = I_D(t_i)/I_{ref}$ , where  $0 \le U_i \le 1$ . Next, the boundary vectors ( $W_i$ , where j = 1 to n) are defined as the

references for the classification of  $U_i$ . In our experiment, four boundary vectors, namely,  $W_1$ ,  $W_2$ ,  $W_3$ , and  $W_4$  (n =4), correspond to the tactile patterns of "00", "01", "10", and "11", respectively (the dotted curves in Fig. 5a). Based on the Euclidean distance between  $U_i$  and  $W_j$ , the tactile pattern that corresponds to  $U_i$  can be inferred. Therefore, two processes need to be performed iteratively: (1) the learning process for determining  $W_i$  with the labeled  $U_i$ and (2) the recognition process based on the calculation of the Euclidean distance between  $U_i$  and  $W_j$ . These learning and recognition processes are similar to the knearest neighbors (KNN) algorithm, and they can be performed efficiently with a resistive crossbar array<sup>6</sup>.  $W_i$ can be directly mapped as a set of weights in the nonvolatile CNT transistor array in a columnwise fashion, i.e., to the W matrix ( $W = [W_1 \ W_2 \ W_3 \ W_4]$ ; thus, the size of Wis  $m \times n$ , Fig. 5b). The weights are in turn linearly mapped to the device conductance values. Additionally, to calculate the Euclidean distance, the *S* matrix (of size  $1 \times n$ ) should be included<sup>6</sup>. Thus, an  $(m+1) \times n$  nonvolatile

CNT transistor array (referred to as the synaptic network

wherein m = 9 and n = 4) was exploited in our experiment.

The details of the learning and recognition processes are presented in Fig. S5 in Supplementary Information Note 5. In brief (Fig. 5c), during the learning process, W and Sare iteratively updated according to the designed learning rule. The learning rule was based on a supervised scheme using the label  $U_i$ . By using the update-verify feedback method<sup>28,29</sup>, the device conductance in the synaptic network was updated and had an increased accuracy as desired. Herein, because the device conductance (weight) should be maintained over a long period, the CNT transistors in the synaptic network should be operated in a nonvolatile mode. Therefore, pulses with sufficiently large  $V_{\text{high}}$  and  $V_{\text{low}}$  values were applied to the gate electrode  $(V_{\text{high}} = +8 \text{ V}, \text{ and } V_{\text{low}} = -9 \text{ V})$  to update the device conductance. Moreover, during the recognition process, only a small DC bias  $(V_{high} = V_{low} = V_{G,read} = -3 \text{ V})$  was applied to the gate electrodes of all the CNT transistors to read the device conductance. Instead,  $U_i$  was converted according to the drain voltage magnitude (0 V  $\leq V_{D, Ui} \leq 2$  V).

calculating the Euclidean distance between the measured data and each boundary vector and by finding the minimum distance, the tactile pattern that generates the measured data can be inferred. **b** Mapping the process of the Euclidean distance calculation onto the 10×4 CNT transistor array (synaptic network). All the boundary vectors  $W_1$ ,  $W_2$ ,  $W_3$ , and  $W_4$  can be directly mapped as weights in the 9×4 CNT transistor array (*W* matrix) in a columnwise fashion. Additionally, the 1×4s matrix is included in the synaptic network. The input vector is coded using pulses with different levels and is then applied to the drain of the CNT transistor in the row direction. The integrated currents at the column outputs allow direct comparisons of the Euclidean distances. The highest column current ( $\Sigma_{I_{S,C}}$ ) represents the shortest Euclidean distance between  $U_i$  and  $W_j$ . **c** Flowchart of the learning and recognition processes. **d** The measured evolution of the *W* matrix weights (i.e., device conductance of each CNT transistor) during the iterative learning process. Each column represents the corresponding boundary vector. **e** The recognition error rate as a function of the learning iterations. Each data point is the averaged error rate following 30 repetitions.

The sum of the total source currents for each column represented the sum of the product of  $V_{D,Ui}$  and  $W_j$   $(\Sigma I_{S,Cj} = \Sigma V_{D,Ui} \cdot W_j)$ . As a result, as the  $\Sigma I_{S,Cj}$  values obtained from a particular column in the synaptic network increased, the Euclidean distance between  $U_i$  and  $W_j$ —which was recorded in the column—decreased. Figure 5d shows the updating of the weights in the W matrix during the iterative learning process, wherein each column represents  $W_j$ . All the weights were randomly assigned to an initial state. As the leaning process was repeated, the weights were adjusted to adhere to  $W_4(i) > W_3(i) > W_2(i) > W_1(i)$ . Subsequently, when  $U_i$  (without a label) was input to the learned matrix, the tactile pattern could be inferred through the column that generated the

largest output current. As shown in Fig. 5e, a recognition error rate less than 5% can be obtained through 50 or more learning iterations. Therefore, our perceptual sensory system can be improved by learning repeated stimuli and can achieve a performance that is very close to the biological sensory system.

#### Conclusions

In summary, our tactile sensor system was based on the semivolatile CNT transistor device and was composed of a tactile sensor, VCO, neuronal device, and synaptic network. It captured essential morphological and functional similarities related to the biological sensory system. Our tactile sensor system can distinguish temporally correlated pressure stimuli, and the features of tactile patterns can be extracted for pattern recognition. Note that the recognition accuracy can be improved through an iterative learning process, thus illustrating a similarity to biological perceptual learning processes. In addition to the prior attempts executed to capture the similarities of the human sensory system, the developed circuit models of our tactile sensor system enabled a quantitative analysis of the entire system that achieved product-level feasibility based on its similarity with existing digital circuits. Moreover, the developed learning and recognition processes can be equally applicable to other advanced sensors<sup>30–33</sup>.

#### Acknowledgements

This research was supported by the Nano-Material Technology Development Program (2016M3A7B4910426) funded by the Ministry of Science, ICT and Future Planning; the National Research Foundation of Korea (NRF) (grants 2019R1A2C1002491, 2019R1A2B5B01069988, 2016R1A5A1012966, and 2020R1A6A1A03038540); and the Future Semiconductor Device Technology Development Program (grant 10067739) funded by the Ministry of Trade, Industry & Energy (MOTIE) and the Korea Semiconductor Research Consortium (KSRC).

#### Author contributions

S.K. and S.J.C. conceived the project; Y.L. fabricated the CNT transistors; H.D.K. contributed to the analysis of the sensor device; S.K. constructed most of the experimental setup and performed the measurements.

#### Conflict of interest

The authors declare that they have no conflict of interest.

#### Publisher's note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary information is available for this paper at https://doi.org/10.1038/s41427-020-00258-9.

# Received: 10 June 2020 Revised: 21 September 2020 Accepted: 30 September 2020.

Published online: 11 December 2020

#### References

- 1. Mead, C. Neuromorphic electronic systems. Proc. IEEE 78, 1629–1636 (1990).

- Jo, S. H. et al. Nanoscale memristor device as synapse in neuromorphic systems. Nano Lett. 10, 1297–1301 (2010).

- 3. Yu, S. Neuro-inspired computing with emerging nonvolatile memorys. *Proc. IEEE* **106**, 260–285 (2018).

- Kuzum, D., Yu, S. & Philip Wong, H.-S. Synaptic electronics: materials, devices and applications. *Nanotechnology* 24, 382001 (2013).

- Prezioso, M. et al. Training and operation of an integrated neuromorphic network based on metal-oxide memristors. *Nature* 521, 61–64 (2015).

- Jeong, Y., Lee, J., Moon, J., Shin, J. H. & Lu, W. D. K -means data clustering with memristor networks. *Nano Lett.* 18, 4447–4453 (2018).

- Choi, S., Shin, J. H., Lee, J., Sheridan, P. & Lu, W. D. Experimental demonstration of feature extraction and dimensionality reduction using memristor networks. *Nano Lett.* **17**, 3113–3118 (2017).

- Kim, S., Yoon, J., Kim, H. D. & Choi, S. J. Carbon nanotube synaptic transistor network for pattern recognition. ACS Appl. Mater. Interfaces 7, 25479–25486 (2015).

- Hasegawa, T. et al. Learning abilities achieved by a single solid-state atomic switch. Adv. Mater. 22, 1831–1834 (2010).

- Lai, Q. et al. lonic/electronic hybrid materials integrated in a synaptic transistor with signal processing and learning functions. *Adv. Mater.* 22, 2448–2453 (2010).

- 11. Yoon, J. H. et al. An artificial nociceptor based on a diffusive memristor. *Nat. Commun.* **9**, 417 (2018).

- Wang, Z. et al. Memristors with diffusive dynamics as synaptic emulators for neuromorphic computing. *Nat. Mater.* 16, 101–108 (2017).

- Burkitt, A. N. A review of the integrate-and-fire neuron model: I. Homogeneous synaptic input. *Biol. Cybern.* 95, 1–19 (2006).

- Tee, B. C.-K et al. A skin-inspired organic digital mechanoreceptor. Science 350, 313–6 (2015).

- Zang, Y., Shen, H., Huang, D., Di, C. A. & Zhu, D. A dual-organic-transistor-based tactile-perception system with signal-processing functionality. *Adv. Mater.* 29, 1606088 (2017).

- Kim, Y. et al. A bioinspired flexible organic artificial afferent nerve. Science 360, 998–1003 (2018).

- Wang, H. et al. A ferroelectric/electrochemical modulated organic synapse for ultraflexible, artificial visual-perception system. *Adv. Mater.* 30, 1803961 (2018).

- Indiveri, G. & Horiuchi, T. K Frontiers in neuromorphic engineering. Front. Neurosci. 5, 118 (2011).

- Wan, C. et al. An artificial sensory neuron with tactile perceptual learning. Adv. Mater. 30, 1801291 (2018).

- Ohno, T. et al. Short-term plasticity and long-term potentiation mimicked in single inorganic synapses. *Nat. Mater.* 10, 591–595 (2011).

- Chang, T., Jo, S.-H. & Lu, W. Short-term memory to long-term memory transition in a nanoscale memristor. ACS Nano 5, 7669–7676 (2011).

- Kim, S. et al. Experimental demonstration of a second-order memristor and its ability to biorealistically implement synaptic plasticity. *Nano Lett.* 15, 2203–2211 (2015).

- Du, C., Ma, W., Chang, T., Sheridan, P. & Lu, W. D. Biorealistic implementation of synaptic functions with oxide memristors through internal ionic dynamics. *Adv. Funct. Mater.* 25, 4290–4299 (2015).

- Wang, Z. et al. Fully memristive neural networks for pattern classification with unsupervised learning. *Nat. Electron.* 1, 137–145 (2018).

- Park, R. S. et al. Hysteresis in carbon nanotube transistors: measurement and analysis of trap density, energy level, and spatial distribution. ACS Nano 10, 4599–4608 (2016).

- Lee, J. et al. Transparent, flexible strain sensor based on a solutionprocessed carbon nanotube network. ACS Appl. Mater. Interfaces 9, 26279–26285 (2017).

- Kim, S. et al. Pattern recognition using carbon nanotube synaptic transistors with an adjustable weight update protocol. ACS Nano 11, 2814–2822 (2017).

- Kim, S., Lee, Y., Kim, H. D. & Choi, S. J. Parallel weight update protocol for a carbon nanotube synaptic transistor array for accelerating neuromorphic computing. *Nanoscale* 12, 2040–2046 (2020).

- Kim, S., Lee, Y., Kim, H. D. & Choi, S. J. Precision-extension technique for accurate vector-matrix multiplication with a CNT transistor crossbar array. *Nanoscale* 11, 21449–21457 (2019).

- Zhang, J. et al. Highly sensitive flexible three-axis tactile sensors based on the interface contact resistance of microstructured graphene. *Nanoscale* 10, 7387–7395 (2018).

- Dai, M. et al. Two-dimensional van der waals materials with aligned in-plane polarization and large piezoelectric effect for self-powered piezoelectric sensors. *Nano Lett.* **19**, 5410–5416 (2019).

- Feng, W. et al. Sensitive electronic-skin strain sensor array based on the patterned two-dimensional a-In2Se3. *Chem. Mater.* 28, 4278–4283 (2016).

- Wang, X., Qiu, Y., Cao, W. & Hu, P. Highly stretchable and conductive coresheath chemical vapor deposition graphene fibers and their applications in safe strain sensors. *Chem. Mater.* 27, 6969–6975 (2015).