Abstract

In thick dielectrics, electrical breakdown is caused by the generation of spatially and temporally correlated defects that are produced — as in lightning1 — by feedback between defect formation and local stress2. New defects are created in the vicinity of existing defects, leading to rapid and correlated propagation of field-induced defect chains that cause breakdown. By contrast, we show here that defects formed in ultrathin films subjected to realistic electrical stress remain spatially and temporally uncorrelated, even when multiple 'shorts' (chains of defects) begin to bridge the thickness of the films. Besides their relevance to different applications of thin dielectric films, our results have positive implications for the scalability of modern integrated circuits3,4,5,6.

Similar content being viewed by others

Main

To investigate the correlation in defect generation and formation of shorts, we electrically stressed the thin gate dielectrics in about 100 field-effect transistors (FETs) by applying a voltage to the gates and then monitoring the terminal currents as defects accumulated (Fig. 1a).

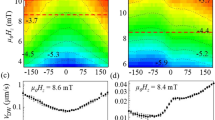

a, Gate dielectric of a field-effect transistor (shaded) configured to study the evolution of n shorts (n is 1, 2, 3 or 4) and the underlying correlation in defect generation in thin films. Each new short is registered by a discrete jump in the gate current, Ig,n, balanced by discrete increases in source and drain current, Is,n and Id,n, which can be used to time and locate the shorts (for example, short 2 occurred at a distance x2 from the source along the channel length Lchan). b, Timing of shorts as a function of gate current. c, Measured time sequence for samples with identical area and thickness to develop at least n shorts. Top, traces measured as for b are used to compute Fn, the cumulative failure distributions with at least n measured shorts (n is 1–4; Tfilm = 1.7 nm, Afilm = 2.5 µm2); bottom, the coincidence of the F1 ← n, derived from Fn using equation (1), shows that these shorts are uncorrelated in location and time (n = 1, measured; when n is 2–4, scaled). d, Improvement in functional reliability as a function of F. The time, tn, at which a fraction of integrated circuits with n faults (Fn) fails depends on the ability of the FET to survive n − 1 shorts without logic failure. Data from oxides of different thickness and area (filled and open symbols), stressed under different conditions, support the scaling theory (solid line). If only 1 out of 10,000 integrated circuit failures is acceptable for a technology, A → B shows the relative improvement in reliability provided that the circuit can sustain just two shorts.

The discrete and irreversible jumps in the gate current (Fig. 1b) that accompany the formation of individual shorts, as current increases through the low-resistivity paths, enabled us to determine the number of shorts (n) present at a given time, and the time of appearance (tn) of each short. Likewise, the ratio of the discrete increases in the source and drain currents determines the position (xn) of these shorts7.

To analyse the degree of correlation in our measurements, we used the theoretical framework of a three-dimensional cubic-lattice percolation model8,9. If a film of thickness Tfilm and area Afilm is stressed at constant voltage, and if the defect generation is spatially and temporally uncorrelated, then the theory makes two key predictions.

First, the cumulative probability distribution of the distances between pairs of shorts should be characterized by the correlation distance Lc → 1 (M.A.A. and R.K.S., unpublished results). The measured locations of the shorts are characterized by an effective correlation distance of Lceff ≥ 0.83, indicating that the spatial correlation is weak. Second, a single-parameter scaling relation

where Fn is the fraction of samples with at least n shorts at time t, must hold. The scaling parameter χ = KAfilmtβ, where K is the stress-dependent constant, and β ∝ Tfilm. The results shown in Fig. 1c for each Fn can be inverted by using equation (1) to obtain χ, and then used to predict F1→n = 1 − e− χ.

The coincidence of these plots in Fig. 1c shows that equation (1) describes the data well. We find that equation (1) holds for films of different thickness and area, subjected to electrical stresses of different duration and field strength, indicating that the spatial and temporal distributions of the shorts in thin films are essentially uncorrelated.

Historically, silicon FETs used thicker silica films as gate insulators. For these films, the initial short was so catastrophic and subsequent defect generation so strongly correlated that the FET, and consequently the integrated circuit, could no longer perform logic operations. By contrast, modern FETs4 use thinner films operated at lower voltages, so that the individual uncorrelated shorts are too 'soft' to cause logic malfunctions10.

If an FET is fault-tolerant up to (n − 1) shorts, the operating lifetime (tn) of the integrated circuit will increase geometrically (from equation (1)) over the traditional fault-intolerant lifetime (t1); that is, (tn/t1)β ≈ (n/e)(2πn)(1/2n)/Fn(1 − 1/n) (Fig. 1d). For β≈1, an acceptable failure fraction of Fn = 10−4 (point A, Fig. 1d), and an integrated circuit that is fault-tolerant to two shorts, the integrated circuit will function for almost 1,000 times as long as would be predicted on the basis of the model for bulk dielectric breakdown (t3 ≈ 850t1; point B, Fig. 1d).

Our results indicate that most modern integrated circuits may have been unintentionally overdesigned for reliability, and that it is possible to design faster integrated circuits with higher operating voltage without sacrificing functional reliability. Although issues such as power management, shallow junction formation and so on remain and must be addressed5,6, our findings allow a relaxation of the speed–reliability constraint that effectively removes oxide breakdown as a fundamental obstacle to continued scaling of silicon integrated circuits.

References

Ogawa, T. in CRC Handbook on Atmospherics Vol. 1 (ed. Volland, H.) 23–63 (1982).

Hippel, A. J. Appl. Phys. 8, 815–832 (1937).

Moore, G. E. Electronics 38, 114–116 (1965).

Semiconductor Industry Association Roadmap for Semiconductors 1999 edn (http://www.itrs.net/ntrs/publntrs.nsf).

Packan, P. A. Science 285, 2079–2080 (1999).

Kingon, A. I., Maria, J.-P & Streiffer, S. K. Nature 406, 1032–1038 (2000).

Degraeve, R., Kaczer, B., De Keersgeiter, A. & Groeseneken, G. Proc. Int. Reliability Phys. Symp. 36, 360–366 (2001).

Capehart, T. W. & Fisher, M. E. Phys. Rev. B 13, 5021–5038 (1976).

Stathis, J. J. Appl. Phys. 86, 5757–5766 (1999).

Alam, M. A., Weir, B. E. & Silverman. P. J. IEEE Trans. Elec. Dev. 49, 239–246 (2002).

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Rights and permissions

About this article

Cite this article

Alam, M., Smith, R., Weir, B. et al. Uncorrelated breakdown of integrated circuits. Nature 420, 378 (2002). https://doi.org/10.1038/420378a

Issue Date:

DOI: https://doi.org/10.1038/420378a

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.