Abstract

Superconducting circuits are exceptionally flexible, enabling many different devices from sensors to quantum computers. Separately, epitaxial semiconductor devices such as spin qubits in silicon offer more limited device variation but extraordinary quantum properties for a solid-state system. It might be possible to merge the two approaches, making single-crystal superconducting devices out of a semiconductor by utilizing the latest atomistic fabrication techniques. Here we propose superconducting devices made from precision hole-doped regions within a silicon (or germanium) single crystal. We analyse the properties of this superconducting semiconductor and show that practical superconducting wires, Josephson tunnel junctions or weak links, superconducting quantum interference devices (SQUIDs) and qubits are feasible. This work motivates the pursuit of ‘bottom-up’ superconductivity for improved or fundamentally different technology and physics.

Similar content being viewed by others

Introduction

The Nb/AlOx/Nb (or Al/AlOx/Al) Josephson junction (JJ) has become almost ubiquitous for superconducting (SC) applications such as magnetometers1, voltage standards2,3, logic4 and qubits5. This follows a long history of development beginning in force with the IBM Josephson digital computer program during the 1970s6, which pioneered the tunnelling JJ technology (mostly based on Pb-alloy tunnel junctions, the critical current spread and the instability of the Pb that limited its applicability). Nb-based tunnel junctions such as Nb/Al-AlOx/Nb (ref. 7) and Nb/AlOx/Nb (refs 8, 9) proved to be more reliable and stable and have become the material of choice in many traditional SC devices, while Al/AlOx/Al junctions are typically preferred for quantum computing at millikelvin-operating temperatures.

But heterogeneous devices such as these can pose problems, especially for low-power or quantum applications, where losses in or at the interfaces of the various materials (for example, surface oxides on the superconductor, JJ insulator, substrate, interlayer dielectrics) can limit device quality dramatically. Possible solutions include better materials10,11,12, weak-link junctions13, symmetry protection14 or three-dimensional (3D) cavity qubits15. Here we consider an alternative approach: atomically precise16, hole-doped SC silicon17 (or germanium18) JJ devices and qubits made entirely out of the same crystal. Like the Si spin qubit, our super-semi19 JJ devices exist inside the ‘vacuum’20,21 of ultra-pure silicon, far away from any dirty interfaces. We predict the possibility of SC wires, JJs and qubits, calculate their critical parameters and find that most known SC qubits should be realizable. This approach may enable better devices and exotic SC circuits as well as a new physical testbed for superconductivity.

Our proposal builds from experimental progress in three different areas. First, the list of SC materials has expanded to include doped covalent semiconductors22, particularly Si (refs 17, 23) and Ge (refs 18, 24). Extremely high doping rates (of acceptors) above the equilibrium solubility were achieved by gas-immersion laser doping (GILD) or ion implantation and annealing, and SC was observed in these high-density hole systems. Second, rapid progress in precise and high-density doping (of donors) in Si16 and Ge25 utilizing atomic layer doping and scanning tunnelling microscope (STM) lithography has opened a new world of possible semiconductor devices, including single dopant qubits26, single-atom-wide wires27 and even vertically stacked 3D nanodevices28,29,30. These same techniques should be applicable to acceptor incorporation. Finally, SC and Si/Ge qubits are widely considered to be leading candidates for fault-tolerant quantum computing; yet both have negatives that combination may improve. For example, coherence times in isotopically enriched and chemically purified Si can reach seconds20, while SC qubits offer a huge range of design space due to their macroscopic nature. Motivated by these results, we consider the following questions: What are the relevant properties of hole-doped SC ‘wires’ in Si? What is required to create properly placed, hole-doped SC Si JJs? And if such fabrication requirements are plausible, would such devices be of interest for qubits or other JJ circuits? The answers to these questions are not obvious a priori given this unusual SC semiconductor system.

Results

Superconductivity in silicon

By doping a semiconductor or an insulator above the metal–insulator transition density, it has been expected that the host material turns into a superconductor19. Superconductivity has been observed in many such materials. (See refs 22 and 31 for reviews.) Particularly, superconductivity in hole-doped, group-IV materials have been found in diamond32, silicon17 and germanium18. Various methods, such as high-pressure high-temperature treatments32 and growth using chemical vapour deposition33,34 for C:B, GILD17,35,36 for Si:B, and ion implantation and annealing for Si:Ga (refs 23, 37) and Ge:Ga (refs 18, 24, 38), were used to achieve very high hole densities required for superconductivity. Table 1 summarizes the superconducting parameters of the hole-doped group-IV materials including those calculated here. They are compared with the conventional metal superconductors.

Superconductivity in silicon was first reported in ref. 17, by heavily doping a Si layer with boron (B) (above its equilibrium solubility in Si, 6 × 1020 cm−3). This led to the very high hole density of nh≃5 × 1021 cm−3 and superconductivity was observed below Tc≃0.35 K, although the SC Si layer (thickness≃35 nm) was inhomogeneous with long tails in the superconducting and diamagnetic transitions. Later experiments35 with much more homogeneous samples (thickness≃80–90 nm) allowed systematic measurements of the dependence of the superconductivity on system parameters, such as the density and the external magnetic field. The highest Tc≃0.6 K was observed for the B density cB≃8 at.% (1 at.% means 1% of Si atoms are replaced with B atoms, which corresponds to 5 × 1020 cm−3) and the minimum B density cc for superconductivity was cc≃2 at.%. The critical field Hc2 for cB=8 at.% was measured to be 0.1 T. The experimental results agree well with the conventional Bardeen–Cooper–Schrieffer (BCS) theory39 for superconductors of type II.

We estimate the characteristic parameters of this superconductor for cB=8 at.%. The observed critical temperature Tc=0.6 K corresponds to a zero temperature energy gap Δ(0)=1.76kBTc=91 μeV. The characteristic lengths in an ideal (pure and local) SC and the more realistic effective values from Ginzburg–Landau (GL) theory have the following relations41:

where ξ0 (ξ) is the BCS (GL) coherence length and λL (λ) is the London (effective) penetration depth, respectively. l is the mean free path and J(R, T) is a function of length R and the temperature T defined by BCS39. Using Hc2(0)=Φ0/2πξ2(0) with Hc2(0)=0.1 T where Φ0=h/2e is the flux quantum, we obtain the GL coherence length ξ(0)≃57 nm. The London penetration depth can be calculated as  with the hole density nh≃4 × 1021 cm3 and the heavy hole effective mass mh≃0.5me with me being the bare electron mass. Since the system with l≃3 nm (<<ξ, λ) is in the dirty limit, using equations (1) and (2) we obtain ξ0=12ξ2(0)/π2l≃1,300 nm and λL(0) (ξ0/l)1/2≃650 nm. The GL parameter κ=λ/ξ≃11 is consistent with type II superconductivity. These characteristic lengths are comparable to conventional metallic superconductors.

with the hole density nh≃4 × 1021 cm3 and the heavy hole effective mass mh≃0.5me with me being the bare electron mass. Since the system with l≃3 nm (<<ξ, λ) is in the dirty limit, using equations (1) and (2) we obtain ξ0=12ξ2(0)/π2l≃1,300 nm and λL(0) (ξ0/l)1/2≃650 nm. The GL parameter κ=λ/ξ≃11 is consistent with type II superconductivity. These characteristic lengths are comparable to conventional metallic superconductors.

Superconducting devices in silicon such as JJs, superconducting quantum interference devices (SQUIDs) and SC qubits could be constructed out of hole-doped regions within the crystal. The doping method (GILD) used for demonstrating the highest Tc SC Si crystals so far35 may not be suitable for the epitaxially encapsulated, nanoscale devices envisioned here. Another method provides an alternative route: STM lithography has been used to precisely implant P dopants in Si. STM lithography is a new technique that allows atomically precise doping of semiconductors. We will briefly summarize the steps of P doping in Si. A Si (001) surface with 2 × 1 reconstruction (dimerization) is prepared and terminated with hydrogen resist. An STM tip is used to selectively remove some of the hydrogen atoms on the surface42 (either across broad swaths of the crystal surface or down to single hydrogen atoms), exposing regions of unmasked silicon atoms. A phosphine (PH3) gas is introduced, which bonds selectively to the exposed silicon sites. At least three adjacent desorbed dimers are needed for a P to replace a surface Si atom. A phosphine molecule is chemisorbed to a dimer, dissociating into PH2+H at room temperature. Further annealing at 350° allows recombination/dissociation processes, resulting in a P atom incorporated into the top Si layer ejecting a Si atom16. In this way, P atoms were then incorporated into the exposed regions (via atomic layer doping), with positioning accuracy to one lattice site43. The resulting 1D or 2D impurity sheet could reach very high doping rate, up to one in every four Si atoms being replaced with a P atom27. It is not necessary to use an STM tip for the hydrogen desorption step, other lithographic techniques may be possible. This process can be repeated to make stacked δ-doped layers as was demonstrated in Ge (refs 28, 29) and Si (ref. 30).

Superconducting wires

The SC Si:B realized by GILD was in a 2D layer with a thickness of tens of nanometres. For SC circuits and JJ applications, forming SC wires will be essential. We consider the use of atomic layer doping and STM lithography to dope B (or other acceptor) atoms into the Si crystal to achieve the very high hole density necessary for SC wires. Since this approach achieved a P density much higher than the B density reached in SC Si doped by GILD, higher hole doping rates may be possible (hence possibly higher critical temperatures) together with extremely fine control on the position and size of the SC region. Figure 1a shows a Si crystal doped with acceptor atoms. The lithographic region has length L, width W and depth D. We assume that every kth layer is doped with doping rate of rD. If Nl monolayers are doped, the depth D=(a/4)(Nl−1)k and the total number of monolayers in the lithographic region are  . The total number of B dopants ND is given by

. The total number of B dopants ND is given by

(a) A specific region inside a single Si crystal, far from any noisy interfaces or surfaces, is hole doped to sufficient acceptor density to go superconducting. The hole cloud, depicted by the orange region, has a larger extent than the lithographically doped region due to finite spread of the hole wavefunction. (b–d) Hole density as a function of the number of total monolayers Nltot of the doped region for different layer-doping rates rD=5, 10, 15, 20 and 25 at.% from bottom to top. Every layer (b), every other layer (c) and every third layer (d) is doped. The critical temperature Tc is shown on the right side of each plot. The blue dashed line indicates the density nh=4 × 1021 cm−3 corresponding to the highest observed Tc=0.6 K for boron in silicon.

where  , with a=5.43 Å being the lattice constant of Si. To estimate hole density, we have to take into account the finite range of the holes27. For the P impurities with Bohr radius 2.5 nm, the effective electron density region has a diameter dB ranging from 1 to 2 nm. An isolated B impurity in Si has a Bohr radius of 1.6 nm (ref. 44), and we choose dB=1 nm. Assuming all B dopants are activated, the hole density nh is given by

, with a=5.43 Å being the lattice constant of Si. To estimate hole density, we have to take into account the finite range of the holes27. For the P impurities with Bohr radius 2.5 nm, the effective electron density region has a diameter dB ranging from 1 to 2 nm. An isolated B impurity in Si has a Bohr radius of 1.6 nm (ref. 44), and we choose dB=1 nm. Assuming all B dopants are activated, the hole density nh is given by

For W and L much larger than dB, it is simplified as nh=(rDNl/b2)/[(a/4)(Nl−1)k+dB]. If the B density in a layer could reach the same level as the P in Si (~25 at.%), the hole density of a single doped layer is 1.7 × 1021 cm−3, which is above the critical hole density for superconductivity. In this case, using the experimentally observed density dependence of the critical temperature, Tc=C(cB/cc−1)0.5 with C≃0.35 (ref. 35), we obtain Tc~0.3 K, but actual critical temperature could be lower than this due to the thin-layer geometry45. The maximum hole density is achieved for a thick doped region (D>>dB) with every layer being doped (k=1). For rD=25 at.%, nh=1/ab2=1.25 × 1022 cm−3 (a few times more than the highest density obtained by laser doping), we get a maximum Tc≃1.2 K, which is comparable to the critical temperature of aluminium (Al). Although this could be possible if all the assumptions here are satisfied, to be more realistic all our calculations below will be for Tc=0.6 K, which has been experimentally realized. Figure 1b–d shows the hole density as a function of depth D when every layer (k=1), every other layer (k=2) or every third layer (k=3) is doped, respectively, for different doping rate rD. The highest observed Tc of 0.6 K for Si:B should be reasonable for applications, for example, quantum devices based on Al with Tc~1 K start to have problems due to quasiparticles at T~200 mK, and the requirements for classical applications such as photon detectors are much less restrictive. To reach the Tc=0.6 K, we need at least three doped layers if each layer is maximally doped (25 at.%) for k=1, corresponding to the minimum depth of the lithographic layer D=a/2=0.27 nm and the hole layer D+dB=1.27 nm. The density strongly depends on the depth for small D (that is, small Nl) and saturates to 4rD/(kab2) for large D. For thin SC wires, a cross-section area larger than 103 nm3 is preferable (that is, W,D≳30 nm) to prevent quantum phase slips46.

Josephson junctions

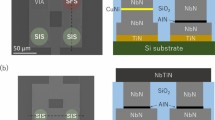

JJs are an essential ingredient for many SC applications. Now we describe how one might realize a JJ made of this Si:B superconductor. We will consider two types of JJs: the SC tunnel junction (STJ, Fig. 2a) and the weak-link47 JJ (Fig. 2b,c). They are different in the way two superconductors are connected. A STJ consists of two SC electrodes divided by a tunnelling barrier such as an insulating layer, while in weak-link JJs the two SCs are connected by a superconducting or metallic bridge. Traditionally, the STJ has been widely used due to its easier fabrication with a AlOx barrier and its well-defined nonlinear current–phase relation. Weak-link junctions could be a good alternative especially in applications requiring high Josephson critical current and/or small size junction areas.

Examples of JJ devices that can be constructed inside the semiconductor are shown. Wire figures depict the extent of the hole wavefunction. (a) STJ with overlapping area A separated by distance d. (b) Weak-link JJ with overlapping SC layers. Critical current is determined by the bridge of cross-section Awl and length d, while the capacitance is determined by the overlap area A and distance d. This geometry is suitable when a large overlap area A (small charging energy EC) is required. (c) Weak-link JJ in a variable thickness bridge geometry (or STJ with no link), suitable if large A is not necessary. (d) SQUID circuit.

Two energy scales that characterize a JJ are the charging energy EC=(2e)2/2CJ for junction capacitance CJ and the junction energy EJ=ħIc/2e where Ic is the critical current (maximum d.c. Josephson current). For the capacitance CJ=εrε0A/d with εr≃12 for Si, the charging energy is given by EC=3.0 eV nm × d/A. For the STJ, the critical current and the normal resistance Rn has a relation48 IcRn=(πΔ)/(2e) tanh(Δ/2kBT), which reduces to IcRn=πΔ(0)/2e at zero temperature. Here Rn is the resistance of the junction in the normal state. The above relation holds true for the weak link near T=Tc, but at T=0, IcRn=1.32πΔ(0)/2e in the dirty limit49. The junction energy at zero temperature then is EJ=0.29 eV Ω × (1/Rn) for the STJ and 0.39 eV Ω × (1/Rn) for the weak link.

The normal resistance Rn has a simple form ρnd/Awl for a weak link where ρn=103 Ω nm (ref. 35). To estimate the normal resistance Rn of the tunnel JJ, we assumed a square potential barrier of width d and height Vb=Eg/2+εF where Eg is the energy gap of Si and εF is the Fermi energy of the holes for a given density. Then, the tunnelling conductance G per unit area is given by

where T(εz) is the transmission coefficient,

and  . Tunnelling resistance Rn=1/G. We numerically calculated the tunnelling resistance assuming the hole effective mass mh=0.5me and obtained Rn≃104e5.6d/A[Ω] with d in unit of nm and A in unit of nm2, for barrier height of Vb=Eg/2+εF≃2.4 eV where Eg is the energy gap of Si and εF is the Fermi energy of holes. Actually, the Fermi energy obtained by using the effective mass at low density is overestimated than the actual Fermi energy of high-density holes50, but the barrier height Vb and shape could be significantly modified, for example, by a spatially well-separated heavily doped region acting as a metallic gate. Therefore, the resistance is tunable to a great extent. Figure 3 gives the tunnelling resistance as a function of the barrier width, for different barrier heights. It clearly shows that Rn is proportional to eαd/A for some constant α. By tuning the barrier height, for example, by lowering it, we can significantly relax the requirement on the necessary thinness of the barrier. If d≲3 nm was needed to obtain large enough tunnelling current for Vb=Eg/2+εF≃2.4 eV, we would need d≲7 nm for Vb=1.9 eV.

. Tunnelling resistance Rn=1/G. We numerically calculated the tunnelling resistance assuming the hole effective mass mh=0.5me and obtained Rn≃104e5.6d/A[Ω] with d in unit of nm and A in unit of nm2, for barrier height of Vb=Eg/2+εF≃2.4 eV where Eg is the energy gap of Si and εF is the Fermi energy of holes. Actually, the Fermi energy obtained by using the effective mass at low density is overestimated than the actual Fermi energy of high-density holes50, but the barrier height Vb and shape could be significantly modified, for example, by a spatially well-separated heavily doped region acting as a metallic gate. Therefore, the resistance is tunable to a great extent. Figure 3 gives the tunnelling resistance as a function of the barrier width, for different barrier heights. It clearly shows that Rn is proportional to eαd/A for some constant α. By tuning the barrier height, for example, by lowering it, we can significantly relax the requirement on the necessary thinness of the barrier. If d≲3 nm was needed to obtain large enough tunnelling current for Vb=Eg/2+εF≃2.4 eV, we would need d≲7 nm for Vb=1.9 eV.

To overcome thermal fluctuations, the junction energy must be much larger than the temperature. In practice, EJ≳5kBT≈4.3 μeV for 10 mK. The barrier distance d of the STJ then must satisfy d≲3 nm for A=1 μm2. The junction area A cannot be much smaller since then the distance d would need to be very small, but an external gate that could also be built of a separate doped region can control the tunnelling barrier height and shape relaxing the restrictions at the cost of more complication in device design. A large junction area would be more easily implemented in the overlapping geometry of Fig. 2a, given that doping a thin layer with large area is probably easier than doping a small but thick region with STM lithography. For the weak link, on the other hand, the required condition is Aw1/d≳0.01 nm, which could be easily satisfied, and the junction energy is independent of the total junction area A. Hence, both Fig. 2b,c would be possible.

If we want to avoid hysteresis in the I–V curve as is usually required for dc SQUID application, we need an overdamped JJ and the junction quality factor Q=ωpRCJ must be smaller than 1, where  is the plasma frequency of the JJ. R is of the order of Rn for the weak link and

is the plasma frequency of the JJ. R is of the order of Rn for the weak link and  for the STJ. For the STJ to satisfy Q<1, typically a shunting resistance would be necessary to reduce the total resistance, since R is very large for an isolated tunnel junction (one would want to avoid this for quantum applications). Alternatively, SC-Insulator-Normal metal-Insulator-SC (SINIS)-type junctions51 may be advantageous for achieving an overdamped JJ. For the weak link,

for the STJ. For the STJ to satisfy Q<1, typically a shunting resistance would be necessary to reduce the total resistance, since R is very large for an isolated tunnel junction (one would want to avoid this for quantum applications). Alternatively, SC-Insulator-Normal metal-Insulator-SC (SINIS)-type junctions51 may be advantageous for achieving an overdamped JJ. For the weak link,  and for Awl=100 nm2, A<3.3 μm2, allowing much smaller size than the STJ.

and for Awl=100 nm2, A<3.3 μm2, allowing much smaller size than the STJ.

For a SQUID application such as shown in Fig. 2d, additional conditions should be satisfied to avoid magnetic hysteresis: βm=2LIc/Φ0<1 where L is the inductance of the SQUID loop. STJs can easily satisfy this since the critical current is small, but a fairly large loop would be needed due to the large junction area A≃1 μm2 required to overcome the thermal fluctuations as discussed above. On the other hand, weak-link JJs open up the possibility of a nanoscale SQUID. For a square loop of area 1 μm × 1 μm, the geometrical inductance L is ~3 pH for wire diameter of a few tens of nm, assuming that the relative permeability of doped Si is one like most nonmagnetic metals. Then, βm<1 translates into Awl/d<2 × 103 nm. Typical values Aw1≃100 nm2 and d≃10 nm would be suitable for a nano-SQUID. Compared with the nano-SQUID based on the metallic SC bridges52, we could get much shorter weak links due to the much higher precision of STM lithography over electron-beam lithography, allowing one to reach the short link limit with highly nonlinear inductance and larger modulation depth in critical current.

Qubits

Finally, we consider the possibility of SC qubits in Si:B. The requirements on JJ parameters for qubits are different from the conditions, for example, SQUID discussed in the previous section. We will consider the core SC qubits—charge, phase and flux—to estimate relevant parameters, noting that more complicated designs would relax the restrictions on the parameters significantly. A charge qubit is a single Cooper pair box connected to a JJ where the two discrete low-energy levels form a logical qubit space. Usually, a gate voltage is applied to tune the system to be in a sweet spot to reduce the effects of the charge noise, but in this case its known sensitivity to charge noise might make a good probe of the charge environment of this system. Figure 4a shows a possible geometry for a charge qubit and Fig. 4b is the equivalent circuit diagram. By choosing different geometries for the two tunnel junctions, for example, dJ≲3 nm and d≳10 nm, the left junction can have large enough JJ energy to act as a JJ, while the right junction has negligible JJ energy and can be considered as a simple capacitor with capacitance Cg. The charge qubit is operated in a regime kBT<<EJ~EC<<Δ where EC is now the total charging energy EC=(2e)2/2(CJ+Cg). Assuming T=10 mK, a JJ with dJ=2.5 nm means that AJ should be ≃1 μm2. The charging energy EC=3.0 eV nm × 1/(AJ/dJ+A/d) with dJ=2.5 nm and AJ=1 μm2 constrains the geometry of the capacitor A/d<<3.1 × 106 nm. So we can choose, for example, A~106 nm2 and d~20 nm.

High JJ critical current makes the phase qubit a good choice for the weak-link JJ. Figure 4c shows a circuit diagram for a simple phase qubit. A phase qubit operates in a regime with kBT<<EC<<EJ, which translates into d/A>>3 × 10−7 nm−1 and AAw1/d2>>7.7 × 103 nm2. A reasonable set of parameters would be, for example, d~10 nm, Aw1~100 nm2 and A~106 nm2. For the flux qubit, the simplest model is a loop with a JJ (radio frequency (rf)-SQUID loop) coupled to an externally supplied flux. The flux qubit operates usually with LJ≲L, where LJ=Φ0/2πIc. The loop inductance is relatively quite small compared with LJ for the typical geometries we have considered so far. This restriction can be lifted by using, for example, a three JJ loop53,54. More advanced qubits such as the transmon qubit55 are realizable by incorporating a big capacitor in the system, which is straight forward. In that case, the JJ can have a small junction area A and both geometries in Fig. 2b,c could be used.

Discussion

Our proposal is promising for new types of JJ devices. The noise environment of buried dopant layers has been reported to be quite low56, which is motivating for quantum applications, but obviously not sufficient. Fabrication requirements, as envisioned, have already been realized in the Si:P or Ge:P systems. Many JJ device and qubit geometries are possible beyond what are considered here, which may further reduce fabrication needs; lattice-site precision of impurities is not a fundamental requirement. An assumption in this work is the plausibility of acceptor placement with atomic layer doping and STM lithography. B is currently being pursued in this context, but it is unproven whether the chemistry of adsorption and incorporation (for example, of B2H6) will work in a similar manner as PH3, nor whether the same densities can be achieved (one in four atoms per ML). We have accounted for this by considering lower densities per monolayer. Quick B diffusion and clumping may limit further thermal anneal budgets, but this problem has already been overcome with low-temperature molecular beam epitaxy (MBE)57. Local strain due to the strong B bonds is almost certainly present, but does not effect the epitaxial nature of the crystal17. As potentially better dopant alternatives, Al (AlH3) or Ga (GaH3) for both Si and Ge should be pursued, as well as more advanced chemistry and surface preparation approaches for STM lithography and doping (for example, BCl3 is used in GILD, so Cl might be considered instead of H).

The extension of the hole cloud (~1 nm) would limit the sharpness of the SC region and hole density would drop to zero over this length. Since it is much smaller than the SC coherence length, the entire hole cloud is expected to be superconducting due to the proximity effect. One of the advantages of this single-crystal device could be that there would be no Schottky barrier between heavily doped (metallic) region and lightly doped (semiconducting) region, and no interface states are expected in the interface between doped and undoped regions.

Stacked multilayer designs of electron-doped Si devices were already demonstrated experimentally30. A second doped layer was grown on top of a nanowire capped by undoped Si of 50–120 nm thickness. The whole device was grown epitaxially. The rather large separation between two doped layers in the experiment was needed to obtain smoother surface for the STM lithography of the top layer and also to get enough separation so that the top layer works as a metallic gate. On the contrary, we need the hole wavefunctions to overlap between layers for the 3D SC region. Thus, we need much smaller separation between layers, and this could be a challenge. In fact, Ge may offer significant benefits over Si for JJ devices. Ge’s clean surfaces and lower thermal requirements for good epitaxial growth28,29 may allow for more and better 3D doped layers as compared with Si (where the limits of epitaxial growth are more likely to result in surface roughness), with less diffusion due to thermal activation anneals.

It is unclear what critical temperatures are possible in pure Ge (or Si) with other acceptors (critical temperatures of up to 7 K (ref. 23) have been reported in Si:Ga/SiO2 interface structures and even higher for diamond, and numerical simulation49 suggests that Al can lead to a higher critical temperature than B in Si). We have focused on Si due to the greater amount of experimental data versus density to guide our device proposals. Theory does not preclude electron-doped SC semiconductors19,49, but experimental efforts have so far shown no evidence44.

The AlOx-based tunnelling JJ has been very successful in many applications over the years, and other materials and different structures have also been studied for various devices58. Building SC devices inside a semiconductor proposed here gives several advantages over conventional approaches. The availability of ultra-pure 28Si with <50 p.p.m. 29Si (ref. 59) and the atomically precise positioning of dopants by STM lithography can help suppress the subgap states due to impurities in the JJ, which is one of the main decoherence channels of SC qubits. Flux noise is another possible source of decoherence for the SQUID60, phase qubit61,62 and flux qubit63,64. It was suggested that the flux noise comes from the fluctuating spins at interfaces and surfaces of the device65,66. Hyperfine interaction was proposed as a possible mechanism for the relaxation of the surface spins67. The lack of nuclear spin in enriched Si at the surface, the separation of the active device region from the surface and the single-crystal structure of the whole device should help significantly reduce the flux noise. The epitaxially grown barrier in this proposal should also reduce any potential two-level fluctuators, as was shown for a crystalline Al2O3 barrier68,69,70. In the Al/Al2O3/Al junctions, the critical current density showed a wider variation than amorphous AlOx barriers. A qubit can be designed to be tolerable to these variations in junction critical current, but it involves a more complicated structure71. For precisely positioned Si:B/Si/Si:B junctions, we expect less variations in system parameters for identically designed devices; barrier quality would be less important for weak-link JJs. Further, the devices can be constructed well below the surface of the semiconductor, away from oxide interfaces that typically cause loss. The quality of the superconducting semiconductor itself is a new concern, and a good early experiment would be to determine the loss of such a device (for example, via a cavity Q). Intriguing in these systems is the possibility of dissipation/quasiparticle engineering by manipulating the disorder of the implanted impurities.

Since the SC properties depend on the hole density, material parameters can be tuned with additional gates, allowing for a tunable SC-normal metal-SC JJ72. In that case, the proximity effect will play an important role and needs to be fully taken into account, a topic also of interest in Majorana physics. In addition to these potentially improved material properties, STM lithography is suitable for small devices such as the nano-SQUID and allows for arbitrary 3D device designs for different types of qubits, detectors, circuits and so on.

Progress in ‘bottom-up’ fabrication techniques, such as STM lithography, has increased the space of devices worth pursuing. Our work further motivates the investigation of acceptor doping via precision techniques, beyond the context of single acceptor qubits73 or for nanoscale but classical electronic devices. Successful demonstration of such proposed physics could not only enable the devices suggested in this work, but also offer an atomically configurable testbed for the nature and limits of semiconductor superconductivity (through, for example, isotope variation, density, disorder, phonon, strain and so on), for Tc engineering, as well as for new devices such as 3D SC device geometries, top-gated tunable JJs or topological qubits74.

Additional information

How to cite this article: Shim, Y.-P. and Tahan, C. Bottom-up superconducting and Josephson junction devices inside a group-IV semiconductor. Nat. Commun. 5:4225 doi: 10.1038/ncomms5225 (2014).

References

Clarke, J., Goubau, W. M. & Ketchen, M. B. Tunnel junction dc SQUID: fabrication, operation, and performance. J. Low Temp. Phys. 25, 99–144 (1976).

Niemeyer, J., Hinken, J. H. & Kautz, R. L. Microwave-induced constant-voltage steps at one volt from a series array of Josephson junctions. Appl. Phys. Lett. 45, 478–480 (1984).

Benz, S. P. & Hamilton, C. A. A pulse-driven programmable Josephson voltage standard. Appl. Phys. Lett. 68, 3171–3173 (1996).

Likharev, K. K. & Semenov, V. K. RSFQ logic/memory family: a new Josephson-junction technology for sub-terahertz-clock-frequency digital systems. IEEE Trans. Appl. Supercond. 1, 3–28 (1991).

Devoret, M. H. & Schoelkopf, R. J. Superconducting circuits for quantum information: an outlook. Science 339, 1169–1174 (2013).

Anacker, W. Josephson compuer technology. IBM J. Res. Develop. 24, 107–112 (1980).

Gurvitch, M., Washington, M. A. & Huggins, H. A. High quality refractory Josephson tunnel junctions utilizing thin aluminum layers. Appl. Phys. Lett. 42, 472–474 (1983).

Ketchen, M. B. et al. Sub-μm, planarized, Nb-AlOx-Nb Josephson process for 125mm wafers developed in partnership with Si technology. Appl. Phys. Lett. 59, 2609–2611 (1991).

Nakagawa, H. et al. A 4-bit Josephson computer ETL-JC1. IEEE Trans. Appl. Supercond. 1, 37–47 (1991).

Kim, Z. et al. Anomalous avoided level crossings in a Cooper-pair box spectrum. Phys. Rev. B 78, 144506 (2008).

Kline, J. S. et al. Sub-micrometer epitaxial Josephson junctions for quantum circuits. Supercond. Sci. Technol. 25, 025005 (2012a).

Chang, J. B. et al. Improved superconducting qubit coherence using titanium nitride. Appl. Phys. Lett. 103, 012602 (2013).

Vijay, R., Sau, J. D., Cohen, M. L. & Siddiqi, I. Optimizing anharmonicity in nanoscale weak link Josephson junction oscillators. Phys. Rev. Lett. 103, 087003–087006 (2009).

Gladchenko, S. et al. Superconducting nanocircuits for topologically protected qubits. Nat. Phys. 5, 48–53 (2005).

Paik, H. et al. Observation of high coherence in Josephson junction qubits measured in a three-dimensional circuit QED architecture. Phys. Rev. Lett. 107, 240501 (2011).

Fuechsle, M. et al. A single-atom transistor. Nat. Nanotechnol. 7, 242–246 (2012).

Bustarret, E. et al. Superconductivity in doped cubic silicon. Nature 444, 465–468 (2006).

Herrmannsdörfer, T. et al. Superconducting state in a gallium-doped germanium layer at low temperatures. Phys. Rev. Lett. 102, 217003 (2009).

Cohen, M. L. The existence of a superconducting state in semiconductors. Rev. Mod. Phys. 36, 240–243 (1964).

Tyryshkin, A. M. et al. Electron spin coherence exceeding seconds in high-purity silicon. Nat. Mater. 11, 143–147 (2012).

Steger, M. et al. Quantum information storage for over 180s using donor spins in a 28Si ‘semiconductor vacuum’. Science 336, 1280–1283 (2012).

Blase, X., Bustarret, E., Chapelier, C., Klein, T. & Marcenat, C. Superconducting group-IV semiconductors. Nat. Mater. 8, 375–382 (2009).

Skrotzki, R. et al. On-chip superconductivity via gallium overdoping of silicon. Appl. Phys. Lett. 97, 192505 (2010).

Skrotzki, R. et al. The impact of heavy Ga doping on superconductivity in germanium. J. Low Temp. Phys. 37, 877–883 (2011).

Scappucci, G. et al. A complete fabrication route for atomic-scale, donor-based devices in single-crystal germanium. Nano Lett. 11, 2272–2279 (2011a).

Kane, B. E. A silicon-based nuclear spin quantum computer. Nature 393, 133–137 (1998).

Weber, B. et al. Ohm's law survives to the atomic scale. Science 335, 64–67 (2012).

Scappucci, G., Capellini, G., Klesse, W. M. & Simmons, M. Y. Phosphorus atomic layer doping of germanium by the stacking of multiple δ layers. Nanotechnology 22, 375203 (2011b).

Klesse, W. M., Scappucci, G., Capellini, G., Hartmann, J. M. & Simmons, M. Y. Atomic layer doping of strained Ge-on-insulator thin films with high electron densities. Appl. Phys. Lett. 102, 151103 (2013).

McKibbin, S., Scappucci, G., Pok, W. & Simmons, M. Epitaxial top-gated atomic-scale silicon wire in a three-dimensional architecture. Nanotechnology 24, 045303 (2013).

Iakoubovskii, K. Recent advances in superconductivity of covalent superconductors. Physica C 469, 675–679 (2009).

Ekimov, E. A. et al. Superconductivity in diamond. Nature 428, 542–545 (2004).

Takano, Y. et al. Superconductivity in diamond thin films well above liquid helium temperature. Appl. Phys. Lett. 85, 2851–2853 (2004).

Takano, Y. et al. Superconducting properties of homoepitaxial CVD diamond. Diam. Relat. Mater. 16, 911–914 (2007).

Marcenat, C. et al. Low-temperature transition to a superconducting phase in boron-doped silicon films grown on (001)-oriented silicon wafers. Phys. Rev. B 81, 020501–020504(R) (2010).

Dahlem, F. et al. Subkelvin tunneling spectroscopy showing Bardeen-Cooper-Schrieffer superconductivity in heavily boron-doped silicon epilayers. Phys. Rev. B 82, 140505(R) (2010).

Fiedler, J. et al. Superconducting films fabricated by high-fluence Ga implantation in Si. Phys. Rev. B 83, 214504 (2011).

Fiedler, J. et al. Superconducting Ga-overdoped Ge layers capped with SiO2: structural and transport investigations. Phys. Rev. B 85, 134530 (2012).

Bardeen, J., Cooper, L. N. & Schrieffer, J. R. Theory of Superconductivity. Phys. Rev. 108, 1175–1204 (1957).

Marder, M. P. Condensed Matter Physics John-Wiley & Sons, Inc. (2000).

Tinkham, M. Introduction to Superconductivity 2nd edn McGraw-Hill Book Co. (1996).

Lyding, J. W., Shen, T., Hubacek, J. S., Tucker, J. R. & Abeln, G. C. Nanoscale patterning and oxidation of Hpassivated Si(100)2×1 surfaces with an ultrahigh vacuum scanning tunneling microscope. Appl. Phys. Lett. 64, 2010–2012 (1994).

Fuechsle, M. et al. Spectroscopy of few-electron single-crystal silicon quantum dots. Nat. Nanotechnol. 5, 502–505 (2010).

Gasseller, M. et al. Single-electron capacitance spectroscopy of individual dopants in silicon. Nano Lett. 11, 5208–5212 (2011).

Grockowiak, A. et al. Superconducting properties of laser annealed implanted Si:B epilayers. Supercond. Sci. Technol. 26, 045009 (2013).

Tinkham, M. & Lau, C. N. Quantum limit to phase coherence in thin superconducting wires. Appl. Phys. Lett. 80, 2946–2948 (2002).

Likharev, K. K. Superconducting weak links. Rev. Mod. Phys. 51, 101–159 (1979).

Ambegaokar, V. & Baratoff, A. Tunneling between superconductors. Phys. Rev. Lett. 10, 486–489 (1963).

Kulik, I. O. & Omel'yanchuk, A. N. Zh. Eskp. Teor. Fiz. Pis. Red. 21, 216 (1975); trans. JETP Lett. 21, 96 (1975).

Bourgeois, E. & Blase, X. Superconductivity in doped cubic silicon: An ab initio study. Appl. Phys. Lett. 90, 142511 (2007).

Maezawa, M. & Shoji, A. Overdamped Josephson junctions with Nb/AlOx/Al/AlOx/Nb structure for integrated circuit application. Appl. Phys. Lett. 70, 3603–3605 (1997).

Vijay, R., Levenson-Falk, E. M., Slichter, D. H. & Siddiqi, I. Approaching ideal weak link behavior with three dimensional aluminum nanobridges. Appl. Phys. Lett. 96, 223112 (2010).

Mooij, J. E. et al. Josephson persistent-current qubit. Science 285, 1036–1039 (1999).

Chiorescu, I., Nakamura, Y., Harmans, C. J. P. M. & Mooij, J. E. Coherent quantum dynamics of a superconducting flux qubit. Science 299, 1869–1871 (2003).

Koch, J. et al. Charge-insensitive qubit design derived from the Cooper pair box. Phys. Rev. A 76, 042319 (2007).

Shamim, S., Mahapatra, S., Polley, C., Simmons, M. Y. & Ghosh, A. Suppression of low-frequency noise in two-dimensional electron gas at degenerately doped Si:P delta layers. Phys. Rev. B 83, 233304 (2011).

Weir, B. E. et al. Electrical characterization of an ultrahigh concentration boron delta doping layer. Appl. Phys. Lett. 65, 737–739 (1994).

Golubov, A. A., Kupriyanov, M. Y. & Il'ichev, E. The current-phase relation in Josephson junctions. Rev. Mod. Phys. 76, 411–469 (2004).

Becker, P., Pohl, H.-J., Riemann, H. & Abrosimov, N. Enrichment of silicon for a better kilogram. Phys. Status Solidi A 207, 49–66 (2010).

Anton, S. M. et al. Magnetic flux noise in dc SQUIDs: temperature and geometry dependence. Phys. Rev. Lett. 110, 147002 (2013).

Bialczak, R. C. et al. 1/f Flux noise in Josephson phase qubits. Phys. Rev. Lett. 99, 187006 (2007).

Sank, D. et al. Flux noise probed with real time qubit tomography in a Josephson phase qubit. Phys. Rev. Lett. 109, 067001 (2012).

Yoshihara, F., Harrabi, K., Niskanen, A. O., Nakamura, Y. & Tsai, J. S. Decoherence of flux qubits due to 1/f flux noise. Phys. Rev. Lett. 97, 167001 (2006).

Kakuyanagi, K. et al. Dephasing of a superconducting flux qubit. Phys. Rev. Lett. 98, 047004 (2007).

Sendelbach, S. et al. Magnetism in SQUIDs at millikelvin temperatures. Phys. Rev. Lett. 100, 227006 (2008).

Sendelbach, S., Hover, D., Mück, M. & McDermott, R. Complex inductance, excess noise, and surface magnetism in dc SQUIDs. Phys. Rev. Lett. 103, 117001 (2009).

Wu, J. & Yu, C. C. Modeling flux noise in SQUIDs due to hyperfine interactions. Phys. Rev. Lett. 108, 247001 (2012).

Oh, S. et al. Low-leakage superconducting tunnel junctions with a single-crystal Al2O3 barrier. Supercond. Sci. Technol. 18, 1396–1399 (2005).

Oh, S. et al. Elimination of two level fluctuators in superconducting quantum bits by an epitaxial tunnel barrier. Phys. Rev. B 74, 100502(R) (2006).

Kline, J. S. et al. Sub-micrometer epitaxial Josephson junctions for quantum circuits. Supercond. Sci. Technol. 25, 025005 (2012b).

Kline, J. S., Wang, H., Oh, S., Martinis, J. M. & Pappas, D. P. Josephson phase qubit circuit for the evaluation of advanced tunnel barrier materials. Supercond. Sci. Technol. 22, 015004 (2009).

Doh, Y.-J. et al. Tunable supercurrent through semiconductor nanowires. Science 309, 272–275 (2005).

Ruskov, R. & Tahan, C. On-chip cavity quantum phonodynamics with an acceptor qubit in silicon. Phys. Rev. B 88, 064308 (2013).

Nayak, C., Simon, S. H., Stern, A., Freedman, M. & Sarma, S. D. Non-Abelian anyons and topological quantum computation. Rev. Mod. Phys. 80, 1083–1159 (2008).

Acknowledgements

We thank R. Butera, M. Friesen, A. Mizel, B. Palmer and R. Ruskov for critical reading of the manuscript, and R. Joynt for useful conversations.

Author information

Authors and Affiliations

Contributions

C.T. planned the project. Y.-P.S. performed the theoretical and numerical calculations. Both the authors contributed to the interpretation of the results, discussions and writing of the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing financial interests.

Rights and permissions

About this article

Cite this article

Shim, YP., Tahan, C. Bottom-up superconducting and Josephson junction devices inside a group-IV semiconductor. Nat Commun 5, 4225 (2014). https://doi.org/10.1038/ncomms5225

Received:

Accepted:

Published:

DOI: https://doi.org/10.1038/ncomms5225

This article is cited by

-

Energy-participation quantization of Josephson circuits

npj Quantum Information (2021)

-

Single-crystalline boron-doped diamond superconducting quantum interference devices with regrowth-induced step edge structure

Scientific Reports (2019)

-

Graphene qubit motivates materials science

Nature Nanotechnology (2019)

-

Semiconductor-inspired design principles for superconducting quantum computing

Nature Communications (2016)

-

Bottom-up assembly of metallic germanium

Scientific Reports (2015)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.