Abstract

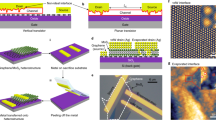

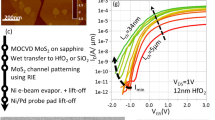

Ultra-scaled transistors are of interest in the development of next-generation electronic devices1,2,3. Although atomically thin molybdenum disulfide (MoS2) transistors have been reported4, the fabrication of devices with gate lengths below 1 nm has been challenging5. Here we demonstrate side-wall MoS2 transistors with an atomically thin channel and a physical gate length of sub-1 nm using the edge of a graphene layer as the gate electrode. The approach uses large-area graphene and MoS2 films grown by chemical vapour deposition for the fabrication of side-wall transistors on a 2-inch wafer. These devices have On/Off ratios up to 1.02 × 105 and subthreshold swing values down to 117 mV dec–1. Simulation results indicate that the MoS2 side-wall effective channel length approaches 0.34 nm in the On state and 4.54 nm in the Off state. This work can promote Moore’s law of the scaling down of transistors for next-generation electronics.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 51 print issues and online access

$199.00 per year

only $3.90 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Data availability

The data that support the findings of this study are available from the corresponding author upon reasonable request.

References

Liu, Y. et al. Promises and prospects of two-dimensional transistors. Nature 591, 43–53 (2021).

Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors. Nat. Rev. Mater. 1, 16052 (2016).

Akinwande, D. et al. Graphene and two-dimensional materials for silicon technology. Nature 573, 507–518 (2019).

Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS2 transistors. Nat. Nanotechnol. 6, 147–150 (2011).

Desai, S. B. et al. MoS2 transistors with 1-nanometer gate lengths. Science 354, 99–102 (2016).

Moore, G. E. Cramming more components onto integrated circuits. Proc. IEEE 86, 82–85 (1998).

Chau, R., Doyle, B., Datta, S., Kavalieros, J. & Zhang, K. Integrated nanoelectronics for the future. Nat. Mater. 6, 810–812 (2007).

Lundstrom, M. Moore’s law forever? Science 299, 210–211 (2003).

Migita, S., Morita, Y., Matsukawa, T., Masahara, M. & Ota, H. Experimental demonstration of ultrashort-channel (3 nm) junctionless FETs utilizing atomically sharp V-grooves on SOI. IEEE Trans. Nanotechnol. 13, 208–215 (2014).

Novoselov, K. S. et al. Electric field effect in atomically thin carbon films. Science 306, 666–669 (2004).

Deng, N. et al. Black phosphorus junctions and their electrical and optoelectronic applications. J. Semicond. 42, 081001 (2021).

Kim, K. S. et al. Large-scale pattern growth of graphene films for stretchable transparent electrodes. Nature 457, 706–710 (2009).

Lee, S., Sohn, J., Jiang, Z., Chen, H.-Y. & Wong, H.-S. P. Metal oxide-resistive memory using graphene-edge electrodes. Nat. Commun. 6, 8407 (2015).

Sohn, J., Lee, S., Jiang, Z., Chen, H. & Wong, H. P. Atomically thin graphene plane electrode for 3D RRAM. In 2014 IEEE International Electron Devices Meeting (IEDM) 5.3.1–5.3.4 (IEEE, 2014).

Wu, F. et al. A 10 nm short channel MoS2 transistor without the resolution requirement of photolithography. Adv. Electron. Mater. 7, 2100543 (2021).

Yoon, Y., Ganapathi, K. & Salahuddin, S. How good can monolayer MoS2 transistors be? Nano Lett. 11, 3768–3773 (2011).

Dunlap, W. C. & Watters, R. L. Direct measurement of the dielectric constants of silicon and germanium. Phys. Rev. 92, 1396–1397 (1953).

Xie, L. et al. Graphene-contacted ultrashort channel monolayer MoS2 transistors. Adv. Mater. 29, 1702522 (2017).

Liu, C. et al. Two-dimensional materials for next-generation computing technologies. Nat. Nanotechnol. 15, 545–557 (2020).

Yu, Z. et al. Realization of room-temperature phonon-limited carrier transport in monolayer MoS2 by dielectric and carrier screening. Adv. Mater. 28, 547–552 (2016).

Tseng, A. A., Kuan, C., Chen, C. D. & Ma, K. J. Electron beam lithography in nanoscale fabrication: recent development. IEEE Trans. Electron. Packag. Manuf. 26, 141–149 (2003).

Sinha, S., Cline, B., Yeric, G., Chandra, V. & Cao, Y. Design benchmarking to 7 nm with FinFET predictive technology models. In Proc. 2012 ACM/IEEE International Sympposium on Low Power Electrons and Design 15–20 (Association for Computing Machinery, 2012).

Suzuki, K., Tanaka, T., Tosaka, Y., Horie, H. & Arimoto, Y. Scaling theory for double-gate SOI MOSFET’s. IEEE Trans. Electron Devices 40, 2326–2329 (1993).

Xuejue, H. et al. Sub 50-nm FinFET: PMOS.In International Electron Devices Meeting (IEDM) Technical Digest Paper 67–70 (IEEE, 1999).

Yang-Kyu, C. et al. Sub-20nm CMOS FinFET technologies. In International Electron Devices Meeting (IEDM) Technical Digest Paper 19.11.11–19.11.14 (IEEE, 2001).

Bin, Y. et al. FinFET scaling to 10 nm gate length. In International Electron Devices Meeting (IEDM) Technical Digest Paper 10.2.1-10.2.4 (IEEE, 2002).

Fu-Liang, Y. et al. 5nm-gate nanowire FinFET. In Proc. Symposium on VLSI Technology, Digest of Technical Papers 196–197 (IEEE, 2004).

Lee, H. et al. Sub-5nm all-around gate FinFET for ultimate scaling. In Proc. Symposium on VLSI Technology, Digest of Technical Papers 58–59 (IEEE, 2006).

Yeo, K. H. et al. Gate-all-around (GAA) twin silicon nanowire MOSFET (TSNWFET) with 15 nm length gate and 4 nm radius nanowires. In International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2006).

Loubet, N. et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In Symposium on VLSI Technology T230-T231 (IEEE, 2017).

Franklin, A. D. et al. Sub-10 nm carbon nanotube transistor. Nano Lett. 12, 758–762 (2012).

Cao, Q., Tersoff, J., Farmer, D. B., Zhu, Y. & Han, S.-J. Carbon nanotube transistors scaled to a 40-nanometer footprint. Science 356, 1369–1372 (2017).

Qiu, C. et al. Scaling carbon nanotube complementary transistors to 5-nm gate lengths. Science 355, 271–276 (2017).

English, C. D., Smithe, K. K. H., Xu, R. L. & Pop, E. Approaching ballistic transport in monolayer MoS2 transistors with self-aligned 10 nm top gates. In International Electron Devices Meeting (IEDM) 5.6.1–5.6.4 (IEEE, 2016).

Jiang, J. et al. Ultrashort vertical-channel van der Waals semiconductor transistors. Adv. Sci. 7, 1902964 (2020).

Zou, X., Liu, L., Xu, J., Wang, H. & Tang, W.-M. Few-layered MoS2 field-effect transistors with a vertical channel of sub-10 nm. ACS Appl. Mater. Inter. 12, 32943–32950 (2020).

International Roadmap for Devices and Systems (IRDS™) 2021 Edition (IEEE, 2021); https://irds.ieee.org/editions/2021

Bohr, M. A 30 year retrospective on Dennard’s MOSFET scaling paper. IEEE Solid-State Circuits Soc. Newsl. 12, 11–13 (2007).

Acknowledgements

We thank W.-Z. Bao from Fudan University for valuable discussions. This work was supported by the National Natural Science Foundation of China (grant nos. 62022047, 61874065, U20A20168 and 51861145202), the National Key R&D Program (grant no. 2021YFC3002200 and 2020YFA0709800), The Beijing Natural Science Foundation (grant no. M22020), the Fok Ying-Tong Education Foundation (grant no. 171051), the Beijing National Research Center for Information Science and Technology Youth Innovation Fund (grant no. BNR2021RC01007), State Key Laboratory of New Ceramic and Fine Processing of Tsinghua University (grant no. KF202109) and the Research Fund from Beijing Innovation Center for Future Chip, Center for Flexible Electronics Technology of Tsinghua University and the Independent Research Program of Tsinghua University (grant no. 20193080047).

Author information

Authors and Affiliations

Contributions

H.T. and T.-L.R. proposed the idea and the project. H.T. and F.W. designed the experiment. Y. Shen and Y. Sun performed the simulation. F.W., Z.H., G.G. and J.R. performed the device fabrication and characterization. Y.Y. provided suggestions to the manuscript. T.-L.R. and H.T. supervised the project. All the authors discussed the results and commented on the manuscript.

Corresponding authors

Ethics declarations

Competing interests

The authors declare no competing interests.

Peer review

Peer review information

Nature thanks Dennis Lin and the other, anonymous, reviewers(s) for their contribution to the peer review of this work.

Additional information

Extended data

is available for this paper at https://doi.org/10.1038/s41586-021-04323-3.

Publisher’s note Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Extended data figures and tables

Extended Data Fig. 1 As-fabricated, Al-contacted graphene transistors.

(a, b) The IDS-VGS transfer curves and IDS-VDS output curves. The electrical conductivity is ~106 S/m at VGS = 0 V. (c) The optical image. After Al deposition and lift-off process, the samples were stored at 10−5 bar vacuum to avoid oxidization. (d) The device structure diagram. The channel width and channel length are 8 μm and 22 μm, respectively.

Extended Data Fig. 2 The quality verification of self-oxidized AlOx.

(a) The I-V curves another 10 devices. The 2.4 V voltage drop between graphene and Al is a safe value for the measurements. (b) A typical optical image of the measured structure. (c) The diagram of the measured structure. After Al deposited on graphene, the samples are stored in clean atmosphere condition for more than 3 days. Then, Al is surrounded by dense AlOx layer, and Pt is deposited after EBL process.

Extended Data Fig. 3 The EDS mapping of 0.34 nm gate-length side-wall transistor.

(a) The TEM image of this EDS mapping region in BF mode. (b–i) The EDS mapping of carbon (C), oxygen (O), aluminum (Al), silicon (Si), sulfur (S), titanium (Ti), molybdenum (Mo) and hafnium (Hf). The mapping of Mo and S verifies the presence of the 2D MoS2 channel. The C element seen on the top of MoS2 can be attributed to the organic residue like PMMA or contaminants from fabrication.

Extended Data Fig. 4 Back-gated planar MoS2 transistors.

(a) The measured structure. The channel width and channel length are 4 μm and 5 μm, respectively. (b–p)The IDS-VBG transfer curves under different VDS bias of the 15 typical back-gated planar MoS2 transistors. The MoS2 channel is highly n-doped when VBG = 50 V.

Extended Data Fig. 5 The tunability of the Al screening layer of the 0.34 nm gate-length side-wall transistor.

(a) The measured structure and signal input. (b) The IDS-VBS characteristics under different VAl bias, when graphene gate is fixed at 0 V.

Extended Data Fig. 6 The detailed tunability of the Al screening layer.

(a) The basic 0.34 nm graphene side-wall edge gated MoS2 transistor and signal input, the Al screening layer is connected to ground. (b) The IDS-VGr characteristics at VBS = 0 V and VAl = 0 V. The VDS varies from 10 mV to 3.0 V. (c) The 0.34 nm graphene side-wall edge gated MoS2 transistor and signal input, the Al screening layer is fixed at different bias. (d) The IDS-VGr characteristics at VDS = 0 V and VAl = 0 V. The VAl varies from –2.0 V to 2.0 V with 0.5 V step. (e) The Al side-wall gated MoS2 transistor and signal input, the graphene layer is connected to ground. (f) The IDS-VAl characteristics at VBS = 0 V and VGr = 0 V. The VDS varies from 10 mV to 3.0 V.

Extended Data Fig. 7 The reproducibility of the 0.34 nm gate-length side-wall transistors.

Additional 49 devices are measured at VBS = 50 V, VAl = 0 V and VDS = 1 V. From additional device 1 to device 28, the measured 0.34 nm gate-length side-wall transistors are with Lch = 1 μm; from additional device 29 to device 49, the measured 0.34 nm gate-length side-wall transistors are with Lch = 0.5 μm.

Extended Data Fig. 8 TCAD simulation for extracting the effective gate length in the Off state.

(a) The simulated transfer curve under VBS = 50 V, VAl = 0 V and VDS = 50 mV. (b) The carrier density along vertical MoS2 channel. By definition of Ioff = 10−12A and nthreshold = 2 × 1012 cm−3 (correspond to 1.3 × 105 cm−2), the Leff is 4.54 nm.

Extended Data Fig. 9 The TCAD simulation results of the 0.34 nm gate-length side-wall transistors to boost On-state performance.

The transfer curves by scaling down Lch from 500 nm to 4.54 nm shown in (a) log-scale and (b) linear-scale. The transfer curves under extreme Lch = 4.54 nm with different fixed Al bias shown in (c) log-scale and (d) linear-scale. The transfer curves under extreme Lch = 4.54 nm by scaling down gate dielectric thickness from 14 nm to 5 nm shown in (e) log-scale and (f) linear-scale. Under 14 nm HfO2 as gate dielectric, VBS = 50 V, VAl = 0 V and VDS = 50 mV condition, the On-state current can be further improved ~2 orders of magnitude.

Rights and permissions

About this article

Cite this article

Wu, F., Tian, H., Shen, Y. et al. Vertical MoS2 transistors with sub-1-nm gate lengths. Nature 603, 259–264 (2022). https://doi.org/10.1038/s41586-021-04323-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41586-021-04323-3

This article is cited by

-

Logic-in-memory application of ferroelectric-based WS2-channel field-effect transistors for improved area and energy efficiency

npj 2D Materials and Applications (2024)

-

Vertical iontronic energy storage based on osmotic effects and electrode redox reactions

Nature Energy (2024)

-

High-performance ferroelectric field-effect transistors with ultra-thin indium tin oxide channels for flexible and transparent electronics

Nature Communications (2024)

-

Ultrashort vertical-channel MoS2 transistor using a self-aligned contact

Nature Communications (2024)

-

Homojunction-loaded inverters based on self-biased molybdenum disulfide transistors for sub-picowatt computing

Nature Electronics (2024)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.