Abstract

Electronics is approaching a major paradigm shift because silicon transistor scaling no longer yields historical energy-efficiency benefits, spurring research towards beyond-silicon nanotechnologies. In particular, carbon nanotube field-effect transistor (CNFET)-based digital circuits promise substantial energy-efficiency benefits, but the inability to perfectly control intrinsic nanoscale defects and variability in carbon nanotubes has precluded the realization of very-large-scale integrated systems. Here we overcome these challenges to demonstrate a beyond-silicon microprocessor built entirely from CNFETs. This 16-bit microprocessor is based on the RISC-V instruction set, runs standard 32-bit instructions on 16-bit data and addresses, comprises more than 14,000 complementary metal–oxide–semiconductor CNFETs and is designed and fabricated using industry-standard design flows and processes. We propose a manufacturing methodology for carbon nanotubes, a set of combined processing and design techniques for overcoming nanoscale imperfections at macroscopic scales across full wafer substrates. This work experimentally validates a promising path towards practical beyond-silicon electronic systems.

This is a preview of subscription content, access via your institution

Access options

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

$29.99 / 30 days

cancel any time

Subscribe to this journal

Receive 51 print issues and online access

$199.00 per year

only $3.90 per issue

Buy this article

- Purchase on Springer Link

- Instant access to full article PDF

Prices may be subject to local taxes which are calculated during checkout

Similar content being viewed by others

Change history

20 September 2019

A minor error in the wording of the legend for Fig. 3 has been corrected.

References

Khan, H. N., Hounshell, D. A. & Fuchs, E. R. H. Science and research policy at the end of Moore’s law. Nat. Electron. 1, 14–21 (2018).

Shulaker, M. et al. Carbon nanotube computer. Nature 501, 526–530 (2013).

Hills, G. et al. Understanding energy efficiency benefits of carbon nanotube field-effect transistors for digital VLSI. IEEE Trans. NanoTechnol. 17, 1259–1269 (2018).

Franklin, A. et al. Sub-10 nm carbon nanotube transistor. Nano Lett. 12, 758–762 (2012).

Brady, G. J. et al. Quasi-ballistic carbon nanotube array transistors with current density exceeding Si and GaAs. Science 2, e1601240 (2016).

Javey, A., Guo, J., Wang, Q., Lundstrom, M. & Dai, H. Ballistic carbon nanotube field-effect transistors. Nature 424, 654–657 (2003).

Aly, M. M. S. et al. Energy-efficient abundant-data computing: the N3XT approach to energy-efficient abundant-data computing. Proc. IEEE 107, 19–48 (2019).

Lee, C.-S., Pop, E., Franklin, A. D., Haensch, W. & Wong, H.-S. P. A compact virtual-source model for carbon nanotube FETs in the sub-10-nm regime-Part I: Intrinsic elements. IEEE Trans. Electron Devices 62.9 3061-3069 (2015).

Tans, S. J., Verschueren, A. R. M. & Dekker, C. Room-temperature transistor based on a single carbon nanotube. Nature 393, 49–52 (1998).

Patil, N. et al. VMR: VLSI-compatible metallic carbon nanotube removal for imperfection-immune cascaded multi-stage digital logic circuits using carbon nanotube FETs. In IEEE Int. Electron Devices Meet. https://doi.org/10.1109/IEDM.2009.5424295 (IEEE, 2009).

Cao, Q., Kim, H., Pimparkar, N., Kulkarni, J. & Wang, C. Medium-scale carbon nanotube thin-film integrated circuits on flexible plastic substrates. Nature 454, 495–500 (2008).

Shulaker, M., Saraswat, K., Wong, H. & Mitra, S. Monolithic three-dimensional integration of carbon nanotube FETs with silicon CMOS. In Symp. VLSI Technology Digest Tech. Pap. https://doi.org/10.1109/VLSIT.2014.6894422 (IEEE, 2014).

Shulaker, M. et al. Carbon nanotube circuit integration up to sub-20 nm channel lengths. ACS Nano. 8, 3434–3443 (2014).

Shulaker, M. et al. Experimental demonstration of a fully digital capacitive sensor interface built entirely using carbon-nanotube FETs. In IEEE Int. Solid-State Circuits Conf. Digest Tech. Pap. https://doi.org/10.1109/ISSCC.2013.6487660 (IEEE, 2013).

Shulaker, M. et al. Sensor-to-digital interface built entirely with carbon nanotube FETs. IEEE J. Solid-State Circ. 41, https://doi.org/10.1109/JSSC.2013.2282092 (2014).

Ding, L. et al. CMOS-based carbon nanotube pass-transistor logic integrated circuits. Nat. Commun. 3, 677 (2012).

Shulaker, M. et al. Efficient metallic carbon nanotube removal for highly-scaled technologies. In IEEE Int. Electron Devices Meet. https://doi.org/10.1109/IEDM.2015.7409815 (IEEE, 2015).

Shulaker, M., Wei, H., Patil, N., Provine, J. & Chen, H. Linear increases in carbon nanotube density through multiple transfer technique. Nano Lett. 11, 1881–1886 (2011).

Won, Y. et al. Zipping, entanglement, and the elastic modulus of aligned single-walled carbon nanotube films. Proc. Natl Acad. Sci. USA 110, 20426–20430 (2013).

Kang, S.-M. & Leblebici, Y. CMOS Digital Integrated Circuits (Tata McGraw-Hill Education, 2003).

Zhang, Z. et al. Doping-free fabrication of carbon nanotube based ballistic CMOS devices and circuits. Nano Lett. 7, 3603–3607 (2007).

Shahrjerdi, D. et al. High-performance air-stable n-type carbon nanotube transistors with erbium contacts. ACS Nano 7, 8303–8308 (2013).

Ding, L. et al. Y-contacted high-performance n-type single-walled carbon nanotube field-effect transistors: scaling and comparison with Sc-contacted devices. Nano Lett. 9, 4209–4214 (2009).

Xu, J.-L. et al. Efficient and reversible electron doping of semiconductor-enriched single-walled carbon nanotubes by using decamethylcobaltocene. Sci. Rep. 7, 6751 (2017).

Geier, M. L., Moudgil, K., Barlow, S., Marder, S. R. & Hersam, M. C. Controlled n-type doping of carbon nanotube transistors by an organorhodium dimer. Nano Lett. 16, 4329–4334 (2016).

Zhang, J., Wang, C., Fu, Y., Che, Y. & Zhou, C. Air-stable conversion of separated carbon nanotube thin-film transistors from p-type to n-type using atomic layer deposition of high-κ oxide and its application in CMOS logic circuits. ACS Nano 5, 3284–3292 (2011).

Markov, I. L., Hu, J. & Kim, M.-C. Progress and challenges in VLSI placement research. Proc. IEEE 103, 1985–2003 (2015).

Celio, C., Patterson, D. A. & Asanovic, K. The Berkeley Out-Of-Order Machine (BOOM): an Industry-Competitive, Synthesizable, Parameterized RISC-V Processor. Technical Report No. UCB/EECS-2015-167 (University of California at Berkeley, 2015); http://www2.eecs.berkeley.edu/Pubs/TechRpts/2015/EECS-2015-167.pdf.

Patterson, D. 50 Years of computer architecture: From the mainframe CPU to the domain-specific tpu and the open RISC-V instruction set. In IEEE Int. Solid-State Circuits Conf. (IEEE, 2018).

Lau, C., Srimani, T., Bishop, M. D., Hills, G. & Shulaker, M. M. Tunable n-type doping of carbon nanotubes through engineered atomic layer deposition HfOx films. ACS Nano 12, 10924–10931 (2018).

Brady, G. et al. Polyfluorene-sorted, carbon nanotube array field-effect transistors with increased current density and high on/off ratio. ACS Nano 8, 11614–11621 (2014).

Wang, J. et al. Growing highly pure semiconducting carbon nanotubes by electrotwisting the helicity. Nat. Catal. 1, 326–331 (2018).

Si, J. et al. Scalable preparation of high-density semiconducting carbon nanotube arrays for high-performance field-effect transistors. ACS Nano 12, 627–634 (2018).

Lin, A., Patil, N., Wei, H., Mitra, S. & Wong, H.-S. P. ACCNT—A metallic-CNT-tolerant design methodology for carbon-nanotube VLSI: concepts and experimental demonstration. IEEE Trans. Electron Dev. 56, 2969–2978 (2009).

Batude, P. et al. Advances, challenges and opportunities in 3D CMOS sequential integration. In IEEE Int. Electron Devices Meet. https://doi.org/10.1109/IEDM.2011.6131506 (IEEE, 2011).

Shulaker, M. et al. Monolithic 3D integration of logic and memory: Carbon nanotube FETs, resistive RAM, and silicon FETs. In IEEE Int. Electron Devices Meet. https://doi.org/10.1109/IEDM.2014.7047120 (IEEE, 2014).

Clark, L. T. et al. ASAP7: A 7-nm finFET predictive process design kit. Microelectron. J. 53, 105–115 (2016).

Zhang, J. et al. Carbon nanotube correlation: promising opportunity for CNFET circuit yield enhancement. In Proc. 47th Design Autom. Conf. https://doi.org/10.1145/1837274.1837497 (IEEE, 2010).

Sherazi, S. M. et al. Track height reduction for standard-cell in below 5nm node: how low can you go? In Design-Process-Technology Co-optimization for Manufacturability XII 10588 1058809 (International Society for Optics and Photonics, 2018).

Hills, G. et al. Rapid co-optimization of processing and circuit design to overcome carbon nanotube variations. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 34, 1082–1095 (2015).

Acknowledgements

We acknowledge Analog Devices, Inc. (ADI), the Defence Advanced Research Projects Agency (DARPA) Three-Dimensional System-on-Chip (3DSoC) program, the National Science Foundation and the Air Force Research Laboratory for support. We thank S. Feindt, A. Olney, T. O’Dwyer, S. Gupta and S. Knepper (all at ADI), and Dimitri Antoniadis and Utsav Banerjee (both at MIT) for collaborations.

Author information

Authors and Affiliations

Contributions

G.H. performed all VLSI design aspects of this project (developing and analysing DREAM, creating the CNFET process design kit and designing all standard cells in the CNFET library; he performed the entire RV16X-NANO RTL-to-GDS physical design and led experimental calibration and testing). C.L. performed all fabrication aspects of this project (developing and experimentally demonstrating RINSE, developing, experimentally demonstrating and characterizing MIXED; he developed the fabrication process, and fabricated all of the RV16X-NANO wafers and their subsequent packaging to chips). A.W. led the architectural definition of RV16X-NANO (including Bluespec, the Verilog hardware description language and the instruction-set architecture; he also wrote the test programs). S.F. contributed to the architectural definition, system design and implementation. M.D.B., T.S., P.K. and R.H. contributed to developing the fabrication process and establishing the CNFET fabrication flow. A.A. contributed to circuit design. Y.S. and D.M. contributed to project development. A., A.C. and M.M.S. were in charge, advised, and led on all aspects of the project.

Corresponding author

Ethics declarations

Competing interests

A.C. is a board member at Analog Devices, Inc., and this work was sponsored in part by Analog Devices, Inc.

Additional information

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Peer review information Nature thanks Marko Radosavljevic and the other, anonymous, reviewer(s) for their contribution to the peer review of this work.

Extended data figures and tables

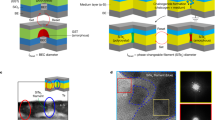

Extended Data Fig. 1 Fabrication process flow for RV16X-NANO.

The fabrication process is a 5-metal-layer (M1 to M5) process and involves >100 individual process steps. s-CNT, semiconducting CNT; S/D, source/drain.

Extended Data Fig. 2 Microscopy image of a full fabricated RV16X-NANO die.

The processor core is in the middle of the die, with test circuitry surrounding the perimeter (when the RV16X-NANO is diced for packaging, these test structures are removed). The test structures include test structures for monitoring fabrication, as well as for measuring and characterizing all of the 63 standard cells in our standard cell library.

Extended Data Fig. 3 CNFET standard cell library.

List of all of the standard cells comprising our standard cell library, along with a microscopy image of each fabricated standard cell, the schematic of each cell, and a typical measured waveform from each fabricated cell. As expected for static CMOS logic stages, the CNFET logic stages exhibit output voltage swing exceeding 99% of VDD, and achieve gain of >15. Experimental waveforms are not shown for cells whose functionality is not demonstrated by output voltage as a function of either input voltage or time; for example, for cells without outputs (for example, fill cells: cell names that start with ‘fill_’ or decap cells: cell names that start with ‘decap_’), for cells whose output is constant (tied high/low: cell names that start with ‘tie_’), or for transmission gates (cell names that start with ‘tg_’).

Extended Data Fig. 4 Image of a completed RV16X-NANO 150-mm wafer.

Each wafer includes 32 dies (single die shown in Extended Data Fig. 2).

Extended Data Fig. 5 Negligible effect of RINSE on CNTs and CNFETs.

a, CNT density is the same pre- versus post-RINSE. b, CNFET ID–VGS exhibit minimal change for sets of CNFETs fabricated with and without RINSE (VDS = −1.8 V for all measurements shown). Both samples came from the same wafer, which was diced after the CNT deposition but before the RINSE process. One sample underwent RINSE while the other sample did not. c, CNFETs can still be doped NMOS after the RINSE process, leveraging our MIXED process (VDS = −1.2 V for all measurements shown).

Extended Data Fig. 6 MIXED CNFET CMOS characterization.

a, Definitions of key metrics for characterizing logic gates, including SNM, gain and swing. VOH, VIH, VIL and VIL (labelled on the VTCs in a, where (VIL, VOH) and (VIH, VOL) are the points on the VTC where ΔVOUT/ΔVIN = −1) are used to extract the noise margin: SNM = min(SNMH, SNML). b, Key metrics extracted for the 10,400 CNFET CMOS nor2 logic gates measured in Fig. 5 (metrics defined in a). This is the largest CNT CMOS demonstration to date, to our knowledge. VDD is 1.2 V. c, SNM is extracted based on the distributions from b. We analyse >100 million logic gate pairs based on these experimental results. d, Spatial dependence of VIH (as an example parameter to compute SNM). Each pixel represents the VIH of the nor2 at that location in the die. Importantly, VIH increases across the die (from top to bottom). The change in VIH corresponds with slight changes in CNFET threshold voltage. The fact that the threshold voltage variations are not independently and identically distributed (i.i.d.), but rather have spatial dependence, illustrates that a portion of the threshold voltage variations (and therefore variation in SNM) is due to wafer-level processing-related variations (CNT deposition is more uniform across the 150-mm wafer). Future work should optimize processing steps, for example, increasing the uniformity of the atomic-layer-deposition oxide deposition used for electrostatic doping to further improve SNM for realizing VLSI circuits. e, Wafer-scale CNFET CMOS characterization. Measurements from 4 dies across 150-mm wafer (1,000 CNFET CMOS nor2 logic gates are sampled randomly from the 10,400 such logic gates in each die). No outliers are excluded. Yield and performance variations are negligible across the wafer, illustrated by the distribution of the output voltage swing.

Extended Data Fig. 7 Effect of metallic CNTs on digital VLSI circuits.

a, Reduction in CNFET EDP benefits versus pS (metallic CNTs increase IOFF, degrading EDP). pS ≈ 99.999%, sufficient to minimize EDP cost due to metallic CNTs to ≤5%. b, pNMS versus pS (metallic CNTs degrade SNM), (shown for SNMR = VDD/5, and for a circuit of one million logic gates). Although 99.999% pS is sufficient to limit EDP degradation to ≤5%, panel b shows that SNM imposes far stricter requirements on purity: pS ≈ 99.999999% (that is, number of 9s is 8) to achieve pNMS ≥ 99% (number of 9s is 2). Results in panels a and b are simulated for VLSI circuit modules from a 7-nm node processor core (see Supplementary Information and Methods for additional details).

Extended Data Fig. 8 Methodology to solve VTCs using CNFET I–V measurements.

a, Experimentally measured ID versus VGS for all 1,000 NMOS (VDS = 1.8 V) and 1,000 PMOS CNFETs (VDS = −1.8 V), with no CNFETs omitted. Metallic CNTs (m-CNTs) present in some CNFETs result in high off-state leakage current (IOFF = ID at VGS = 0 V). b, VTC and SNM parameter definitions, for example, for (nand2, nor2). DR is the driving logic stage; LD is the loading logic stage. SNM = min(SNMH, SNML), where SNMH = VOH(DR) – VIH(LD) and SNML = VIL(LD) – VOL(DR). c–e, Methodology to solve VTCs (for example, for nand2) using experimentally measured CNFET I–V curves. c, Example ID versus VDS for NMOS and PMOS CNFETs (VGS is swept from −1.8 V to 1.8 V in 0.1-V increments). d, Schematic. To solve a VTC (for example, VOUT versus VA with VB = VDD): for each VA, find V1 and VOUT such that iPA + iPB = iNA = iNB (DC, direct current, convergence). e, Current in the pull-up network (iPU, where iPU = iPA + iPB, and iPA and iPB are the labelled drain currents of the PMOS FETs gated by A and B, respectively) and current in the pull-down network (iPD, where iPD = iNA = iNB, and iNA and iNB are the labelled drain currents of the NMOS FETs gated by A and B, respectively) versus VOUT and VA. The VTC is seen where these currents intersect. CNFETs are fabricated at a ~1 µm technology node, and the CNFET width is 19 µm in panel a.

Extended Data Fig. 9 DREAM implementation and methodology.

a, Standard cell layouts (derived using the ‘asap7sc7p5t’ standard cell library37), illustrating the importance of CNT correlation: because the length of CNTs (which can be of the order of hundreds of micrometres) is typically much longer compared with the CNFET contacted gate pitch (CGP, for example about 42–54 nm for a 7-nm node37), the number of s-CNTs and m-CNTs in CNFETs can be uncorrelated or highly correlated depending on the relative physical placement of CNFET active regions38. For many CMOS standard cell libraries at sub-10-nm nodes (for example refs 37,39), the active regions of FETs are highly aligned, resulting in highly correlated number of m-CNTs among CNFETs in library cells, further degrading VTCs (because one m-CNT can affect multiple CNFETs simultaneously). b–f, Generating a variation-aware CNFET SNM model, shown for a D-flip-flop (dff) derived from the asap7sc7p5t standard cell library37. b, Layout used to extract netlists for each logic stage. c, Schematic: CNFETs are grouped by logic stage (with nodes arbitrarily labelled ‘D’, ‘MH’, ‘MS’, ‘SH’, ‘SS’, ‘CLK’, ‘clkn’, ‘clkb’ and ‘QN’ for ease of reference). d, For each extracted netlist, there can be multiple VTCs: for each logic stage output, a logic stage input is sensitized if the output state (0 or 1) depends on the state of that input (given the states of all the other inputs). For example, for a logic stage with Boolean function: Y = !(A*B+C), C is sensitized when (A, B) = (0, 0), (0, 1) or (1, 0). We simulate all possible VTCs (over all logic stage outputs and sensitized inputs), and also in the presence of m-CNTs. For example, panel d shows a subset of the VTCs for the logic stage in panel b with output node ‘MH’ (labelled in panel c), and sensitized input ‘D’ (with labelled nodes (‘clkb’, ‘clkn’, ‘MS’) = (0, 1, 0)). The dashed line indicates VTC with no m-CNTs, and the solid lines are example VTCs in the presence of m-CNTs (including the effect of CNT correlation). In each case, we model VOH, VIH, VIL and VOL as affine functions of the number of m-CNTs (Mi) in each of r regions (M1, ..., Mr), with calibration parameters in the static noise margin (SNM) model matrix T (shown in panel f). e, Example calibration of the SNM model matrix T for the VTC parameters extracted in panel d; the symbols are VTC parameters extracted from circuit simulations (using Cadence Spectre), and solid lines are the calibrated model. f, Affine model form. g–j, VLSI design and analysis methodology. g, Industry-practice physical design flow to optimize energy and delay of CNFET digital VLSI circuits, including: (1) library power/timing characterization (using Cadence Liberate) across multiple VDD and using parasitics extracted from standard cell layouts (derived from the asap7sc7p5t standard cell library), in conjunction with a CNFET compact model8. (2) Synthesis (using Cadence Genus), place-and-route (using Cadence Innovus) with back-end-of-line (BEOL) wire parasitics from the ASAP7 process design kit (PDK). (3) Circuit EDP optimization: we sweep both VDD and target clock frequency (during synthesis/place-and-route) to create multiple physical designs. The one with best EDP is used to compare design options (for example, DREAM versus baseline). h, Subset of logic gates in an example circuit module, showing the effect of CNT correlation at the circuit level (for example, the m-CNT counts of CNFETs P3,1 and P5,1 are both equal to M1 + M2 + M3)40. i, Distribution of SNM over all connected logic stage pairs, for a single sample of the circuit m-CNT counts. The minimum SNM for each trial limits the probability that all noise margin constraints in the circuit are satisfied (pNMS). j, Cumulative distribution of minimum SNM over 10,000 Monte Carlo trials, shown for multiple target pS values, where pS is the probability that a given CNT is a semiconducting CNT. These results are used to find pNMS versus pS for a target SNM requirement (SNMR), where pNMS is the fraction of trials that meet the SNM requirement for all logic stage pairs. We note that pNMS can then be exponentiated to adjust for various circuit sizes based on the number of logic gates. k, CNFET compact model parameters (for example, 7-nm node).

Supplementary information

Supplementary Information

Supplementary Text, Data, Tables and References.

Rights and permissions

About this article

Cite this article

Hills, G., Lau, C., Wright, A. et al. Modern microprocessor built from complementary carbon nanotube transistors. Nature 572, 595–602 (2019). https://doi.org/10.1038/s41586-019-1493-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41586-019-1493-8

This article is cited by

-

Chirality engineering for carbon nanotube electronics

Nature Reviews Electrical Engineering (2024)

-

The reformation of catalyst: From a trial-and-error synthesis to rational design

Nano Research (2024)

-

Ternary bistable ring PUF for high-secure applications

The Journal of Supercomputing (2024)

-

A programmable gain amplifier based on a two-level CNTFET op amp with optimized trans-conductance to drain current ratio

Analog Integrated Circuits and Signal Processing (2024)

-

Highly selective growth of (6,5) single-walled carbon nanotubes from sigma phase alloy catalyst

Nano Research (2024)

Comments

By submitting a comment you agree to abide by our Terms and Community Guidelines. If you find something abusive or that does not comply with our terms or guidelines please flag it as inappropriate.